一种低功耗采样MOSFET功率管电流的电路的制作方法

一种低功耗采样mosfet功率管电流的电路

技术领域

1.本发明涉及电子元器件、半导体、集成电路,尤其涉及一种既低功耗采样mosfet功率管电流的电路。

背景技术:

2.在dc/dc转换器的设计中,无论采用任何一种控制方法,对mosfet功率管的电流采样都必不可少,例如:在谷底电流和峰值电流模式下,分别需要每个周期采集下功率管和上功率管的电流,并结合相应的斜波补偿,形成电流斜波,电流斜波与跨导放大器的输出相交,产生pwm信号,控制功率管的开关,电流斜波的斜率需要精准的控制在设定的范围内,才能够保证控制环路的稳定性,例如:峰值电流模式下,斜波补偿的上升斜率(m)和采样电感电流的下降斜率(m2)需要满足以下关系:

[0003][0004]

控制环路才能够稳定,式中,d代表占空比。

[0005]

如果电流采样偏离设计值过高,相当于斜率补偿不够,会出现次谐波震荡;反之,如果电流采样偏离设计值过低,合成后的电流斜波斜率主要由斜率补偿组成,控制模式变为电压模式,按照电流模式设计的频率补偿将无法正确的补偿环路中的零极点,从而导致不稳定的震荡,因此,精准的电流采样是dc/dc转换器保持稳定的基础。

[0006]

图1所示为用上功率管作为范例的电流采样的结构图,包括功率管m0、采样管m1、放大器1、电阻r4和p型mos管m2,功率管m0可以是上功率管或者下功率管,根据控制模式的不同,选择合适的功率管采样。

[0007]

当电感电流流经该功率管m0,需要对其电流进行采样,采样管m1与功率管m0是相同类型,只是尺寸面积比功率管m0小,采样管m1与功率管m0共栅极,源极或者漏极其中之一也连接在一起,没有相连的另一极通过放大器1的作用保持在相同电位;例如:对图1中的n型上功率管采样,采样管m1与功率m1管共栅极和漏极,功率管m0的源极连接到放大器1的正向输入端,放大器1的输出连接p型mos管m2的栅极,采样管m1的源极与mos管m2的源极相连,并一起连接到放大器1的反向输入端,放大器1与mos管m2形成完整的负反馈控制环路,在该环路的作用下,采样管m1与功率管m0的源极保持相同电压,功率管m0和采样管m1开启时,漏极和源极之间的电气特性等效于一个电阻,漏极与源极之间的电压差除以这个电阻就等于两极之间流过的电流,由于两个管子的漏极与源极之间的电压差相等,各自流过的电流就与各自的等效电阻保持一个反比的关系,例如:功率管m0与采样管m1的等效电阻比例是1:n,

[0008]

r1=n*r0,

[0009]

r0代表功率管m0的等效电阻,r1采样管m1的等效电阻,那么功率管m0与采样管m1的电流比例是n:1,也就是:

[0010]

i

smpl

=i

out

/n

[0011]

功率管m0与采样管m1的等效电阻不是一个固定的值,会受到外界因素的影响,例

如:阻值会随着栅极对源极的电压差增大而降低,并随着环境温度的提高而增大,但是,这些变化对阻值影响的百分比是相同的,因此,两个管子阻值的比例能够保持不变,使得电流的比例也保持恒定,这个比例由各自的面积决定,面积越大,阻值越小,最终,与功率管m0电流保持固定比例的采样电流通过电阻可以转换为采样电压,供下游电路处理。

[0012]

功率管m0工作时自身消耗的功率为:

[0013]

p

m0

=(v

in

‑

v

out

)*i

out

[0014]

对这个电流进行采样所消耗的功率为:

[0015]

p

sample

=v

in

*i

out

/n

[0016]

采样电流由v

in

,经过采样管m1、mos管m2以及采样电阻r4,一直到地,采样所需的功耗不仅仅是采样管m1的功耗,而是采样电流在整个路径上的消耗,如果功率管m0采用集成电路的工艺设计,采样管m1的大小有很大的灵活性,通常几十欧姆到几千欧姆都很容易实现,因此,根据功耗的要求可以自由选择一个很大的采样比例,取得很小的采样电流,降低采样功耗,例如:功率管m0的导通电阻是100mω,n=10000时,m1的导通电阻就是1000ω,在v

in

=5v,i

out

=1a时,m0消耗的功率是100mw,采样导致的额外功耗是0.5mw,也就是0.5%,然而,采用集成电路工艺设计的功率管m0结构复杂,例如:当今0.18um工艺下的20v耐压的功率ldmos(laterally double

‑

diffused mosfet)需要18层光罩完成制成,当今为了更好的性能,更具竞争力的成本,功率管m0往往采用分离半导体器件的工艺设计,例如:同样是20v耐压的功率管m0,在分离器件工艺下只需要5层光罩,成本上的优势显而易见,采样管m1需要与功率管m0使用相同的工艺,才能够保证各种电气性能的匹配,因此,采样管m1和功率管m0在同一片晶圆(wafer)上,控制电路必须用集成电路工艺设计,需要另一片晶圆,在封装时,就不可避免的把来自两片晶圆上的裸片(die)合封在一起,如图2所示,功率管m0和采样管m1的源极分别通过打线连接到控制电路,打线需要焊盘(bond pad),其尺寸正比于打线的线径,例如:1.2mil(=30.48um)线径的铜线需要90um x 90um的焊盘。焊盘的尺寸不能大于mosfet的源极的尺寸,因为这样的话焊盘之下会留有很大的空余面积,从而降低源极的样本密度(pattern density),影响其电气特性,也就是说,采样管m1的最小尺寸被焊盘的大小限制了,例如:图3中所示的耐压20v的功率管m0的等效电阻是15mω,功率管m0与采样管m1的面积比例是大约64,在v

in

=5v,i

out

=1a时,功率管m0消耗的功率是15mw,采样导致的额外功耗是78mw,比功率管m0的消耗还大!

技术实现要素:

[0017]

传统的电流采样方法之所以产生大量功耗是因为采样电流由输入流到地。相对于输出电流,采样电流虽然很小,但是其路径上的电压差很大,导致采样功耗很大。过大的采样功耗,会降低系统的整体效率,甚至会触发热保护,影响系统的正常运转,因此,要降低采样功耗,或者降低采样电流,或者降低路径上的电压差。本发明提供的低功耗采样mosfet功率管电流的结构,从这两方面着手,实现低功耗采样,并且摆脱了功率管与采样管大小比例的限制。

[0018]

本发明采用的技术方案为:包括:放大器1、采样管m1、功率管m0和mos管m2,采样管m1和功率管m0共栅极,采样管m1和功率管m0共漏极,用于输入v

in

电压,采样管m1的源极为采样极,采样极与mos管m2连接、且共同连接到放大器1的反向输入端,放大器1的输出端连接

mos管m2的栅极,mos管m2输出端接采样电阻r4;功率管m0的源极为输出级,用于输出v

out

电压;还包括:mos管m3、分压电阻r5、分压电阻r6,分压电阻r5与分压电阻r6串联在功率管m0的源极和漏极之间,分压电阻r5与分压电阻r6共接点连接放大器1的正向输入端;mos管m3的漏极接输出极,mos管m3与mos管m2共栅极和共源极,mos管m3与mos管m2构成电流镜。

[0019]

进一步的,采用独立的两片裸片作为器件的基底,功率管m0和采样管m1位于裸片1上;放大器1、mos管m3、mos管m2、采样电阻r4、分压电阻r5和分压电阻r6分布于裸片2上,分压电阻r5未与分压电阻r6连接的一端接入v

in

电压。

[0020]

进一步的,功率管m0和采样管m1为同类型的mos管,选用n型mos管。

[0021]

进一步的,所述mos管m2与mos管m3类型相同,都采用p型mos管,mos管m2的源极接采样极、漏极接采样电阻r4。

[0022]

进一步的,所述mos管m3与mos管m2之间还连接有控制环路,用于保证mos管m3与mos管m2漏极电压相同,所述控制环路包括:放大器2、p型mos管m4,mos管m2和mos管m3的漏极分别接入放大器2的反向输入端和正向输入端,放大器2的输出端接mos管m4栅极,mos管m4源极接mos管m2漏极、漏极接采样电阻r4。

[0023]

进一步的,所述mos管m4还可以选用n型,mos管m2和mos管m3的漏极分别接入放大器2的正向输入端和反向输入端,放大器2的输出端接mos管m4栅极,mos管m4漏极接mos管m2漏极、源极接采样电阻r4。

[0024]

从上述技术方案可以看出本发明具有如下优点:在电流采样电路中增加了分压电阻r5、分压电阻r6,通过降低分压电阻r5与r6之间的比例,可以降低采样管m1上的原始采样电流,这就等效于增大了功率管与采样管的面积比例;在此基础上,mos管m2与mos管m3形成的电流镜,使得采样管m1的原始采样电流得以重新分配,增大mos管m2与mos管m3的电流镜比例,原始采样电流的大部分可以返回输出,成为输出电流,小部分经由采样电阻流入地,成为最终采样电流,这等效于进一步增大了功率管与采样管的面积比例,于是,在功率管与采样管的面积比例比较小的情况下,本发明中的结构解决了采样功耗过大的问题。

[0025]

同时,随着功率管与采样管的面积比例比变小,原始采样电流与功率管电流的比例更加准确,分压电阻和电流镜的加入会对最终采样电流的准确性产生一定的影响,但是,电阻分压以及电流镜准确度都依赖于器件之间的匹配,集成电路工艺下,对匹配的控制远远好于分离器件,因此,分压电阻和电流镜的加入对最终采样电流的准确性影响可以忽略不计。

附图说明

[0026]

图1为现有电流采样结构图;

[0027]

图2为现有的采用不同工艺设计mosfet与控制电路时的合封结构图;

[0028]

图3为现有的采用分离器件工艺设计的功率mosfet和采样mosfet的版图;

[0029]

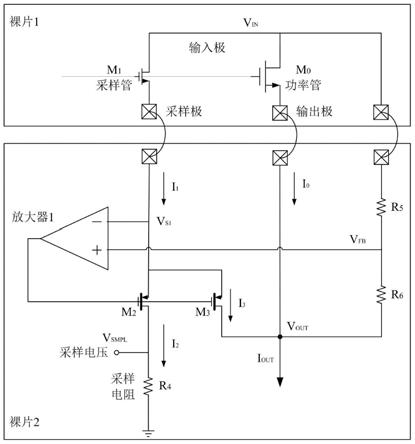

图4为本专利的电路原理图;

[0030]

图5为本专利关于保证电流镜漏极电压相同的控制环路;

[0031]

图6为本专利的关于保证电流镜漏极电压相同的又一控制环路。

具体实施方式

[0032]

以下结合附图对本发明的具体实施方式做具体说明。

[0033]

图4为本发明的原理图,包括:放大器1、采样管m1、功率管m0和mos管m2,采样管m1和功率管m0二者选用同类型,都采用n型,且而二者共栅极和共漏极,漏极输入v

in

电压,采样管m1的源极为采样极,采样极与mos管m2连接、且共同连接到放大器1的反向输入端,放大器1的输出端连接mos管m2的栅极,mos管m2的输出端接采样电阻r4;功率管m0的源极为输出极,用于输出v

out

电压;还包括:mos管m3、分压电阻r5、分压电阻r6,该电路采用独立的两片裸片作为器件的基底,图4所示功率管m0和采样管m1位于裸片1上,放大器1、mos管m3、mos管m2、采样电阻r4、分压电阻r5和分压电阻r6分布于裸片2上,分压电阻r5与分压电阻r6串联在功率管m0的源极和漏极之间,用于采样v

in

与v

out

之间的电压差;分压电阻r5与分压电阻r6的共接点电压v

fb

等于:

[0034]

v

fb

=(v

in

–

v

out

)*r6/(r5+r6)+v

out

[0035]

分压电阻r5与分压电阻r6的共接点连接放大器1的正向输入端,电压v

fb

接入放大器1正向输入端,采样管m1的采样极电压v

s1

接到放大器1的反向输入端和p型mos管m2的源极,mos管m2的栅极与放大器1的输出端相连,mos管m2的漏极作为最终采样电流的输出,接到采样电阻r4;由放大器1和mos管m2形成的负反馈回路保证了:

[0036]

v

s1

=v

fb

,

[0037]

采样管m1的电流是:

[0038]

i1=(v

in

‑

v

s1

)/r1,

[0039]

可以简化为:

[0040]

i1=i0/n/(1+r6/r5),

[0041]

mos管m2也可以为n型mos管,如果选择n型,放大器1的正向输入端、反向输入端需要交换连接方式。

[0042]

mos管m3与mos管m2共栅极和共源极连接,构成电流镜,mos管m3的漏极端接输出极,假设mos管m3的mos管m2的面积比例是m:1,相应的电流比例就是:

[0043]

i2=i3/m,

[0044]

其中,i2为mos管m2的电流,i3为mos管m3的电流,由于:

[0045]

i1=i2+i3,

[0046]

所以:

[0047]

i2=i0/n/(1+r6/r5)/(1+m),

[0048]

对比传统方式,最终采样电流相比功率管电流降低的倍数是:

[0049]

k=(1+r6/r5)*(1+m),

[0050]

因为,另一部分采样管m1的电流经由mos管m3的漏极输出到v

out

:

[0051]

i3=i0*m/(1+m)/n/(1+r6/r5),

[0052]

改进之后的采样电路产生的功耗可以分为与r5和r6相关的:

[0053]

p

r

=(v

in

‑

v

out

)*(v

in

‑

v

out

)/(r5+r6),

[0054]

以及与i3相关的:

[0055]

p

i3

=i3*(v

in

‑

v

out

),

[0056]

以及与i2相关的:

[0057]

p

i2

=i2*v

in

,

[0058]

分压电阻r5和分压电阻r6的电流输出到v

out

,i3也最终输出到v

out

,这两个电流都成为i

out

的一部分,最终的输出电流是它们的总和:

[0059]

i

out

=i0*[1+m/(1+m)/n/(1+r6/r5)+r0/(r5+r6)]

[0060]

因此,p

r

与p

i3

虽然由采样电路产生,但是这部分功耗与m0产生的功耗一样,都属于输出电流导致的功耗,此外,r5和r6是分压电阻,其值通常很大,例如:几十kω到几百kω,导致r0/(r5+r6)<<1,产生的电流和功耗可以忽略不计,由此可见,采样导致的额外功耗只有p

i2

,它与功率管m0产生的功耗的比例是:

[0061]

p

i2

/p

m0

=v

in

/(v

in

–

v

out

)/n/k,

[0062]

在n不变的情况下,p

i2

可以通过调整分压电阻r5与分压电阻r6的比例来降低,同时增大电流镜m3与m2的比例,把流入地的最终采样电流i2进一步降低,以满足功耗的要求,例如:如果分压电阻r5与分压电阻r6的比例为1:2,mos管m3与mos管m2的比例为50:1,在同样的情况下v

in

=5v,i

out

=1a,r0=15mω,n=64,输出电流消耗的功率依然大约是15mw,采样导致的额外功耗p

i2

是0.51mw,也就是3.4%。相比传统方法下78mw的额外功耗,降低了153倍,实际上i

out

≠i0,而是i

out

=1.005*i0,但是在上述计算中,把i

out

近似为i0,该简化造成的误差可以忽略不计。

[0063]

分压电阻r5与分压电阻r6的比例以及mos管m3与mos管m2的比例要进行调整,不能仅仅考虑功耗,也要保证电路的性能,例如:如果分压电阻r6与分压电阻r5的比例过高,采样管m1的漏极与源极之间的压降就会很小,采样过小的电压需要放大器具有更低的输入失调电压,否则功率管m0与采样管m1的电流比例无法保证,这无疑增加了放大器的设计难度;反之,如果降低这个比例,增大采样管m1漏极与源极之间的压降,采样管m1的源极会十分接近输出电压,当这个电压差太小时,mos管m3的源极和漏极将没有足够的空间以保证电流镜的正常工作,因此,优化分压电阻r6与分压电阻r5的比例时,要在保证电路正常工作的前提下平衡功耗和准确性。

[0064]

mos管m3与mos管m2形成电流镜结构,要使得电流镜能够按照mos管m3与mos管m2的面积比例分流采样管m1的电流,mos管m3与mos管m2需要工作在相同的工作区,mosfet在工作的状态下,有2个工作区,也就是,线性区和恒流区,要保证mos管m3与mos管m2处在相同的工作区,它们的漏极电压要相同,这通常需要增加一个保证漏极电压相同的控制环路,如图5所示,mos管m2和mos管m3的漏极分别接入放大器2的反向输入端和正向输入端,该控制环路通过放大器2与p型mos管m4形成的负反馈回路,强制mos管m2和mos管m3的漏极始终保持相等的电压,从而保证mos管m2和mos管m3的工作区一样;图6所示,如果mos管m4选择n型mos管,控制环路仍然能够工作,mos管m2和mos管m3的漏极分别接入放大器2的正向输入端和反向输入端,放大器2的输出端接mos管m4栅极,mos管m4漏极接mos管m2漏极、源极接采样电阻r4。

[0065]

增大mos管m3与mos管m2的比例,固然可以降低p

i2

,但是,过大的比例会使得i2在低输出电流的情况下变的很小,i2不仅仅是电流镜的其中一个分支电流,也在放大器1和放大器2的这两个反馈回路中扮演着重要角色,如果i2过低,这两个回路存在不稳定或者响应太慢的问题,因此,优化mos管m3与mos管m2的比例要平衡功耗和环路在各种条件下的正常工作。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1