串列周边接口SPI系统和其数据传输方法与流程

串列周边接口spi系统和其数据传输方法

技术领域

1.本发明的实施例主要有关于一串列周边接口(serial peripheral interface,spi)技术,特别有关于动态选取芯片选取引脚的串列周边接口技术。

背景技术:

2.串列周边接口(serial peripheral interface bus,spi)是一种用于芯片通信的同步串行通信接口规范。串列周边接口在单芯片(system on a chip,soc)和微控制器(microcontroller,mcu)的领域中广泛被使用。

3.在目前的串列周边接口技术,当主装置连接从装置时,主装置(master device)的一组串列周边接口主埠(master port)会配置一芯片选取引脚来连接一从装置(slavedevice)。然而,当主装置连接多个从装置时,主装置往往必须配置多组串列周边接口主埠,因而造成引脚的浪费。

技术实现要素:

4.有鉴于上述背景技术的问题,本发明的实施例提供了一种串列周边接口(spi)系统和数据传输方法。

5.根据本发明的一实施例提供了一种串列周边接口系统。串列周边接口系统包括多个从装置和一主装置。主装置包括一芯片选取控制电路和一芯片选取模式选取电路。芯片选取控制电路用以产生一第一选取信号和一第二选取信号。芯片选取模式选取电路耦接上述芯片选取控制电路和一动态芯片选取引脚电路,且根据上述第一选取信号决定是否选取上述动态芯片选取引脚电路,来选取一芯片选取引脚。当上述动态芯片选取引脚电路被选取时,上述芯片选取控制电路传送上述第二选取信号至上述动态芯片选取引脚电路,以从多个芯片选取引脚选取上述芯片选取引脚,并将数据传送给对应上述被选取的芯片选取引脚的上述多个从装置的一个。

6.在一些实施例中,上述芯片选取模式选取电路更耦接一静态芯片选取引脚电路,且上述芯片选取模式选取电路根据上述第一选取信号,决定选取上述静态芯片选取引脚电路或上述动态芯片选取引脚电路,来选取上述芯片选取引脚。

7.在一些实施例中,上述静态芯片选取引脚电路、上述动态芯片选取引脚电路和上述多个芯片选取引脚包含在一通用型的输入输出接口中。

8.在一些实施例中,上述主装置更包括一控制接口,且上述芯片选取控制电路根据来自上述控制接口输出的一控制信号,产生上述第一选取信号。

9.在一些实施例中,上述主装置更包括一存储器接口,且上述芯片选取控制电路根据来自上述存储器接口产生的一判断结果,产生上述第二选取信号。

10.在一些实施例中,上述主装置更包括一逻辑电路,以输出要传输给对应上述被选取的芯片选取引脚的上述从装置的数据。

11.根据本发明的一实施例提供了一种数据传输方法。数据传输方法适用一串列周边

接口(spi)系统。数据传输方法的步骤包括:借由上述串列周边接口系统的一主装置的一芯片选取控制电路,产生一第一选取信号;借由上述主装置的一芯片选取模式选取电路,根据上述第一选取信号决定是否选取上述串列周边接口系统的一动态芯片选取引脚电路,来选取一芯片选取引脚;当上述动态芯片选取引脚电路被选取时,借由上述芯片选取控制电路传送一第二选取信号至上述动态芯片选取引脚电路,以从上述串列周边接口系统的多个芯片选取引脚选取上述芯片选取引脚;以及将数据传送给对应上述被选取的芯片选取引脚的上述串列周边接口系统的多个从装置的一个。

12.根据本发明提出的串列周边接口系统和数据传输方法,可借由一动态芯片选取引脚电路来选取需要进行通讯的从装置所对应的静态芯片选取引脚。因此,在本发明提出的串列周边接口系统中,主装置仅需要配置一组主埠即可达成切换不同静态芯片选取引脚的目的。因此,本发明提出的串列周边接口系统和数据传输方法可避免引脚的浪费。

13.关于本发明其他附加的特征与优点,本领域技术人员,在不脱离本发明的精神和范围内,当可根据本案实施方法中所揭露的串列周边接口系统和数据传输方法,做些许的更动与润饰而得到。

附图说明

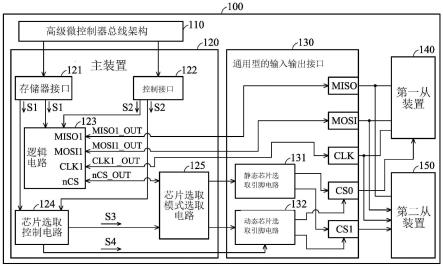

14.图1是显示根据本发明的一实施例所述的一串列周边接口系统100的方块图。

15.图2是根据本发明的一实施例所述的数据传输方法的流程图。

16.附图标记

17.100:串列周边接口系统

18.110:高级微控制器总线架构

19.120:主装置

20.121:存储器接口

21.122:控制接口

22.123:逻辑电路

23.124:芯片选取控制电路

24.125:芯片选取模式选取电路

25.130:通用型的输入输出接口

26.131:静态芯片选取引脚电路

27.132:动态芯片选取引脚电路

28.140:第一从装置

29.150:第二从装置

30.miso:主装置输入从装置输出引脚

31.miso1:主装置输入从装置输出埠

32.mosi:主装置输出从装置输入引脚

33.mosi1:主装置输出从装置输入埠

34.clk:时脉引脚

35.clk1:时脉输出埠

36.cs0:第一芯片选取引脚

37.cs1:第二芯片选取引脚

38.ncs:芯片选取埠

39.s1:判断结果

40.s2:控制信号

41.s3:第一选取信号

42.s4:第二选取信号

43.s210~s250:步骤

具体实施方式

44.本章节所叙述的是实施本发明的较佳方式,目的在于说明本发明的精神而非用以限定本发明的保护范围,本发明的保护范围须参考所附的权利要求限定范围。

45.图1是显示根据本发明的一实施例所述的一串列周边接口(serial peripheralinterface,spi)系统100的方块图。如图1所示,串列周边接口系统100可包括一高级微控制器总线架构(advanced microcontroller bus architecture,amba)(例如:一高级高性能总线(advanced high-performance bus,ahb))110、一主装置(masterdevice)120、一通用型的输入输出(general-purpose input/output,gpio)接口130、一第一从装置(slave device)140以及一第二从装置150。注意地是,在图1中所示的方块图,仅是为了方便说明本发明的实施例,但本发明并不以图1为限。串列周边接口系统100中亦可包含其他元件。

46.根据本发明一实施例,如图1所示,主装置120可至少包括一存储器接口(memoryinterface)121、一控制接口(control interface)122、一逻辑电路123、一芯片选取(chipselect,cs)控制电路124,以及一芯片选取(cs)模式选取电路125。注意地是,在图1中所示的主装置120,仅是为了方便说明本发明的实施例,但本发明并不以图1为限。主装置120中亦可包含其他元件。

47.此外,根据本发明一实施例,如图1所示,通用型的输入输出130可包括一主装置输入从装置输出引脚miso(master input/slave output)、一主装置输出从装置输入引脚mosi(master output/slave input)、一时脉引脚clk、一第一芯片选取引脚cs0、一第二芯片选取引脚cs1、一静态芯片选取引脚电路131和一动态芯片选取引脚电路132。此外,根据本发明一实施例,如图1所示,第一芯片选取引脚cs0会连接至第一从装置140,且第二芯片选取引脚cs1会连接至第二从装置150。

48.根据本发明的实施例,存储器接口121可判断高级微控制器总线架构110所存取的存储器位址是对应到哪一从装置,以产生一判断结果s1。举例来说,若第一从装置140所对应的存储器位址范围是0x1000~0x1ffff,且第二从装置150所对应的存储器位址范围是0x2000~0x2ffff,当存储器接口121判断高级微控制器总线架构110所存取的存储器位址是在存储器位址范围0x1000~0x1ffff中,存储器接口121就会判断高级微控制器总线架构110所存取的存储器位址是对应到第一从装置140。注意地是,上述例子仅是用以说明本发明的实施例,但本发明不以此为限。存储器接口121会将判断结果s1传送给逻辑电路123和芯片选取控制电路124。

49.根据本发明的实施例,控制接口122可根据来自高级微控制器总线架构110的指

令,产生一控制信号s2,并将控制信号s2传送给逻辑电路123和芯片选取控制电路124。逻辑电路123和芯片选取控制电路124可根据控制信号s2得知是要使用静态芯片选取引脚功能或是动态芯片选取引脚功能(即得知要选取静态芯片选取引脚电路131或动态芯片选取引脚电路132),来选取芯片选取引脚。

50.根据本发明的实施例,逻辑电路123可视为一组串列周边接口主埠(master port)。根据本发明的实施例,逻辑电路123可包括一主装置输入从装置输出埠miso1、一主装置输出从装置输入埠mosi1、一时脉输出埠clk1和一芯片选取埠ncs。逻辑电路123可借由主装置输入从装置输出埠miso1、主装置输出从装置输入埠mosi1、时脉输出埠clk1和芯片选取埠ncs传送数据或信号给被选取的从装置。如图1所示,主装置输入从装置输出埠miso1会连接到通用型的输入输出130的主装置输入从装置输出引脚miso,以传送信号miso_out至主装置输入从装置输出引脚miso。主装置输出从装置输入埠mosi1会连接到通用型的输入输出130的主装置输出从装置输入引脚mosi,以传送信号mosi_out至主装置输出从装置输入引脚mosi。时脉输出埠clk1会连接到通用型的输入输出130的时脉引脚clk,以传送时脉信号clk_out至时脉引脚clk。芯片选取埠ncs会连接到芯片选取模式选取电路125,以传送信号ncs_out至芯片选取模式选取电路125。

51.根据本发明的实施例,芯片选取控制电路124可根据接收到控制信号s2,得知要使用静态芯片选取引脚功能或是动态芯片选取引脚功能(即得知要选取静态芯片选取引脚电路131或动态芯片选取引脚电路132),来选取芯片选取引脚,并据此产生一第一选取信号s3。接着,芯片选取控制电路124会将第一选取信号s3传送给芯片选取模式选取电路125。芯片选取模式选取电路125可根据第一选取信号s3,决定使用静态芯片选取引脚电路131或动态芯片选取引脚电路132,来选取芯片选取引脚和传送信号ncs_out。

52.当静态芯片选取引脚电路131被选取时,静态芯片选取引脚电路131会根据通用型的输入输出130的一暂存器(图未显示)的数值决定启动第一芯片选取引脚cs0或第二芯片选取引脚cs1。

53.当动态芯片选取引脚电路132被选取时,动态芯片选取引脚电路132可根据来自芯片选取控制电路124之第二选取信号s4,决定启动第一芯片选取引脚cs0或第二芯片选取引脚cs1。底下将会有更详细的叙述。

54.根据本发明的一实施例,当芯片选取控制电路124根据控制信号s2得知要使用动态芯片选取引脚功能(即动态芯片选取引脚电路132被选取)来选取芯片选取引脚时,芯片选取控制电路124会根据判断结果s1,得知要从存取哪一从装置,以决定要启动第一芯片选取引脚cs0或第二芯片选取引脚cs1,并据此产生一第二选取信号s4。接着,芯片选取控制电路124会将第二选取信号s4传送给动态芯片选取引脚电路132。动态芯片选取引脚电路132即可根据第二选取信号s4,决定启动第一芯片选取引脚cs0或第二芯片选取引脚cs1,以将信号ncs_out所包含的数据传送给第一芯片选取引脚cs0或第二芯片选取引脚cs1。也就是说,动态芯片选取引脚电路132可根据第二选取信号s4,动态选取第一芯片选取引脚cs0或第二芯片选取引脚cs1。

55.当第一芯片选取引脚cs0被选取时,主装置120即可和第一从装置140进行通讯,以及当第二芯片选取引脚cs1被选取时,主装置120即可和第二从装置150进行通讯。

56.图2是根据本发明的一实施例所述的一数据传输方法的流程图。数据传输方法可

适用串列周边接口(serial peripheral interface,spi)系统100。如图2所示,在步骤s210,借由串列周边接口系统100的主装置的一芯片选取控制电路,产生一第一选取信号。

57.在步骤s220,借由串列周边接口系统100的主装置的一芯片选取模式选取电路,根据第一选取信号决定是否选取串列周边接口系统的一动态芯片选取引脚电路或一静态芯片选取引脚电路,来选取一芯片选取引脚。

58.当动态芯片选取引脚电路被选取时,进行步骤s230。在步骤s230,借由芯片选取控制电路传送一第二选取信号至动态芯片选取引脚电路,以根据第二选取信号从串列周边接口系统100的多个芯片选取引脚选取上述芯片选取引脚。在步骤s250,借由串列周边接口系统100的一逻辑电路将要输出给对应被选取的芯片选取引脚的从装置的数据给该从装置。在此实施例中,静态芯片选取引脚电路、动态芯片选取引脚电路和多个芯片选取引脚可包含在串列周边接口系统100的一通用型的输入输出接口中。

59.当静态芯片选取引脚电路被选取时,进行步骤s240。在步骤s240,借由串列周边接口系统100的通用型的输入输出接口从串列周边接口系统100的多个芯片选取引脚选取一芯片选取引脚。接着,进行步骤s250。

60.根据本发明的实施例,数据传输方法更包括,借由串列周边接口系统100的芯片选取控制电路根据来自串列周边接口系统100的一控制接口输出的一控制信号,产生第一选取信号。

61.根据本发明的实施例,数据传输方法更包括,借由串列周边接口系统100的芯片选取控制电路根据来自串列周边接口系统100的一存储器接口产生的一判断结果,产生第二选取信号。存储器接口可借由判断串列周边接口系统100的一高级微控制器总线架构所存取的存储器位址是对应到哪一从装置,以产生一判断结果s1。

62.根据本发明提出的串列周边接口系统和数据传输方法,可借由一动态芯片选取引脚电路来选取需要进行通讯的从装置所对应的静态芯片选取引脚。因此,在本发明提出的串列周边接口系统中,主装置仅需要配置一组主埠即可达成切换不同静态芯片选取引脚的目的。因此,本发明提出的串列周边接口系统和数据传输方法可避免引脚的浪费。

63.本说明书中以及申请专利范围中的序号,例如“第一”、“第二”等等,仅是为了方便说明,彼此之间并没有顺序上的先后关系。

64.本发明的说明书所揭露的方法和演算法的步骤,可直接通过执行一处理器直接应用在硬件以及软件模组或两者的结合上。一软件模组(包括执行指令和相关数据)和其它数据可储存在数据存储器中,像是随机存取存储器(ram)、快闪存储器(flashmemory)、只读存储器(rom)、可抹除可规化只读存储器(eprom)、电子可抹除可规划只读存储器(eeprom)、暂存器、硬盘、可携式硬盘、只读光盘存储器(cd-rom)、dvd或在此领域已知技术中任何其它电脑可读取的储存媒体格式。一储存媒体可耦接至一机器装置,举例来说,像是电脑或者处理器(为了说明的方便,在本说明书以处理器来表示),上述处理器可用来读取信息(像是程序代码),以及写入信息至储存媒体。一储存媒体可整合一处理器。一特殊应用集成电路(asic)包括处理器和储存媒体。一用户设备则包括一特殊应用集成电路。换句话说,处理器和储存媒体以不直接连接用户设备的方式,包含于用户设备中。此外,在一些实施例中,任何适合电脑程序的产品包括可读取的储存媒体,其中可读取的储存媒体包括和一或多个所揭露实施例相关的程序代码。在一些实施例中,电脑程序的产品可包括封装材料。

65.以上段落使用多种层面描述。显然的,本文的教示可以多种方式实现,而在范例中揭露的任何特定架构或功能仅为一代表性的状况。根据本文的教示,任何本领域技术人员应理解在本文揭露的各层面可独立实际应用或两种以上之层面可以合并实际应用。

66.虽然本揭露已以实施例揭露如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本揭露精神和范围内,当可作些许的更动与润饰,因此发明的保护范围须参考所附的权利要求限定范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1