一种基于反高斯偏置电路电流反馈电压驱动器的LDO

一种基于反高斯偏置电路电流反馈电压驱动器的ldo

技术领域

1.本发明涉及电流反馈电压驱动器技术领域,具体涉及一种基于反高斯偏置电路的电流反馈电压驱动器。

背景技术:

2.近年来由于各种便携式电子类产品的普及,电池供电的电源管理类芯片需求量也不断增大,对电源管理类芯片性能的要求也不断提高。当负载从轻载在1ns瞬态变化重载或者从重载瞬间变化轻载时,恢复时间小于5us,且静态电流小于10ua要求下,采用传统的设计方法难以实现。传统方法要求恢复时间快的情况,那么便需要大的静态电流,消耗巨大功耗,难以均衡。

技术实现要素:

3.实用新型目的:本实用新型涉及一种基于反高斯偏置电路电流反馈电压驱动器的线性低压降稳压器ldo,其目的在于解决传统的设计方法难以实现超快速负载瞬态响应的低功耗结构。

4.技术方案:

5.一种基于反高斯偏置电流反馈电压驱动器的ldo,包括误差放大器模块、反高斯偏置电路、电流反馈电压驱动器、供电电源电压vdd、系统接地端vss、外部偏置电路输入端vbp、外部带隙基准电路输入端口vr和ifbufv输出端口vout。

6.供电电源电压vdd、系统接地端vss、外部偏置电路输入端vbp、外部带隙基准电路输入端口vr、ifbufv输出端口vout作为误差放大器模块的输入端口,误差放大器模块的ea输出端口vset连接电流反馈电压驱动器;供电电源电压vdd、系统接地端vss、外部带隙基准电路输入端口vr、ifbufv输出端口vout作为反高斯偏置电路的输入端口,反高斯偏置电路的输出端第十四晶体管m13输入至电流反馈电压驱动器。

7.进一步的,误差放大器模块包括第一晶体管m0、第二晶体管m1、第三晶体管m2、第四晶体管m3、第五晶体管m4、第六晶体管m5、第七晶体管m6、第八晶体管m7和第九晶体管m8,

8.第一晶体管m0的源级接供电电源电压vdd、第一晶体管m0的栅极为外部偏置电路输入端vbp,第一晶体管m0的漏极连接第二晶体管m1的源极和第三晶体管m2的源极,第二晶体管m1的栅极连接ifbufv输出端口vout,第三晶体管m2的栅极连接外部带隙基准电路输入端口vr和反高斯偏置电路的第十七晶体管m16,第二晶体管m1的漏极分别接第四晶体管m3的漏极、第四晶体管m3的栅极和第六晶体管m5的栅极,第四晶体管m3的源极接系统接地端vss;第四晶体管m3与第六晶体管m5构成电流镜,第四晶体管m3的栅极接第六晶体管m5的栅极,第六晶体管m5的源极接系统接地端vss,第六晶体管m5的漏极接第八晶体管m7的栅极和第八晶体管m7漏极;第三晶体管m2的漏极接第五晶体管m4的漏极、第五晶体管m4的栅极和第七晶体管m6的栅极,第七晶体管m6的源极接系统接地端vss,第七晶体管m6的漏极接第九晶体管m8的漏极,并引出ea输出端口vset,ea输出端口vset接电流反馈电压驱动器,并串联

第一电容c1后接系统接地端vss,第八晶体管m7和第九晶体管m8的源极连接供电电源电压vdd。

9.进一步的,第一晶体管m0提供误差放大器所需的电流,第二晶体管m1、第三晶体管m2作为误差放大器的差分输入管为高比例w/l晶体管,以产生高的低频开环增益。

10.进一步的,反高斯偏置电路模块包括第十晶体管m9、第十一晶体管m10、第十二晶体管m11、第十三晶体管m12、第十四晶体管m13、第十五晶体管m14、第十六晶体管m15、第十七晶体管m16、第十八晶体管m17、第十九晶体管m18、第二十晶体管m19、第二十一晶体管m20、第二十二晶体管m21、第二十三晶体管m22、第二十四晶体管m23、第二十五晶体管m24、第二十六晶体管m25和第二十七晶体管m26,第十晶体管m9的源极、第十七晶体管m16的漏极、第十五晶体管m14的源极、第十一晶体管m10的源极、第十二晶体管m11的源极、第二十晶体管m19的漏极、第十三晶体管m12的源极以及第十四晶体管m13的源极均接供电电源电压vdd;第二十一晶体管m20的源极、第二十二晶体管m21的源极、第二十三晶体管m22的源极、第二十四晶体管m23的源极、第二十五晶体管m24的源极、第二十六晶体管m25的源极和第二十七晶体管m26的源极均接系统接地端vss;

11.第十晶体管m9的栅极和第十三晶体管m12的栅极连第一晶体管m0的栅极并连接外部偏置电路输入端vbp,第十晶体管m9的漏极接第二十一晶体管m20的漏极,第二十一晶体管m20以二极管方式连接,第二十一晶体管m20漏极和栅极短接, 第二十一晶体管m20栅极与第二十二晶体管m21的栅极和第二十四晶体管m23的栅极连接;第十七晶体管m16和第十九晶体管m18的栅极接第三晶体管m2的栅极并连接外部带隙基准电路输入端口vr,第十七晶体管m16的源极和第十八晶体管m17的源极短接与第二十二晶体管m21的漏极连接;第十八晶体管m17和第二十晶体管m19的栅极接ifbufv输出端口vout,第十八晶体管m17的漏极接第十五晶体管m14的漏极,第十五晶体管m14的漏极与第十五晶体管m14的栅极短接与第十六晶体管m15的栅极连接,第十六晶体管m15的源极接第十一晶体管m10的漏极,第十一晶体管m10的栅极接第十二晶体管m11的栅极,第十二晶体管m11的栅极与第十二晶体管m11的漏极短接与第十九晶体管m18的漏极连接,第十九晶体管m18的源极和第二十晶体管m19的源极短接与第二十四晶体管m23的漏极连接;第十六晶体管m15的漏极接第二十三晶体管m22的漏极,第二十三晶体管m22的漏极与第二十三晶体管m22的栅极短接与第二十五晶体管m24的栅极连接,第二十五晶体管m24的漏极与第十三晶体管m12的漏极短接与第二十六晶体管m25的漏极连接,第二十六晶体管m25的漏极与第二十六晶体管m25的栅极短接与第二十七晶体管m26的栅极连接,第二十七晶体管m26的漏极与第十四晶体管m13的漏极连接,第十四晶体管m13的漏极与第十四晶体管m13的栅极短接与电流反馈电压驱动器连接。

12.进一步的,电流反馈电压驱动器包括第二十八晶体管m27、第二十九晶体管m28、第三十晶体管m29、第三十一晶体管m30和第三十二晶体管m31,第二十八晶体管m27源极和第二十九晶体管m28的漏极接供电电源电压vdd,第三十一晶体管m30源极和第三十二晶体管m31的源极接系统接地端vss,第二十八晶体管m27的栅极接第十四晶体管m13的栅极,第二十八晶体管m27的漏极分别与第三十一晶体管m30的漏极、第二电容c2和第二十九晶体管m28的栅极连接,第三十一晶体管m30的栅极接第三十二晶体管m31的栅极,第三十二晶体管m31的栅极与第三十二晶体管m31的漏极短接与第三十晶体管m29的漏极连接,第三十晶体管m29的栅极连接ea输出端口vset,第三十晶体管m29源极与第二十九晶体管m28的源极连

接构成ifbufv输出端口vout,第二十九晶体管m28的体端接第三电容c3的一端和电阻r1的一端,第三电容c3另一端与供电电源电压vdd连接,电阻r1另一端与ifbufv输出端口vout连接,ifbufv输出端口vout分别与误差放大器模块的第二晶体管m1的栅极、反高斯动态偏置电路的第十八晶体管m17的栅极和第二十晶体管m19的栅极连接。

13.进一步的,第二十九晶体管m28为高比例w/l尺寸nmos,用于产生负载所需的大电流。

14.优点及效果

15.本实用新型对电流反馈电压驱动器进行动态偏置,使功耗最低。对于超快速负载变化,本实用新型架构由于电流反馈电压驱动器的作用,有着高瞬态响应能力。在cadence仿真软件下,采用tsmc130工艺,3.0v、tt工艺角、40℃典型工艺条件下,负载从200ua到20ma在1ns时间切换的情况下,恢复(vout)+/

‑

10%的情况下,恢复时间最快仅为0.58us,最慢时间为2.16us。

附图说明

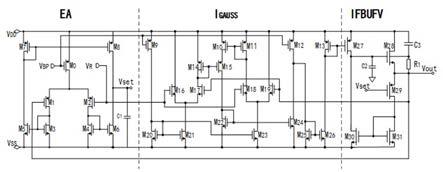

16.图1为ldo架构整体连接;

17.图2为电流反馈电压驱动器电路图;

18.图3为慢速响应工作机制;

19.图4为误差放大器内部电路图;

20.图5为快速响应工作机制;

21.图6为反高斯偏置电路(igauss)内部电路图;

22.图7为瞬态响应能力仿真波形图;

23.图8为反高斯偏置电路(igauss)仿真波形图。

具体实施方式

24.以下结合说明书附图更详细的说明本实用新型。

25.本发明提出一种基于反高斯动态偏置电流反馈电压驱动器的瞬态响应方式,用以设计具有超快速负载瞬态响应的低功耗无片外电容ldo。

26.如图1所示,ldo整体晶体管级连接。从左到右分别是误差放大器模块((error amplifer,ea))、反高斯偏置电路(igauss)及其电流反馈电压驱动器(i

‑

feedback

‑

bufferv,ifbufv)。误差放大器模块(ea)是模拟集成电路设计中的核心电路模块。芯片级最基本的运放结构主要有两种,最基本的运放结构是电流镜为有源负载的五管差分对结构,有基本结构可演进出各种性能的复杂运放。本设计采用的运放结构就是基于五管差分运放的演变而来的对称ota运放,由第一晶体管m0~第九晶体管m8构成。

27.一种基于反高斯偏置电流反馈电压驱动器的ldo,包括误差放大器模块、反高斯偏置电路、电流反馈电压驱动器三部分模块。端口信号为供电电源电压vdd、系统接地端vss、外部偏置电路输入端vbp、外部带隙基准电路输入端口vr和ifbufv输出端口vout。外部偏置电路输入端vbp为外部偏置电路提供,分别为误差放大器模块和反高斯偏置电路提供偏置电压;外部带隙基准电路输入端口vr为外部带隙基准电路提供,供给误差放大器模块和反高斯偏置电路作为参考电压。

28.供电电源电压vdd、系统接地端vss、外部偏置电路输入端vbp、外部带隙基准电路输入端口vr、ifbufv输出端口vout作为误差放大器模块的输入端口,ifbufv输出端口vout输入至图8中m1晶体管栅极提供电压;误差放大器模块的ea输出端口vset连接电流反馈电压驱动器;供电电源电压vdd、系统接地端vss、外部带隙基准电路输入端口vr、ifbufv输出端口vout作为反高斯偏置电路的输入端口,ifbufv输出端口vout输入至图8中m17、m19栅极提供电压,反高斯偏置电路的输出端m13输入至电流反馈电压驱动器。

29.误差放大器模块所在的回路,用于调整由于供电电压、温度、工艺变化而产生的误差;反高斯偏置电路用于给电流反馈电压驱动器模块动态提供偏置,以此来实现低功耗设计;电流反馈电压驱动器用于快速响应负载变化,来提高瞬态响应能力。

30.如图1和图4所示,误差放大器模块ea包括第一晶体管m0

‑ꢀ

第九晶体管m8,第一晶体管m0提供误差放大器所需的电流,第二晶体管m1、第三晶体管m2作为误差放大器的差分输入管为高比例w/l晶体管,典型参数可以为10u/1u,m=4,以产生高的低频开环增益。m3与m5、m4与m6、m7与m8分别构成电流镜的形式。

31.第一晶体管m0的源级接供电电源电压vdd、第一晶体管m0的栅极为外部偏置电路输入端vbp,由外部偏置电路提供,为误差放大器模块提供电流,第一晶体管m0的漏极连接第二晶体管m1的源极和第三晶体管m2的源极,第二晶体管m1的栅极vn连接ifbufv输出端口vout,第三晶体管m2的栅极vp接反高斯偏置电路的第十七晶体管m16并连接外部带隙基准电路输入端口vr,第四晶体管m3和第五晶体管m4以二极管的形式连接,并分别与第六晶体管m5和第七晶体管m6构成电流镜的形式。第二晶体管m1的漏极分别接第四晶体管m3的漏极、第四晶体管m3的栅极和第六晶体管m5的栅极,第四晶体管m3的源极接系统接地端vss;第四晶体管m3与第六晶体管m5构成电流镜,第四晶体管m3的栅极接第六晶体管m5的栅极,第六晶体管m5的源极接系统接地端vss,第六晶体管m5的漏极接第八晶体管m7的栅极和第八晶体管m7漏极;第三晶体管m2的漏极接第五晶体管m4的漏极、第五晶体管m4的栅极和第七晶体管m6的栅极,第七晶体管m6的源极接系统接地端vss,第七晶体管m6的漏极接第九晶体管m8的漏极,并引出ea输出端口vset,ea输出端口vset接电流反馈电压驱动器第三十晶体管m29的栅极,并串联第一电容c1后接系统接地端vss,第八晶体管m7和第九晶体管m8的源极连接供电电源电压vdd。

32.如图1和图6所示,静态功耗在集成电路设计为一个重要的衡量指标,如何降低系统的静态功耗成为重中之重。对于具有高瞬态响应能力的ldo,进行最大程度的低功耗设计,提出了反高斯动态偏置电路,用于给电流反馈电压驱动器动态提供偏置电流,以此来最大程度实现低功耗设计。反高斯动态偏置电路决定着电流反馈电压驱动器消耗电流的大小。图6为反高斯偏置电路的原理图。

33.反高斯动态偏置电路包括第十晶体管m9~第二十七晶体管m26,第十晶体管m9的源极、第十七晶体管m16的漏极、第十五晶体管m14的源极、第十一晶体管m10的源极、第十二晶体管m11的源极、第二十晶体管m19的漏极、第十三晶体管m12的源极以及第十四晶体管m13的源极均接供电电源电压vdd;第二十一晶体管m20的源极、第二十二晶体管m21的源极、第二十三晶体管m22的源极、第二十四晶体管m23的源极、第二十五晶体管m24的源极、第二十六晶体管m25的源极和第二十七晶体管m26的源极均接系统接地端vss;第十晶体管m9的栅极和第十三晶体管m12的栅极连第一晶体管m0的栅极,即外部偏置电路输入端vbp输入信

号,为该电路输入偏置电压;第十晶体管m9的漏极接第二十一晶体管m20的漏极,第二十一晶体管m20以二极管方式连接,第二十一晶体管m20漏极和栅极短接, 第二十一晶体管m20栅极与第二十二晶体管m21的栅极和第二十四晶体管m23的栅极连接;第二十一晶体管m20与第二十二晶体管m21、第二十四晶体管m23构成电流镜的形式,分别为m16与m17支路、m18与m19支路提供固定电流。第十七晶体管m16和第十九晶体管m18的栅极接第三晶体管m2的栅极vp,即外部带隙基准电路输入端口vr输入信号,为该电路的参考电压,由外部带隙基准电压源提供;第十七晶体管m16的源极和第十八晶体管m17的源极短接与第二十二晶体管m21的漏极连接;第十八晶体管m17和第二十晶体管m19的栅极接ifbufv输出端口vout,用于动态跟踪ldo系统输出。第十八晶体管m17的漏极接第十五晶体管m14的漏极,第十五晶体管m14和第十二晶体管m11以二极管的方式连接分别与第十一晶体管m10和第十六晶体管m15构成电流镜结构。第十五晶体管m14的漏极与第十五晶体管m14的栅极短接与第十六晶体管m15的栅极连接,第十六晶体管m15的源极接第十一晶体管m10的漏极,即第十一晶体管m10漏极与第十六晶体管m15源极连接构成并联结构,第十一晶体管m10的栅极接第十二晶体管m11的栅极,第十二晶体管m11的栅极与第十二晶体管m11的漏极短接与第十九晶体管m18的漏极连接,第十九晶体管m18的源极和第二十晶体管m19的源极短接与第二十四晶体管m23的漏极连接;第二十三晶体管m22以二极管的方式连接与第二十五晶体管m24构成电流镜的结构。第十六晶体管m15的漏极接第二十三晶体管m22的漏极,第二十三晶体管m22的漏极与第二十三晶体管m22的栅极短接与第二十五晶体管m24的栅极连接,第二十五晶体管m24的漏极与第十三晶体管m12的漏极短接与第二十六晶体管m25的漏极连接,第二十六晶体管m25以二极管方式连接与第二十七晶体管m26构成电流镜结构。第二十六晶体管m25的漏极与第二十六晶体管m25的栅极短接与第二十七晶体管m26的栅极连接,第二十七晶体管m26的漏极与第十四晶体管m13的漏极连接,第十四晶体管m13的漏极与第十四晶体管m13的栅极短接与电流反馈电压驱动器的第二十八晶体管m27的栅极连接,用于给电流反馈电压驱动器提供偏置电压。

34.本实用新型的反高斯动态偏置电路中第十七晶体管m16与第十九晶体管m18的栅级电压由外部带隙基准电压源提供,第十八晶体管m17与第二十晶体管m19的栅压由ldo的ifbufv输出端口vout设定,用于跟踪ldo的输出电压。那么我们将根据ldo ifbufv输出端口vout与带隙基准参考电压的误差来动态的生成电流,由第二十三晶体管m22和第二十五晶体管m24构成的电流镜的方式引出来。第二十六晶体管m25与第二十七晶体管m26、第十四晶体管m13与第二十八晶体管m27分别构成电流镜结构,进而产生偏置电流供电流反馈电压驱动器工作。

35.如图1、图3和图5所示,ldo的高瞬态响应能力主要由电流反馈电压驱动器决定。电流反馈电压驱动器,由第二十八晶体管m27~第三十一晶体管m30构成。

36.第二十八晶体管m27源极和第二十九晶体管m28的漏极接供电电源电压vdd,第三十一晶体管m30源极和第三十二晶体管m31的源极接系统接地端vss,第二十八晶体管m27的栅极接第十四晶体管m13的栅极,即第二十八晶体管m27栅极电压为输入信号vbpi由反高斯偏置电路提供。第二十八晶体管m27的漏极分别与第三十一晶体管m30的漏极、第二电容c2和第二十九晶体管m28的栅极连接,第三十一晶体管m30的栅极接第三十二晶体管m31的栅极,第三十二晶体管m31以二极管方式连接与第三十一晶体管m30构成电流镜结构。第三十

二晶体管m31的栅极与第三十二晶体管m31的漏极短接与第三十晶体管m29的漏极连接,第三十晶体管m29的栅极连接ea输出端口vset,即第三十晶体管m29的栅端为此模块的输入信号vset,由误差放大器的输出端vset提供。第三十晶体管m29源极与第二十九晶体管m28的源极连接构成ifbufv输出端口vout,第二十九晶体管m28为功率管,第二十九晶体管m28的体端采取不接地的手段,第二十九晶体管m28的体端接第三电容c3电容的一端和电阻r1的一端,第三电容c3另一端与供电电源电压vdd连接,电阻r1另一端与ifbufv输出端口vout连接,使系统静态消耗电流不随负载的变化而变化。这样做的好处是静态消耗电流不随负载的变化而变化。ifbufv输出端口vout分别与误差放大器模块ea的第二晶体管m1的栅极、反高斯动态偏置电路的第十八晶体管m17的栅极和第二十晶体管m19的栅极连接。

37.第二十九晶体管m28为大尺寸功率管,用于产生负载所需的大电流。第三十晶体管m29相当于构成了源跟随器,第三十晶体管m29栅极接ea输出端口vset输入电压,第三十晶体管m29源极接ifbufv输出端口vout输出电压,ea输出端口vset与ifbufv输出端口vout差一个常数,该常数随着pvt的变化而变化。第三十一晶体管m30与第三十二晶体管m31构成了电流镜结构。假若当负载电流增加时,流向m31管的电流减小,经过第三十一晶体管m30、第三十二晶体管m31管镜像后,第三十一晶体管m30的支路电流减小,进而驱动m28管的电压升高,使得功率管第二十九晶体管m28产生大电流提供负载;反之亦然。在设计过程当中考虑到功率管的尺寸过大,存在过大的栅源寄生电容cgs,因此引入稳定功率管栅压的第二电容c2。同时还考虑到防止ldo静态消耗电流随负载电流变化而变化,引入了第三电容c3、电阻r1来抑制此效应。对于电流反馈电压驱动器的功耗主要由图8中反高斯偏置电路提供给电流反馈电压驱动器偏置电流的大小和第三十二晶体管m31、第三十一晶体管m30的尺寸比例所决定。第三十一晶体管m30所在的支路电流主要是第二十八晶体管m27生成的漏电流。第二十六晶体管m25、第二十七晶体管m26为电流镜结构,第十四晶体管m13、第二十八晶体管m27为电流镜结构,因此可以得知电流反馈电压驱动器的前一级反高斯,因此设计了反高斯偏置电路来动态的产生该模块的偏置电流。

38.本实用新型用于解决现有ldo瞬态响应能力不够高的问题。图2中包括误差放大器、基于反高斯动态偏置的电流反馈电压驱动器。该架构工作主要由两种工作机制(慢速响应回路、快速响应回路)有机合理的配合。

39.图3电路图中加深部分为慢速响应回路。vref为参考电压。基于误差放大器(图4)的反馈回路用于跟踪供电电压、温度、工艺的变化,并为电流反馈电压驱动器提供输入电压vset。此回路对带宽要求不大,因此引入了第一电容c1来降低该回路的带宽。

40.图5电路图中加深部分为快速响应回路。该部分主要由电流反馈电压驱动器构成,其中架构图中igauss物理上代表着动态反高斯偏置电路。该回路工作机制主要为:当负载电流增加时,流向第二晶体管m1的电流减小,经过第三晶体管m2、第四晶体管m3镜像后,第四晶体管m3的支路电流减小,进而驱动第一晶体管m0的电压升高,使得功率管第一晶体管m0产生大电流提供负载;反之亦然。以此方式来构成电流负反馈进而提供功率管驱动电压。

41.对系统进行瞬态响应能力仿真测试,vdd电源电压3.0v,vr参考电压1.2v,vbp由外部偏置电路提供,在输出端vout接上200ua与20ma以1ns的切换速度周期为10us的电流源ipulse进行仿真测试,得到图7,可以看到最快恢复时间仅为0.58us,最慢恢复时间为2.16us响应迅速。

42.对反高斯偏置电路小模块进行仿真测试,vdd电源电压3.0v,第十七晶体管m16、第十九晶体管m18栅极为输入电压vr外部提供1.2v,第十晶体管m9和第十三晶体管m12栅极电压由外部偏置电路提供。对第十八晶体管m17和第二十晶体管m19的栅极电压进行直流扫描,观察第二十七晶体管m26的漏极电流,可以得到图8的效果。当系统工作在静态的时候,电流消耗最低。实现了低功耗的效果。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1