抗干扰带隙基准电路的制作方法

1.本发明涉及微电子领域的基准电路,尤其涉及一种抗干扰带隙基准电路。

背景技术:

2.在大多数微电子电路应用中精确的参考电压是必须的。在标准工艺中都是采用标准的带隙基准电路,正常情况下输入电压是不会跳动的,但在直流对直流降压转换器(dc to dc buck)应用下会因输出端的摆动而受到干扰,参考电压也因此随之摆动,为了让参考电压稳定不受干扰,设计时必须加上相当大的对地电容让参考电压稳定。

3.在标准cmos工艺中,带隙基准电路的电路设计如图1所示,电路由两个pmos管、两个nmos管、两个pnp管、一个电阻,以及输出级的1个pmos管、1个pnp管和1个电阻所组成。利用图1的带隙基准电路进行仿真试验得到图4,从图4中可以看出电源(v3a)在5v~3.3v间摆动过程中,输出电压(vdc_bg)会随电源摆动而起伏;现有技术中为了降低输出电压的起伏通常采用增加一个电阻和一个电容的技术方案,如图2和图5所示。以现今工艺持续微缩下,用增加电容面积来解决问题,电容面积需放大100倍,约占芯片面积的1/4,在实际应用过程中极大的增加了成本。

4.因此,亟待解决上述问题。

技术实现要素:

5.发明目的:本发明的目的是提供一种成本低廉且具有稳定基准电压的抗干扰带隙基准电路。

6.技术方案:为实现以上目的,本发明公开了一种抗干扰带隙基准电路,包括依次相连的用于产生固定电压并作为带隙基准电路基准电压的电源锁定电路、用于产生带隙基准电压的带隙基准电路和用于输出带隙基准电压的输出电路,所述电源锁定电路的一端与输入电源相连,一端与接地端相连,该电源锁定电路包括6个mos管、1个电阻和1个三极管。

7.其中,电源锁定电路包括第六mos管、第七mos管、第八mos管、第九mos管、第十mos管、第十一mos管、第四电阻和第四三极管,第六mos管的漏极连接于基准电压,第六mos管的栅极与带隙基准电路和输出电路相连,第六mos管的源极连接第四电阻,第四电阻的另一端连接于第四三极管的第一极,第四三极管的栅极和第二极都连接至接地端,第八mos管和第九mos管的源极连接于输入电源,第八mos管的漏极连接于基准电压,第八mos管的栅极和第九mos管的栅极和漏极相连,第十一mos管的漏极连接于第九mos管的漏极,第十一mos管的栅极连接于第十mos管的栅极,第十一mos管的源极连接至接地端,第七mos管的源极连接于基准电压,第七mos管的栅极与带隙基准电路和输出电路相连,第七mos管的漏极连接于第十mos管的漏极,第十mos管的漏极与栅极相连,第十mos管的源极连接至接地端。

8.优选的,第六mos管、十mos管和第十一mos管为nmos管,第七mos管、第八mos管和第九mos管为pmos管。

9.再者,带隙基准电路包括第二mos管、第三mos管、第四mos管、第五mos管,第二三极

管、第三三极管和第一电阻,第二mos管和第三mos管的源极连接于基准电压,第二mos管、第三mos管、第六mos管和第七mos管的栅极相连,第三mos管的漏极与栅极相连,第二mos管的漏极连接至第四mos管的漏极,第三mos管的漏极连接至第五mos管的漏极,第四mos管和第五mos管的栅极相连,第四mos管的漏极与栅极相连,第五mos管的源极连接第一电阻,再连接于第三三极管的第一极,第四mos管的源极连接第二三极管的第一极,第二三极管和第三三极管的栅极和第二极都连接至接地端。

10.进一步,第二mos管和第三mos管为pmos管,第四mos管和第五mos管为nmos管。

11.优选的,输出电路包括第一mos管、第一三极管、第二电阻、第三电阻和第一电容,第一mos管的源极连接于基准电压,第一mos管的栅极与第二mos管、第三mos管、第六mos管和第七mos管的栅极相连,第一mos管的漏极连接于第二电阻的一端,第二电阻的另一端连接于第一三极管的第一极,第一三极管的栅极和第二极都连接至接地端,第三电阻和第一电容连接,第三电阻的另一端连接于第一mos管的漏极,第一电容的另一端连接于接地端,第三电阻与第一电容的连接点为输出端。

12.再者,第一mos管为pmos管。

13.有益效果:与现有技术相比,本发明具有以下显着优点:

14.(1)、本发明在版图上电容面积缩小99%,利用mos管和三极管特性提供带隙基准电路稳定输入电源,几乎不增加成本的情况下解决输入电压摆动对参考电压的干扰;即在带隙基准电路前端加入电源锁定电路,利用组件特性将基准电压锁定在特定电压作为带隙基准电路电源,进而让带隙基准电路摆脱输入端摆动干扰;

15.(2)、本发明电源锁定电路由六个mos管、一个电阻和一个三极管组成,架构简单又能有效降低版图面积,在dc to dc的芯片设计上提供一个有效且可靠的参考电压。

附图说明

16.图1为现有带隙基准电路示意图;

17.图2为现有带隙基准电路输出加挂电阻和电容示意图;

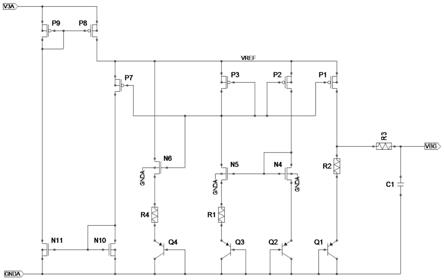

18.图3为本发明的电路示意图;

19.图4为图1的电路时序仿真图;

20.图5为图2的电路时序仿真图;

21.图6为图3电路时序仿真图。

22.图7为现有带隙基准电路输入加挂常见电压锁定电路示意图;

23.图8为图7电路时序仿真图。

具体实施方式

24.下面结合附图对本发明的技术方案作进一步说明。

25.如图3所示,本发明一种抗干扰带隙基准电路包括依次相连的电源锁定电路、带隙基准电路和输出电路,电源锁定电路的一端与输入电源相连,一端与接地端相连。

26.电源锁定电路用于产生固定电压并作为带隙基准电路基准电压,电源锁定电路包括第六mos管n6、第七mos管p7、第八mos管p8、第九mos管p9、第十mos管n10、第十一mos管n11、第四电阻r4和第四三极管q4。带隙基准电路用于产生带隙基准电压,带隙基准电路包

括第二mos管p2、第三mos管p3、第四mos管n4、第五mos管n5,第二三极管q2、第三三极管q3和第一电阻r1。输出电路用于输出带隙基准电压,输出电路包括第一mos管p1、第一三极管q1、第二电阻r2、第三电阻r3和第一电容c1。电源锁定电路与带隙基准电路相连用于向带隙基准电路提供稳定电压和电流,带隙基准电路用于产生带隙基准电压,透过输出电路输出。本发明的重点电源锁定电路原理则是,第七mos管p7、第八mos管p8、第九mos管p9、第十mos管n10和第十一mos管n11利用电流镜原理提供稳定电流源;而第四三极管q4的第一级与栅极间的固定电压加上固定电流流经第四电阻r4与第六mos管n6导通电压产生固定电压将基准电压vref锁定,在此架构下就可以摆脱输入电源v3a摆动所产生的干扰。

27.本发明中第六mos管n6的漏极连接于基准电压vref,第六mos管n6的栅极与第一mos管p1、第二mos管p2和第三mos管p3的栅极相连,第六mos管n6的源极连接第四电阻r4,第四电阻r4的另一端连接于第四三极管q4的第一极,第四三极管q4的栅极和第二极都连接至接地端gnda,第八mos管p8和第九mos管p9的源极连接于输入电源v3a,第八mos管p8的漏极连接于基准电压vref,第八mos管p8的栅极和第九mos管p9的栅极和漏极相连,第十一mos管n11的漏极连接于第九mos管p9的漏极,第十一mos管n11的栅极连接于第十mos管n10的栅极,第十一mos管n11的源极连接至接地端gnda,第七mos管p7的源极连接于基准电压vref,第七mos管p7的栅极与第一mos管p1、第二mos管p2和第三mos管p3的栅极相连,第七mos管p7的漏极连接于第十mos管n10的漏极,第十mos管n10的漏极与栅极相连,第十mos管n10的源极连接至接地端gnda。

28.第二mos管p2和第三mos管p3的源极连接于基准电压vref,第二mos管p2、第三mos管p3、第六mos管n6和第七mos管p7的栅极相连,第三mos管p3的漏极与栅极相连,第二mos管p2的漏极连接至第四mos管n4的漏极,第三mos管p3的漏极连接至第五mos管n5的漏极,第四mos管n4和第五mos管n5的栅极相连,第四mos管n4的漏极与栅极相连,第五mos管n5的源极连接第一电阻(r1),再连接于第三三极管q3的第一极,第四mos管n4的源极连接第二三极管q2的第一极,第二三极管q2和第三三极管q3的栅极和第二极都连接至接地端gnda。

29.第一mos管p1的源极连接于基准电压vref,第一mos管p1的栅极与第二mos管p2、第三mos管p3、第六mos管n6和第七mos管p7的栅极相连,第一mos管p1的漏极连接于第二电阻r2的一端,第二电阻r2的另一端连接于第一三极管q1的第一极,第一三极管q1的栅极和第二极都连接至接地端gnda,第三电阻r3和第一电容c1连接,第三电阻r3的另一端连接于第一mos管p1的漏极,第一电容c1的另一端连接于接地端gnda,第三电阻r3与第一电容c1的连接点为输出端vbg,输出端vbg输出电压vdc_bg。

30.本发明中第一mos管p1、第二mos管p2、第三mos管p3、第七mos管p7、第八mos管p8和第九mos管p9为pmos管。第四mos管n4、第五mos管n5、第六mos管n6、十mos管n10和第十一mos管n11为nmos管。

31.仿真时将输入电源v3a做3.3v至5v间摆动,图4中的输出电压vdc_bg出现两阶段电压,输入3.3v时为1.214,输入5v时为1.221,还有明显的突波1.209v至1.226v;图5中的vdc_bg还是有两阶段电压,但经过大电容c1吸收突波后vdc_bg在输入摆动时已无突波;图6中的vdc_bg除了消除了两阶段电压,还将突波抑制在0.001v。从图4、图5和图6的比对可以明显看到本发明在输入端大幅度摆动的条件下,可以将vdc_bg保持在固定电压,由此结果来说,除了可以应用的dc to dc buck产品外,也能用于各类需要稳定参考电压的产品上,例如精

密的比较器。

32.图7的左半边为常见电压锁定电路,由第四电阻r4、第六mos管n6、第七mos管n7、第八mos管n8、第九mos管n9所组成。串接第七mos管n7、第八mos管n8及第九mos管n9,利用mos管启动电压迭加与电阻调整流通电流将第六mos管n6的栅极电压锁定,进而提供稳定的vref。

33.图8则是比较图1中现有带隙基准电路、图3中本发明的电路与图7中现有带隙基准电路输入加挂常见电压锁定电路仿真结果,最下方的波形为现有带隙基准电路输入加挂常见电压锁定电路的结果,相较现有带隙基准电路也能消除vdc_bg两阶段电压,但还是有0.008v的突波;0.008v的突波使用在精密的比较器上会造成误判;而本发明可以消除了两阶段电压,还将突波抑制在0.001v。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1