用于记载和记录错误处理信息的方法和系统与流程

用于记载和记录错误处理信息的方法和系统

背景技术:

1.在现有系统中,外围部件互连快速(pcie)部件记载与未完成的pcie事务相关联的详细的错误处理信息。使用相应的错误记载电路“以硬件形式”记载错误处理信息,所述错误处理信息可以包括数据包报头或数据包本身,诸如事务层数据包(tlp)报头、tlp前缀和实现特定的元数据。随着pcie链路带宽的增加,有更多未完成的pcie事务,从而导致pcie报头的数量变多(例如,因为信息在pcie规范/实现的每一代中被添加到报头),并且随着更多pcie端口变得可用,错误处理信息的数量增加。这导致需要用于错误处理信息存储电路的更多的半导体布局区域,以及要求在已经在半导体布局区域和电力消耗方面都受到限制的电路中消耗更多的电力。

附图说明

2.可从结合附图以举例的方式给出的以下描述中获得更详细的理解,在附图中:

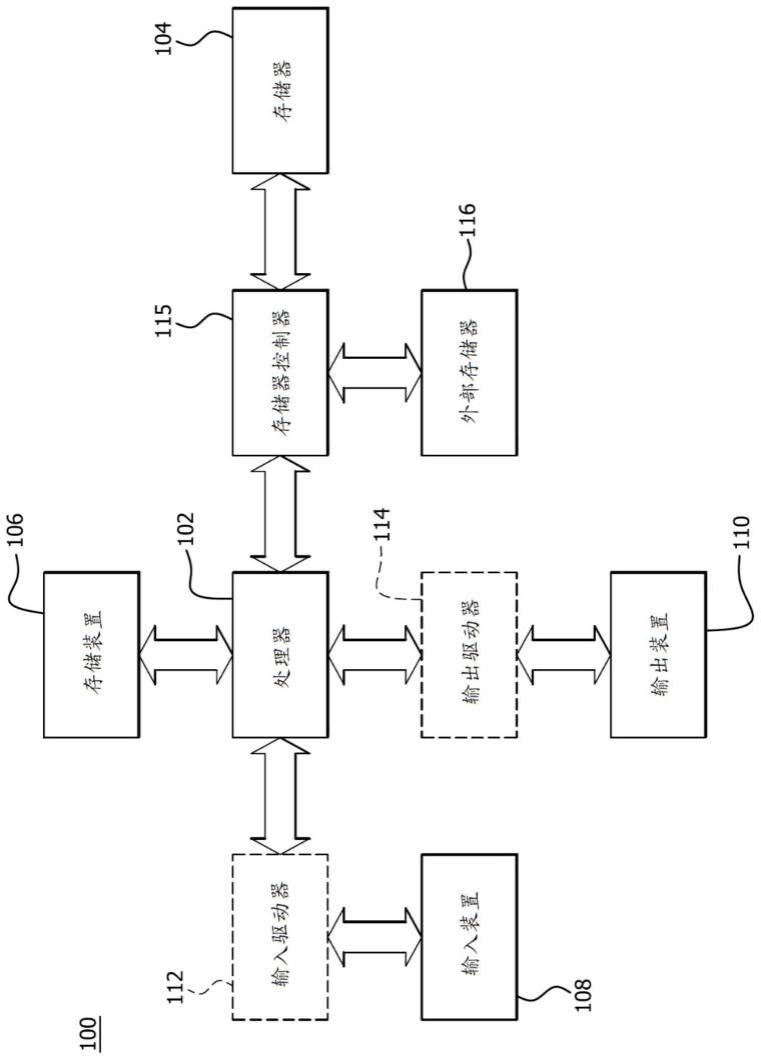

3.图1是可以实现本公开的一个或多个特征的示例性装置的框图;

4.图2是可以实现本公开的一个或多个特征的fifo的框图;以及

5.图3是记载和记录错误处理信息的示例性方法的流程图。

具体实施方式

6.尽管所述方法和系统下面得到了更详细的扩展,但是本文简要地描述了用于记载和记录错误处理信息的方法和系统。

7.记载和记录错误处理信息包括基于事务的老化(或其他特性),以不同的分辨率或复杂程度维护事务的错误处理信息。例如,一些特性可以包括事务是已发布还是未发布、流量类别或事务是否在虚拟通道上。

8.通常,最初会为活动的/进行中的事务保留完整或典型的错误处理信息,随着活动的/进行中的事务老化(可能对于某些事务子集),错误处理信息在分辨率或复杂性方面会逐渐/逐步降低。例如,可以将对识别错误不太重要或可能具有决定性作用的错误处理信息保持在较新事务的完整的错误处理信息中,但最终将其丢弃,以在事务老化时降低错误处理信息的复杂性/分辨率。

9.如果所有事务都正确执行,则不一定需要错误信息,但是需要记录错误以了解事务未正确执行的原因。例如,如果请求的地址已损坏,则在未正确执行事务时应记录该请求。

10.用于在计算机系统中记载和记录错误的方法包括读取关于事务的第一错误处理信息。将第一错误处理信息存储在第一部件中,并且基于存储在第一部件中的条件,从第一部件中删除最旧的错误信息。

11.用于记载和记录错误处理信息的计算机系统包括存储器以及与存储器和端点部件可操作地耦接并且通信的处理器。处理器被配置为读取关于事务的第一错误处理信息,将第一错误处理信息存储在第一部件中,并且基于存储在第一部件中的条件,从第一部件

中删除最旧的错误处理信息。

12.一种用于在计算机系统中记载和记录错误处理信息的非暂时性计算机可读介质,所述非暂时性计算机可读介质具有记载在其上的指令,所述指令在由处理器执行时使处理器执行操作。操作包括读取关于事务的第一错误处理信息。将第一错误处理信息存储在第一部件中,并且基于存储在第一部件中的条件,从第一部件中删除最旧的错误信息。

13.图1是可以实现本公开的一个或多个特征的示例性装置100的框图。装置100可包括例如计算机、服务器、游戏装置、手持式装置、机顶盒、电视机、移动电话或平板计算机。装置100包括处理器102、存储器104、存储装置106、一个或多个输入装置108以及一个或多个输出装置110。装置100还可任选地包括输入驱动器112和输出驱动器114。另外,装置100包括与处理器102和存储器104通信并且还可以与外部存储器116通信的存储器控制器115。在一些实施例方案中,存储器控制器115将被包括在处理器102内。应理解,装置100可包括图1中未示出的另外的部件。

14.在各种替代方案中,处理器102包括中央处理单元(cpu)、图形处理单元(gpu)、位于同一管芯上的cpu和gpu、或者一个或多个处理器核,其中每个处理器核可能是cpu或gpu。在各种替代方案中,存储器104与处理器102位于相同的管芯上,或者与处理器102分开定位。存储器104包括易失性或非易失性存储器,例如随机存取存储器(ram)、动态ram或高速缓存。

15.存储装置106包括固定式或可移除存储装置,例如硬盘驱动器、固态驱动器、光盘或闪存驱动器。输入装置108包括但不限于键盘、小键盘、触摸屏、触摸板、检测器、传声器、加速计、陀螺仪、生物特征扫描仪或网络连接(例如,用于传输和/或接收无线ieee 802信号的无线局域网卡)。输出装置110包括但不限于显示器、扬声器、打印机、触觉反馈装置、一个或多个灯、天线或网络连接(例如,用于传输和/或接收无线ieee 802信号的无线局域网卡)。

16.输入驱动器112与处理器102和输入装置108通信,并且容许处理器102接收来自输入装置108的输入。输出驱动器114与处理器102和输出装置110通信,并且容许处理器102将输出发送到输出装置110。应注意,输入驱动器112和输出驱动器114为任选部件,并且装置100在不存在输入驱动器112和输出驱动器114的情况下将以相同方式操作。另外,元件108、110、112和114可以被包括在单个i/o装置/部件中。

17.外部存储器116可以类似于存储器104,并且可以以片外存储器的形式驻留。另外,外部存储器可以是驻留在服务器中的存储器,其中存储器控制器115通过网络接口通信以访问存储器116。

18.图2是可以实现本公开的一个或多个特征的先进先出(fifo)系统200的框图。fifo系统200包括多个fifo 210(指定的2100、2101、2102、...、210n)。尽管下面描述了描述所述方法的更多细节,但是在诸如读取/写入请求之类的pcie事务期间,信息被推入第一存储fifo2110中。当其他事务发生时,信息被推入后续fifo 211中。

19.当所有的fifo 211已满,并且当其他事务发生时,最旧的信息被推出fifo 211n以便在fifo系统210中腾出另外的空间。另外,当事务完成时,无论它是否有错误,无论信息驻留在哪里或哪个fifo211中,都从fifo系统210中删除与完成的事务匹配的存储元件。

20.在一个实施方案中,上述的fifo系统200是可折叠fifo系统,其中每个较新的元件

在fifo 211中向前移位,而较旧的元件被推向删除。另外,fifo系统200可以驻留在系统100中的每个i/o装置中。也就是说,它可以驻留在连接到每个i/o装置的处理器pcie根端口内。

21.图3是记载和记录错误的示例性方法300的流程图。在步骤310中,接收pcie事务。所述事务可以来自连接到系统100的一个或多个pcie部件装置。

22.在步骤320中,将关于事务的错误信息存储在fifo装置210中。通常,最初会为活动的/进行中的事务保留完整或典型的错误处理信息,随着活动的/进行中的事务老化(可能对于某些事务子集),错误处理信息在分辨率或复杂性方面会逐渐且逐步降低。例如,对识别错误不太重要或可能具有决定性作用的错误处理信息可以包括较新事务的完整错误处理信息。例如,可以完全存储请求的地址位置,或者可以存储指向地址位置的标记。

23.例如,完整的错误处理信息可以包括生成完全保真度高级错误报告(aer)报头和前缀日志所需的所有信息。较低保真度错误日志可能会省略一些信息,诸如例如地址、事务标记、属性和前缀。

24.在步骤330中,确定较旧的错误信息是否存储在fifo中。也就是说,确定是否已经将信息推入fifo的存储区域中。如果较旧的信息存储在fifo中(步骤330),则基于该fifo是否已满(步骤340),从该fifo中删除最旧的错误信息(步骤360)。

25.然后,将最新的错误信息存储在该fifo中(步骤360)。例如,第一fifo 2100可以包含用于处理错误的高分辨率错误处理信息。然后,将从该fifo删除的条目存储在第二fifo 2101中,所述第二fifo可以记载较低分辨率的错误处理信息。

26.为了实现方法300,fifo系统210中的错误信息记载电路可以包括表(或其他记录)的层次结构,其中第一表包括一组n个条目(其中n=24、32或不同数字),用于为n个最新事务(例如,最近传输的事务)存储完整的错误处理信息。表的层次结构中的第二表包括m个条目(其中m=56、128或其他数字),用于存储减少的错误处理信息。也就是说,在步骤350之后,例如,当信息被从fifo 2100中删除时,将减少的错误处理信息存储在可以驻留在fifo 2101中的第二表中。

27.例如,假设错误处理信息包括与事务相关联的报头信息,则减少的错误处理信息可以包括更少的报头字段。也就是说,它可能比完整的错误处理信息少一个或多个报头字段。层次结构中的第三表和后续表也可以包括条目集,在其中存储了越来越少的错误处理信息。

28.如上所述,上述错误处理信息可以存储在fifo 210中的存储区域中,或者所述信息可以存储在单独的位置中,其中存储在fifo 210中的指针指向存储错误处理信息的存储位置。

29.因此,错误处理信息随着各个事务的老化而在表之间流动(或被碰撞或推动)。例如,最初可以为事务记载完整或典型的错误处理信息,诸如通过在表的层次结构的第一表中记载完整或典型的错误处理信息。随着时间的流逝,事务的完整或典型信息被从第一表中删除,诸如通过变得足够旧和/或被移除以释放空间用于将较新事务的错误处理信息写入到第一表。

30.当从第一表中删除时,减少错误处理信息(例如,丢弃指定的字段、部分等),并且然后将其存储在表的层次结构中的第二表的条目中。由于表的层次结构中的第二表和较低的表存储的事务的错误处理信息较少,因此这些表的半导体布局区域可以较小,并且可以

消耗较少的电力。

31.尽管一些错误处理信息在层次结构的较低的表中被丢弃或丢失,但是可以选择被丢弃或丢失的错误处理信息,以便更可能相关的错误处理信息保留在层次结构中的较低的表中。

32.根据错误情况,可以快速检测到错误,或者可以在事务管道中进一步检测到错误。也就是说,当处理器(例如,处理器102)从i/o装置接收到一系列存储器读取事务时,其在处理存储器读取的同时记载每个事务的错误处理信息。可以快速检测到一些错误类型,诸如格式错误的事务层数据包(tlp)错误,同时可以在管道中进一步检测到其他错误(例如,由于地址转换错误而中止)。另外,其他错误或成功事务的确定要求处理器从存储器中获取数据。例如,内存故障可能会导致中止错误。

33.此外,事务发生在pcie总线之外的事务可能需要更长的时间才能检测到。在那些情况下,可能希望记录不太详细的错误信息(例如,错误信息的前64个事务)。

34.在那些情况下,错误类型和地址可能没有记录完整的报头日志,或者如上所述,较低级别的错误信息可以存储在表的层次结构中。在一个示例中,可以减少那些错误事务的报头(例如,用报头中的单个比特填充)。替代地,可以记录整个报头,最多32个字节(报头和前缀)。

35.尽管以上方法被描述为与pcie总线上的错误记录有关,但是应注意,任何端点功能和部件都可以利用以上方法。例如,可以在根端口或交换机端口中利用以上方法。也可以利用关于错误记录的其他动作。例如,动作可以包括进行ras动作,诸如例如通知系统或平台固件。

36.所提供的方法可以在通用计算机、处理器或处理器核中实现。合适的处理器例如包括通用处理器、专用处理器、常见处理器、数字信号处理器(dsp)、多个微处理器、与dsp核相关联的一个或多个微处理器、控制器、微控制器、专用集成电路(asic)、现场可编程门阵列(fpga)电路、任何其他类型的集成电路(ic)和/或状态机。可以通过以下方式制造这种处理器:使用处理后的硬件描述语言(hdl)指令的结果和其他中间数据(包括网表)(这种指令能够存储在计算机可读介质上)来配置制造过程。这种处理的结果可能是掩模,所述掩模然后在半导体制造过程中用来制造实现本公开的特征的处理器。此外,尽管在控制和配置pcie链路和端口的上下文中描述了上述方法和设备,但是可以在协商了链路宽度的任何互连协议中利用所述方法和设备。

37.本文提供的方法或流程图可以在并入非暂时性计算机可读存储介质中的计算机程序、软件或固件中实现,以便由通用计算机或处理器执行。非暂时性计算机可读存储介质的示例包括只读存储器(rom)、随机存取存储器(ram)、寄存器、高速缓存存储器、半导体存储器装置、磁性介质(诸如内部硬盘和可移除磁盘)、磁光介质以及诸如cd-rom盘和数字通用光盘(dvd)的光学介质。例如,上述方法可以在处理器102或计算机系统100中的任何其他处理器上实现。

38.*ꢀ*ꢀ*

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1