用于神经网络的推理引擎及其操作方法与流程

1.本发明是有关于实施人工神经网络的技术的改善,且特别包括特征是非理想存储器装置行为(non-ideal memory device behavior)的存储器装置及其操作方法。

背景技术:

2.人工神经网络(artificial neural network,ann)技术已成为一有效且重要的计算工具,特别是人工智能的实现。深度神经网络(deep neural network)是使用多个非线性且复杂的转换层以依次塑造(model)高级特征(high-level feature)的人工神经网络的一类型。为了训练的目的,深度神经网络通过后向传播(backpropagation)提供回馈,其负载(carry)观测的输出及预测的输出之间的差异以调整模型参数。深度神经网络随着大训练数据组(training dataset)的可用性(availability)、并行计算及分布式计算(parallel and distributed computing)的能力(power)及精密训练算法而发展。包括深度神经网络的所有种类的人工神经网络(ann)促进众多领域(domain)的主要进展,例如计算机视觉(computer vision)、语音识别(speech recognition)及自然语言处理(natural language processing)。

3.卷积神经网络(convolutional neural network,cnns)及递归神经网络(recurrent neural network,rnns)可被使用于深度神经网络的元件(component)中,或被使用作为深度神经网络的元件。卷积神经网络已特别在具有包括卷积层(convolution layer)、非线性层及池化层(pooling layer)的一架构(architecture)的影像识别(image recognition)成功。递归神经网络系被设计,以利用具有建立区块(building block)中的循环连接(cyclic connection)的输入数据的循序信息(sequential information),建立区块例如是感知器(perceptron)、长短期存储器单元与门控递归单元(gated recurrent unit)。此外,许多其他新兴的(emergent)深度神经网络已被提出而用于各种内容,例如深度时空神经网络(deep spatio-temporal neural network)、多维递归神经网络(multi-dimensional recurrent neural network)及卷积自动编码器(convolutional auto-encoder)。

4.一些应用中,一人工神经网络(ann)系统的训练系使用高速计算系统完成,此高速计算系统系使用分布式处理器或平行处理器(distributed or parallel processor),参数的结果组(resulting set)系被转换至一计算单元中的一存储器,本发明中系被称作一推理引擎(inference engine),系实施使用于仅进行推理的操作(inference-only operation)的人工神经网络(ann)的一训练实例(trained instance)。然而,由于编程错误(programming error)、存储器电平波动(memory level fluctuation)、噪声(noise)及其他因素,仅进行推理的机器(inference-only machine)中的存储单元的行为可以是非理想的,特别是在一些类型的非易失性存储器中。存储参数的存储单元的非理想行为可能导致应用参数的推理引擎中的计算错误。这些计算错误依序(in turn)导致人工神经网络(ann)系统中的准确度(accuracy)的损失(loss)。

5.应用于人工神经网络(ann)技术的一算术函数(arithmetical function)是一「积项和(sum-of-product)」操作,亦已知为一「乘法与累加(multiply-and-accumulate)」操作。此函数可以下方的简单形式表示:

[0006][0007]

此表示式(expression)中,每一个乘积项(product term)是一变量输入(variable input)xi及一权重wi的一乘积(product)。举例而言,权重wi是可在多个项中变化的一参数,这些项系对应于变量输入xi的参数。人工神经网络(ann)技术亦可包括其他类型的参数,例如加入至用于偏差(bias)或其他效应的多个项的常数。

[0008]

各种技术(techniques)系被发展以加速乘法与累加操作。已知为「存储器内计算(compute-in-memory,cim)」的一技术包含非易失性存储器的使用,例如电阻式存储器、浮栅存储器(floating gate memory)及相变化存储器等,以存储代表计算的参数的数据及提供代表积项和计算结果的输出。举例而言,一交叉点可变电阻式存储器阵列(cross-point reram array)可被配置在一存储器内计算架构中,转换一输入电压至电流而作为阵列中的存储单元的电导(electrical conductance)的一函数且提供使用多输入及一交叉点串行(cross-point string)的一积项和操作。举例而言,请参照lin等人于

″

performance impacts of analog reram non-ideality on neuromorphic computing

″

,ieee transactions on electron devices,vol.66,no.3,2019年3月,第1289-1295页所述,在此被并入参考,如同已被充分阐述(which is incorporated by reference as if fully set forth herein)。

[0009]

然而,由于存储单元可具有代表操作中的系数或权重的非定值电导(non-constant conductance),使用于存储器内计算系统中的非易失性存储器可以是非理想的。举例而言,可变电阻式存储器(reram)可具有多个存储单元,这些存储单元具有作为读取电压及编程电导(programmed conductance)(本发明称作一目标电导(target conductance))的两者的一函数而变化的电导(conductance)。

[0010]

提供改善利用非理想存储器以存储参数的人工神经网络(ann)系统的技术,包括在用于一存储器内计算系统的机器学习程序(machine learning procedure)期间存储所产生的参数,因此系期望的。

技术实现要素:

[0011]

一种用于一神经网络的推理引擎系被叙述,包括存储核心系数(kernel coefficient)的一存储器内计算阵列(compute-in-memory array)。存储器内计算阵列的输入系被配置以接收一箝位输入向量(clamped input vector)及产生代表箝位输入向量及核心(kernel)的一函数的一输出向量,此箝位输入向量可以是一箝位输入矩阵(clamped input matrix)的一部分。一电路系被包括,操作地(operatively)耦接于一输入向量的一来源(source),输入向量的元素具有一第一数值范围(first range ofvalue)中的数值。电路系被配置以箝位在一第二数值范围(second range 0f value)的一限度的输入向量的元素的数值,以提供箝位输入向量。第二数值范围系更窄于第一数值范围且根据存储器内计

算阵列的特性被设定。第一数值范围可被使用于使用数字计算资源(digital computation resource)的训练中,第二数值范围可被使用于使用存储器内计算阵列的推理中。

[0012]

存储器内计算阵列包括存储核心的元素的存储单元。存储单元具有多个电导,这些电导具有误差量。此误差量可以是在存储单元的输入电压的一函数,可以是一编程操作期间在目标电导的存储单元组(memory cell set)的电导的一函数,且可以是输入电压及目标电导的两者的一函数。

[0013]

推理引擎可包括数字-模拟转换器(digital-to-analog converter,dac),以转换(transduce)箝位输入向量至代表箝位输入向量的元素的模拟电压。数字-模拟转换器的模拟输出系被应用至存储器内计算阵列的输入。存储器内计算阵列可被配置,以在模拟电压的一电压范围内操作。数字-模拟转换器在推理操作期间转换箝位输入向量的元素为存储器内计算阵列的全电压范围或大部分的电压范围。于一训练操作期间,此机器可利用通过其全数值范围的以数字格式的输入向量。

[0014]

神经网络可包括多个层,包括第一层、一或多个中间层及一最终层(final layer)。存储器内计算阵列可以是一或多个中间层中的一中间层的一元件。输入向量的来源可包括一在先层(preceding layer)或多个在先层,包括多个层中的一第一层。

[0015]

一些实施例中,用作输入向量的一来源的在先层可应用一激活函数(activation function),以产生皆在推理操作中及训练操作中的输入向量。部署(deployed)于推理引擎中的电路可筘位在激活函数的输出的元素的数值。电路可结合箝位函数(clamping function)及激活函数。

[0016]

箝位输入向量的元素的数值的逻辑可耦接于一缓存器(register),此缓存器存储箝位电路(clamping circuit)的范围的可编程的极限(programmable limit)。这些可编程的极限可根据输入向量或矩阵的特性且根据利用于存储器内计算阵列中的存储器技术的特性被设定。

[0017]

本发明的实施例中,存储器内计算阵列、箝位输入向量的电路、存储箝位范围的限度的缓存器以及数字-模拟转换器可以是一单一集成电路的元件。

[0018]

一种用于操作一推理引擎的方法系被叙述,包括在一存储器内计算阵列中存储一核心的系数,且应用一箝位输入向量至存储器内计算阵列以产生代表箝位输入向量及核心(kernel)的一函数的一输出向量。通过箝位在一第二数值范围的一限度的输入向量的元素的数值以提供箝位输入向量,此方法可包括更改(modify)一输入向量,输入向量的元素具有一第一数值范围中的数值,第二数值范围系更窄于第一数值范围。

[0019]

此方法可包括,训练使用输入向量的第一数值范围的神经网络,而不需在一数字积项和引擎(digital sum-of-products engine)的中箝位。

[0020]

一种存储器装置系被叙述,包括一第一计算单元(computing unit),接收一影像信号(image signal)以产生一第一输出信号;一映像测距电路(mapping range circuit),耦接于第一计算单元且转换第一输出信号为一有限测距信号(limited range signal);及一第二计算单元,耦接于映像电路且接收有限测距信号以产生一第二输出信号;其中,有限测距信号系被一上限(upper bound)及一下限(1ower bound)所局限。

[0021]

通过阅读以下附图、详细说明以及权利要求书,可见本发明的其他方面以及优点。

附图说明

[0022]

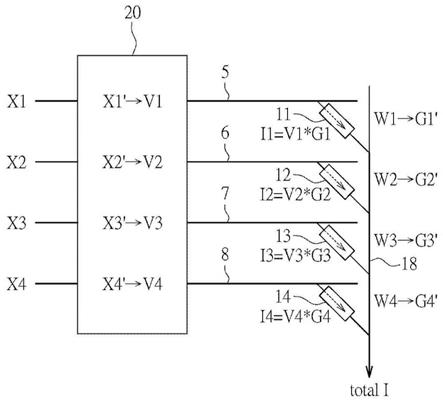

图1是本发明所述的一存储器内计算电路的简化表示法。

[0023]

图2是用于编程电导数值(program conductance value)的一范围的用于一存储器内计算电路的存储单元的读取电压对电导的图表。

[0024]

图3是绘示通过一神经网络中的一在先层的输出所提供(举例而言,例如可通过处理输入影像所产生)且结合一修正线性单元激活函数(relu activation function)的输入数值的一分布的图表。

[0025]

图4是绘示通过一存储器内计算阵列与理想电导的模拟所产生的乘法与累加数值的分布的图表。

[0026]

图5是绘示通过一存储器内计算阵列与非理想电导的模拟所产生的乘法与累加数值的分布的图表。

[0027]

图6a绘示可被定义而使用于本发明所述的一箝位电路中的一限制输入范围,关于类似图3的输入分布。

[0028]

图6b绘示箝位输入范围至使用作为一存储器内计算阵列中的输入的模拟电压范围的一映像。

[0029]

图7是绘示通过具有本发明所述的一箝位输入向量的一计算器存储器阵列(computer memory array)的仿真所产生的乘法与累加数值的分布的图表。

[0030]

图8是绘示用于输入数值的一种类型的分布的输入数值的一限制范围的简化图表。

[0031]

图9是绘示用于输入数值的另一种类型的分布的输入数值的一限制范围的简化图表。

[0032]

图10是包括具有本发明所述的一箝位电路及存储器内计算阵列的一层的一神经网络的一实施方式的方块图。

[0033]

图11是包括一层的一神经网络的一实施方式的方块图,其中箝位电路系被结合于一激活函数。

[0034]

【符号说明】

[0035]

5~8:输入

[0036]

11~14:非易失性存储单元

[0037]

18:输出导体

[0038]

20:电路

[0039]

100:存储器

[0040]

101:数字-模拟转换器

[0041]

102:阵列

[0042]

103:感测电路

[0043]

104:批正规化电路

[0044]

105:激活函数

[0045]

110:箝位电路

[0046]

111:缓存器

[0047]

112:数字-模拟转换器(dac)

[0048]

113:阵列

[0049]

114:感测电路

[0050]

115:批正规化电路

[0051]

116:激活函数

[0052]

120~121:分布

[0053]

150:方块

[0054]

200:存储器阵列

[0055]

201:感测电路

[0056]

202:批正规化电路

[0057]

204:激活函数

[0058]

205:箝位逻辑

[0059]

206:缓存器

[0060]

210:逻辑

[0061]

211:数字-模拟转换器(dac)

[0062]

212:阵列

[0063]

213:感测电路

[0064]

220~221:分布

具体实施方式

[0065]

本发明的实施例的详细说明系参照图1一图11提供。

[0066]

图1是一存储器内计算阵列的一部分的示意图。此阵列存储一核心的系数的一部分,包括用于积项和操作中的此实施例中的权重w1-w4。此阵列的此部分包括以目标电导g1

′

、g2

′

、g3

′

、g4

′

所编程的非易失性存储单元11、12、13、14,以代表权重。此阵列具有输入5、6、7、8(例如是字线),其施加模拟电压v1、v2、v3、v4至对应的非易失性存储单元11、12、13、14。模拟电压v1、v2、v3、v4代表输入向量x1、x2、x3、x4的个别元素。一输入电路20系操作地耦接于输入向量x1、x2、x3、x4的一来源(source),输入向量的元素具有一第一数值范围的数值。输入向量x1、x2、x3、x4可使用浮点编码(floating point encoding)来代表,例如16位浮点(floating point)或32位浮点表示法,包括例如是浮点算术(floating-point arithmetic)的ieee标准中所述的编码格式(encoding format)(ieee 754)。此外,输入向量可于一些实施例中以二位数字形式(binary digital form)被编码。

[0067]

输入电路20系用以于一第二数值范围的一限度(limit)箝位输入向量(或矩阵)的元素的数值,以提供通过模拟电压v1-v4所代表的一箝位输入向量(x1

′

、x2

′

、x3

′

、x4

′

),第二数值范围系更窄于第一数值范围。完全的(full)第一数值范围可被使用于训练算法,此训练算法系使用数字计算资源。因此,输入数值的箝位范围(clamped range)系更窄于训练期间所使用的范围。

[0068]

输入电路中的箝位可使用一数字电路实施以通过一数字-模拟转换器来计算箝位数值(clamped value),以提供输出电压v1-v4。此外,输入电路中的箝位可于模拟电路中计算,例如通过箝位用于输入向量的每一元素的数字-模拟转换器的输出,以提供输出电压v1-v4。

[0069]

非易失性存储单元11、12、13、14具有电导g1、g2、g3、g4,电导g1、g2、g3、g4系根据被利用的非易失性单元(nonvolatile cell)的特定实施及类型,可作为模拟输入电压(analog input voltage)的一函数、作为单元的目标电导的一函数,作为输入电压及目标电导的两者的一函数、且作为其他因素的函数,而波动(fluctuate)或变化。

[0070]

电流i1-i4系被产生于每一个存储单元中且结合于一输出导体(output conductor)18的上,输出导体18例如是一位线。多个单元的每一者中的电流系被结合以产生一总电流「total i」,以一积项和代表如下:

[0071]

v1*g1+v2*g2+v3*g3+v4*g4。

[0072]

本发明可使用存储器内计算(compute-in-memory,cim)推理引擎中的许多类型的目标存储器技术来应用,包括非易失性存储器技术。可操作为可编程电阻式存储器(programmable resistance memory)的非易失性存储单元技术的实施例包括浮栅装置(floating gate device)、电荷捕捉装置(charge trapping device)(例如sonos)、相变化存储器装置(pcm)、过渡金属氧化物电阻变化装置(transition metal oxide resistance change device)(tmo reram)、导通桥电阻变化装置(conduction bridge resistance change device)、铁电装置(feram)、铁电隧穿结装置(ferroelectric tunneling junction device)(fjt)、磁阻装置(magnetoresistive device)(mram)等。

[0073]

非易失性存储器装置的实施例可包括操作于一模拟模式(analog mode)中的存储器阵列。一模拟模式存储器(analog mode memory)可被编程于许多电平中的期望数值,例如8或更多电平,其可被转换至多位的数字输出(digjtal output),例如3或更多位。由于装置物理特性(device physical characteristics),可能有准确度议题(issue)(来自编程错误、装置噪声(device noise)等)而导致存储器电平(memory level)发散(spread out),甚至形成意图具有相同「数值」的多个单元的一分布。为编程一模拟存储单元(analog memory cell),数据可通过简单地施加一单一编程脉冲(program pulse)被存储。此外,一编程操作可通过局限数值分布(数值错误(value error))至一可接受范围中,使用多编程脉冲或一编程及验证方案(program-and-verify scheme)以增加编程准确度。

[0074]

举例而言,由于多电平存储器使用重叠邻近存储状态的电平分布来操作,一模拟模式存储器可使用高达64电平或100电平,系有效模拟(举例而言,由于来自错误、噪声等的电平偏移(level shift),一阵列中的一单元可以非信心地读取为电平#56或电平#57)。

[0075]

图2是,当读取电压在基于过渡金属氧化物存储材料的一可变电阻式存储器阵列(reram array)中的多个单元中从0v扫掠(sweep)至1v,电导对读取电压的图表,此图表绘示非定值电导。可看见的是,根据单元的读取电压电平、和目标电导或编程电导,一给定的读取电压的垂直轴上的实际电导通过取样单元(sampled cell)而按量变化。此外,对于可变电阻式存储器(reram)实施例,在较高读取电压的变化系大于在较低读取电压的变化。

[0076]

图3是,通过一卷积层(convolutional layer)产生超过10,000个输入影像且通过一修正线性单元(rectified linear unit,relu)激活函数来处理的任意单位(arbitrary unit)的数据数值的统计分布图(statistical distribution plot),其亦使用于训练期间,因此所有数值系大于或等于0。此分布代表应用于神经网络的一第二层的数据的一实施例,其可使用存储器内计算来实施。此实施例中,分布的较低范围的输入数值系多于较高范围的数值。

[0077]

图4是,使用用于一存储器内计算电路(cim circuit)的非易失性存储器的理想电导,用于接收作为输入的类似图3的数据的一卷积层,乘积累加运算(multiply and accumulate,mac)操作的输出的模拟统计分布图。和图5对照,图5是,使用用于一存储器内计算电路的非易失性存储器的非理想电导(non-ideal conductance),用于接收作为输入的类似图3的数据的一卷积层,乘积累加运算操作的输出的模拟统计分布图。来自非理想电导的结果的图5中的分布系实质上相异于来自理想电导的图4所示的结果的分布。

[0078]

通过图3-图5所呈现的实施例中,使用包括6个卷积层和3个全连接层(fully connected layer)的一神经网络,推理准确度(inference accuracy)从使用理想电导的约90.4%的理想数值减低至使用非理想电导的21.5%。

[0079]

为了补偿非理想电导,如同参照图1所讨论的一输入映射技术(input mapping technology)系被提供,其可获得一更均匀且对称的输入分布。根据本发明的实施例,此输入映射(input mapping)可致能来自使用非易失性存储器的存储器内计算的计算结果的产生,更接近使用理想电导而可达到的结果。如此可导致更佳的推理准确度。

[0080]

图6a绘示可应用于图3-图5的系统的一输入映像的一实施例,其中通过一第一数值范围(此实施例中,0至10a.u)的输入数值系箝位于一第二范围内(a至b)。其中,此实施例中,a是0且b是约2a.u。输入箝位(input clamping)可被应用于一神经网络的第一层中、一或多个中间层中及一输出层中。图7绘示,参照图3-图5的模拟结果,其中箝位被应用于包括6个卷积层和3个全连接层的神经网络的第二层中。如同所绘示的,通过在范围a至b的限制箝位输入数值,存储器内计算操作的结果可产生具有类似图7的分布的结果,其更接近于理想电导情况的图4的分布。

[0081]

例如使用一浮点编码格式(floating point encoding format)所呈现的箝位输入数值(clamped input value)可被转换至模拟数值(analog value),此模拟数值系用于存储器内计算非易失性阵列(cim nonvolatile array)的通过可用的(available)输入电压的全范围,例如在0伏特与1伏特之间。

[0082]

图6b绘示,相对于从a至b的箝位范围到模拟电压vmin至vmax中的全范围的转换,从一输入最小值(input min)至一输入最大值(input max)的一输入范围到模拟电压vmin至vmax的一全范围的转换。vmin至vmax的范围系被较佳地设计,以落入(fall)存储器内计算阵列(cim array)的一操作范围内。vmin至vmax的范围可包括横跨(span)存储器内计算阵列中的理想擦除状态与编程状态(programmed state)之间的阈值电压(threshold voltage)的电压,因此多个单元于一模拟模式中操作。

[0083]

因此,此处所呈现的实施例中,推理准确度从21.5%改善至88.7%,接近于90.4%的理想情况的准确度。

[0084]

如图6a的实施例,若训练期间所使用的激活函数亦非修正线性单元、或并非类似于修正线性单元,提供输入的层产生具有正数值及负数值的两者的输出矩阵的元素。此情况下,输入电压映像(input voltage mapping)可包括偏移与衡量(scale)输入数值分布(input value distribution)至定义的输入电压分布。举例而言,最小负输入数值与最大正数值可以分别是输入电压范围的低界限(boundary)及高界限。

[0085]

图8及图9绘示用于具有不同数值分布的输入数据数值的箝位函数的实施例。图8中,类似图3及图6a-图6b所示,输入数值落入一范围中,此范围具有于一较低边界(edge)的

一峰值计数(peak in count)且落入当数值增加的计数中。图8的实施例中,输入数值可被箝位于较低边界a及数值b之间。图9中,输入数值具有在限度a及b之间之范围的一峰值计数(peak count),且当数值延伸远离(extend away)峰值计数值(peak count value),输入数值在一类似高斯曲线(gaussian like curve)中衰减(fall off)。如同以上所讨论,通过在限度a及b之间箝位输入数值,推理准确度可在使用存储器内计算电路的系统中被改善。

[0086]

一电路(例如图1的电路20)可被提供,接收来自一前层(previous layer)的输入数值且箝位在限度a与b的范围的数值。举例而言,一箝位电路(clamp circuit)可实施逻辑函数:

[0087]

范围界线数值(range boundary value)

[0088]

(低)a及(高)b

[0089][0090]

箝位电路的一输出是用于次层(next layer)的输入数值(一向量或矩阵)的组,系落入a至b的范围中,而非来自前层的较大范围。训练期间,于编程程序及所使用的存储技术的精确度(precision)内,输入数值的较大范围可用以决定存储为目标数值的系数,例如非易失性存储单元中的目标电导。输入数值的箝位范围可在推理引擎实施。

[0091]

为了本说明书的目的,词组「在一第二范围的一限度来箝位数值」意指,具有大于上限的数值的元素的范围的一上限系被设定至上限或约略上限,且意指具有小于下限的数值的元素的范围的一下限系被设定至下限或约略下限。在约略下限或在约略上限的箝位数值系足够接近于个别的限度,以有效改善神经网络的推理准确度。

[0092]

图10是包括本发明所述的电路的一神经网络的附图。神经网络的实施例中,至神经网络的输入是一影像特征信号(image feature signal),此影像特征信号可包括像素数值(pixel value)的一阵列,系由存储于存储器100中的2d或3d矩阵的元素表示。一数字-模拟转换器101从存储器100转换输入的元素为应用于一存储器内计算非易失性存储器阵列102的模拟电压,其存储一核心的系数(或权重),系由使用于神经网络的对应层中的一训练程序所产生。阵列102的积项和输出(sum-of-products output)系应用于一感测电路103,感测电路103提供数字输出至一批正规化电路(batch normalization circuit)104、接着至由数字定域电路(digital domain circuit)所执行的激活函数105。激活函数105的输出可包括一矩阵,此矩阵具有以一数字格式(例如一浮点格式)的元素数值(element value)的一分布。举例而言,此分布可以类似于如分布120所示,系类似于参照以上图3所述。

[0093]

于本发明所述的电路中,神经网络的输入层(可以是一第一层、一中间层或隐藏层(hidden layer))的激活函数105的输出系被应用作为至神经网络中的一次层的输入,一般地由方块150的元件所代表。一实施方式中,至少包括箝位逻辑(clamping logic)、数字-模拟转换器及存储器内计算阵列的方块150的元件是在一单一集成电路或多芯片模块(multichip module)上实施,其包括共同封装的多于一芯片。

[0094]

输入数值(来自激活函数105的输出)系至执行一箝位函数(clamp function)的一箝位电路110的输入,此箝位函数响应存储于一缓存器111中的一限值。箝位函数在一些实施例中的训练期间并未被使用。缓存器111可存储用于箝位电路的数字范围的限度a、b,限

度根据存储器内计算架构(cim architecture)及神经网络函数被设定。箝位电路的输出可包括具有多个元素的一矩阵,这些元素具有落入类似分布121所示的一分布中的数值,箝位于数值0(a=0)的范围的较低边界上且箝位于数值b的范围的一较高边界。如此导致,用于一箝位矩阵(clamped matrix)的分布包括元素数值的一峰值计数,系在接近数值b的范围的边界。

[0095]

箝位矩阵的元素系被应用作为至一数字-模拟转换器(dac)112的输入,数字-模拟转换器(dac)112转换数字数值(digital value)的箝位范围至用于阵列113的模拟输入电压的一范围,其可以是用于阵列113的操作的一全特定范围。举例而言,数字-模拟转换器可以是存储器内计算阵列中的字线驱动器的一部分。电压系被应用至阵列113,阵列113存储一核心的系数(或权重)且产生应用至感测电路114的积项和输出,此核心的系数(或权重)系由使用于神经网络的对应层中的一训练程序所产生。感测电路的输出可被应用至一批正规化电路115,其输入系被应用至激活函数116。神经网络的第二层可提供其输出数值至如上所讨论的一深度神经网络中的附加层(further layer)。可被实施在一单一集成电路或多芯片模块上的方块150中的电路,可以循环的方式在后续层(subsequent layer)再使用。或者地,图10所示的电路的多个实例可被实施在一单一集成电路或多芯片模块上。

[0096]

电路的逻辑函数(方块150)可通过专用的(dedicated)或应用特定逻辑电路(application specific logic circuit)、可编程栅极阵列电路(programmable gate array circuit)、执行一计算机程序(computer program)的通用处理器(general purpose processor)及这些电路的组合被实施。阵列113可使用例如以上所述的可编程电阻存储单元(programmable resistance memory cell)实施。

[0097]

一些实施例中,箝位电路可在一模拟格式(analog format)中实施。举例而言,使用一次性编程(one time only programming)或通过存储于缓存器111中的数值,数字-模拟转换器(dac)112可产生大范围的模拟数值,提供至具有筘位极限组(clamp limits set)的一模拟箝位电路(analog clamping circuit)。

[0098]

图11绘示一替代实施方式,其中激活函数204可使用一单一电路中的箝位逻辑205来结合。结合的激活函数及箝位函数在训练期间可以系未被使用。

[0099]

因此,此实施例中,神经网络中的一前层的存储器阵列200可输出积项和数值至一感测电路201。感测电路201的输出可被应用至一批正规化电路202,批正规化电路202产生具有如分布220所示的输出数值的一分布的一矩阵。一些实施例中,批正规化电路202的输出或直接来自感测电路201的输出可被应用至一结合激活函数/箝位函数逻辑(clamping function logic)210的电路此逻辑210实施一激活函数204及响应存储于缓存器206中的范围限度(range limit)的一箝位电路205。在所实施的激活函数可以是一修正线性单元函数或一类似函数的情况下,逻辑210的输出包括具有元素的一箝位矩阵,具有如分布221所示的数值的一分布。箝位矩阵的元素接着被应用至数字-模拟转换器(dac)211,其转译(translate)箝位矩阵的元素的数值至使用于驱动阵列212的电压的较佳范围且存储通过使用于神经网络的对应层中的一训练程序所产生的一核心的系数(或权重)。阵列212产生积项和输出,此积项和输出系被应用至一感测电路213。感测电路的输出可被处理,以输送至神经网络中的一次层等。

[0100]

本发明所述的箝位函数系基于存储器内计算装置的操作特性。应用此技术可包括

转换一训练模型(trained model)的一或多个层至箝位函数系被应用的存储器内计算架构。箝位数值(clamp value)根据存储器内计算存储器装置及网络模型中的多个层来设定。因此,此箝位函数系弹性的(flexible)且可调的(tunable),此箝位函数并未被训练模型(training model)固定。

[0101]

使用模拟的基于nvm的存储器内计算电路(compute-in-memory circuit)所部署的用于神经网络的输入映像技术(input mapping technique)系被叙述。通过局限用于神经网络中的存储器内计算阵列的输入信号数值范围(input signal value range)至最小化非定值权重效应(non-constant weight effect)的范围,存储器内计算系统可达到良好的识别准确度。此技术的实施例中,一额外函数系被包括在系统中以局限输入范围。用于映像的稳定的阈值数值(threshold value)系被存储于系统中,且根据输入矩阵中的数值的分布的特性、及存储器内计算阵列的操作范围及非理想电导而可以系可编程的。

[0102]

用于一存储器内计算系统(compute-in-memory system)的实施例系被叙述。此技术可被应用于具有流动通过模拟计算单元(analog computing unit)以达成放大(multiplication)的输入信号的任何系统中,计算单元的数值(例如电导)根据输入信号。

[0103]

至此,已经结合附图对本公开实施例进行了详细描述。

[0104]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1