一种基于FPGA的FLASH应用验证系统的制作方法

一种基于fpga的flash应用验证系统

技术领域

1.本发明属于芯片应用验证领域,涉及非易失性存储器领域的应用验证,具体涉及一种基于fpga的flash应用验证系统。

背景技术:

2.随着科学技术的发展,数据的存储和处理越来越重要;非易失性存储器,由于其断电数据不会丢失的特点,因而应用领域非常广泛。

3.目前国内设计和生产宇航用flash的厂商相对较少,对flash验证项目不够充分,且不能兼容不同型号,其中大部分应用验证系统和验证方法主要是验证flash的时序匹配性,不具备通用性。为此,需开发一种flash应用验证系统,能通用各类flash存储器,以满足非易失性存储器的应用验证需求。

技术实现要素:

4.本发明的技术解决问题是:克服现有技术的不足,为各类flash的应用验证提供一套通用性强,验证功能全面的flash应用验证系统。

5.为达到上述目的,本发明采用以下技术方案予以实现:

6.一种基于fpga的flash应用验证系统,包括pc机、flash应用验证板和程控电源;

7.flash应用验证板包括两块fpga、串口模块、电源模块、配置存储器接插件、jtag和sram;其中两块fpga分别记为fpga_a和fpga_b;

8.当验证被测flash的擦写读功能时,被测flash与fpga_a的io口连接;当验证被测flash的jtag功能和存储器配置功能时,被测flash与配置存储器接插件连接,所述配置存储器接插件为fpga的配置接口;

9.串口模块用于连接pc机和fpga_a,将pc机的擦、写、读指令发送给fpga_a,并将fpga_a反馈的结果反馈回pc机;

10.fpga_a根据pc机的擦、写、读指令对被测flash进行擦、写、读测试,采集被测flash的输出数据,据此判断被测flash是否正常工作,判断结果反馈给串口模块;

11.fpga_b采集正在进行工作的被测flash的所有输入输出数据,通过配置存储器接插件和jtag发送给pc机;

12.pc机:当验证被测flash的擦写读功能时,向串口模块发送擦、写、读指令,接收fpga_a反馈的结果,并显示;当验证被测flash的jtag功能时,通过jtag向被测flash发送擦、写、读指令,通过jtag读取被测flash反馈的结果并显示;通过jtag向被测flash发送程序配置指令,以验证被测flash的存储器配置功能;对fpga_b采集的被测flash的所有输入输出数据进行实时显示;

13.电源模块用于为flash应用验证板供电,程控电源为电源模块供电。

14.优选的,fpga_a内部集成了flash控制器和可控时钟单元,flash控制器接收pc机发送的擦、写、读指令,据此对被测flash进行擦写读功能验证,采集被测flash的输出数据,

判断被测flash是否正常工作,判断结果反馈给串口模块;可控时钟单元为fpga_a内部pll,用于产生两种时钟频率,一种时钟频率用来维持fpga_a正常工作,另一种时钟频率作为被测flash的输入时钟频率。

15.优选的,flash控制器对被测flash进行擦写读功能验证的方法如下:

16.flash控制器接收到pc机发送的擦指令后,将擦控制信号和地址发送给被测flash,被测flash执行擦除指令;执行完后flash控制器采集被测flash所有地址的数据,如果数据为ff,代表擦除成功,否则擦除失败;

17.flash控制器接收到pc机发送的写指令后,将写控制信号、输入数据和地址发送给被测flash,直至所有地址写入完毕;

18.flash控制器接收到pc机发送的读指令后,采集被测flash相应地址的输出数据,将输入数据和输出数据进行对比,当读操作执行结束时,若输入数据和输出数据一直相同,则被测flash的读写功能正常,如果输入数据和输出数据不一致,表示被测flash的读写功能异常。

19.优选的,pc机验证被测flash的jtag功能的实现方式如下:

20.pc机读入预加载的数据;

21.pc机通过jtag读取被测flash的id;

22.pc机通过jtag向被测flash发送擦指令,被测flash执行完擦指令后,pc机通过jtag对被测flash相应地址的数据通过校验和查空检查,若数据查空成功,说明擦除成功,否则失败;

23.pc机通过jtag向被测flash发送写指令,将预加载的数据写入被测flash指定地址;

24.pc机通过jtag向被测flash发送读指令,从指定地址读取数据,对读取的数据与预加载的数据进行校验,两者一致,则认为写和读成功。

25.优选的,验证被测flash的存储器配置功能的实现方法如下:

26.pc机通过jtag向被测flash发送程序配置指令和配置码型数据,被测flash加载配置码型数据;fpga_a上设置了led灯,所述配置码型数据用于控制led灯实现跑马灯功能;

27.被测flash完成加载后,观测fpga_a上的led灯,看其是否能实现跑马灯功能,若不能,则被测flash的存储器配置功能异常;若能,则被测flash断电再重新上电,此时若不能实现跑马灯功能,则被测flash的存储器配置功能异常,若仍能实现跑马灯功能,则对被测flash进行软复位;

28.软复位后,若不能实现跑马灯功能,则被测flash的存储器配置功能异常;若仍能实现跑马灯功能,则被测的存储器配置功能正常。

29.优选的,fpga_b内部集成了flash控制器和可控时钟单元,fpga_b外挂sram,能够向sram发送控制信号、时钟、地址和数据,并且能够采集sram的输出数据。

30.优选的,fpga_b也能作为flash,此时fpga_a的jtag与fpga_b的io口相连;

31.pc机通过jtag指令访问fpga_b,将测试程序下载到fpga_b里,此时的fpga_b变为被测flash;

32.pc机通过jtag指令访问fpga_a,验证fpga_b作为被测flash的擦、写、读功能。

33.优选的,还能进行被测flash数字逻辑验证,方法如下:

34.fpga_a的jtag与fpga_b的io口相连,被测flash与fpga_a的io口连接;将此时的fpga_b记为假flash;

35.pc机通过串口模块向fpga_a发送操作指令,fpga_a根据该操作指令控制被测flash执行相应操作,并采集被测flash实时数据通过串口模块反馈给pc机;

36.同时,pc机通过jtag向fpga_a发送操作指令,fpga_a根据该操作指令控制假flash执行相应操作,并采集假flash实时数据通过jtag反馈给pc机;

37.pc机同时实时监测被测flash和假flash在工作时数据端的工作状态,以此判断被测flash数字逻辑是否准确。

38.优选的,电源模块包括第一电源模块和第二电源模块,第一电源模块为fpga_a、串口模块、被测flash供电,第二电源模块为fpga_b和外挂sram供电。

39.优选的,被测flash为spi子板、nor_flash子板或prom子板。

40.与现有技术相比,本发明具有以下有益效果:

41.本发明flash应用验证板,可覆盖spi_flash、nor_flash、prom等非易失存储器的应用验证,包括功能验证、配置验证等,解决了现有flash应用验证板仅可以验证单一flash的缺点,极大地提高了应用验证的覆盖性。

42.本发明flash应用验证板,有两个独立fpga,一个可作为控制器,另一个作为处理器,实时监测工作状态并反馈给pc机,可验证数字逻辑,与真实对标器件相比,便于发现待验证器件的设计问题,加速调试过程和加快器件成熟。

附图说明

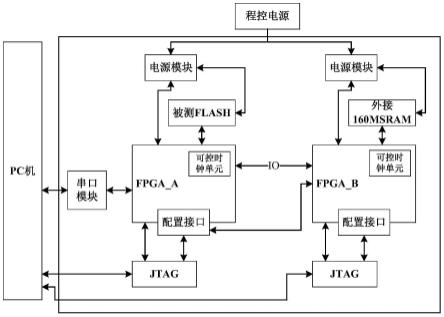

43.图1为flash应用系统原理框图;

44.图2为flash和fpga_a信号连接示意图;

45.图3为flash子板与配置存储器接插件相连接示意图;

具体实施方式

46.参见图1,本发明flash应用验证系统包括pc机、flash应用验证板和程控电源。

47.flash应用验证板包括两块fpga、串口模块、电源模块、配置存储器接插件、jtag、160mb容量sram和被测flash。

48.串口模块用于连接pc机和fpga_a,将pc机的指令发送给fpga_a,并将fpga_a反馈的结果反馈回pc机。

49.fpga_a内部集成了flash控制器和可控时钟单元,flash控制器连接被测flash,flash控制器接收pc机指令,向被测flash发送控制信号、时钟、地址和数据,采集被测flash的输出数据;可控时钟单元为fpga内部pll,用于产生两种时钟频率,一种用来维持fpga正常工作。另一种时钟频率作为被测flash的输入时钟频率;根据被测flash的输出数据来判断flash是否正常工作,结果反馈给串口模块。

50.fpga_b内部集成了flash控制器和可控时钟单元,功能全部涵盖fpga_a功能,除此之外,fpga_b外挂160mb容量sram,可向sram发送控制信号、时钟、地址和数据,并且可采集sram的输出数据。

51.电源模块以ltm4644为核心器件,给fpga、串口模块供电,供电分为两套,fpga_a和

fpga_b单独供电,相互独立上电,互不影响,单独控制上电时序,满足fpga的上电时序要求以及被测flash的上电时序要求。

52.配置存储器接插件为fpga的配置接口,采用fmc接插件,此接插件为bga封装,满足接口多,高速接口等特点,用来连接被测flash,用作配置存储器。

53.pc机应用impact软件通过jtag口发送jtag指令,对被测flash执行各项操作,并把结果反馈给pc机。

54.pc机:向串口模块发送指令,通过串口接收结果,并进行显示;向jtag发送jtag指令,对被测执行操作,并记录结果;fpga_b使用chipscop软件对正在进行工作的被测flash进行实时数据监测。

55.程控电源为电源模块供电。

56.根据被测flash的jtag功能,pc机在impct软件上通过jtag向被测flash发送访问指令,通过jtag对被测flash进行各项功能操作,首先pc机读入预加载的数据,然后对被测flash进行id读取,确认好被测flash的id和状态后,pc机通过jtag对其进行擦、写、读指令的操作。进行完擦指令后,校验数据,查空检查,数据查空成功,说明擦除成功,否则失败;写操作执行完后,对预加载的数据执行校验功能,以此判断写和读是否成功。所有的执行操作结果均会通过jtag向pc机显示。被测flash完成擦写读功能后,全部成功,才能说明被测flash功能正常。被测数据为mcs文件格式,为了能保证被测flash的全面性功能,测试的数据有递增码型、55aa码型、00码型等特殊码型文件;测试的码型容量大小有全容量码型、1/2容量码型、1/4码型等,完成全部的jtag功能验证。

57.根据被测flash的配置功能验证,pc机通过jtag向被测flash发送访问指令,加载配置码型数据,数据能实现跑马灯功能,被测flash完成预加载数据的加载后。fpga的工作模式选择正确,观测fpga系统验证板,是否能实现跑马灯功能,断电后再重新上电,跑马灯功能是否能再此加载成功,软复位后,跑马灯功能依然能加载,以此来判断存储器配置功能,更改被测flash的配置频率,可改变成功数据加载的时间,完成配置功能验证。

58.根据所述的数字逻辑原型验证方法,fpga_a作为验证系统的控制器,对flash进行所有性能的操作。fpga_b作为验证系统的处理器,可作为被测flash,也可实时处理数据,监测端口工作状态。

59.fpga_b外接160mb sram可使验证的数据容量扩充到160mbit,fpga本身的容量不足以支持大容量数据验证,需外加大容量存储器,sram的操作指令简单,易使用,故选用大容量sram,可验证128m的数据擦写读,未来有需求,可直接扩充到256mbit等更大容量。

60.在impact软件执行此功能验证,pc机通过jtag指令访问fpga_b,将测试程序下载到fpga_b里,此时的fpga变作为被测flash,然后pc机通过jtag指令访问fpga_a,对flash进行各项操作,此系统可以验证flash的擦、写、读数字逻辑功能是否正确。fpga_a的jtag与fpga_b的io口相连,能实时监测真的flash和假flash在工作时数据端的工作状态等功能。

61.fpga_b添加控制信号,既能作为假flash,也能监控fpga_a对被测flash的各项指令操作,用chipscop观测数据,当pc机对fpga_a执行指令操作时,将指令给真的flash,即fpga_b添加的配置被测flash,同时将指令给到假的flash,即fpga_b作为假flash,实时观测数据,以此来对比各个指令的数字逻辑是否与对标器件有区别,以此来判断数字逻辑的准确性,便于发现待验证器件的设计问题,加速调试过程和加快器件成熟。

62.fpga_b用chipscop来实时观测数据,jtag访问fpga_a的program、erase、blank check、verify的等指令,用chipscop完成各个指令的数据抓取,未保证各个指令抓取的数据完整性,可在程序中添加计数器,在chipscop在并完成所有数据的保存,可触发定位数据异常点,实现抓取错误指令,完成数据保存。

63.参见图2,根据被测flash的工作模式,pc机通过串口模块将对应的功能指令发送给fpga:

64.fpga通过flash控制器将控制信号、数据和地址发送给被测flash,执行擦除指令;执行完后fpga将所有地址保存的数据对比,是否为ff,如果输出数据为ff,代表擦除成功,并将结果反馈回fpga;

65.fpga通过可控时钟单元设置被测flash输入时钟频率,并通过flash控制器将控制信号、数据和地址发送给被测flash,输入数据可为递增码型、00码型、55aa码型等,直至所有地址写入完毕;

66.fpga执行读操作,将输入数据和输出数据进行对比,如果输入数据和输出数据相同,将继续执行程序,当程序执行结束时,若输入数据和输出数据一直相同,则表示被测flash的读写功能正常,如果输入数据和输出数据不一致,表示被测flash的读写功能异常;

67.fpga将最终擦写读的结果通过串口模块传输至pc机,pc机将记录和显示。

68.参见图3,flash子板,用来和配置存储器接插件相连接,作为配置存储器,flash子板有spi、nor_flash子板,以及以后有更多需求,可添加不同类型flash子板,实现替换子板,验证不同类型的flash,通用性极强,并且节省成本。

69.本发明一方面,被测flash采用的是接插件方式,可验证不同类型的flash的功能,另一方面,本发明采用了两块fpga,每个系统相互独立工作,同时又能实时监测另一块fpag的工作状态。

70.综上,本发明提供了一套验证项目全面、通用性强的flash的应用验证系统及其验证方法,在该系统下可以测试不同类型的flash,采用了高频、接口多的接插件,更换子板就能验证不同类型的flash,从而节约了硬件成本,基于该系统的应用验证方法验证功能全面和通用性强对于flash的应用验证具有重要意义。

71.本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1