一种FIFO存储器的多级流水读写方法和装置与流程

一种fifo存储器的多级流水读写方法和装置

技术领域

1.本发明涉及数据缓存技术领域,尤其涉及一种fifo(first input first output,先入先出)存储器的多级流水读写方法和装置。

背景技术:

2.随着电子信息技术的飞速发展,为缓存数据流、匹配传输速率,fifo存储器因其先进先出的特性在信息采集、传输、处理等系统中广泛应用,尤其在cpu(center process unit,中央处理器)、dsp(digital signal processor,数字信号处理器)、fpga(field programmable gate array,现场可编程门阵列)、ai(artificial intelligence,人工智能)、asic(application-specific integrate circuit,领域专用集成电路)等各类数字芯片中,常作为标准的存储器模块来使用。

3.随着系统需求的不断增加,数字芯片的规模也越来越大,单片可以集成上百亿的晶体管,往往会存在长数据路径的应用场景,即fifo的读写逻辑和fifo的物理距离较远,此时传统做法是通过在fifo读写的控制和数据通路上插多级流水来保证工作时序,这种控制逻辑非常复杂,而且会损失非空即读的重要特性。因此,有必要设计一种fifo存储器的多级流水读写方法,既可以非常便捷的支持长距离传输应用时fifo的读写时序要求,也可以保留非空即读的特性,大幅降低控制逻辑复杂度。

技术实现要素:

4.为解决长距离传输应用时fifo的读写控制逻辑复杂的问题和保留非空即读的特性,本发明公开了一种fifo存储器的多级流水读写方法,并开发了适用于各类数字芯片的fifo存储器的多级流水读写装置,目的是通过一组小容量fifo的级联和控制,实现长距离传输应用时对fifo便捷的读写控制,并保留非空即读的特性,小容量fifo的级联数量可根据时序要求进行灵活配置。

5.本发明公开了一种fifo存储器的多级流水读写方法,采用一个主fifo存储单元(master fifo,m_fifo)和若干个串联的辅fifo存储单元(tiny fifo,小容量fifo单元)来实现,所述辅fifo存储单元包括一个fifo存储器和一个与逻辑模块,本方法包括,

6.近端的写逻辑判断主fifo存储单元的空满状态,如果主fifo存储单元为非慢状态,则近端将数据写入主fifo存储单元后,与所述主fifo存储单元相连的第零级辅fifo存储单元判断所述主fifo存储单元和自身的空满状态,当所述主fifo存储单元非空且自身非满的情况下,所述第零级辅fifo存储单元将发出读指令将所述主fifo存储单元的数据搬入所述第零级辅fifo存储单元;相应的,第零级辅fifo存储单元读入数据后,与所述第零级辅fifo存储单元相连的第一级辅fifo存储单元判断所述第零级辅fifo存储单元和自身的空满状态,当所述第零级辅fifo存储单元非空且第一级辅fifo存储单元非满的情况下,所述第一级辅fifo存储单元将发出读指令将所述第零级辅fifo存储单元的数据搬入所述第一级辅fifo存储单元;以此类推,所述主fifo存储单元的数据会依次被递送到最后一级辅

fifo存储单元中;当远端的读逻辑在需要读取数据时,判断所述最后一级辅fifo存储单元是否为非空状态,如果为非空状态,则读取所需数据。

7.所述的近端是指靠近主fifo存储单元的设备,所述的远端是指靠近最后一级辅fifo存储单元的设备。

8.所述主fifo存储单元采用寄存器或ram实现。

9.所述辅fifo存储单元的fifo存储器的容量小于主fifo存储单元的容量,所述辅fifo存储单元的fifo存储器由寄存器实现。

10.本发明公开了一种fifo存储器的多级流水读写装置,包括一个主fifo存储单元和若干个串联的辅fifo存储单元,所述辅fifo存储单元包括一个fifo存储器和一个与逻辑模块,近端的写逻辑判断主fifo存储单元的空满状态,如果主fifo存储单元为非慢状态,则近端将数据写入主fifo存储单元后,与所述主fifo存储单元相连的第零级辅fifo存储单元判断所述主fifo存储单元和自身的空满状态,当所述主fifo存储单元非空且自身非满的情况下,所述第零级辅fifo存储单元将发出读指令将所述主fifo存储单元的数据搬入所述第零级辅fifo存储单元;相应的,第零级辅fifo存储单元读入数据后,与所述第零级辅fifo存储单元相连的第一级辅fifo存储单元判断所述第零级辅fifo存储单元和自身的空满状态,当所述第零级辅fifo存储单元非空且第一级辅fifo存储单元非满的情况下,所述第一级辅fifo存储单元将发出读指令将所述第零级辅fifo存储单元的数据搬入所述第一级辅fifo存储单元;以此类推,所述主fifo存储单元的数据会依次被递送到最后一级辅fifo存储单元中;当远端的读逻辑在需要读取数据时,判断所述最后一级辅fifo存储单元是否为非空状态,如果为非空状态,则读取所需数据。

11.所述的fifo存储器的多级流水读写装置,所述的近端是指靠近主fifo存储单元的设备,所述的远端是指靠近最后一级辅fifo存储单元的设备。

12.所述的fifo存储器的多级流水读写装置,所述主fifo存储单元采用寄存器或ram实现。

13.所述的fifo存储器的多级流水读写装置,所述辅fifo存储单元的fifo存储器的容量小于主fifo存储单元的容量,所述辅fifo存储单元的fifo存储器由寄存器实现。

14.本发明的有益效果为:

15.1、在大规模集成电路中长距离数据传输的应用条件下,本发明用若干级联的小容量fifo实现了对fifo便捷的读写控制,保留了fifo非空即读的特性,大幅降低了控制逻辑复杂度;

16.2、本发明通过1个主fifo和级联的n个小容量fifo单元实现了fifo数据的长距离传输,级联方式简单,级数易于扩展;

17.3、本发明输入输出接口均为标准的fifo读写接口,使用简单;

18.4、本发明的辅fifo存储单元的级联数量可根据时序要求进行灵活配置,适用于不同的应用场景,通用性强。

附图说明

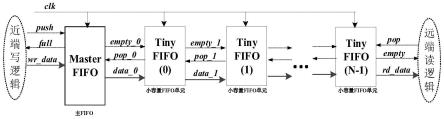

19.图1为本发明fifo存储器的多级流水读写方法的实现结构框图;

20.图2为fifo存储器的多级流水读写方法的实施例中小容量fifo单元结构图;

21.图3为fifo存储器的多级流水读写方法的实施例中支持3级流水读写fifo存储器的工作时序图。

具体实施方式

22.为了更好的了解本发明内容,这里给出一个实施例。

23.实施例一:

24.本发明公开了一种fifo存储器的多级流水读写方法,采用一个主fifo存储单元(master fifo,m_fifo)和若干个串联的辅fifo存储单元(tiny fifo,小容量fifo单元)来实现,所述辅fifo存储单元包括一个fifo存储器和一个与逻辑模块,本方法包括,

25.近端的写逻辑判断主fifo存储单元的空满状态,如果主fifo存储单元为非慢状态,则近端将数据写入主fifo存储单元后,与所述主fifo存储单元相连的第零级辅fifo存储单元判断所述主fifo存储单元和自身的空满状态,当所述主fifo存储单元非空且自身非满的情况下,所述第零级辅fifo存储单元将发出读指令将所述主fifo存储单元的数据搬入所述第零级辅fifo存储单元;相应的,第零级辅fifo存储单元读入数据后,与所述第零级辅fifo存储单元相连的第一级辅fifo存储单元判断所述第零级辅fifo存储单元和自身的空满状态,当所述第零级辅fifo存储单元非空且第一级辅fifo存储单元非满的情况下,所述第一级辅fifo存储单元将发出读指令将所述第零级辅fifo存储单元的数据搬入所述第一级辅fifo存储单元;以此类推,所述主fifo存储单元的数据会依次被递送到最后一级辅fifo存储单元中;当远端的读逻辑在需要读取数据时,判断所述最后一级辅fifo存储单元是否为非空状态,如果为非空状态,则读取所需数据。

26.所述的近端是指靠近主fifo存储单元的设备,所述的远端是指靠近最后一级辅fifo存储单元的设备。

27.所述主fifo存储单元采用寄存器或ram实现。

28.所述辅fifo存储单元的fifo存储器的容量小于主fifo存储单元的容量,所述辅fifo存储单元的fifo存储器由寄存器实现。

29.本发明公开了一种fifo存储器的多级流水读写装置,包括一个主fifo存储单元和若干个串联的辅fifo存储单元,所述辅fifo存储单元包括一个fifo存储器和一个与逻辑模块,近端的写逻辑判断主fifo存储单元的空满状态,如果主fifo存储单元为非慢状态,则近端将数据写入主fifo存储单元后,与所述主fifo存储单元相连的第零级辅fifo存储单元判断所述主fifo存储单元和自身的空满状态,当所述主fifo存储单元非空且自身非满的情况下,所述第零级辅fifo存储单元将发出读指令将所述主fifo存储单元的数据搬入所述第零级辅fifo存储单元;相应的,第零级辅fifo存储单元读入数据后,与所述第零级辅fifo存储单元相连的第一级辅fifo存储单元判断所述第零级辅fifo存储单元和自身的空满状态,当所述第零级辅fifo存储单元非空且第一级辅fifo存储单元非满的情况下,所述第一级辅fifo存储单元将发出读指令将所述第零级辅fifo存储单元的数据搬入所述第一级辅fifo存储单元;以此类推,所述主fifo存储单元的数据会依次被递送到最后一级辅fifo存储单元中;当远端的读逻辑在需要读取数据时,判断所述最后一级辅fifo存储单元是否为非空状态,如果为非空状态,则读取所需数据。

30.所述的fifo存储器的多级流水读写装置,所述的近端是指靠近主fifo存储单元的

设备,所述的远端是指靠近最后一级辅fifo存储单元的设备。

31.所述的fifo存储器的多级流水读写装置,所述主fifo存储单元采用寄存器或ram实现。

32.所述的fifo存储器的多级流水读写装置,所述辅fifo存储单元的fifo存储器的容量小于主fifo存储单元的容量,所述辅fifo存储单元的fifo存储器由寄存器实现。

33.实施例二:

34.本发明公开了一种fifo存储器的多级流水读写方法,主要包括一个m_fifo(master fifo,主fifo)和若干个串联的t_fifo(tiny fifo,小容量fifo单元),所述t_fifo主要包括一个小容量fifo和一个与逻辑,近端的写逻辑将数据写入所述m_fifo;与所述m_fifo相连的第零级t_fifo会判断所述m_fifo和自身的空满状态,当所述m_fifo非空且自身非满的情况下,所述第零级t_fifo将发出读指令将所述m-fifo的数据搬入所述第零级t_fifo;类似的,与所述第零级t_fifo相连的第一级t_fifo会判断所述第零级t_fifo和自身的空满状态,当所述第零级t_fifo非空且自身非满的情况下,所述第一级t_fifo将发出读指令将所述第零级t_fifo的数据搬入所述第一级t_fifo;以此类推,所述m_fifo的数据会依次被递送到最后一级即第n-1级t_fifo中;当远端的读逻辑在需要读取数据时,判断所述最后一级t_fifo是否非空即可读取所需数据。

35.所述m_fifo为寄存器文件或ram,但不限于以上两种存储结构;

36.所述t_fifo由一个小容量fifo和一个与逻辑组成,所述小容量fifo通常由寄存器构成,但不限于该存储结构;

37.本发明公开了一种fifo存储器的多级流水读写方法,支持多级流水读写的fifo存储器结构框图如附图1所示。其中,push为m_fifo的写使能,wr_data为m_fifo的写数据,full为m_fifo的满标志,empty_0为m_fifo的空标志,pop_0和data_0分别为m_fifo的读使能和读数据;empty_1为第零级t_fifo的空标志,pop_1和data_1分别为第零级t_fifo的读使能和读数据;以此类推,第n-1级t_fifo的空标志empty、读使能pop、读数据rd_data送给远端读逻辑。

38.每个t_fifo的结构图如附图2所示,包含一个与逻辑和一个小容量fifo,当上一级输入的空标志empty_i和自身的满标志full均无效时,表明上一级非空且自身非满,则通过pop_i信号发出读操作,并将读到的数据存入小容量fifo中。

39.采用以上结构的n级流水读写的fifo存储器通过以下步骤实现:

40.首先,近端的写逻辑判断m_fifo的full标志,当非满时将数据写入m_fifo中。

41.然后,级联的n级t_fifo依次将前级数据读出并存到各自的小容量fifo中;

42.最后,远端的读逻辑判断第n-1级t_fifo的空状态,当非空时即可发出读操作,将数据读出。

43.对远端读逻辑而言,中间级联的t_fifo相当于透明传输,当近端写逻辑将数据写入m_fifo后,n个时钟周期后,远端读逻辑即可以收到非空标志,从而根据需要发起读操作,实现了长距离传输时fifo数据读写的便捷控制,fifo的非空即读的特性也得以保留,大幅降低传统方案中为匹配流水级数所需控制逻辑的复杂度,且级联方式简单,级数可灵活配置,适用于不同应用场景,通用性强。

44.根据以上技术方案,在asic工作主频500mhz的应用需求下,因数据路径较远,为保

证时序,fifo的数据需要3个时钟周期才能到达远端,设计了一款3级流水读写的fifo存储器,m_fifo的大小为256

×

32bit,t_fifo中小容量fifo大小为3

×

32bit,其工作时序示意图如附图3所示。

45.可以看到,近端的写逻辑根据需要分三次burst共写了12个数据,不失一般性,数据依次记为1~12。当数据1被写入后,empty_0即无效表示非空,第零级t_fifo自身也非满,发出了读信号pop_0;同样的第一级和第二级也依次发出了读信号。

46.由于远端读逻辑未达到读条件,第二级t_fifo读了3个数据后,因自身fifo已满,即停止了读操作,在第8个时钟周期,远端读逻辑开始burt读操作,读出了10个数据,直至empty信号有效,即第二级t_fifo已空。

47.在第21个时钟周期,远端读逻辑发现empty信号无效后,即第二级t_fifo非空后,立即发出了读操作,将数据11和数据12顺利读出。

48.以上所述仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1