半导体存储器及其部分写入方法与流程

1.本发明涉及一种存储器数据存取技术,特别涉及一种半导体存储器及其部分写入方法。

背景技术:

2.在例如在感测放大器与输入/输出引脚之间具有超多内部输入/输出线路的通用半导体存储器中,因为用于传输输入数据或输出数据以将输入数据写入至存储器组中或自存储器组读取输出数据的半导体存储器的内部输入/输出线路可在内部输入/输出线路上引起具有大电压差的多个电压摆动(voltage swing),故通用半导体存储器在存储器读取操作或存储器写入操作期间消耗极大供电电流。尤其,当半导体存储器执行存储器写入操作时,因为内部输入/输出线可在全电压中摆动,故内部输入/输出线路可在存储器写入操作期间消耗比存储器读取操作大两倍或三倍的电流。因此,关于如何减少由内部输入/输出线路上的存储器写入操作造成的功耗,以下提供若干实施例的解决方案。

技术实现要素:

3.本发明针对能够提供较佳存储器数据存取效率的半导体存储器及其部分写入方法。

4.本发明的半导体存储器包含存储器组、写入放大器电路、多个输入/输出引脚以及多个地址引脚。写入放大器电路经由多个内部输入/输出线路来耦接至存储器组。多个输入/输出引脚经由多个输入线路来耦接至写入放大器电路。多个地址引脚的一部分用以接收列地址指令,且所述多个地址引脚的另一部分中的至少一个用以在数据写入时段期间接收操作码。半导体存储器根据操作码来判断用于传输输入数据的多个内部输入/输出线路的一部分,且根据部分写入指令来操作写入放大器电路以执行部分写入模式以便根据列地址指令经由多个内部输入/输出线路的部分将输入数据写入至存储器组中。

5.在本发明的实施例中,半导体存储器还包含控制逻辑、地址寄存器、模式寄存器以及放大器控制器。地址寄存器经耦接至多个地址引脚,且用以接收列地址指令及操作码。控制逻辑用以提供模式寄存器设置命令。模式寄存器经耦接至地址寄存器,且用以接收由控制逻辑提供的模式寄存器设置命令,且输出模式选择信号。放大器控制器经耦接至模式寄存器及写入放大器电路,且用以接收模式选择信号以根据模式选择信号来控制写入放大器电路以执行部分写入模式。

6.在本发明的实施例中,半导体存储器还包含列地址锁存器。列地址锁存器经耦接至地址寄存器及写入放大器,且用以接收由地址寄存器提供的列地址指令及操作码。列地址锁存器将部分写入指令提供至写入放大器电路,使得写入放大器电路由放大器控制器控制以经由多个内部输入/输出线路将输入数据写入至存储器组中。

7.在本发明的实施例中,半导体存储器还包含列解码器。列解码器经耦接至列地址锁存器及存储器组。列地址锁存器将列地址指令提供至列解码器,使得列解码器根据列地

址指令来判断存储器组中的部分写入区。

8.在本发明的实施例中,半导体存储器还包含行地址锁存器及行解码器。行地址锁存器经耦接至地址寄存器。行解码器耦接至行地址锁存器及存储器组。地址寄存器进一步用以经由地址引脚来接收行地址指令,且行地址锁存器用以接收由地址寄存器提供的行地址指令且将行地址指令输出至行解码器,使得列解码器及行解码器根据列地址指令及行地址指令来判断存储器组中的部分写入区。

9.在本发明的实施例中,操作码包含特定部分写入指令,且放大器控制器进一步耦接至列地址锁存器。放大器控制器用以接收由列地址锁存器提供的特定部分写入指令以控制写入放大器电路来以实时方式执行部分写入模式。

10.在本发明的实施例中,特定部分写入指令为1位数据,且特定部分写入指令经由多个地址引脚的另一部分中的另一个而接收。

11.在本发明的实施例中,内部输入/输出线路经分类为多个输入/输出线路群组,且操作码包含n位数据,其中n为正整数,且写入放大器电路根据n位数据来选择多个输入/输出线路群组中的一个以经由多个输入/输出线路群组中的一个将输入数据写入至存储器组中。

12.在本发明的实施例中,当多个地址引脚用以经由多个地址引脚来接收行地址指令时。

13.在本发明的实施例中,多个地址引脚进一步用以经由多个地址引脚的部分来接收另一列地址指令,且多个地址引脚的另一部分中的至少一个在数据读取时段期间为未定义。

14.在本发明的实施例中,半导体存储器还包含组选择引脚、另一存储器组及另一写入放大器电路。组选择引脚用以接收组选择指令。另一写入放大器电路经由其他多个内部输入/输出线路来耦接至另一存储器组,且经由多个输入线路来耦接至多个地址引脚。半导体存储器根据组选择指令来选择写入放大器电路或另一写入放大器电路以在存储器组或另一存储器组上执行部分写入,使得写入放大器电路或另一写入放大器电路经由多个内部输入/输出线路的部分或其他多个内部输入/输出线路的一部分将输入数据写入至存储器组或另一存储器组中。

15.本发明的部分写入方法适于半导体存储器。部分写入方法包含以下步骤:在数据写入时段期间经由多个地址引脚的一部分来接收列地址指令及经由多个地址引脚的另一部分中的至少一个来接收操作码;根据操作码来判断用于传输输入数据的多个内部输入/输出线路的一部分;以及根据操作码来操作写入放大器电路以执行部分写入模式以根据列地址指令经由多个内部输入/输出线路的部分将输入数据写入至存储器组中。

16.基于以上,根据本发明的半导体存储器及其部分写入方法,半导体存储器能够执行部分写入模式以有效地减少由存储器写入操作造成的功耗。

17.为使前述内容更容易理解,如下详细描述随附有图式的若干实施例。

附图说明

18.包含随附图式以提供对本发明的进一步理解,且随附图式并入于本说明书中且构成本说明书的一部分。图式说明本发明的例示性实施例,并连同描述内容一起用以解释本

发明的原理。

19.图1为根据本发明的实施例的半导体存储器的功能方块图。

20.图2为根据本发明的实施例的以一般写入模式操作以执行数据写入的半导体存储器的存储器操作时序图。

21.图3为根据本发明的实施例的以部分写入模式操作以执行数据写入的半导体存储器的存储器操作时序图。

22.图4为根据本发明的另一实施例的以部分写入模式操作从而以实时方式执行数据写入的半导体存储器的存储器操作时序图。

23.图5为根据本发明的另一实施例的半导体存储器的功能方块图。

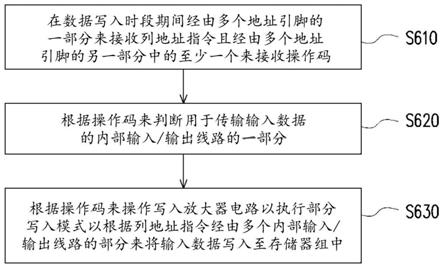

24.图6为根据本发明的实施例的部分写入方法的流程图。

25.【符号说明】

26.100、500:半导体存储器

27.101、501:控制逻辑

28.110、510、520:存储器组

29.111、511、521:感测放大器

30.112、512、522:列解码器

31.113、513、523:行解码器

32.131、531、541:写入放大器电路

33.132、532、542:读取放大器电路

34.133、533:写入驱动器

35.134、534:读取驱动器

36.150、550:地址寄存器

37.151、551:列地址锁存器

38.152、552:行地址锁存器

39.153、553:模式寄存器

40.154、554:放大器控制器

41.161、561:输入接口

42.162、562:输出接口

43.163、563:地址指令接口

44.171、571:输入线路

45.172、572:输出线路

46.173、573、574:内部输入/输出线路

47.564:组选择引脚

48.570:组控制逻辑

49.add[8:0]:第一地址引脚至第九地址引脚

[0050]

add[9]:第十地址引脚

[0051]

add[10]:第十一地址引脚

[0052]

add[11]:第十二地址引脚

[0053]

ck_t:时序信号

[0054]

cmd:控制信号

[0055]

d0、d0'、d1、d1':输入数据

[0056]

d[255:0]:第1输入线路至第256输入线路

[0057]

d[511:256]:第257输入线路至第512输入线路

[0058]

q0:输出数据

[0059]

q[511:0]:第1输出线路至第512输出线路

[0060]

s610、s620、s630:步骤

[0061]

t20、t21、t22、t23、t30、t31、t32、t33、t40、t41、t42、t43、t44、t45:时间

具体实施方式

[0062]

为了使本发明的内容可以被更容易明了,以下特举实施例做为本发明确实能够据以实施的范例。另外,凡可能之处,在图式及实施方式中使用相同标号的元件/构件/步骤,代表相同或类似部件。

[0063]

在整个本说明书(包含权利要求书)中使用的术语「耦接」可指任何直接或间接连接方式。举例而言,若描述第一装置经耦接至第二装置,则应理解,第一装置可直接连接至第二装置或经由其他装置、电线或某些连接构件间接地连接至第二装置。另外,在适当的情况下,具有相同图式元件符号的元件/组件/步骤在图式及实施例中表示相同或类似部分。在不同实施例中具有相同图式元件符号或术语的元件/组件/步骤的描述可彼此参考。

[0064]

图1为根据本发明的实施例的半导体存储器的功能方块图。参考图1,半导体存储器100包含控制逻辑101、存储器组110、感测放大器111、写入放大器电路131、写入驱动器133、输入接口161以及地址指令接口163。写入放大器电路131经由感测放大器111及多个内部输入/输出线路(input/output line)(或称总线(bus))173耦接至存储器组(memory bank)110,且写入放大器电路131包含多个写入放大器。写入放大器电路131经耦接至写入驱动器133。输入接口161包含多个输入引脚,且输入接口161经由多个输入线路(input line)171耦接至写入放大器电路131及写入驱动器133。地址指令接口163包含多个地址引脚。在本发明的实施例中,存储器100可为动态随机存取存储器(dynamic random-access memory;dram),但本发明不限于此。此外,控制逻辑101用以接收一或多个控制指令以控制半导体存储器100及以上存储器内部电路以执行存储器写入操作或存储器读取操作。

[0065]

在本发明的实施例中,当半导体存储器100在数据写入时段中操作时,地址指令接口163的地址引脚的一部分接收列地址指令,且地址引脚的另一部分中的至少一个在数据写入时段期间接收操作码。接着,半导体存储器100根据操作码来判断用于传输输入数据的内部输入/输出线路173的一部分。写入驱动器133经由输入线路171自输入接口161的输入引脚接收输入数据,且将输入数据提供至写入放大器电路131,使得半导体存储器100可根据操作码来操作写入放大器电路131以执行部分写入模式以根据列地址指令经由内部输入/输出线路173的部分及感测放大器111将输入数据写入至存储器组110中。因此,本发明的半导体存储器100可经由内部输入/输出线路173的部分来在存储器组110上执行部分写入,以便有效地减少由将所有内部输入/输出线路173用于存储器写入造成的功耗。

[0066]

在本发明的实施例中,半导体存储器100还包含列解码器112、行解码器113、地址寄存器150、列地址锁存器151、行地址锁存器152、模式寄存器153以及放大器控制器154。列

解码器112及行解码器113经耦接至存储器组110。地址寄存器150经耦接至地址指令接口163的地址引脚,且经耦接至列地址锁存器151、行地址锁存器152以及模式寄存器153。模式寄存器153进一步耦接至控制逻辑101及放大器控制器154。列地址锁存器151经耦接至列解码器112。行地址锁存器152经耦接至行解码器113。放大器控制器154经耦接至列地址锁存器151及写入放大器电路131。在本发明的实施例中,模式寄存器153用以藉由模式寄存器设置命令来设置半导体存储器100从而以例如读取模式、一般写入模式、部分写入模式或部分写入实时模式操作,且半导体存储器100维持先前设置存取模式直至模式寄存器153接收下一模式寄存器设置命令为止。

[0067]

更详细说明,当半导体存储器100执行部分写入操作时,地址寄存器150自地址指令接口163的地址引脚接收列地址指令及操作码。地址寄存器150、控制逻辑101可将模式寄存器设置命令提供至模式寄存器153,使得模式寄存器153设置半导体存储器100以操作一些特定存取操作,诸如部分写入操作。模式寄存器153接收由控制逻辑101提供的模式寄存器设置命令以根据模式寄存器设置命令将模式选择信号提供至放大器控制器154。亦即,模式寄存器153根据模式寄存器设置命令来设置存储器存取模式,且放大器控制器154根据模式选择信号来控制写入放大器电路131以执行部分写入模式。因此,写入放大器电路131由放大器控制器154控制以经由内部输入/输出线路173的部分将输入数据驱动至感测放大器111以便将输入数据写入至存储器组110中。另外,列地址锁存器151接收由地址寄存器150提供的列地址指令及操作码,且列地址锁存器151将列地址指令提供至列解码器112,使得列解码器112根据列地址指令来判断存储器组110中的部分写入区。因此,写入放大器电路131在存储器组110上执行部分写入。亦即,写入放大器电路131经由内部输入/输出线路173的部分将输入数据写入至存储器组110中的部分写入区中,以便有效地减少由将所有内部输入/输出线路173用于存储器写入造成的功耗。

[0068]

此外,在本发明的实施例中,地址寄存器150进一步用以经由地址指令接口163的地址引脚来接收行地址指令,且行地址锁存器152用以在数据写入时段期间接收由地址寄存器150提供的行地址指令且将行地址指令输出至行解码器113,使得列解码器112及行解码器113根据列地址指令及行地址指令来判断存储器组110中的部分写入区。然而,在本发明的一个实施例中,地址指令接口163的地址引脚的数目可由行地址判断。换句话说,用于接收行地址指令的地址引脚的数目可大于用于接收列地址指令的地址引脚的数目。

[0069]

在本发明的实施例中,内部输入/输出线路173可经分类为多个输入/输出线路群组,且操作码包含n位数据,其中n为正整数。列地址锁存器151将n位数据(操作码)提供至写入放大器电路131,使得写入放大器电路131根据n位数据来选择输入/输出线路群组中的一个以自输入/输出线路群组中的一个接收输入数据。在本发明的一个实施例中,操作码可包含特定部分写入指令,且放大器控制器154进一步耦接至列地址锁存器151。放大器控制器154可进一步用以接收特定部分写入指令以控制写入放大器电路131以执行部分写入模式实时方式。特定部分写入指令可为1位数据,且特定部分写入指令经由地址指令接口163的地址引脚中的一个传输。

[0070]

另外,半导体存储器100还包含读取放大器电路132及读取驱动器134以及输出接口162。读取放大器电路132经由感测放大器111及内部输入/输出线路173耦接至存储器组110,且读取放大器电路132包含多个读取放大器。读取放大器电路132经耦接至读取驱动器

134及放大器控制器154。模式寄存器153接收模式寄存器设置命令以设置放大器控制器154,以便进一步设置写入放大器电路131或读取放大器电路132以执行存储器读取操作或存储器写入操作。输出接口162包含多个输出引脚,且输出接口162经由多个输出线路(output line)172耦接至读取放大器电路132及读取驱动器134。举例而言,输入线路171的数目可为512个,且输出线路172的数目也可为512个,但本发明不限于此。换句话说,输入线路171的带宽可为512个位,且输出线路172的带宽也可为512个位。另外,输入接口161、输出接口162以及地址指令接口163经耦接至半导体存储器100外部的其他电路或模块,诸如中央处理器单元(center processor unit;cpu)、图像信号处理器(image signal processor;isp)核心、数字信号处理器(digital signal processor;dsp)核心、图形处理单元(graphics processing unit;gpu)核心、卷积神经网络(convolutional neural network;cnn)加速器或具有存储器存取需要的其他模块,其中输入/输出接口161及输入/输出接口162经由两个外部输入/输出总线来耦接至半导体存储器100外部的其他电路或模块。在本发明的一个实施例中,半导体存储器100通常比存储器写入操作执行更多存储器读取操作。

[0071]

在本发明的实施例中,当半导体存储器100在数据读取时段中操作时,地址引脚的部分进一步用以接收另一列地址指令及另一行地址指令,且地址引脚的另一部分中的至少一个在数据读取时段期间为未定义(undefined)。接着,放大器控制器154控制读取放大器电路132以选择用于传输输出数据的所有内部输入/输出线路173。读取放大器电路132根据另一列地址指令及另一行地址指令经由感测放大器111经由所有内部输入/输出线路173自存储器组110读取输出数据,且读取驱动器134经由输出线路172将输出数据提供至输出接口162的输出引脚。换句话说,用于在数据写入时段期间接收指令的地址指令接口163的地址引脚的数目大于用于在数据读取时段期间接收指令的地址指令接口163的地址引脚的数目。

[0072]

图2为根据本发明的实施例的以一般写入模式操作以执行数据写入的半导体存储器的存储器操作时序图。参看图1及图2,例如,半导体存储器100的控制逻辑接收时序信号ck_t及控制信号cmd以控制半导体存储器100以执行相关存储器操作。在本发明的实施例中,地址引脚的数目可为12个,图2中的符号add[8:0]表示第一地址引脚至第九地址引脚。图2中的符号add[9]表示第十地址引脚。图2中的符号add[10]表示第十一地址引脚。图2中的符号add[11]表示第十二地址引脚。在本发明的实施例中,第十地址引脚及第十一地址引脚(add[9]及add[10])用以接收操作码的2位数据,且第十二地址引脚(add[11])用以接收操作码的特定部分写入指令的1位数据。换句话说,以上地址引脚(add[9]至add[11])的3位数据可形成为操作码,且模式寄存器153根据模式寄存器设置命令将模式选择信号提供至放大器控制器154,使得放大器控制器154控制写入放大器电路131以选择用于传输输入数据的输入/输出线路173的至少部分。

[0073]

在本发明的实施例中,内部输入线路171的数目可为512个,但本发明不限于此。输入线路171经分类为多个输入线路群组。因此,图2中的符号d[255:0]表示第1输入线路至第256输入线路,且图2中的符号d[511:256]表示第257输入线路至第512输入线路。图2中的符号q[511:0]表示第1输出线路至第512输出线路。内部输入/输出线路173的数目也可为512个。内部输入/输出线路173亦分类为对应于输入线路171的多个内部输入/输出线路,所述

输入线路171为第1输入线路至第256输入线路以及第257输入线路至第512输入线路。

[0074]

在本发明的实施例中,半导体存储器100能够执行四分之一部分写入操作。举例而言,若由第十地址引脚(add[9])接收的数据为「0」且由第十一地址引脚(add[10])接收的数据为「0」,则第1内部输入/输出线路至第128内部输入/输出线路用以接收输入数据(经由第1输入线路至第128输入线路),且第129内部输入/输出线路至第512内部输入/输出线路经停用。若由第十地址引脚(add[9])接收的数据为「1」且由第十一地址引脚(add[10])接收的数据为「0」,则第129内部输入/输出线路至第256内部输入/输出线路用以接收输入数据(经由第129输入线路至第256输入线路),且第1内部输入/输出线路至第128内部输入/输出线路以及第257内部输入/输出线路至第512内部输入/输出线路经停用。若由第十地址引脚(add[9])接收的数据为「0」且由第十一地址引脚(add[10])接收的数据为「1」,则第257内部输入/输出线路至第384内部输入/输出线路用以接收输入数据(经由第257输入线路至第384输入线路),且第1内部输入/输出线路至第256内部输入/输出线路以及第385内部输入/输出线路至第512内部输入/输出线路经停用。若由第十地址引脚(add[9])接收的数据为「1」且由第十一地址引脚(add[10])接收的数据为「1」,则第385内部输入/输出线路至第512内部输入/输出线路用以接收输入数据(经由第385输入线路至第512输入线路),且第1内部输入/输出线路至第384内部输入/输出线路经停用。

[0075]

在部分写入设置的另一实例中,半导体存储器100能够执行一半部分写入操作。若由第十地址引脚(add[9])接收的数据为「0」且第十一地址引脚(add[10])为「x」(为未定义),则第1内部输入/输出线路至第256内部输入/输出线路用以接收输入数据(经由第1输入线路至第256输入线路),且第257内部输入/输出线路至第512内部输入/输出线路经停用。若由第十地址引脚(add[9])接收的数据为「1」且第十一地址引脚(add[10])为「x」(为未定义),则第257内部输入/输出线路至第512内部输入/输出线路用以接收输入数据(经由第257输入线路至第512输入线路),且第1内部输入/输出线路至第256内部输入/输出线路经停用。

[0076]

在本发明的实施例中,因为半导体存储器100经设置为一般写入模式,在时间t20处,半导体存储器100接收控制信号cmd以执行数据写入(由指令「wr」指示),第十地址引脚及第十二地址引脚(add[9]及add[11])为未定义(由指令「x」指示),且第一地址引脚至第九地址引脚(add[8:0])接收列地址(由指令「ca」指示)。因此,地址寄存器150接收列地址指令(来自add[8:0]的8位数据),且将列地址指令(来自add[8:0]的8位数据)提供至列地址锁存器151。模式寄存器153将一般写入模式信号提供至写入放大器131。列地址锁存器151将列地址指令(来自add[8:0]的8位数据)提供至列解码器112,其中列解码器112解码8位数据以获得列地址,以便判断存储器组110中的一般写入区。在时间t21处,写入放大器电路131经由第1内部输入/输出线路至第256内部输入/输出线路以及第257内部输入/输出线路至第512内部输入/输出线路将输入数据d0及输入数据d1两者自输入接口161驱动至感测放大器111。举例而言,在时间t20与时间21之间存在一个延迟时间。

[0077]

接着,在时间t22处,因为半导体存储器100接收控制信号cmd以执行数据读取(由指令「rd」指示),故半导体存储器100以读取模式操作。另外,第一地址引脚至第九地址引脚(add[8:0])在时间t22处接收另一列地址(由指令「ca」指示)。因此,读取放大器电路132读取输出数据q0,且读取放大器电路132在时间t23处经由第1内部输入/输出线路至第512内

部输入/输出线路将输出数据q0传输至输出接口162。举例而言,在时间t22与时间t23之间存在三个延迟时间。

[0078]

另外,图2的控制信号cmd中的符号「des」指示控制信号cmd为取消选择命令,且图2的控制信号cmd中的符号「act」指示控制信号cmd为激活命令。图2的地址引脚中的符号「x」指示地址引脚为未定义,且图2的地址引脚中的符号「ra」指示地址引脚接收行地址。

[0079]

换句话说,当半导体存储器100藉由模式寄存器设置命令经设置为一般写入模式时,模式寄存器153接收模式寄存器设置命令以设置放大器控制器154,以便进一步设置写入放大器电路131以执行一般写入操作。在本发明的实施例中,当半导体存储器100以一般写入模式操作时,第十地址引脚至第十二地址引脚(add[9]至add[11])对一般写入操作而言不必要,因此,第十地址引脚至第十二地址引脚(add[9]至add[11])为未定义(由指令「x」指示)(或描述为「不关注」)。

[0080]

图3为根据本发明的实施例的以部分写入模式操作以执行数据写入的半导体存储器的存储器操作时序图。参看图1及图3,相比于图2,因为半导体存储器100经设置为部分写入模式,在时间t30处,半导体存储器100接收控制信号cmd以执行数据写入(由指令「wr」指示),第十地址引脚(add[9])接收「0」作为部分写入地址,第十一地址引脚(add[10])为「x」(为未定义),且第一地址引脚至第九地址引脚(add[8:0])接收列地址(由指令「ca」指示)。因此,在时间t31处,写入放大器电路131经由第1内部输入/输出线路至第256内部输入/输出线路将输入数据d0驱动至感测放大器111的一半部分,且并不经由第257内部输入/输出线路至第512内部输入/输出线路将数据驱动至感测放大器111的另一半。举例而言,在时间t30与时间31之间存在一个延迟时间。

[0081]

接着,在时间t32处,因为半导体存储器100接收控制信号cmd以执行数据读取(由指令「rd」指示),故半导体存储器100以读取模式操作。另外,第一地址引脚至第九地址引脚(add[8:0])在时间t32处接收另一列地址(由指令「ca」指示)。因此,读取放大器电路132读取输出数据q0,且读取放大器电路132在时间t33处经由第1内部输入/输出线路至第512内部输入/输出线路将输出数据q0传输至输出接口162。举例而言,在时间t32与时间t33之间存在三个延迟时间。

[0082]

换句话说,当半导体存储器100藉由模式寄存器设置命令经设置为部分写入模式时,模式寄存器153接收模式寄存器设置命令以设置放大器控制器154,以便进一步设置写入放大器电路131以执行部分写入操作。在本发明的实施例中,当半导体存储器100以部分写入模式操作时,第十地址引脚(add[9])用于经由内部输入/输出线路的一半部分将输入数据指派至驱动至感测放大器111(由指令「0」或指令「1」指示),且第十一地址引脚及第十二地址引脚(add[10]及add[11])为未定义(由指令「x」指示),但本发明不限于此。在本发明的另一实施例中,当半导体存储器100以部分写入模式操作时,第十地址引脚及第十一地址引脚(add[9]及add[10])用于经由内部输入/输出线路的四分之一部分将输入数据指派至驱动至感测放大器111(由指令「0」或指令「1」指示),且第十二地址引脚(add[11])为未定义(由指令「x」指示)。

[0083]

图4为根据本发明的另一实施例的以部分写入模式操作从而以实时方式执行数据写入的半导体存储器的存储器操作时序图。参看图1及图4,相比于图3,因为半导体存储器100经设置为部分写入实时模式,在时间t40处,半导体存储器100接收控制信号cmd以执行

数据写入(由指令「wr」指示),第十地址引脚(add[9])接收数据「0」作为部分写入地址,第十一地址引脚(add[10])为「x」(为未定义)且第十二地址引脚(add[11])接收「1」作为部分写入启用指令。另外,第一地址引脚至第九地址引脚(add[8:0])在时间t40处接收列地址(由指令「ca」指示)。因此,在时间t41处,写入放大器电路131经由第1内部输入/输出线路至第256内部输入/输出线路将输入数据d0'驱动至感测放大器111的一半部分,且并不经由第257内部输入/输出线路至第512内部输入/输出线路将输入数据驱动至感测放大器111的另一半。举例而言,在时间t40与时间41之间存在一个延迟时间。然而,在时间t42处,因为半导体存储器100接收控制信号cmd以执行数据写入(由指令「wr」指示),且第十二地址引脚(add[11])接收「0」作为部分写入停用指令,半导体存储器100停止部分写入模式且变为一般写入模式。因此,在时间t43处,写入放大器电路131经由第1内部输入/输出线路至第256内部输入/输出线路将输入数据d0'连续驱动至感测放大器111的一半部分,且写入放大器电路131开始经由第257内部输入/输出线路至第512内部输入/输出线路将输入数据d1'驱动至感测放大器111的另一半。

[0084]

接着,在时间t44处,因为半导体存储器100接收控制信号cmd以执行数据读取(由指令「rd」指示),故半导体存储器100以读取模式操作。另外,第一地址引脚至第九地址引脚(add[8:0])在时间t44处接收另一列地址(由指令「ca」指示)。因此,读取放大器电路132读取输出数据q0,且读取放大器电路132在时间t44处经由第1内部输入/输出线路至第512内部输入/输出线路将输出数据q0传输至输出接口162。举例而言,在时间t44与时间t45之间存在三个延迟时间。

[0085]

应注意,在本发明的实施例中,半导体存储器100首先用以执行部分写入模式且接着根据第十二地址引脚(add[11])而变为执行一般写入模式,但本发明不限于此。在本发明的另一实施例中,半导体存储器100首先用以执行一般写入模式且接着根据第十二地址引脚(add[11])而变为执行部分写入模式。

[0086]

换句话说,当半导体存储器100藉由模式寄存器设置命令来设置为部分写入实时模式时,模式寄存器153接收模式寄存器设置命令以设置放大器控制器154,以便进一步设置写入放大器电路131以动态地切换为执行一般写入操作或部分写入操作。在本发明的实施例中,当半导体存储器100以部分写入实时模式操作时,且第十二地址引脚(add[11])接收「1」作为部分写入启用指令,第十地址引脚(add[9])用于经由内部输入/输出线路的一半部分将输入数据指派至驱动至感测放大器111(由指令「0」或指令「1」指示),且第十一地址引脚(add[10])为未定义(由指令「x」指示),但本发明不限于此。在本发明的另一实施例中,第十地址引脚及第十一地址引脚(add[9]及add[10])用于经由内部输入/输出线路的四分之一部分将输入数据指派至驱动至感测放大器111(由指令「0」或指令「1」指示)。另外,当半导体存储器100以部分写入实时模式操作时,且第十二地址引脚(add[11])接收「0」作为部分写入停用指令,在不考虑第十地址引脚及第十一地址引脚(add[9]及add[10])的情况下,写入放大器电路131经切换为执行一般写入操作。

[0087]

图5为根据本发明的另一实施例的半导体存储器的功能方块图。参看图5,半导体存储器500可为动态随机存取存储器(dram)的存储器芯片。半导体存储器500包含两个存储器组510及存储器组520。在本发明的实施例中,半导体存储器500包含控制逻辑501、存储器组510及存储器组520、感测放大器511及感测放大器521、列解码器512及列解码器522、行解

码器513及行解码器523、写入放大器电路531及写入放大器电路541、读取放大器电路532及读取放大器电路542、写入驱动器533、读取驱动器534、地址寄存器550、列地址锁存器551、行地址锁存器552、模式寄存器553及放大器控制器554、输入接口561、输出接口562、地址指令接口563以及组(bank)选择引脚564。输入接口561包含多个输入引脚,且输出接口562包含多个输出引脚。地址指令接口563包含多个地址引脚。

[0088]

在本发明的实施例中,地址寄存器550耦接至地址指令接口563、组选择引脚564及列地址锁存器551、行地址锁存器552、模式寄存器553以及组控制逻辑570。模式寄存器553耦接至控制逻辑501及放大器控制器554。列地址锁存器551耦接至列解码器512及列解码器522、写入放大器电路531及写入放大器电路541以及放大器控制器554。列解码器512及行解码器513经耦接至存储器组510。列解码器522及行解码器523经耦接至存储器组520。写入驱动器533经耦接至写入放大器电路531及写入放大器电路541,且经由多个输入线路571耦接至输入接口561。读取驱动器534耦接至读取放大器电路532及读取放大器电路542,且经由多个输出线路572耦接至输出接口562。写入放大器电路531及读取放大器532经由感测放大器511及多个内部输入/输出线路573耦接至存储器组510。写入放大器电路541及读取放大器542经由感测放大器521及多个内部输入/输出线路574耦接至存储器组520。

[0089]

在本发明的实施例中,存储器组510及存储器组520共用输入线路571以将用于部分写入的输入数据传输至存储器组510或存储器组520,且共用输出线路572以将输出数据自存储器组510或存储器组520传输至输出接口562。在本发明的实施例中,半导体存储器500可根据由组选择引脚564接收的组选择指令(1位)来选择存储器组510或存储器组520以执行存储器写入操作或存储器读取操作。具体而言,当地址寄存器550藉由组选择引脚564接收组选择指令时,地址寄存器550将组选择指令提供至组控制逻辑570,使得组控制逻辑570将组选择指令进一步提供至行地址锁存器552,且行地址锁存器552根据组选择指令来选择行解码器513及行解码器523。因此,行解码器513及行解码器523中的选定一个根据对应行地址来进一步判断数据写入区或数据读取区。

[0090]

在本发明的实施例中,存储器组510及存储器组520可独立操作。由于存储器组510及存储器组520共用输入线路571及输出线路572,半导体存储器500可操作存储器组510及存储器组520中的一个以藉由经由输入线路571接收输入数据来执行存储器写入操作,且同时操作存储器组510及存储器组520中的另一个以藉由经由输出线路572传输输出数据来执行存储器读取操作。尤其,半导体存储器500可选择存储器组510及存储器组520中的一个以执行部分写入模式。具体而言,当半导体存储器500的控制逻辑接收部分写入要求时,地址指令接口563的地址引脚的一部分接收列地址指令,地址引脚的另一部分中的至少一个接收操作码,且组选择引脚564接收组选择指令。另外,地址指令接口563的地址引脚的部分额外接收行地址指令。因此,地址寄存器550将列地址指令及操作码提供至列地址锁存器551及模式寄存器553,将行地址指令提供至行地址锁存器552,且将组选择指令提供至组控制逻辑570。组控制逻辑570将组选择指令提供至行地址锁存器552以选择行解码器513及行解码器523中的一个以判断存储器组510或存储器组520中的部分写入区。应注意,部分写入区藉由自列地址锁存器551接收列地址指令的列解码器512或列解码器522且藉由行解码器513及行解码器523中的选定一个判断。

[0091]

在本发明的实施例中,控制逻辑501将模式寄存器设置命令提供至模式寄存器

553,且模式寄存器553根据模式寄存器设置命令将模式选择信号提供至放大器控制器554,使得放大器控制器554根据模式选择信号来控制写入放大器电路531或写入放大器电路541以执行部分写入模式。列地址锁存器551将操作码提供至写入放大器电路531或写入放大器电路541,使得写入放大器电路531或写入放大器电路541由放大器控制器554控制以判断经由写入驱动器553接收输入数据并经由内部输入/输出线路573的一部分或内部输入/输出线路574的一部分将输入数据写入至存储器组510或存储器组520中。因此,本发明的半导体存储器500可选择经由内部输入/输出线路573的部分或内部输入/输出线路574的部分来输入数据写入至存储器组510或存储器组520中的部分写入区中,以便有效地减少由将所有内部输入/输出线路用于存储器写入造成的功耗。

[0092]

另外,可自图1至图4的实施例的相关描述习得对实施例的半导体存储器500的其他存储器特征、实施方案细节以及技术特征的充足教示及建议,且不重复其细节。

[0093]

图6为根据本发明的实施例的部分写入方法的流程图。参看图1及图6,图6的部分写入方法可至少适于图1的半导体存储器100。在步骤s610中,半导体存储器100在数据写入时段期间经由多个地址引脚的部分来接收列地址指令且经由地址引脚的另一部分中的至少一个来接收操作码。在步骤s620中,半导体存储器100根据操作码来判断用于传输输入数据的内部输入/输出线路173的部分。在步骤s630中,半导体存储器100根据操作码来操作写入放大器电路以执行部分写入模式以根据列地址指令经由多个内部输入/输出线路173的部分来将输入数据写入至存储器组中。因此,由于写入放大器电路131经由内部输入/输出线路173的部分将输入数据写入至存储器组110中的部分写入区中,实施图6的部分写入方法的半导体存储器100可有效地减少由将所有内部输入/输出线路用于存储器写入造成的功耗。

[0094]

另外,可自图1至图5的实施例的相关描述习得对实施例的半导体存储器100的其他存储器特征、实施方案细节以及技术特征的充足教示及建议,且不重复其细节。

[0095]

总之,在本发明的半导体存储器及其部分写入方法中能够在半导体存储器中的存储器组中的任何所选一个上执行部分写入模式,且半导体存储器不需要添加用于部分写入的引脚。本发明的半导体存储器能够有效地减少由将所有内部输入/输出线路用于存储器写入造成的功耗。

[0096]

本领域的技术人员将显而易见,在不偏离本发明的范围或精神的情况下,能够对所公开实施例作出各种修改及改变。鉴于是前述内容,本发明意欲覆盖修改及改变,前提为所述修改及改变属于权利要求书及其等效物的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1