能够调节数据和数据选通信号的定时的半导体设备的制作方法

1.各种实施方式总体上涉及集成电路技术,更具体地,涉及一种可与时钟信号同步操作的半导体设备和半导体系统。

背景技术:

2.电子装置可包括许多电子组件。例如,计算机系统可包括由半导体组成的大量半导体设备。构成计算机系统的半导体设备可在发送和接收时钟和数据时彼此通信。半导体设备可与时钟信号同步操作。半导体设备可发送和/或接收数据和数据选通信号,以便与其它半导体设备执行数据通信。数据选通信号可以是与发送数据的定时同步切换的时钟信号。因此,重要的是使数据和数据选通信号的定时匹配,使得半导体设备准确地发送和/或接收数据。然而,由于半导体设备的各种内部因素,在数据和数据选通信号的定时之间可能出现偏差。

技术实现要素:

3.在实施方式中,一种半导体设备可包括第一接收器、第一延迟线、第二接收器、第二延迟线、第一电压检测电路和第二电压检测电路。第一接收器可被配置为使用第一电源电压来接收输入信号。第一延迟线可被配置为基于第一延迟控制信号和第一互补延迟控制信号来延迟第一接收器的输出,以生成接收的信号。第二接收器可被配置为使用第二电源电压来接收时钟信号。第二延迟线可被配置为基于第二延迟控制信号和第二互补延迟控制信号来延迟第二接收器的输出,以生成接收的时钟信号。第一电压检测电路可被配置为接收第一电源电压作为正输入信号,接收第二电源电压作为负输入信号,并且比较第一电源电压和第二电源电压的电平以生成第一延迟控制信号和第一互补延迟控制信号。第二电压检测电路可被配置为接收第二电源电压作为正输入信号,接收第一电源电压作为负输入信号,并且比较第一电源电压和第二电源电压的电平以生成第二延迟控制信号和第二互补延迟控制信号。

4.在实施方式中,一种半导体设备可包括数据接收器、第一延迟线、选通接收器和第二延迟线。数据接收器可被配置为从第一电源线接收第一电源电压并且接收数据信号。第一延迟线可被配置为可变地延迟接收的数据信号以生成延迟的数据信号。选通接收器可被配置为从第二电源线接收第二电源电压并且接收数据选通信号。第二延迟线可被配置为可变地延迟接收的数据选通信号以生成延迟的数据选通信号。基于第一电源电压和第二电源电压来与第二延迟线的延迟量互补地改变第一延迟线的延迟量。

附图说明

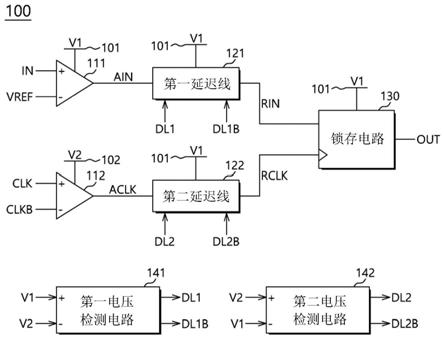

5.图1是示出根据实施方式的半导体设备的配置的图。

6.图2是示出图1所示的第一电压检测电路的配置的图。

7.图3是示出图1所示的第二电压检测电路的配置的图。

8.图4是示出根据实施方式的半导体设备的配置的图。

9.图5是示出根据实施方式的半导体系统的配置的图。

具体实施方式

10.图1是示出根据实施方式的半导体设备100的配置的图。参照图1,半导体设备100可接收输入信号in和时钟信号clk,并且基于输入信号in和时钟信号clk生成输出信号out。半导体设备100可延迟输入信号in和时钟信号clk,并且通过使延迟的输入信号与延迟的时钟信号同步来生成输出信号out。半导体设备100可使用不同的电源电压通过不同的路径接收输入信号in和时钟信号clk。输入信号in可与时钟信号clk同步接收。例如,输入信号in的电平可在时钟信号clk的边缘处改变。半导体设备100可使用第一电源电压v1接收输入信号in,并且通过第一延迟路径来延迟输入信号in。半导体设备100可使用第二电源电压v2接收时钟信号clk,并且通过第二延迟路径来延迟时钟信号clk。半导体设备100可通过与通过第二延迟路径延迟的时钟信号clk同步对通过第一延迟路径延迟的输入信号in进行采样来生成输出信号out。

11.半导体设备100可包括第一接收器111、第二接收器112、第一延迟线121和第二延迟线122。第一接收器111可接收输入信号in。第一接收器111还可接收基准电压vref。第一接收器111可通过对输入信号in和基准电压vref进行差分放大来生成放大的输入信号ain。基准电压vref可具有与输入信号in摆动的范围的中间对应的电压电平。第一接收器111可使用第一电源电压v1接收输入信号in。第一接收器111可接收第一电源电压v1和接地电压,并且将输入信号in和基准电压vref放大。第一接收器111可联接到第一电源线101,并且通过第一电源线101接收第一电源电压v1。第一电源线101可以是用于供应第一电源电压v1的电源网。

12.第二接收器112可接收时钟信号clk。第二接收器112还可接收互补时钟信号clkb。互补时钟信号clkb可具有与时钟信号clk相反的电压电平。第二接收器112可接收作为差分信号发送的时钟信号clk和互补时钟信号clkb。第二接收器112可通过对时钟信号clk和互补时钟信号clkb进行差分放大来生成放大的时钟信号aclk。第二接收器112可使用第二电源电压v2接收时钟信号clk。第二接收器112可接收第二电源电压v2和接地电压,并且将时钟信号clk和互补时钟信号clkb放大。第二接收器112可联接到第二电源线102,并且通过第二电源线102接收第二电源电压v2。第二电源线102可以是用于供应第二电源电压v2的电源网。第二电源线102可以是与第一电源线101分离的电源网。

13.第一延迟线121可联接到第一接收器111,并且接收第一接收器111的输出。第一延迟线121可以是用于延迟输入信号in的第一延迟路径。第一延迟线121可通过延迟第一接收器111的输出来生成接收的输入信号rin。第一延迟线121可通过可变地延迟放大的输入信号ain来生成接收的输入信号rin。第一延迟线121可联接到第一电源线101,并且通过从第一电源线101接收的第一电源电压v1来操作。第二延迟线122可联接到第二接收器112,并且接收第二接收器112的输出。第二延迟线122可以是用于延迟时钟信号clk的第二延迟路径。第二延迟线122可通过延迟第二接收器112的输出来生成接收的时钟信号rclk。第二延迟线122可通过可变地延迟放大的时钟信号aclk来生成接收的时钟信号rclk。第二延迟线122可联接到第一电源线101,并且通过从第一电源线101接收的第一电源电压v1来操作。

14.第一电源电压v1和第二电源电压v2可以是从外部电源电压生成的内部电压。第一电源电压v1和第二电源电压v2可被生成为具有基本上相同的电压电平。由于第一电源电压v1和第二电源电压v2通过不同的电源线供应,所以根据半导体设备100的操作环境,第一电源电压v1和第二电源电压v2可能难以保持相同的电压电平。当第一电源电压v1和第二电源电压v2没有保持相同的电平时,在接收的输入信号rin与接收的时钟信号rclk之间可能出现定时偏差。因此,尽管输入信号in和时钟信号clk以同步的定时输入到第一接收器111和第二接收器112,但是放大的输入信号ain和放大的时钟信号aclk可在不同的时间点生成。因此,在接收的输入信号rin与接收的时钟信号rclk之间可能出现相位差。第一电源电压v1与第二电源电压v2之间的相对电压电平差越大,定时偏差和/或相位差越大。当接收的输入信号rin与接收的时钟信号rclk之间的相位差增大时,半导体设备100可与接收的时钟信号rclk同步减小用于采样接收的输入信号rin的建立和保持时间。因此,半导体设备100可通过变化第一延迟线121和第二延迟线122的延迟量来补偿定时偏差和/或相位差。

15.半导体设备100可基于第一电源电压v1和第二电源电压v2来与第二延迟线122的延迟量互补地改变第一延迟线121的延迟量。可基于第一电源电压v1相对于第二电源电压v2的电压电平来改变第一延迟线121的延迟量。可根据第一电源电压v1是否具有高于或低于第二电源电压v2的电压电平来改变第一延迟线121的延迟量。可基于第二电源电压v2相对于第一电源电压v1的电压电平来改变第二延迟线122的延迟量。可根据第二电源电压v2是否具有高于或低于第一电源电压v1的电压电平来改变第二延迟线122的延迟量。

16.第一延迟线121可接收第一延迟控制信号dl1,并且可基于第一延迟控制信号dl1改变第一延迟线121的延迟量。可基于第一电源电压v1相对于第二电源电压v2的电压电平来生成第一延迟控制信号dl1。第一延迟线121还可接收第一互补延迟控制信号dl1b,并且可基于第一互补延迟控制信号dl1b与第一延迟控制信号dl1来改变第一延迟线121的延迟量。可基于第二电源电压v2相对于第一电源电压v1的电压电平来生成第一互补延迟控制信号dl1b。第一延迟线121的延迟量可基于第一延迟控制信号dl1而增大,并且基于第一互补延迟控制信号dl1b而减小。然而,根据第一延迟控制信号dl1和第一互补延迟控制信号dl1b改变第一延迟线121的延迟量的方法和/或操作不限于此。

17.第二延迟线122可接收第二延迟控制信号dl2,并且可基于第二延迟控制信号dl2来改变第二延迟线122的延迟量。可基于第二电源电压v2相对于第一电源电压v1的电压电平来生成第二延迟控制信号dl2。第二延迟线122还可接收第二互补延迟控制信号dl2b,并且可基于第二互补延迟控制信号dl2b与第二延迟控制信号dl2来改变第二延迟线122的延迟量。可基于第一电源电压v1相对于第二电源电压v2的电压电平来生成第二互补延迟控制信号dl2b。第二延迟线122的延迟量可基于第二延迟控制信号dl2而增大,并且基于第二互补延迟控制信号dl2b而减小。然而,根据第二延迟控制信号dl2和第二互补延迟控制信号dl2b改变第二延迟线122的延迟量的方法和/或操作不限于此。

18.第一延迟控制信号dl1、第一互补延迟控制信号dl1b、第二延迟控制信号dl2和第二互补延迟控制信号dl2b可以是模拟电压信号。第一延迟线121和第二延迟线122可以是电压控制的延迟线,并且可基于作为模拟电压信号的第一延迟控制信号dl1、第一互补延迟控制信号dl1b、第二延迟控制信号dl2和第二互补延迟控制信号dl2b来改变第一延迟线121和第二延迟线122的延迟量。在实施方式中,第一延迟线121和第二延迟线122可以是数字控制

的延迟线。第一延迟线121和第二延迟线122可另外包括被配置为将作为模拟电压信号的第一延迟控制信号dl1、第一互补延迟控制信号dl1b、第二延迟控制信号dl2和第二互补延迟控制信号dl2b转换为数字信号的模数转换器。可基于数字信号来改变第一延迟线121和第二延迟线122的延迟量。

19.半导体设备100还可包括锁存电路130。锁存电路130可联接到第一延迟线121,并且接收从第一延迟线121输出的接收的输入信号rin。锁存电路130可联接到第二延迟线122,并且接收从第二延迟线122输出的接收的时钟信号rclk。锁存电路130可与接收的时钟信号rclk同步地采样接收的输入信号rin。锁存电路130可与接收的时钟信号rclk同步地输出接收的输入信号rin作为输出信号out。锁存电路130可通过其输入端子接收所接收的输入信号rin,通过其时钟端子接收所接收的时钟信号rclk,并且通过其输出端子输出输出信号out。锁存电路130可联接到第一电源线101,并且由通过第一电源线101接收的第一电源电压v1来操作。

20.半导体设备100还可包括第一电压检测电路141和第二电压检测电路142。第一电压检测电路141可基于第一电源电压v1和第二电源电压v2来生成第一延迟控制信号dl1和第一互补延迟控制信号dl1b。第一电压检测电路141可接收第一电源电压v1作为正输入信号,并且接收第二电源电压v2作为负输入信号。第一电压检测电路141可通过比较第一电源电压v1和第二电源电压v2的电压电平来生成第一延迟控制信号dl1和第一互补延迟控制信号dl1b。第二电压检测电路142可基于第一电源电压v1和第二电源电压v2来生成第二延迟控制信号dl2和第二互补延迟控制信号dl2b。第二电压检测电路142可接收第二电源电压v2作为正输入信号,并且接收第一电源电压v1作为负输入信号。第二电压检测电路142可通过比较第二电源电压v2和第一电源电压v1的电压电平来生成第二延迟控制信号dl2和第二互补延迟控制信号dl2b。第一电压检测电路141和第二电压检测电路142可具有相同的电路结构,并且互补地接收第一电源电压v1和第二电源电压v2。因此,第一延迟控制信号dl1可与第二延迟控制信号dl2具有互补关系,并且第一互补延迟控制信号dl1b可与第二互补延迟控制信号dl2b具有互补关系。

21.图2是示出图1所示的第一电压检测电路141的配置的图。参照图2,第一电压检测电路141可包括分压器211、分压器212、第一比较器221和第二比较器222。分压器211可接收第一电源电压v1,并且通过对第一电源电压v1进行分压来生成第一分压电压dv1。例如,第一分压电压dv1可具有与第一电源电压v1的一半对应的电压电平。分压器212可接收第二电源电压v2,并且通过对第二电源电压v2进行分压来生成第二分压电压dv2。例如,第二分压电压dv2可具有与第二电源电压v2的一半对应的电压电平。

22.第一比较器221可通过其正输入端子(+)接收第一分压电压dv1,并且通过其负输入端子(-)接收第二分压电压dv2。第一比较器221可通过比较第一分压电压dv1和第二分压电压dv2的电压电平来生成第一延迟控制信号dl1。第二比较器222可通过其正输入端子(+)接收第二分压电压dv2,并且通过其负输入端子(-)接收第一分压电压dv1。第二比较器222可通过比较第一分压电压dv1和第二分压电压dv2的电压电平来生成第一互补延迟控制信号dl1b。

23.图3是示出图1所示的第二电压检测电路142的配置的图。参照图2,第二电压检测电路142可包括分压器311、分压器312、第三比较器321和第四比较器322。分压器311可接收

第一电源电压v1,并且通过对第一电源电压v1进行分压来生成第一分压电压dv1。分压器312可接收第二电源电压v2,并且通过对第二电源电压v2进行分压来生成第二分压电压dv2。在实施方式中,分压器可仅安装在第一电压检测电路141和第二电压检测电路142中的任一个中,并且第一至第四比较器221、222、321和322可被修改为共同接收第一分压电压dv1和第二分压电压dv2。在实施方式中,分压器可设置在第一电压检测电路141和第二电压检测电路142的外部,第一电压检测电路141可仅由第一比较器221和第二比较器222组成,并且第二电压检测电路142可仅由第三比较器321和第四比较器322组成。

24.第三比较器321可通过其正输入端子(+)接收第二分压电压dv2,并且通过其负输入端子(-)接收第一分压电压dv1。第三比较器321可通过比较第一分压电压dv1和第二分压电压dv2的电压电平来生成第二延迟控制信号dl2。由于第三比较器321以与第一比较器221相反的方式接收第一分压电压dv1和第二分压电压dv2,所以第二延迟控制信号dl2可与第一延迟控制信号dl1具有互补关系。第四比较器322可通过其正输入端子(+)接收第一分压电压dv1,并且通过其负输入端子(-)接收第二分压电压dv2。第四比较器322可通过比较第一分压电压dv1和第二分压电压dv2的电压电平来生成第二互补延迟控制信号dl2b。由于第四比较器322以与第二比较器222相反的方式接收第一分压电压dv1和第二分压电压dv2,所以第二互补延迟控制信号dl2b可与第一互补延迟控制信号dl1b具有互补关系。

25.图4是示出根据实施方式的半导体设备400的配置的图。参照图4,半导体设备400可从外部装置接收数据信号和数据选通信号并且生成内部数据信号。半导体设备400可包括第一数据焊盘401、第二数据焊盘402、第三数据焊盘403、第四数据焊盘404、第一选通焊盘405和第二选通焊盘406。第一数据焊盘401可联接到从外部装置发送第一数据信号dq1的数据传输线,并且半导体设备400可通过第一数据焊盘401接收第一数据信号dq1。第二数据焊盘402可联接到从外部装置发送第二数据信号dq2的数据传输线,并且半导体设备400可通过第二数据焊盘402接收第二数据信号dq2。第三数据焊盘403可联接到从外部装置发送第三数据信号dq3的数据传输线,并且半导体设备400可通过第三数据焊盘403接收第三数据信号dq3。第四数据焊盘404可联接到从外部装置发送第四数据信号dq4的数据传输线,并且半导体设备400可通过第四数据焊盘404接收第四数据信号dq4。图4示出半导体设备400通过四个数据焊盘接收四个数据信号,但本实施方式不限于此。包括在半导体设备400中的数据焊盘的数量和通过数据焊盘接收的数据信号的数量可被设定为8、16、32或更多。第一选通焊盘405可联接到从外部装置发送数据选通信号dqs的数据选通传输线,并且半导体设备400可通过第一选通焊盘405接收数据选通信号dqs。第二选通焊盘406可联接到从外部装置发送互补数据选通信号dqsb的数据选通传输线,并且半导体设备400可通过第二选通焊盘406接收互补数据选通信号dqsb。

26.半导体设备400可包括第一数据接收器411、第二数据接收器412、第三数据接收器413、第四数据接收器414和选通接收器415。第一数据接收器411可联接到第一数据焊盘401,并且通过第一数据焊盘401接收第一数据信号dq1。第一数据接收器411可使用基准电压vref来接收第一数据信号dq1。基准电压vref可具有与第一数据信号dq1至第四数据信号dq4摆动的范围的中间对应的电压电平。第二数据接收器412可联接到第二数据焊盘402,并且通过第二数据焊盘402接收第二数据信号dq2。第二数据接收器412可使用基准电压vref来接收第二数据信号dq2。第三数据接收器413可联接到第三数据焊盘403,并且通过第三数

据焊盘403接收第三数据信号dq3。第三数据接收器413可使用基准电压vref来接收第三数据信号dq3。第四数据接收器414可联接到第四数据焊盘404,并且通过第四数据焊盘404接收第四数据信号dq4。第四数据接收器414可使用基准电压vref来接收第四数据信号dq4。图1所示的第一接收器111可作为第一数据接收器411至第四数据接收器414中的每一个来应用。第一数据接收器411至第四数据接收器414可通过供应给其的第一电源电压v1来操作。选通接收器415可联接到第一选通焊盘405和第二选通焊盘406,并且接收数据选通信号dqs和互补数据选通信号dqsb。选通接收器415可通过对数据选通信号dqs和互补数据选通信号dqsb进行差分放大来接收数据选通信号dqs。图1所示的第二接收器112可作为选通接收器415来应用。选通接收器415可通过供应给其的第二电源电压v2来操作。

27.半导体设备400可包括第一中继器421、第二中继器422、第三中继器423、第四中继器424、第五中继器425、第六中继器426、第一延迟线431、第二延迟线432、第三延迟线433、第四延迟线434、第五延迟线435和第六延迟线436。第一延迟线431至第四延迟线434可用作数据延迟线,并且第五延迟线435和第六延迟线436可用作选通延迟线。第一中继器421和第一延迟线431可用作第一数据信号dq1的延迟路径。第一中继器421可驱动通过第一数据接收器411接收的第一数据信号dq1,并且第一延迟线431可通过延迟第一数据信号dq1来生成第一延迟数据信号ddq1。第二中继器422和第二延迟线432可用作第二数据信号dq2的延迟路径。第二中继器422可驱动通过第二数据接收器412接收的第二数据信号dq2,并且第二延迟线432可通过延迟第二数据信号dq2来生成第二延迟数据信号ddq2。第三中继器423和第三延迟线433可用作第三数据信号dq3的延迟路径。第三中继器423可驱动通过第三数据接收器413接收的第三数据信号dq3,并且第三延迟线433可通过延迟第三数据信号dq3来生成第三延迟数据信号ddq3。第四中继器424和第四延迟线434可用作第四数据信号dq4的延迟路径。第四中继器424可驱动通过第四数据接收器414接收的第四数据信号dq4,并且第四延迟线434可通过延迟第四数据信号dq4来生成第四延迟数据信号ddq4。第五中继器425、第六中继器426、第五延迟线435和第六延迟线436可用作数据选通信号dqs的延迟路径。第五中继器425和第六中继器426中的每一个可驱动数据选通信号dqs,并且第五延迟线43和第六延迟线436中的每一个可通过延迟数据选通信号dqs来生成延迟的数据选通信号ddqs。

28.半导体设备400可包括第一锁存电路441、第二锁存电路442、第三锁存电路443和第四锁存电路444。第一锁存电路441可联接到第一延迟线431和第五延迟线435,从第一延迟线431接收第一延迟数据信号ddq1,并且从第五延迟线435接收延迟的数据选通信号ddqs。第一锁存电路441可与延迟的数据选通信号ddqs同步对第一延迟数据信号ddq1进行采样,并且输出采样的信号作为第一内部数据信号di1。第二锁存电路442可联接到第二延迟线432和第五延迟线435,从第二延迟线432接收第二延迟数据信号ddq2,并且从第五延迟线435接收延迟的数据选通信号ddqs。第二锁存电路442可与延迟的数据选通信号ddqs同步对第二延迟数据信号ddq2进行采样,并且输出采样的信号作为第二内部数据信号di2。第三锁存电路443可联接到第三延迟线433和第六延迟线436,从第三延迟线433接收第三延迟数据信号ddq3,并且从第六延迟线436接收延迟的数据选通信号ddqs。第三锁存电路443可与延迟的数据选通信号ddqs同步对第三延迟数据信号ddq3进行采样,并且输出采样的信号作为第三内部数据信号di3。第四锁存电路444可联接到第四延迟线434和第六延迟线436,从第四延迟线434接收第四延迟数据信号ddq4,并且从第六延迟线436接收延迟的数据选通信

号ddqs。第四锁存电路444可与延迟的数据选通信号ddqs同步对第四延迟数据信号ddq4进行采样,并且输出采样的信号作为第四内部数据信号di4。图1所示的锁存电路130可作为第一锁存电路441至第四锁存电路444中的每一个来应用。

29.半导体设备400可包括第一数据电压检测电路451、第二数据电压检测电路452和选通电压检测电路453。第一数据电压检测电路451可接收第一电源电压v1和第二电源电压v2,并且生成第一数据延迟控制信号ddl1和第一互补数据延迟控制信号ddl1b。第一数据电压检测电路451可接收第一电源电压v1作为正输入信号,并且接收第二电源电压v2作为负输入信号。第一数据电压检测电路451可基于第一电源电压v1相对于第二电源电压v2的电压电平来生成第一数据延迟控制信号ddl1,并且基于第二电源电压v2相对于第一电源电压v1的电压电平来生成第一互补数据延迟控制信号ddl1b。图1和图2所示的第一电压检测电路141可作为第一数据电压检测电路451来应用。可基于第一数据延迟控制信号ddl1和第一互补数据延迟控制信号ddl1b来改变第一延迟线431和第二延迟线432的延迟量。

30.第二数据电压检测电路452可接收第一电源电压v1和第二电源电压v2,并且生成第二数据延迟控制信号ddl2和第二互补数据延迟控制信号ddl2b。第二数据电压检测电路452可接收第一电源电压v1作为正输入信号,并且接收第二电源电压v2作为负输入信号。第二数据电压检测电路452可基于第一电源电压v1相对于第二电源电压v2的电压电平来生成第二数据延迟控制信号ddl2,并且基于第二电源电压v2相对于第一电源电压v1的电压电平来生成第二互补数据延迟控制信号ddl2b。图1和图2所示的第一电压检测电路141可作为第二数据电压检测电路452来应用。可基于第二数据延迟控制信号ddl2和第二互补数据延迟控制信号ddl2b来改变第三延迟线433和第四延迟线434的延迟量。

31.选通电压检测电路453可接收第一电源电压v1和第二电源电压v2,并且生成选通延迟控制信号sdl1和互补选通延迟控制信号sdl1b。选通电压检测电路453可接收第二电源电压v2作为正输入信号,并且接收第一电源电压v1作为负输入信号。选通电压检测电路453可基于第二电源电压v2相对于第一电源电压v1的电压电平来生成选通延迟控制信号sdl1,并且基于第一电源电压v1相对于第二电源电压v2的电压电平来生成互补选通延迟控制信号sdl1b。图1和图3所示的第二电压检测电路142可作为选通电压检测电路453来应用。可基于选通延迟控制信号sdl1和互补选通延迟控制信号sdl1b来改变第五延迟线和第六延迟线的延迟量。

32.第一数据电压检测电路451可设置在选通电压检测电路453的左侧,并且第二数据电压检测电路452可设置在选通电压检测电路453的右侧。第一数据电压检测电路451可与设置有第一数据焊盘401、第二数据焊盘402、第一延迟线431和第二延迟线432的区域相邻设置。选通电压检测电路453可与设置有第一选通焊盘405、第二选通焊盘406、第五延迟线435和第六延迟线436的区域相邻设置。第二数据电压检测电路452可与设置有第三数据焊盘403、第四数据焊盘404、第三延迟线433和第四延迟线434的区域相邻设置。第一电源电压v1可通过第一电源线共同供应给第一数据电压检测电路451、第二数据电压检测电路452和选通电压检测电路453,并且第二电源电压v2可通过与第一电源线分离的第二电源线来共同供应给第一数据电压检测电路451、第二数据电压检测电路452和选通电压检测电路453。然而,可根据设置有电压检测电路的区域发生不同的ir降和/或欧姆降,并且由电压检测电路接收的第一电源电压v1和第二电源电压v2的电平变化可改变。半导体设备400可包括分

别与接收数据信号和数据选通信号的区域相邻的多个电压检测电路,并且通过多个电压检测电路生成不同的延迟控制信号,从而为各个延迟线设定最佳延迟量,而不管pvt(工艺、电压和温度)变化如何。

33.图5是示出根据实施方式的半导体系统500的配置的图。参照图5,半导体系统500可包括第一半导体设备510和第二半导体设备520。第一半导体设备510可提供用于操作第二半导体设备520的各种控制信号。第一半导体设备510可包括各种类型的主机装置。例如,第一半导体设备510可包括cpu(中央处理单元)、gpu(图形处理单元)、mmp(多媒体处理器)、数字信号处理器、ap(应用处理器)和存储控制器。例如,第二半导体设备520可以是存储器设备。存储器设备可包括易失性存储器和非易失性存储器。易失性存储器可包括sram(静态ram)、dram(动态ram)和sdram(同步dram),非易失性存储器可包括rom(只读存储器)、prom(可编程rom)、eeprom(电可擦除可编程rom)、eprom(电可编程rom)、闪存、pram(相变ram)、mram(磁ram)、rram(电阻ram)和fram(铁电ram)。

34.第二半导体设备520可通过多条总线联接到第一半导体设备510。多条总线可以是用于发送信号的信号传输路径、链路或通道。多条总线可包括数据总线501和数据选通总线502。数据总线501和数据选通总线502可以是双向总线。数据总线501可包括多条数据传输线,并且数据选通总线502可包括多条数据选通传输线。第一半导体设备510和第二半导体设备520可通过数据总线501和数据选通总线502执行写操作和读操作。写操作可指示将数据从第一半导体设备510发送到第二半导体设备520的操作,读操作可指示将数据从第二半导体设备520发送到第一半导体设备510的操作。在写操作期间,第一半导体设备510可通过数据总线501将数据dq发送到第二半导体设备520。第一半导体设备510可通过数据选通总线502将数据选通信号dqs和互补数据选通信号dqsb发送到第二半导体设备520。在读操作期间,第二半导体设备520可通过数据总线501将数据dq输出到第一半导体设备510。第二半导体设备520可通过数据选通总线502将数据选通信号dqs和互补数据选通信号dqsb发送到第一半导体设备510。尽管未示出,第二半导体设备520可通过命令总线、地址总线、时钟总线等联接到第一半导体设备510。命令总线、地址总线和时钟总线可以是单向总线。第一半导体设备510可通过命令总线将命令信号提供给第二半导体设备520。第一半导体设备510可通过地址总线将地址信号提供给第二半导体设备520。第一半导体设备510可通过时钟总线将系统时钟信号提供给第二半导体设备520。

35.第一半导体设备510可包括数据发送电路511、数据接收电路512、选通发送电路513和选通接收电路514。数据发送电路511可联接到数据总线501,并且基于第一半导体设备510的内部数据din1来驱动数据总线501并通过数据总线501发送数据dq。数据接收电路512可联接到数据总线501,并且通过数据总线501接收从第二半导体设备520发送的数据dq。数据接收电路512可基于数据dq来生成第一半导体设备510的内部数据din1。选通发送电路513可联接到数据选通总线502,并且基于写数据选通信号wdqs来驱动数据选通总线502并通过数据选通总线502将数据选通信号dqs和互补数据选通信号dqsb发送到第二半导体设备520。选通接收电路514可联接到数据选通总线502,并且通过数据选通总线502接收从第二半导体设备520发送的数据选通信号dqs和互补数据选通信号dqsb。选通接收电路514可基于数据选通信号dqs和互补数据选通信号dqsb来生成读数据选通信号rdqs。从数据发送电路511输出的数据dq的定时可与从选通发送电路513输出的数据选通信号dqs的定时

同步。从第二半导体设备520发送的数据dq和数据选通信号dqs的定时可彼此同步,并且数据接收电路512可基于读数据选通信号rdqs对通过数据总线501接收的数据dq进行采样。

36.第二半导体设备520可包括数据发送电路521、数据接收电路522、选通发送电路523和选通接收电路524。数据发送电路521可联接到数据总线501,并且基于第二半导体设备520的内部数据din2来驱动数据总线501并通过数据总线501发送数据dq。数据接收电路522可联接到数据总线501,并且通过数据总线501接收从第一半导体设备510发送的数据dq。数据接收电路522可基于数据dq来生成第二半导体设备520的内部数据din2。选通发送电路523可联接到数据选通总线502,并且基于读数据选通信号rdqs来驱动数据选通总线502并通过数据选通总线502将数据选通信号dqs和互补数据选通信号dqsb发送到第一半导体设备510。选通接收电路524可联接到数据选通总线502,并且通过数据选通总线502接收从第一半导体设备510发送的数据选通信号dqs和互补数据选通信号dqsb。选通接收电路524可基于数据选通信号dqs和互补数据选通信号dqsb来生成写数据选通信号wdqs。从数据发送电路521输出的数据dq的定时可与从选通发送电路523输出的数据选通信号dqs的定时同步。从第一半导体设备510发送的数据dq和数据选通信号dqs的定时可彼此同步,并且数据接收电路522可基于写数据选通信号wdqs对通过数据总线501接收的数据dq进行采样。

37.数据接收电路522可通过供应给其的第一电源电压v1来操作。选通接收电路524可通过供应给其的第二电源电压v2和第一电源电压v1来操作。因此,当第一电源电压v1与第二电源电压v2之间出现电压电平差时,在写数据选通信号wdqs与通过数据接收电路522接收的数据之间可能出现定时偏差和/或相位差。数据接收电路522可基于第一电源电压v1和第二电源电压v2的电压电平来可变地延迟接收的数据。数据接收电路522可基于数据延迟控制信号ddl和互补数据延迟控制信号ddlb来调节接收的数据被延迟的时间。选通接收电路524可通过基于第一电源电压v1和第二电源电压v2的电压电平可变地延迟接收的数据选通信号来生成写数据选通信号wdqs。选通接收电路524可基于选通延迟控制信号sdl和互补选通延迟控制信号sdlb来调节接收的数据选通信号dqs被延迟的时间。

38.第二半导体设备520还可包括数据电压检测电路525和选通电压检测电路526。数据电压检测电路525可通过检测第一电源电压v1和第二电源电压v2的电压电平来生成数据延迟控制信号ddl和互补数据延迟控制信号ddlb。选通电压检测电路526可通过检测第一电源电压v1和第二电源电压v2的电压电平来生成选通延迟控制信号sdl和互补选通延迟控制信号sdlb。数据电压检测电路525和选通电压检测电路526可具有相同的电路结构,但是互补地接收第一电源电压v1和第二电源电压v2并生成具有互补特性的延迟控制信号。例如,数据电压检测电路525可接收第一电源电压v1作为正输入信号,并且接收第二电源电压v2作为负输入信号。选通电压检测电路526可接收第二电源电压v2作为正输入信号,并且接收第一电源电压v1作为负输入信号。因此,数据延迟控制信号ddl和选通延迟控制信号sdl可具有彼此互补的特性,并且互补数据延迟控制信号ddlb和互补选通延迟控制信号sdlb可具有彼此互补的特性。因此,尽管第一电源电压v1与第二电源电压v2之间出现电压电平差,但是通过数据接收电路522接收的数据的定时可与写数据选通信号wdqs的定时匹配,并且数据接收电路522可确保足以利用写数据选通信号wdqs对接收的数据进行采样的建立和保持时间。

39.第二半导体设备520还可包括内部电压生成电路527。内部电压生成电路527可从

外部电源接收外部电源电压vext,并且基于外部电源电压vext来生成第一电源电压v1和第二电源电压v2。通过内部电压生成电路527生成的第一电源电压v1和第二电源电压v2可具有基本上相同的电压电平。在实施方式中,第一半导体设备510的数据接收电路512和选通接收电路514可被修改以按照与第二半导体设备520的数据接收电路522和选通接收电路524相似的方式操作。第一半导体设备510还可包括与数据电压检测电路525和选通电压检测电路526对应的组件。

40.尽管上面描述了各种实施方式,但是本领域技术人员将理解,所描述的实施方式仅用作示例。因此,不应基于所描述的实施方式限制本文所描述的半导体设备和半导体系统。

41.相关申请的交叉引用

42.本申请要求2019年12月26日提交于韩国知识产权局的韩国申请号10-2019-0175054的优先权,其整体通过引用并入本文。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1