半导体存储装置的制作方法

1.实施方式涉及一种半导体存储装置。

背景技术:

2.作为能够非易失地存储数据的半导体存储装置,已知有nand(与非)型闪速存储器。

技术实现要素:

3.实施方式提供能够简化芯片选择的半导体存储装置。

4.实施方式的半导体存储装置包含从存储器控制器接受第1信号的第1垫(pad)、从所述存储器控制器接受芯片使能信号的第2垫、以及第1控制电路。所述第1控制电路构成为:当在所述芯片使能信号被生效(assert)后接收读取指令顺序时,在所述芯片使能信号被生效的同时或之后且开始接收所述读取指令顺序之前,根据输入到所述第1垫的所述第1信号是否与芯片地址一致来将所述半导体存储装置设为使能(enable)状态或非使能(disable)状态。

附图说明

5.图1是用于说明第1实施方式的存储器系统的构成的框图。

6.图2是用于说明第1实施方式的nand控制器及nand闪速存储器的构成的框图。

7.图3是用于说明第1实施方式的nand闪速存储器的构成的俯视图。

8.图4是用于说明第1实施方式的nand闪速存储器的构成的剖视图。

9.图5是用于说明第1实施方式的存储胞阵列的构成的电路图。

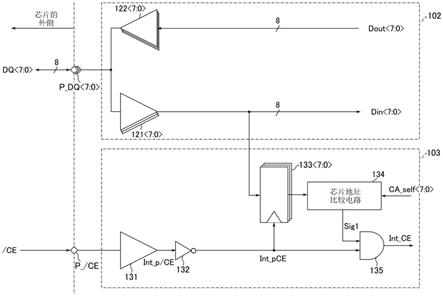

10.图6是用于说明第1实施方式的输入输出电路及逻辑控制电路的构成的框图。

11.图7是用于说明第1实施方式的存储器系统中的芯片选择动作的时序图。

12.图8是用于说明比较例的存储器系统中的读取动作的指令顺序。

13.图9是用于说明第1实施方式的存储器系统中的读取动作的指令顺序。

14.图10是用于说明第1实施方式的变化例的逻辑控制电路的构成的框图。

15.图11是用于说明第1实施方式的变化例的存储器系统中的芯片选择动作的时序图。

16.图12是用于说明第2实施方式的输入输出电路及逻辑控制电路的构成的框图。

17.图13是用于说明第2实施方式的存储器系统中的芯片选择动作的时序图。

18.图14是用于说明第2实施方式的变化例的逻辑控制电路的构成的框图。

19.图15是用于说明第2实施方式的变化例的存储器系统中的芯片选择动作的时序图。

20.图16是用于说明第3实施方式的输入输出电路及逻辑控制电路的构成的框图。

21.图17是用于说明第3实施方式的存储器系统中的芯片选择动作的时序图。

具体实施方式

22.以下,参考附图对实施方式进行说明。另外,以下的说明中,对具有相同功能及构成的构成要素附加共通的参考符号。而且,当要区分具有共通的参考符号的多个构成要素时,对该共通的参考符号附加下标来加以区分。另外,当不需要特别区分多个构成要素时,对该多个构成要素仅附加共通的参考符号,而不附加下标。当构成要素与x比特的比特序列(bit sequence)对应时,对该构成要素的参考符号附加<x-1:0>。当构成要素与x比特的比特序列的第y比特对应时,对该构成要素的参考符号附加<y-1>(1≦y≦x)。

23.1.第1实施方式

24.对第1实施方式进行说明。以下,以作为非易失性存储器的nand闪速存储器、及具备该nand闪速存储器的存储器系统为例进行说明。

25.1.1构成

26.对第1实施方式的存储器系统的构成进行说明。

27.1.1.1存储器系统

28.首先,使用图1对包含第1实施方式的存储器系统的构成的概要进行说明。

29.如图1所示,存储器系统1具备多个nand闪速存储器(图1中记载为“nand”)100(100a-1、100a-2、

…

、100a-k、100b-1、100b-2、

…

、100b-k、100c-1、100c-2、

…

、100c-k、100d-1、100d-2、

…

、及100d-k)、以及存储器控制器200(k为2以上的整数)。各nand闪速存储器100是例如存储器芯片,作为半导体存储装置发挥功能。而且,如后述那样共通地连接的多个nand闪速存储器100(多个存储器芯片)也可作为一个半导体存储装置发挥功能。多个nand闪速存储器100与存储器控制器200例如可通过它们的组合构成一个存储器系统1,作为其例,可列举如sdtm(sd(secure digital,安全数字)

tm

,注册商标)卡那样的存储卡或ssd(solid state drive,固态驱动器)等。而且,存储器系统1也可应用于将多个nand闪速存储器100用作存储介质的数据库或大数据处理系统。以下的说明中,将多个nand闪速存储器100中的任意一个称作“nand闪速存储器100”。而且,将经由信道cha的nand闪速存储器总线而共通地连接的多个nand闪速存储器100中的任意一个称作“nand闪速存储器100a”。

30.nand闪速存储器100是具备多个存储胞且非易失地存储数据的非易失性存储器。存储器控制器200通过nand总线而连接于nand闪速存储器100,且通过主机总线而连接于主机设备300。而且,存储器控制器200控制nand闪速存储器100,且响应从主机设备300接收到的命令,向nand闪速存储器100访问。

31.主机设备300是例如数字相机或个人计算机等,主机总线是例如符合sd

tm

接口、sas(serial attached scsi(small computer system interface)串行连接的小型计算机系统接口)、sata(serial ata(advanced technology attachment),串行高级技术附件)、或pcie(peripheral component interconnect express,外围组件互连高速)标准的总线。

32.nand总线是例如符合sdr(single data rate,单数据速率)接口或触发ddr(double data rate,双数据速率)接口等标准的总线。

33.1.1.2存储器控制器

34.然后,使用图1对存储器控制器200的构成的详情进行说明。

35.存储器控制器200是例如soc(system on a chip,系统单芯片),具备主机接口电

路210、ram(random access memory,随机访问存储器)220、cpu(central processing unit,中央处理器)230、缓冲存储器240、及nand接口电路250。另外,以下说明的存储器控制器200的各部210-250的功能可由硬件构成或硬件资源与固件的组合的构成中的任一个实现。

36.主机接口电路210经由主机总线而与主机设备300连接,将从主机设备300接收到的命令及数据分别传输到cpu230及缓冲存储器240。而且,响应cpu230的命令,将缓冲存储器240内的数据传输到主机设备300。

37.ram220是例如dram等半导体存储器,且用作cpu230的作业区域。而且,ram220保存用于管理nand闪速存储器100的固件或各种管理表格等。

38.cpu230控制存储器控制器200整体的动作。例如,cpu230于从主机设备300接收到写入命令时,响应该写入命令,对nand接口电路250发行写入命令。读取处理及抹除处理时也同样。而且,cpu230执行用于管理nand闪速存储器100的各种处理。

39.缓冲存储器240暂时地保存写入数据或读取数据。

40.nand接口电路250经由nand总线而与nand闪速存储器100连接,且负责与nand闪速存储器100的通信。然后,基于从cpu230接收到的命令将各种信号输出到nand闪速存储器100。而且,写入处理时,将由cpu230发行的写入指令、及缓冲存储器240内的写入数据作为输入信号传输到nand闪速存储器100。进而,读取处理时,将由cpu230发行的读取指令作为输入信号传输到nand闪速存储器100,进而将从nand闪速存储器100读取的数据作为输出信号接收,并将其传输到缓冲存储器240。

41.更具体来说,nand接口电路250包含多个nand控制器(图1中记载为“cnt”)250a、250b、250c、及250d。多个nand控制器250a、250b、250c、及250d的各个与包含多个nand闪速存储器100中的一些的nand闪速存储器100的组相关联,并负责与该相关联的nand闪速存储器100的组的数据的收发。图1的例中,nand控制器250a经由信道cha的nand总线而与多个nand闪速存储器100a-1、100a-2、

…

、及100a-k共通地连接。nand控制器250b经由信道chb的nand总线而与多个nand闪速存储器100b-1、100b-2、

…

、及100b-k共通地连接。nand控制器250c经由信道chc的nand总线而与多个nand闪速存储器100c-1、100c-2、

…

、及100c-k共通地连接。nand控制器250d经由信道chd的nand总线而与多个nand闪速存储器100d-1、100d-2、

…

、及100d-k共通地连接。

42.如以上那样构成的nand控制器250a如所述那样,经由nand总线连接于nand闪速存储器100a-1~100a-k。

43.1.1.3 nand闪速存储器

44.接下来,参考图2、图3及图4对nand闪速存储器100的构成进行说明。另外,图2中,经由信道cha的nand闪速存储器总线而与nand控制器250a共通地连接的多个nand闪速存储器100a-1~100a-k的连接关系作为一例而示出,但关于nand控制器25-b与多个nand闪速存储器100b-1~100b-k、nand闪速存储器控制器250c与多个nand闪速存储器100c-1~100c-k、及nand控制器250d与多个nand闪速存储器100d-1~100d-k,也具有相同的连接关系。而且,图2中,nand闪速存储器100a-1的构成作为一例而示出,关于其他nand闪速存储器100a-2~100a-k、100b-1~100b-k、100c-1~100c-k、及100d-1~100d-k,也具有与nand闪速存储器100a-1相同的构成。

45.如图2所示,nand闪速存储器100具备存储胞阵列101、输入输出电路102、逻辑控制电路103、地址寄存器104、指令寄存器105、定序器106、电压产生电路107、驱动器组108、行解码器109、及感测放大器模块110。nand闪速存储器100的各要素也可形成于一个芯片之中,但不限于此。也可通过将各要素分开形成于多个芯片,并将它们相互连接,而构成nand闪速存储器100。例如,通过将存储胞阵列101形成于一个芯片之中,将其以外的要素形成于另一个芯片之中,并将这些芯片贴合,而构成nand闪速存储器100。

46.存储胞阵列101包含各自与位线及字线建立关联的多个非易失性的存储胞晶体管的集合即多个区块blk。区块blk例如为数据的抹除单位。图2中,图示4个区块blk0~blk3作为一例。存储胞阵列101例如可预先存储唯一地识别自身的nand闪速存储器100(图2的例中nand闪速存储器100a-1)的芯片地址ca_self(未图示)。芯片地址ca_self例如可由8比特构成。

47.输入输出电路102例如具有输入输出用垫p_dq<7:0>、选通信号用垫p_dqs及p_/dqs,与存储器控制器200之间收发8比特的输入输出信号dq<7:0>、信号dqs及/dqs。输入输出信号dq<7:0>包含数据dat、地址add、及指令cmd等。信号dqs为选通信号。信号/dqs为信号dqs的反转信号。输入输出电路102将信号dq<7:0>内的地址add及指令cmd分别传输到地址寄存器104及指令寄存器105。输入输出电路102与感测放大器模块110收发写入数据及读取数据dat。

48.逻辑控制电路103具有控制用垫p_/ce、p_cle、p_ale、p_/we、p_re、p_/re、及p_/wp,从存储器控制器200接收信号/ce、cle、ale、/we、re、/re、及/wp。而且,逻辑控制电路103具有状态通知用垫p_/rb,将信号/rb传输到存储器控制器200并将nand闪速存储器100的状态通知给外部。

49.信号/ce是用于将nand闪速存储器100设为使能状态的信号,通过切换为“l(low,低)”电平而生效。使能状态的nand闪速存储器100构成为例如识别出其他信号cle、ale、/we、re、/re、/wp、dq<7:0>、dqs、及/dqs为指向自身的信号并将这些信号取入至内部,将信号/rb发送至存储器控制器200。

50.而且,信号/ce通过切换为“h(高)”电平而否定,使nand闪速存储器100成为非使能状态。非使能状态例如包含省电(待机)模式,例如可停止nand闪速存储器100内的除最低限度的构成要素的外的部分的功能。也就是说,非使能状态的nand闪速存储器100构成为例如识别出其他信号cle、ale、/we、re、/re、/wp、dq<7:0>、dqs、及/dqs为未指向自身的信号且不将这些信号取入至内部,停止信号/rb的发送。

51.以下的说明中,将如下动作称作“芯片选择动作”,即,在连接于同一nand控制器250a的多个nand闪速存储器100a-1~100a-k中,选择哪个nand闪速存储器100a成为使能状态。

52.信号cle及ale是将向nand闪速存储器100的输入信号dq<7:0>分别为指令及地址通知给nand闪速存储器100的信号。具体来说,例如,在信号cle及ale分别为“h(high)”电平及“l”电平的情况下,将输入信号dq<7:0>为指令cmd通知给nand闪速存储器100,在分别为“l”电平及“h”电平的情况下,将输入信号dq<7:0>为地址add通知给nand闪速存储器100。而且,在信号cle及ale均为“l”电平的情况下,将输入信号dq<7:0>为数据dat通知给nand闪速存储器100。

53.信号/we是以“l”电平被生效且用于将输入信号dq<7:0>取入至nand闪速存储器100的信号。信号/re是以“l”电平被生效且用于从nand闪速存储器100读取输出信号dq<7:0>的信号。信号re是信号/re的反转信号。信号/wp是以“l”电平被生效且用于禁止向nand闪速存储器100写入的信号。

54.信号/rb是表示nand闪速存储器100是就绪状态(可接收来自存储器控制器200的命令的状态)还是忙碌状态(无法接收来自存储器控制器200的命令的状态)的信号,“l”电平表示忙碌状态。在信号/rb为忙碌状态的情况下,即使信号/ce被否定,使能状态的nand闪速存储器100也不会切换为待机模式。

55.nand控制器250a使用共通的信号线而与nand闪速存储器100a-1~100a-k进行所述各种信号dq<7:0>、dqs、/dqs、/ce、cle、ale、/we、re、/re、/wp、及/rb的各个的通信。

56.地址寄存器104保存经由输入输出电路102从存储器控制器200接收到的地址add。该地址add中包含区块地址ba及页面地址pa。指令寄存器105保存经由输入输出电路102从存储器控制器200接收到的指令cmd。

57.定序器106基于保存在指令寄存器105的指令cmd,控制nand闪速存储器100整体的动作。

58.电压产生电路107产生读取动作、写入动作、抹除动作等中使用的电压。驱动器组108将由电压产生电路107产生的电压供给至存储胞阵列101、行解码器109、及感测放大器模块110。

59.行解码器109基于地址寄存器104内的区块地址ba选择区块blk0~blk3中的任一个,进而在所选择的区块blk中选择字线。

60.感测放大器模块110在数据的写入动作中,将从存储器控制器200接收到的写入数据dat传输到存储胞阵列101。而且,感测放大器模块110在数据的读取动作中,感测存储胞阵列101内的存储胞晶体管的阈值电压,并读取基于该感测结果的读取数据dat。

61.图3是表示经由信道cha的nand总线共通地连接的多个nand闪速存储器100a-1、100a-2、

…

、及100a-k的连接关系的图,图4是与图3的a-a线对应的剖视图。

62.如图3及图4所示,多个nand闪速存储器100a-1、100a-2、

…

、及100a-k例如为了减小封装体的尺寸而积层于基板10上。经积层的nand闪速存储器100a-1、100a-2、

…

、及100a-k使用接合线或贯通电极等相互连接。

63.例如,在通过接合线连接的情况下,如图3及图4所示,各nand闪速存储器100a分别以输入输出用垫p_dq<7:0>、选通信号用垫p_dqs、p_/dqs、控制用垫p_/ce、p_cle、p_ale、p_/we、p_re、p_/re、p_/wp、及状态通知用垫p_/rb露出的方式,相互错开地积层。然后,各nand闪速存储器100a的对应的垫共通地连接。

64.这样,本实施方式中,多个nand闪速存储器100a共有用于各信号的输入输出的配线。因此,本实施方式中,nand控制器250a无法仅通过信号/ce将多个nand闪速存储器100a个别地设定为使能状态或非使能状态。

65.1.1.4存储胞阵列

66.图5是用于说明第1实施方式的存储胞阵列的构成的电路图。图5中,示出存储胞阵列101所包含的多个区块blk中的一个区块blk。

67.如图5所示,区块blk包含例如4个串单元su(su0~su3)。各串单元su包含分别与位

线bl0~blm(m为1以上的整数)建立关联的多个nand串ns。各nand串ns例如包含8个存储胞晶体管mt0~mt7、以及选择晶体管st1及st2。存储胞晶体管mt包含控制栅极及电荷蓄积层,非易失地存储与数据对应的电荷(电子)。选择晶体管st1及st2的各个用于在各种动作时选择串单元su。

68.各nand串ns中,存储胞晶体管mt0~mt7串联连接。选择晶体管st1的漏极连接于建立关联的位线bl,选择晶体管st1的源极连接于串联连接的存储胞晶体管mt0~mt7的一端。选择晶体管st2的漏极连接于串联连接的存储胞晶体管mt0~mt7的另一端。选择晶体管st2的源极连接于源极线sl。

69.同一区块blk中,存储胞晶体管mt0~mt7的控制栅极分别共通连接于字线wl0~wl7。串单元su0~su3内的选择晶体管st1的栅极分别共通连接于选择栅极线sgd0~sgd3。选择晶体管st2的栅极共通连接于选择栅极线sgs。

70.即,区块blk是共有相同字线wl0~wl7的多个串单元su的集合体。区块blk是例如数据的抹除单位。也就是说,由同一区块blk内所含的存储胞晶体管mt保存的数据被一次抹除。

71.串单元su是各自连接于不同的位线bl且连接于同一选择栅极线sgd的多个nand串ns的集合体。将串单元su中共通连接于同一字线wl的存储胞晶体管mt的集合体称作胞单元(cell unit)cu。例如,胞单元cu内的多个存储胞晶体管mt内存储的同位比特的集合被定义为“1页面”。胞单元cu可相应于存储胞晶体管mt存储的数据的比特数而具有2页面数据以上的存储容量。

72.另外,以上说明的存储胞阵列101的电路构成不限于以上说明的构成。例如,各nand串ns所包含的存储胞晶体管mt以及选择晶体管st1及st2的个数可分别设计为任意的个数。各区块blk所包含的串单元su的个数可设计为任意的个数。

73.1.1.5输入输出电路及逻辑控制电路

74.接下来,参考图6所示的框图说明第1实施方式的输入输出电路102及逻辑控制电路103的构成。图6中,示出nand闪速存储器100a中的构成作为一例,但其他nand闪速存储器100b~100d也具有相同的构成。

75.如图6所示,输入输出电路102包含输入驱动器121<7:0>、及输出驱动器122<7:0>。逻辑控制电路103包含输入驱动器131、反相器132、正反器电路133<7:0>、芯片地址比较电路134、及逻辑积电路135。

76.一个输入驱动器121<i>及输出驱动器122<i>的组中例如分配有相同种类的信号dq<i>(0≦i≦7)。也就是说,输入驱动器121<i>及输出驱动器122<i>的组构成为可经由输入输出用垫p_dq<i>而与存储器控制器200进行信号dq<i>的通信。输入驱动器121<7:0>在接受信号dq<7:0>时,放大该信号dq<7:0>并产生信号din<7:0>,且从输出端输出到nand闪速存储器100的内部。输出驱动器122<7:0>在从nand闪速存储器100的内部接受信号dout<7:0>时,放大该信号dout<7:0>并产生信号dq<7:0>,且输出到存储器控制器200。

77.输入驱动器131中被分配有信号/ce。也就是说,输入驱动器131构成为可经由控制用垫p_/ce而与存储器控制器200之间接收信号/ce。输入驱动器131在接受信号/ce时,放大该信号/ce并产生信号int_p/ce,且从输出端输出。

78.反相器132包含与输入驱动器131的输出端连接的输入端、及与正反器电路133<7:0>的控制端及逻辑积电路135的第1输入端共通连接的输出端。反相器132在从输入驱动器131接受信号int_p/ce时,从输出端输出信号int_pce。信号int_pce是信号int_p/ce的反转信号。

79.正反器电路133<7:0>包含与输入驱动器121<7:0>的输出端连接的输入端、与芯片地址比较电路134的第1输入端连接的输出端、及与反相器132的输出端连接的控制端。正反器电路133<7:0>以从控制端输入的信号int_pce从“l”电平变为“h”电平作为触发,将从输入端输入的1周期的信号din<7:0>(也就是说,8比特的信息)锁存(latch),并从输出端输出。正反器电路133<7:0>维持例如在信号int_pce维持“h”电平的状态、从“h”电平变为“l”电平的状态及维持“l”电平的状态下锁存的信息的输出。

80.芯片地址比较电路134包含与正反器电路133<7:0>的输出端连接的第1输入端、第2输入端、及与逻辑积电路135的第2输入端连接的输出端。芯片地址比较电路134的第2输入端中例如输入有对各个nand闪速存储器100固有地设定的芯片地址ca_self<7:0>。芯片地址ca_self<7:0>能够通过例如对设置于nand闪速存储器100的未附图的芯片地址指定垫供给电源电压而进行设定。芯片地址ca_self<7:0>也可例如从存储胞阵列101读取。而且,输入到芯片地址比较电路134的芯片地址ca_self<7:0>也可例如在一连串动作之前单独从存储器控制器200发送。芯片地址比较电路134按对应的每个比特,比较从第1输入端及第2输入端的各个输入的8比特的比特序列。然后,芯片地址比较电路134在对应的比特彼此全部一致的情况下,产生“h”电平的信号sig1,在对应的比特彼此中的至少一个不一致的情况下产生“l”电平的信号sig1,并从输出端输出。

81.逻辑积电路135包含输入有信号int_pce的第1输入端、输入有信号sig1的第2输入端、及被输出信号int_ce的输出端。逻辑积电路135在信号int_pce及sig1均为“h”电平的情况下产生“h”电平的信号int_ce,在信号int_pce及sig1中的至少一个为“l”电平的情况下产生“l”电平的信号int_ce,并从输出端输出。信号int_ce是表示共通地输入到k个nand闪速存储器100a-1~100a-k的信号/ce将哪个nand闪速存储器100a设为使能状态的信号,所述k个nand闪速存储器100a-1~100a-k与同一nand控制器250a共通连接。具体来说,逻辑控制电路103根据“h”电平的信号int_ce,判定自身的nand闪速存储器100a为使能状态,根据“l”电平的信号int_ce,判定自身的nand闪速存储器100a为非使能状态。

82.1.2芯片选择动作

83.接下来,参考图7所示的时序图对第1实施方式的存储器系统的芯片选择动作进行说明。图7的例中,示出与nand控制器250a共通连接的nand闪速存储器100a-1~100a-k中,nand闪速存储器100a-1及100a-2依序分别成为使能状态的情况。图7中,nand闪速存储器100a-1及100a-2中的信号int_ce分别表示为信号int_ce1及int_ce2。

84.另外,以下,为了方便说明,分别对nand闪速存储器100a-1及100a-2内的构成的参考符号附加“-1”及“-2”而加以区分。

85.如图7所示,直至达到时刻t10为止,输入驱动器131-1及131-2中供给有“h”电平的信号/ce。由此,输入驱动器131-1及131-2输出的信号int_p/ce-1及int_p/ce-2为“h”电平,反相器132-1及132-2输出的信号int_pce-1及int_pce-2为“l”电平。因此,信号int_ce1及int_ce2均为“l”电平,nand闪速存储器100a-1及100a-2均成为非使能状态。

86.在时刻t10,信号/ce从“h”电平生效为“l”电平。与信号/ce被生效同步地,向输入驱动器121-1<7:0>及121-2<7:0>供给1周期的信号dq<7:0>。输入驱动器121-1<7:0>及121-2<7:0>分别基于信号dq<7:0>输出信号din-1<7:0>及din-2<7:0>。信号din-1<7:0>及din-2<7:0>中均包含例如唯一地识别nand闪速存储器100a-1的芯片地址ca1<7:0>。

87.通过信号/ce被生效,信号int_pce-1及int_pce-2为“h”电平。由此,正反器电路133-1<7:0>及133-2<7:0>将芯片地址ca1<7:0>锁存。

88.芯片地址比较电路134-1及134-2将芯片地址ca1<7:0>与自身所对应的芯片地址ca_self<7:0>进行比较。

89.具体来说,nand闪速存储器100a-1中,芯片地址ca_self<7:0>与芯片地址ca1<7:0>一致。由此,芯片地址比较电路134-1输出“h”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_pce-1及“h”电平的信号sig1-1,输出“h”电平的信号int_ce1。

90.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<7:0>与芯片地址ca1<7:0>不同(与芯片地址ca2<7:0>一致)。由此,芯片地址比较电路134-2输出“l”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_pce-2及“l”电平的信号sig1-2,输出“l”电平的信号int_ce2。

91.根据以上,在时刻t10,nand闪速存储器100a-1成为使能状态,nand闪速存储器100a-2成为非使能状态。

92.在时刻t20,信号/ce从“l”电平否定为“h”电平。由此,信号int_ce1及int_ce2均为“l”电平,nand闪速存储器100a-1及100a-2均成为非使能状态。

93.在时刻t30,信号/ce从“h”电平生效为“l”电平。与信号/ce被生效同步地,输入驱动器121-1<7:0>及121-2<7:0>中供给有信号dq<7:0>。输入驱动器121-1<7:0>及121-2<7:0>分别基于信号dq<7:0>输出信号din-1<7:0>及din-2<7:0>。信号din-1<7:0>及din-2<7:0>中包含例如唯一地识别nand闪速存储器100a-2的芯片地址ca2<7:0>。

94.通过信号/ce被生效,信号int_pce-1及int_pce-2成为“h”电平。由此,正反器电路133-1<7:0>及133-2<7:0>将芯片地址ca2<7:0>锁存。

95.芯片地址比较电路134-1及134-2将芯片地址ca2<7:0>与自身所对应的芯片地址ca_self<7:0>进行比较。

96.具体来说,nand闪速存储器100a-1中,芯片地址ca_self<7:0>与芯片地址ca2<7:0>不同(与芯片地址ca1<7:0>一致)。由此,芯片地址比较电路134-1输出“l”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_pce-1及“l”电平的信号sig1-1输出“l”电平的信号int_ce1。

97.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<7:0>与芯片地址ca2<7:0>一致。由此,芯片地址比较电路134-2输出“h”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_pce-2及“h”电平的信号sig1-2输出“h”电平的信号int_ce2。

98.根据以上,在时刻t30,nand闪速存储器100a-1成为非使能状态,nand闪速存储器

100a-2成为使能状态。

99.另外,如所述那样,包含芯片地址ca1<7:0>的1周期的信号dq<7:0>与在时刻t10信号/ce从“h”电平生效为“l”电平“同步”地被输入,包含芯片地址ca2<7:0>的1周期的信号dq<7:0>与在时刻t30信号/ce从“h”电平生效为“l”电平“同步”地被输入。此处提及的“同步”不限于为同一时序的情况。

100.基于信号/ce的生效而从反相器132将信号int_pce供给至正反器电路133<7:0>的控制端的时序与基于信号dq<7:0>的输入而从输入驱动器121<7:0>将信号din<7:0>供给至正反器电路133<7:0>的输入端的期间重叠即可。

101.1.3本实施方式的效果

102.根据第1实施方式,nand闪速存储器100a-1及100a-2从存储器控制器200供给有同一信号/ce。正反器电路133-1<7:0>及133-2<7:0>与信号/ce被生效同步地,将信号dq<7:0>锁存。芯片地址比较电路134-1及134-2将自身所对应的芯片地址ca_self<7:0>与信号dq<7:0>所包含的芯片地址ca<7:0>进行比较,在一致的情况下分别输出“h”电平的信号sig1-1及sig1-2,在不同的情况下分别输出“l”电平的信号sig1-1及sig1-2。逻辑积电路135-1将作为信号/ce的反转信号的信号int_pce-1与信号sig1-1的逻辑积结果以信号int_ce1的形式输出。逻辑积电路135-2将作为信号/ce的反转信号的信号int_pce-2与信号sig1-2的逻辑积结果以信号int_ce2的形式输出。由此,nand闪速存储器100a-1及100a-2均能够与信号/ce被生效同时地,判定是否被指示为自身成为使能状态。因此,存储器控制器200在每次进行写入动作或读取动作等时,不需要通过指令顺序来指定芯片地址ca。因此,能够简化芯片选择。

103.而且,使能状态的nand闪速存储器100在信号/ce被生效后,能够独占地使用信号/rb而无需接受包含芯片地址的指定的指令顺序的发行。因此,存储器控制器200能够不执行指令顺序而判定使能状态的nand闪速存储器100是就绪状态还是忙碌状态。

104.图8是表示比较例的nand闪速存储器的读取动作的指令顺序。而且,图9表示第1实施方式的nand闪速存储器的读取动作的指令顺序。

105.如图8所示,比较例中,nand控制器250a为了使多个nand闪速存储器100a中的成为动作对象的nand闪速存储器100a执行读取动作,一边切换信号/we,一边连续发行读取指令“00h”、跨5周期的地址add、及指令“30h”。指令“00h”是命令来自存储胞阵列101的数据的读取的指令,指令“30h”是命令该读取动作的开始的指令。

106.比较例中,指定多个nand闪速存储器100a中哪个成为动作对象的信息(例如,芯片地址ca)包含于地址add中。因此,多个nand闪速存储器100a的各个在接收到地址add之前无法判定是否被指示为自身成为使能状态。

107.与此相对,如图9所示,第1实施方式中,nand控制器250a与将信号/ce从“h”电平生效为“l”电平同步地,输入包含芯片地址ca<7:0>的1周期的信号dq<7:0>。由此,多个nand闪速存储器100a的各个能够在比接收指令顺序所包含的地址add更早的时序,判定是否被指示为自身成为使能状态。

108.1.4第1实施方式的变化例

109.第1实施方式不限于所述例,可应用各种变化。例如,所述第1实施方式中,已对nand闪速存储器100经由信号dq<7:0>接收8比特的芯片地址ca<7:0>的情况进行了说

明,但当芯片地址ca的比特数较少时,不限于所述情况。以下的说明中,将省略关于与第1实施方式相同的构成及动作的说明,而主要对与第1实施方式不同的构成及动作进行说明。

110.1.4.1逻辑控制电路

111.图10是用于说明第1实施方式的变化例的逻辑控制电路103的构成的框图。图10中,示出芯片地址ca的比特数为3比特的情况。

112.如图10所示,逻辑控制电路103还包含输入驱动器136、137及138。

113.输入驱动器136~138中分别分配有信号cle、ale、及/we。也就是说,输入驱动器136~138分别构成为可经由控制用垫p_cle、p_ale、及p_/we而与存储器控制器200之间接收信号cle、ale、及/we。输入驱动器136~138在分别接受信号cle、ale、及/we时,放大该信号cle、ale、及/we并产生信号int_cle、int_ale、及int_/we,且从各个输出端输出。

114.正反器电路133<2:0>包含与输入驱动器136~138的各自的输出端连接的输入端、与芯片地址比较电路134的第1输入端连接的输出端、及与反相器132的输出端连接的控制端。正反器电路133<2:0>以从控制端输入的信号int_pce从“l”电平变为“h”电平作为触发,将从输入端输入的1周期的信号int_cle、int_ale、及int_/we锁存,并从输出端输出。正反器电路133<2:0>维持例如在信号int_pce维持“h”电平的状态、从“h”电平变为“l”电平的状态、及维持“l”电平的状态下锁存的信息的输出。

115.根据以上的构成,逻辑控制电路103能够使用信号cle、ale、及/we取入芯片地址ca<2:0>。

116.1.4.2芯片选择动作

117.图11是表示第1实施方式的变化例的存储器系统中的芯片选择动作的时序图,与第1实施方式中的图7对应。

118.如图11所示,直至时刻t10为止与图7相同,因此省略说明。

119.在时刻t10,信号/ce从“h”电平生效为“l”电平。与信号/ce被生效同步地,输入驱动器136-1~138-1、及136-2~138-2的各个中分别供给有信号cle、ale、及/we。信号cle、ale、及/we中分别包含作为芯片地址ca1<2:0>的部分的ca1<0>、ca1<1>、及ca1<2>。输入驱动器136-1~138-1分别输出信号int_cle-1、int_ale-1、及int_/we-1,输入驱动器136-2~138-2分别输出信号int_cle-2、int_ale-2、及int_/we-2。

120.通过信号/ce被生效,信号int_pce-1及int_pce-2成为“h”电平。由此,正反器电路133-1及133-2<2:0>将芯片地址ca1<2:0>锁存。

121.芯片地址比较电路134-1及134-2将芯片地址ca1<2:0>与自身所对应的芯片地址ca_self<2:0>进行比较。

122.具体来说,nand闪速存储器100a-1中,芯片地址ca_self<2:0>与芯片地址ca1<2:0>一致。由此,芯片地址比较电路134-1输出“h”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_pce-1及“h”电平的信号sig1-1,输出“h”电平的信号int_ce1。

123.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<2:0>与芯片地址ca1<2:0>不同(与芯片地址ca2<2:0>一致)。由此,芯片地址比较电路134-2输出“l”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_pce-2及“l”电平的信号sig1-2,输出“l”电平的信号int_ce2。

124.根据以上,在时刻t10,nand闪速存储器100a-1成为使能状态,nand闪速存储器100a-2成为非使能状态。

125.时刻t20的动作因与第1实施方式相同,所以省略说明。

126.而且,时刻t30中的动作中,除通过信号cle、ale、及/we取入芯片地址ca2<2:0>及nand闪速存储器100a-1成为非使能状态、nand闪速存储器100a-2成为使能状态的方面以外,与时刻t10的动作相同,因此省略说明。

127.1.4.3变化例的效果

128.根据第1实施方式的变化例,能够与信号/ce被生效同步地,通过信号dq<7:0>以外的信号cle、ale、及/we取入芯片地址ca<2:0>。由此,在芯片地址ca的比特数可表现为3比特以下的情况下,能够减少芯片选择动作中使用的信号的数量。

129.2.第2实施方式

130.接下来,对第2实施方式进行说明。第1实施方式中,已对在信号/ce被生效的时间点,输入驱动器121<7:0>成为可接收信号dq<7:0>的状态的情况进行了说明。也就是说,已对nand闪速存储器100即使在处于非使能状态时也可动作地维持输入驱动器121(即使在处于非使能状态时也向输入驱动器121供给电源电压)的构成的情况进行了说明。第2实施方式中,将对在信号/ce被生效的时间点输入驱动器121<7:0>不是可接收信号dq<7:0>的状态的情况进行说明。也就是说,将对nand闪速存储器100在处于非使能状态时并非可动作地维持输入驱动器121(在处于非使能状态时不对输入驱动器121供给电源电压)的构成的情况进行说明。以下,省略关于与第1实施方式相同的构成及动作的说明,而主要对与第1实施方式不同的构成及动作进行说明。

131.2.1输入输出电路及逻辑控制电路

132.图12是表示第2实施方式的输入输出电路及逻辑控制电路的框图,与第1实施方式中的图6对应。

133.如图12所示,输入输出电路102还包含电源供给控制电路123,逻辑控制电路103还包含时序控制电路139。

134.电源供给控制电路123包含被输入来自反相器132的信号int_pce的第1输入端、被输入来自逻辑积电路135的信号int_ce的第2输入端、可向输入驱动器121<7:0>供给电压vccq的第1输出端、及向时序控制电路139输出信号sig2的第2输出端。电压vccq是用于驱动输入驱动器121<7:0>的电源电压。电源供给控制电路123在信号int_pce从“l”电平切换为“h”电平时,开始对输入驱动器121<7:0>供给电压vccq。电源供给控制电路123在开始供给电压vccq后,将表示通过电压vccq的供给而输入驱动器121<7:0>可接收信号dq<7:0>的信号sig2输出到时序控制电路139。电源供给控制电路123在信号int_ce从“h”电平切换为“l”电平时,停止向输入驱动器121<7:0>供给电压vccq。

135.时序控制电路139包含被输入有来自反相器132的信号int_pce的第1输入端、从电源供给控制电路123输入有信号sig2的第2输入端、及向正反器电路133<7:0>的控制端及逻辑积电路135的第1输入端输出信号int_dce的第2输出端。时序控制电路139在接受“h”电平的信号int_pce时,使信号int_pce延迟到接受到信号sig2为止。时序控制电路139在接受信号sig2时,将经延迟的信号int_pce以信号int_dce的形式输出。也就是说,时序控制电路139在使“h”电平的信号int_pce延迟到输入驱动器121<7:0>成为可接收的状态之后,以

信号int_dce的形式输出。

136.2.2芯片选择动作

137.图13是表示第2实施方式的存储器系统中的芯片选择动作的时序图,与第1实施方式中的图7对应。

138.如图13所示,直至时刻t10为止,nand闪速存储器100a-1及100a-2均成为非使能状态。与此同时,电源供给控制电路123-1及123-2分别停止向输入驱动器121-1<7:0>及121-2<7:0>供给电压vccq。

139.在时刻t10,信号/ce从“h”电平生效为“l”电平,并且包含芯片地址ca1<7:0>的信号dq<7:0>从存储器控制器200发送。然而,如所述那样,输入驱动器121-1<7:0>及121-2<7:0>在时刻t10的时间点未被供给电压vccq,因此不接收信号dq<7:0>。与信号/ce被生效同步地,电源供给控制电路123-1及123-2分别开始向输入驱动器121-1<7:0>及121-2<7:0>供给电压vccq。

140.另外,伴随信号/ce被生效,时序控制电路139-1及139-2分别接受“h”电平的信号int_pce-1及int_pce-2,但不输出“h”电平的信号int_dce-1及int_dce-2。

141.在时刻t11,输入驱动器121-1<7:0>及121-2<7:0>成为可接收信号dq<7:0>的状态,且分别输出信号din-1<7:0>及din-2<7:0>。与此同时,电源供给控制电路123-1及123-2分别将信号sig2-1及sig2-2输出到时序控制电路139-1及139-2。时序控制电路139-1及139-2在分别接受信号sig2-1及sig2-2时,输出“h”电平的信号int_dce-1及int_dce-2。由此,正反器电路133-1<7:0>及133-2<7:0>将芯片地址ca1<7:0>锁存。

142.另外,输入驱动器121-1<7:0>及121-2<7:0>能够在比信号dq<7:0>的1周期短的期间内成为可接收的状态。因此,输入驱动器121-1<7:0>及121-2<7:0>能够在存储器控制器200输出包含芯片地址ca1<7:0>的信号dq<7:0>的期间,接收信号dq<7:0>。

143.然后,芯片地址比较电路134-1及134-2将芯片地址ca1<7:0>与自身所对应的芯片地址ca_self<7:0>进行比较。

144.具体来说,nand闪速存储器100a-1中,芯片地址ca_self<7:0>与芯片地址ca1<7:0>一致。由此,芯片地址比较电路134-1输出“h”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_pce-1及“h”电平的信号sig1―1,输出“h”电平的信号int_ce1。

145.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<7:0>与芯片地址ca1<7:0>不同。由此,芯片地址比较电路134-2输出“l”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_pce-2及“l”电平的信号sig1-2,输出“l”电平的信号int_ce2。

146.根据以上,在时刻t11,nand闪速存储器100a-1成为使能状态,nand闪速存储器100a-2成为非使能状态。另外,电源供给控制电路123-2在接受“l”电平的信号int_ce2时,停止对输入驱动器121-2<7:0>供给电压vccq。由此,非使能状态的nand闪速存储器100a-2能够迅速地切换为待机模式。

147.在时刻t20,信号/ce从“l”电平否定为“h”电平。由此,信号int_ce1及int_ce2均为

“

l”电平,nand闪速存储器100a-1及100a-2均成为非使能状态。与此同时,电源供给控制电路123-1停止向输入驱动器121-1<7:0>供给电压vccq。

148.在时刻t30,信号/ce从“h”电平生效为“l”电平,并且包含芯片地址ca2<7:0>的信号dq<7:0>从存储器控制器200发送。然而,输入驱动器121-1<7:0>及121-2<7:0>在时刻t30的时间点不接收信号dq<7:0>。与信号/ce被生效同步地,电源供给控制电路123-1及123-2分别开始向输入驱动器121-1<7:0>及121-2<7:0>供给电压vccq。

149.另外,伴随信号/ce被生效,时序控制电路139-1及139-2分别接受“h”电平的信号int_pce-1及int_pce-2,但不输出“h”电平的信号int_dce-1及int_dce-2。

150.在时刻t31,输入驱动器121-1<7:0>及121-2<7:0>成为可接收信号dq<7:0>的状态,分别输出信号din-1<7:0>及din-2<7:0>。与此同时,电源供给控制电路123-1及123-2分别将信号sig2-1及sig2-2输出到时序控制电路139-1及139-2。时序控制电路139-1及139-2在分别接受信号sig2-1及sig2-2时,输出“h”电平的信号int_dce-1及int_dce-2。由此,正反器电路133-1<7:0>及133-2<7:0>将芯片地址ca2<7:0>锁存。

151.另外,输入驱动器121-1<7:0>及121-2<7:0>能够在比信号dq<7:0>的1周期短的期间内成为可接收的状态。因此,输入驱动器121-1<7:0>及121-2<7:0>能够在存储器控制器200输出包含芯片地址ca2<7:0>的信号dq<7:0>期间,接收信号dq<7:0>。

152.然后,芯片地址比较电路134-1及134-2将芯片地址ca2<7:0>与自身所对应的芯片地址ca_self<7:0>进行比较。

153.nand闪速存储器100a-1中,芯片地址ca_self<7:0>与芯片地址ca2<7:0>不同。由此,芯片地址比较电路134-1输出“l”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_dce-1及“l”电平的信号sig1-1,输出“l”电平的信号int_ce1。

154.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<7:0>与芯片地址ca2<7:0>一致。由此,芯片地址比较电路134-2输出“h”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_dce-2及“h”电平的信号sig1-2,输出“h”电平的信号int_ce2。

155.根据以上,在时刻t31,nand闪速存储器100a-2成为使能状态,nand闪速存储器100a-1成为非使能状态。另外,电源供给控制电路123-1在接受“l”电平的信号int_ce1时,停止向输入驱动器121-1<7:0>供给电压vccq。由此,非使能状态的nand闪速存储器100a-1能够迅速地切换为待机模式。

156.2.3本实施方式的效果

157.第2实施方式的nand闪速存储器100构成为在处于非使能状态(待机模式)时,电源供给控制电路123停止向输入驱动器121供给电压vccq。

158.根据第2实施方式,电源供给控制电路123与信号/ce被生效同步地,开始向输入驱动器121供给电压vccq。由此,输入驱动器121-1<7:0>从信号/ce被生效起延迟了期间(t11-t10)而成为可接收信号dq<7:0>的状态。时序控制电路139使信号int_pce延迟到输入驱动器121<7:0>成为可接收信号dq<7:0>的状态为止。然后,时序控制电路139在成为可接收信号dq<7:0>的状态时,将该经延迟的信号int_pce以信号int_dce的形式输

出。由此,能够将正反器电路133<7:0>锁存信号din<7:0>的时序调整为与芯片地址ca<7:0>作为信号din<7:0>被取入的期间重叠。因此,即使在当对nand闪速存储器100的输入驱动器121<7:0>生效信号/ce时输入驱动器121<7:0>不是可立即接收信号dq<7:0>的状态的情况下,也能够相应于信号/ce被生效而取入芯片地址ca<7:0>。因此,能够进一步抑制待机模式中的nand闪速存储器100的消耗电力,并简化芯片选择动作,且能够实现与第1实施方式相同的效果。

159.而且,电源供给控制电路123在接受“l”电平的信号int_ce时,停止向输入驱动器121<7:0>供给电压vccq。由此,能够迅速地停止向未被芯片选择动作选择为使能状态的nand闪速存储器100的输入驱动器121<7:0>供给电源电压。因此,能够抑制非使能状态(待机模式)下的nand闪速存储器100的消耗电力的增加。

160.2.4第2实施方式的变化例

161.第2实施方式不限于所述例,也可应用各种变化。例如,所述第2实施方式可与第1实施方式同样地,应用第1实施方式的变化例的构成。以下的说明中,省略关于与第2实施方式及第1实施方式的变化例相同的构成及动作的说明,而主要对与第2实施方式及第1实施方式的变化例不同的构成及动作进行说明。

162.2.4.1逻辑控制电路

163.图14是用于说明第2实施方式的变化例的逻辑控制电路103的构成的框图。图14中,示出芯片地址ca的比特数为3比特的情况。

164.如图14所示,逻辑控制电路103还包含输入驱动器136~138、及电源供给控制电路140。输入驱动器136~138的构成因与第1实施方式的变化例相同,所以省略说明。

165.电源供给控制电路140包含被输入来自反相器132的信号int_pce的第1输入端、被输入来自逻辑积电路135的信号int_ce的第2输入端、可向输入驱动器136~138供给电压vccq的第1输出端、及向时序控制电路139输出信号sig3的第2输出端。电源供给控制电路140在信号int_pce从“l”电平切换为“h”电平时,开始向输入驱动器136~138供给电压vccq。电源供给控制电路140在开始供给电压vccq后,将表示通过电压vccq的供给而输入驱动器136~138分别可接收信号cle、ale、及/we的信号sig3输出到时序控制电路139。电源供给控制电路140在信号int_ce从“h”电平切换为“l”电平时,停止向输入驱动器136~138供给电压vccq。

166.时序控制电路139取代第2实施方式中的信号sig2而接受信号sig3。由此,时序控制电路139使“h”电平的信号int_pce延迟到输入驱动器136~138成为可接收的状态之后,以信号int_dce的形式输出。

167.根据以上的构成,逻辑控制电路103即使在信号/ce被生效时未向输入驱动器136~138供给电压vccq的情况下,也能够使用信号cle、ale、及/we来取入芯片地址ca<2:0>。

168.2.4.2芯片选择动作

169.图15是表示第2实施方式的变化例的存储器系统中的芯片选择动作的时序图,与第2实施方式中的图13对应。

170.如图15所示,因直至时刻t10为止均与图13相同,所以省略说明。

171.在时刻t10,信号/ce从“h”电平生效为“l”电平,并且包含芯片地址ca1<2:0>的信号cle、ale、及/we从存储器控制器200发送。然而,输入驱动器136-1~138-1及136-2

~138-2的各个在时刻t10的时间点未被供给电压vccq,因此分别不接收信号cle、ale、及/we。与信号/ce被生效同步地,电源供给控制电路140-1及140-2分别开始向输入驱动器136-1~138-1、及136-2~138-2供给电压vccq。

172.另外,伴随信号/ce被生效,时序控制电路139-1及139-2分别接受“h”电平的信号int_pce-1及int_pce-2,但不输出“h”电平的信号int_dce-1及int_dce-2。

173.在时刻t11,输入驱动器136-1~138-1及136-2~138-2的各个分别成为可接收信号cle、ale、及/we的状态。与此同时,电源供给控制电路140-1及140-2分别将信号sig3-1及sig3-2输出到时序控制电路139-1及139-2。时序控制电路139-1及139-2在分别接受信号sig3-1及sig3-2时,输出“h”电平的信号int_dce-1及int_dce-2。由此,正反器电路133-1<2:0>及133-2<2:0>将芯片地址ca1<2:0>锁存。

174.另外,输入驱动器136-1~138-1及136-2~136-2的各个能够分别在比1周期短的期间内成为可接收信号cle、ale、及/we的状态。因此,输入驱动器136-1~138-1及136-2~138-2的各个能够分别在存储器控制器200输出包含芯片地址ca1<2:0>的信号cle、ale、及/we的期间,接收这些信号。

175.然后,芯片地址比较电路134-1及134-2将芯片地址ca1<2:0>与自身所对应的芯片地址ca_self<2:0>进行比较。

176.具体来说,nand闪速存储器100a-1中,芯片地址ca_self<2:0>与芯片地址ca1<2:0>一致。由此,芯片地址比较电路134-1输出“h”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_dce-1及“h”电平的信号sig1-1,输出“h”电平的信号int_ce1。

177.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<2:0>与芯片地址ca1<2:0>不同。由此,芯片地址比较电路134-2输出“l”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_dce-2及“l”电平的信号sig1-2,输出“l”电平的信号int_ce2。

178.根据以上,在时刻t11,nand闪速存储器100a-1成为使能状态,nand闪速存储器100a-2成为非使能状态。电源供给控制电路140-2在接受“l”电平的信号int_ce2时,停止向输入驱动器136-2~138-2供给电压vccq。由此,非使能状态的nand闪速存储器100a-2能够迅速地切换为待机模式。

179.时刻t20中的动作因与第2实施方式相同,所以省略说明。

180.而且,时刻t30及t31中的动作除通过信号cle、ale、及/we取入芯片地址ca2<2:0>的方面及nand闪速存储器100a-1成为非使能状态、nand闪速存储器100a-2成为使能状态的方面以外,与时刻t10及t11中的动作相同,因此省略说明。

181.2.4.3变化例的效果

182.根据第2实施方式的变化例,即使在当信号/ce被生效时停止向输入驱动器136~138供给电压vccq的情况下,也能够通过信号cle、ale、及/we取入芯片地址ca<2:0>。由此,在芯片地址ca的比特数表现为3比特以下的情况下,能够减少芯片选择动作中使用的信号的数量。

183.3.第3实施方式

184.接下来,对第3实施方式进行说明。第1实施方式及第2实施方式中,已对在信号/ce

被生效的周期内将来自存储器控制器200的芯片地址ca取入至nand闪速存储器100的情况进行了说明。第3实施方式中,就与信号/ce以外的信号被生效同步地取入芯片地址ca的方面来说,与第1实施方式及第2实施方式不同。以下,省略关于与第1实施方式及第2实施方式、以及各自的变化例相同的构成及动作的说明,而主要对与第1实施方式及第2实施方式、以及各自的变化例不同的构成及动作进行说明。

185.3.1输入输出电路及逻辑控制电路

186.图16是表示第3实施方式的输入输出电路及逻辑控制电路的框图。

187.如图16所示,逻辑控制电路103还包含芯片选择判定电路141及逻辑积电路142。而且,逻辑控制电路103不包含时序控制电路139。与此同时,电源供给控制电路123及140可分别构成为不输出信号sig2及sig3。

188.芯片选择判定电路141包含被输入来自反相器132的信号int_pce的输入端、及向逻辑积电路135的第1输入端输出信号int_qce的输出端。芯片选择判定电路141在接受了“l”电平的信号int_pce的情况下,判定是否能够将自身的nand闪速存储器100设为非使能状态。当判定为能够设为非使能状态时,芯片选择判定电路141输出“l”电平的信号int_qce。另一方面,当判定为无法设为非使能状态时或当接受了“h”电平的信号int_pce时,芯片选择判定电路141输出“h”电平的信号int_qce。作为判定为无法设为非使能状态的情况的例子,可能会包含正处于写入动作或读取动作等动作期间的情况及信号/ce被否定后直至特定时间经过的情况等。

189.逻辑积电路142包含从输入驱动器136输入有信号int_cle的第1输入端、从输入驱动器137输入有信号int_ale的第2输入端、及与正反器电路133<7:0>的控制端连接的输出端。逻辑积电路142向正反器电路133<7:0>的控制端,当信号cle及ale同时为“h”电平时输出“h”电平的信号,当信号cle及ale中的至少一个为“l”电平时输出“l”电平的信号。

190.正反器电路133<7:0>包含与输入驱动器121<7:0>的输出端连接的输入端、与芯片地址比较电路134的第1输入端连接的输出端、及与逻辑积电路142的输出端连接的控制端。正反器电路133<7:0>以逻辑积电路142的输出信号从“l”电平变为“h”电平作为触发,将从输入端输入的1周期的信号din<7:0>(也就是说,8比特的信息)锁存,并从输出端输出。正反器电路133<7:0>维持例如在逻辑积电路142的输出信号维持“h”电平的状态、从“h”电平变为“l”电平的状态、及维持“l”电平的状态下锁存的信息的输出。

191.3.2芯片选择动作

192.接下来,参考图17所示的时序图对第3实施方式的存储器系统的芯片选择动作进行说明。图17的例中,示出使能状态的nand闪速存储器100从nand闪速存储器100a-1切换为nand闪速存储器100a-2的情况。

193.如图17所示,直至时刻t50为止,从存储器控制器200供给有“l”电平的信号/ce。nand闪速存储器100a-1为使能状态,执行写入动作或读取动作等动作。也就是说,芯片地址比较电路134-1输出“h”电平的信号sig1-1。另一方面,nand闪速存储器100a-2为非使能状态,因此芯片地址比较电路134-2输出“l”电平的信号sig1-2。

194.在时刻t50,信号/ce被否定。与此同时,信号int_pce-1及int_pce-2从“h”电平切换为“l”电平。芯片选择判定电路141-1判定无法将动作中的nand闪速存储器100a-1设为非使能状态,输出“h”电平的信号int_qce-1。由此,信号int_ce1维持“h”电平。

195.在时刻t51,信号/ce再次被生效。与信号/ce被生效同步地,电源供给控制电路123-2及140-2开始向输入驱动器121-2<7:0>、136-2、及137-2供给电压vccq。由此,nand闪速存储器100a-1及100a-2均为可接收信号dq<7:0>、cle、及ale的状态。而且,芯片选择判定电路141-1及141-2分别输出“h”电平的信号int_qce-1及int_qce-2。

196.在时刻t52,nand闪速存储器100a-1结束正执行的动作。nand闪速存储器100a-1继续处于使能状态。

197.在时刻t53,信号cle及ale被生效为“h”电平,并且包含芯片地址ca2<7:0>的信号dq<7:0>从存储器控制器200发送。如所述那样,nand闪速存储器100a-1及100a-2均为可接收信号dq<7:0>、cle、及ale的状态。因此,正反器电路133-1<7:0>及133-2<7:0>将芯片地址ca2<7:0>锁存。

198.然后,芯片地址比较电路134-1及134-2将芯片地址ca2<7:0>与自身所对应的芯片地址ca_self<7:0>进行比较。

199.具体来说,nand闪速存储器100a-1中,芯片地址ca_self<7:0>与芯片地址ca2<7:0>不同。由此,芯片地址比较电路134-1输出“l”电平的信号sig1-1。逻辑积电路135-1基于“h”电平的信号int_qce-1及“l”电平的信号sig1-1,输出“l”电平的信号int_ce1。

200.另一方面,nand闪速存储器100a-2中,芯片地址ca_self<7:0>与芯片地址ca2<7:0>一致。由此,芯片地址比较电路134-2输出“h”电平的信号sig1-2。逻辑积电路135-2基于“h”电平的信号int_qce-2及“h”电平的信号sig1-2,输出“h”电平的信号int_ce2。

201.根据以上,在时刻t53,nand闪速存储器100a-1成为非使能状态,nand闪速存储器100a-2成为使能状态。另外,电源供给控制电路123-1及140-1在接受“l”电平的信号int_ce1时,停止对输入驱动器121-1<7:0>、136-1、及137-1供给电压vccq。由此,非使能状态的nand闪速存储器100a-1能够迅速地切换为待机模式。

202.在时刻t54,使能状态的nand闪速存储器100a-2开始写入动作或读取动作等动作。

203.3.3本实施方式的效果

204.根据第3实施方式,使能状态的nand闪速存储器100的芯片选择判定电路141判定在信号/ce被否定后,是否能够将该nand闪速存储器100设为非使能状态。判定的结果为,当能够设为非使能状态时,将输出到逻辑积电路135的第1输入端的信号int_qce设为“h”电平,当无法设为非使能状态时,设为“l”电平。由此,即使在信号/ce被否定后,也能够将动作中的nand闪速存储器100维持为使能状态。

205.而且,与已否定的信号/ce再次被生效同步地,电源供给控制电路123及140开始向输入驱动器121<7:0>、136、及137供给电压vccq。由此,非使能状态的nand闪速存储器100的输入驱动器121<7:0>、136、及137能够在被供给成为芯片选择动作的触发的信号cle及ale、以及包含芯片地址ca的信号dq<7:0>之前,成为可接收这些信号的状态。因此,nand闪速存储器100在使能状态的nand闪速存储器100的动作结束后,无需考虑输入驱动器的升压所需的时间便能够取入芯片地址ca。因此,即使在输入驱动器121<7:0>的升压需要时间的情况下,如在信号dq<7:0>的1周期内无法使输入驱动器121<7:0>升压时,也能够

在1周期内实质地执行芯片选择动作。

206.而且,电源供给控制电路123及140在接受“l”电平的信号int_ce时,停止向输入驱动器121<7:0>、136、及137供给电压vccq。由此,能够迅速地将芯片选择动作中未选择的nand闪速存储器100的输入驱动器121<7:0>、136、及137切换为待机模式。因此,能够抑制非使能状态下的消耗电力的增加。

207.4.其他

208.所述第1实施方式至第3实施方式中,已对芯片地址ca为8比特的情况进行了说明,但不限于此。例如,芯片地址ca可以是8比特以下的任意比特数。该情况下,仅使用与芯片地址ca的比特数相应的输入驱动器121便可执行芯片选择动作。而且,芯片地址ca可多于8比特。该情况下,nand闪速存储器100可通过重复生效信号/ce(第3实施方式中,信号cle及ale),而跨多个周期取入信号dq<7:0>。

209.而且,所述第1实施方式及第2实施方式中,已对与信号/ce被生效同时地供给芯片地址ca的情况进行了说明,所述第3实施方式中,已对与信号cle及ale均被生效同时地供给芯片地址ca的情况进行了说明,但不限于此。例如,芯片地址ca可在信号/ce被生效后或信号cle及ale均被生效后,且经过了特定的周期数后供给。该情况下,时序控制电路139可无关于信号sig2或sig3,而通过特定的可时序延迟的构成(例如,串联连接的偶数个反相器等)使信号int_p/ce延迟。由此,即使在输入驱动器121等的升压需要1周期以上的情况下,也能够在输入驱动器121等的升压完成后使正反器电路133锁存芯片地址ca。

210.而且,所述第1实施方式的变化例及第2实施方式的变化例中,已对使用信号cle、ale、及/we的情况进行了说明,但不限于此,也可取代地使用或追加信号/wp等其他信号。

211.已对本发明的几个实施方式进行了说明,但这些实施方式作为示例提示,并不意图限定发明的范围。这些实施方式能够以其他各种形态实施,在不脱离发明的主旨的范围内可进行各种省略、置换、变更。这些实施方式或其变化与包含于发明的范围或主旨同样地包含于权利要求所记载的发明及其均等的范围内。

212.[相关申请]

[0213]

本技术享有以日本专利申请2020-51634号(申请日:2020年3月23日)为基础申请的优先权。本技术通过参考该基础申请而包含基础申请的全部内容。

[0214]

[符号的说明]

[0215]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器系统

[0216]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板

[0217]

100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

nand闪速存储器

[0218]

101

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储胞阵列

[0219]

102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入输出电路

[0220]

103

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

逻辑控制电路

[0221]

104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

地址寄存器

[0222]

105

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

指令寄存器

[0223]

106

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

定序器

[0224]

107

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电压产生电路

[0225]

108

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

驱动器组

[0226]

109

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行解码器

[0227]

110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

感测放大器模块

[0228]

121、131、136、137、138

ꢀꢀꢀ

输入驱动器

[0229]

122

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出驱动器

[0230]

123、140

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电源供给控制电路

[0231]

132

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

反相器

[0232]

133

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

正反器电路

[0233]

134

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

芯片地址比较电路

[0234]

135、142

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

逻辑积电路

[0235]

139

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时序控制电路

[0236]

141

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

芯片选择判定电路

[0237]

200

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器控制器

[0238]

210

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机接口电路

[0239]

220

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

ram

[0240]

230

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

cpu

[0241]

240

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

缓冲存储器

[0242]

250

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

nand接口电路

[0243]

250a、250b、250c、250d

ꢀꢀꢀ

nand控制器

[0244]

300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机设备

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1