纠错方法和使用该纠错方法的半导体器件和半导体系统与流程

纠错方法和使用该纠错方法的半导体器件和半导体系统

1.相关申请的交叉引用

2.本技术要求于2020年3月31日提交的韩国专利申请第10-2020-0039316号的优先权,其整体内容通过引用合并于此。

技术领域

3.本公开内容的各实施方式涉及执行故障的内部数据的额外刷新操作的纠错方法,以及使用该纠错方法的半导体器件和半导体系统。

背景技术:

4.近来,用于在各个时钟周期期间接收或输出多比特数据的各种设计方案已被用于提高半导体器件的操作速度。如果半导体器件的数据传输速度变得更快,则在半导体器件中传送数据时错误出现概率会增加。因此,需要高级设计技术来确保半导体器件中的可靠的数据传输。

5.每当在半导体器件中传送数据时,可以生成能够检测错误出现的错误码并且将其与数据一起传送以提高数据传输的可靠性。错误码可以包括能够检测错误的循环冗余校验和错误检测码(edc)以及能够自身纠正错误的纠错码(ecc)。

6.同时,诸如dram器件的半导体器件执行写入操作和读取操作。执行写入操作以将数据存储到由地址选择的包括单元阵列的存储体中,并且执行读取操作以输出存储体中包括的单元阵列中存储的数据。此外,半导体器件被设计成在内部复制具有各种图案的数据并且使用复制的数据执行各种测试。

技术实现要素:

7.根据一个实施方式,一种半导体器件包括纠错电路和刷新控制电路。纠错电路被配置成检测内部数据中包括的错误,生成故障检测信号,以及纠正内部数据的错误。刷新控制电路被配置成响应于故障检测信号存储用于选择内部数据的地址信号,以及被配置成在刷新信号被输入到刷新控制电路预定次数时从地址信号生成用于激活连接到存储内部数据的存储器单元的字线的刷新地址信号。

8.根据另一实施方式,一种半导体器件包括核心电路、纠错电路和刷新控制电路。核心电路被配置成响应于读取信号输出连接到地址信号选择的字线的存储器单元中存储的内部数据,以及被配置成响应于修复信号将连接到存储故障的内部数据的至少一个故障的存储器单元的故障的字线用修复线替代。纠错电路被配置成检测故障的内部数据中包括的错误以生成故障检测信号,以及被配置成纠正故障的内部数据的错误。刷新控制电路被配置成在用于选择故障的内部数据的地址信号被输入第一预定次数时响应于故障检测信号生成修复信号。

9.根据又一实施方式,一种纠错方法可以包括读取操作步骤、纠错步骤和刷新步骤。读取操作步骤在读取操作期间基于地址信号向输入/输出线输出核心电路中存储的内部数

据。纠错步骤检测内部数据的错误,根据内部数据的错误的检测结果锁存地址信号,以及纠正内部数据的错误以输出经纠正的内部数据作为数据。刷新步骤在刷新操作期间在刷新信号被输入预定次数时从地址信号生成刷新地址信号以刷新连接到刷新地址信号选择的字线的存储器单元。

10.根据再一实施方式,一种纠错方法可以包括读取操作步骤、纠错步骤和刷新步骤。读取操作步骤在读取操作期间基于地址信号向输入/输出线输出核心电路中存储的内部数据。纠错步骤检测内部数据的错误,根据内部数据的错误的检测结果锁存地址信号,以及纠正内部数据的错误以输出经纠正的内部数据作为数据。刷新步骤在刷新操作期间在用于选择具有错误的内部数据的地址信号被输入第一预定次数时从锁存的地址信号生成刷新地址信号以刷新连接到刷新地址信号选择的字线的存储器单元。此外,刷新步骤在刷新操作期间在用于选择具有错误的内部数据的地址信号被输入第二预定次数时再次刷新字线。

附图说明

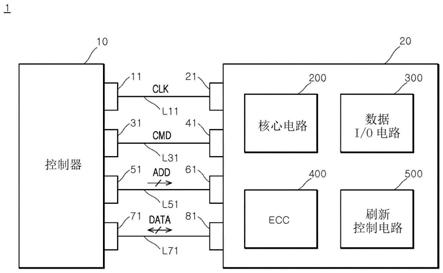

11.图1是示出根据本公开内容的一个实施方式的半导体系统的配置的框图。

12.图2是示出图1中所示的半导体系统中包括的半导体器件的配置的框图。

13.图3是示出图2中所示的半导体器件中包括的核心电路的配置的框图。

14.图4是示出图2中所示的半导体器件中包括的刷新控制电路的配置的框图。

15.图5是示出根据本公开内容的一个实施方式的半导体系统的纠错方法的流程图。

16.图6是示出根据本公开内容的另一实施方式的半导体器件的配置的框图。

17.图7是示出图6中所示的半导体器件中包括的核心电路的配置的框图。

18.图8是示出图6中所示的半导体器件中包括的核心电路的另一示例的框图。

19.图9是示出图6中所示的半导体器件中包括的刷新控制电路的配置的框图。

20.图10和图11是示出根据本公内容的另一实施方式的半导体系统的操作的时序图。

21.图12是示出根据本公内容的另一实施方式的半导体系统的纠错方法的流程图。

22.图13是示出采用图1至图12中所示的半导体系统中的至少一个的电子系统的配置的示图。

具体实施方式

23.在下面的实施方式的描述中,当参数被称为是“预定的”时,旨在意指在处理或算法中使用参数时该参数的值是预先确定的。参数值可以在处理或算法开始时被设定或者可以在执行处理或算法的时段期间被设定。

24.将理解,尽管本文使用术语“第一”、“第二”、“第三”等来描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于识别一个元件区与另一元件。因此,一些实施方式中的第一元件在其他实施方式中可被称为第二元件而不偏离本公开内容的教导。

25.此外,还将理解,当一个元件被称为“连接”或“耦接”到另一元件时,其可以直接连接或耦接到该另一元件,或者可以存在居间的元件。相反,当一个元件被称为“直接连接”或“直接耦接”到另一元件时,不存在居间的元件。

26.逻辑“高”电平和逻辑“低”电平可用于描述电信号的逻辑电平。具有逻辑“高”电平的信号可以区别于具有逻辑“低”电平的信号。例如,当具有第一电压的信号对应于具有逻

辑“高”电平的信号时,具有第二电压的信号对应于具有逻辑“低”电平的信号。在一个实施方式中,逻辑“高”电平可被设定为电压电平高于逻辑“低”电平的电压电平。同时,信号的逻辑电平可以根据不同的实施方式被设定为不同或相反。例如,在一个实施方式中具有逻辑“高”电平的特定信号可以在另一实施方式中被设定为具有逻辑“低”电平

27.下面将参照附图详细描述本公开的各实施方式。然而,本文描述的实施方式仅用于说明性目的而非旨在限制本公开的范围。

28.如图1中所示,根据本公开内容的一个实施方式的半导体系统1可以包括控制器10和半导体器件20。半导体器件20可以包括核心电路200、数据输入/输出(i/o)电路300、纠错电路(ecc)400和刷新控制电路500。

29.控制器10可以包括第一控制引脚11、第二控制引脚31、第三控制引脚51和第四控制引脚71。半导体器件20可以包括第一半导体引脚21、第二半导体引脚41、第三半导体引脚61和第四半导体引脚81。第一控制引脚11和第一半导体引脚21可以通过第一传输线l11彼此连接。第二控制引脚31和第二半导体引脚41可以通过第二传输线l31彼此连接。第三控制引脚51和第三半导体引脚61可以通过第三传输线l51彼此连接。第四控制引脚71和第四半导体引脚81可以通过第四传输线71彼此连接。控制器10可以通过第一传输线l11向半导体器件20传送时钟信号clk以控制半导体器件20。控制器10可以通过第二传输线l31向半导体器件20传送命令信号cmd以控制半导体器件20。控制器10可以通过第三传输线l51向半导体器件20传送地址信号add以控制半导体器件20。控制器10可以通过第四传输线l71从半导体器件20接收数据data或者通过第四传输线l71向半导体器件20传送数据data。

30.控制器10可以向半导体器件20输出时钟信号clk、命令信号cmd和地址信号add以执行读取操作。控制器10可以在读取操作期间从半导体器件20接收数据data。控制器10可以向半导体器件20输出时钟信号clk、命令信号cmd、地址信号add和数据data以执行写入操作。控制器10可以向半导体器件10输出时钟信号clk和命令信号cmd以执行刷新操作。命令信号cmd、地址信号add和数据data可以与时钟信号clk中包括的奇数脉冲或偶数脉冲同步地被连续地输入或输出。

31.核心电路200可以在读取操作期间与时钟信号clk同步地基于命令信号cmd和地址信号add输出数据data。核心电路200可以在写入操作期间与时钟信号clk同步地基于命令信号cmd和地址信号add接收和存储数据data。核心电路200可以在刷新操作期间与时钟信号clk同步地基于命令信号cmd顺次激活其中包括的多个字线。当存储器单元中的连接到特定字线的至少一个存储器单元是存储包括错误数据的内部数据(图2的id<1:k>)的故障的存储器单元时,核心电路200可以在刷新操作期间与时钟信号clk同步地基于命令信号cmd额外激活特定字线。核心电路200可以执行用于将连接到存储包括错误数据的内部数据(图2的id<1:k>)的至少一个故障的存储器单元的字线用修复线替代的修复操作。

32.数据输入/输出电路300可以在读取操作期间从内部数据(图2的id<1:k>)生成数据data。数据输入/输出电路300可以在写入操作期间从数据data生成内部数据(图2的id<1:k>)。

33.纠错电路400可以在读取操作期间检测内部数据(图2的id<1:k>)的错误以生成故障检测信号(图2的fail)。纠错电路400可以在读取操作期间纠正内部数据(图2的id<1:k>)中包括的错误。纠错电路400可以在写入操作期间检测内部数据(图2的id<1:k>)的错误以

生成故障检测信号(图2的fail)。纠错电路400可以在写入操作期间检测内部数据(图2的id<1:k>)的错误以纠正内部数据(图2的id<1:k>)中包括的错误。

34.刷新控制电路500可以在读取操作期间响应于故障检测信号(图2的fail)存储用于选择内部数据(图2的id<1:k>)的地址信号add。刷新控制电路500可以在读取操作期间响应于具有高电平的故障检测信号(图2的fail)存储用于选择内部数据(图2的id<1:k>)的地址信号add。刷新控制电路500可以在刷新操作期间生成用于顺次激活多个字线的刷新地址信号(图2的ref_add<1:m>)。刷新控制电路500可以在刷新操作期间从存储的地址信号add生成刷新地址信号(图2的ref_add<1:m>),刷新地址信号用于激活连接到存储内部数据(图2的id<1:k>)的存储器单元的字线。

35.图2是示出半导体器件20的配置的框图。如图2中所示,半导体器件20可以包括命令解码器100、核心电路200、数据输入/输出电路300、纠错电路400和刷新控制电路500。

36.命令解码器100可以与时钟信号clk同步以生成读取信号rd、写入信号wt和刷新信号ref,上述信号之一根据命令信号cmd被选择性地使能。命令解码器100可以通过与时钟信号clk同步地对命令信号cmd解码来生成用于执行读取操作的读取信号rd。命令解码器100可以通过与时钟信号clk同步地对命令信号cmd解码来生成用于执行写入操作的写入信号wt。命令解码器100可以通过与时钟信号clk同步地对命令信号cmd解码来生成用于执行刷新操作的刷新信号ref。

37.在读取操作期间,核心电路200可以基于读取信号rd和第一至第m地址信号add<1:m>输出其中存储的第一至第k内部数据id<1:k>。核心电路200可以在写入操作期间基于写入信号wt和第一至第m地址信号add<1:m>存储第一至第k内部数据id<1:k>。核心电路200可以在刷新操作期间基于刷新信号ref和第一至第m刷新地址信号ref_add<1:m>执行用于激活多个字线的刷新操作。第一至第k内部数据id<1:k>可以在读取操作期间通过输入/输出线io从核心电路200输出。第一至第k内部数据id<1:k>可以在写入操作期间通过输入/输出线io输入到核心电路200。

38.数据输入/输出电路300可以在读取操作期间缓冲在输入/输出线io上加载的第一至第k内部数据id<1:k>以生成第一至第k数据data<1:k>。数据输入/输出电路300可以在读取操作期间向控制器10输出第一至第k数据data<1:k>。数据输入/输出电路300可以在写入操作期间缓冲第一至第k数据data<1:k>以生成第一至第k内部数据id<1:k>。数据输入/输出电路300可以在写入操作期间向输入/输出线io输出第一至第k内部数据id<1:k>。尽管图2示出了具有单个线的输入/输出线io,但是输入/输出线io可被配置成包括多个线。

39.纠错电路400可以在读取操作期间检测在输入/输出线io上加载的第一至第k内部数据id<1:k>的错误。纠错电路400可以在读取操作期间纠正第一至第k内部数据id<1:k>的错误并且可以将第一至第k内部数据id<1:k>的经纠正的数据输出到输入/输出线io。纠错电路400可以在读取操作期间当输入/输出线io上加载的第一至第k内部数据id<1:k>中出现错误时生成使能的故障检测信号fail。纠错电路400可以在读取操作期间检测在输入/输出线io上加载的第一至第k内部数据id<1:k>的错误。纠错电路400可以在写入操作期间纠正第一至第k内部数据id<1:k>的错误并且可以将第一至第k内部数据id<1:k>的经纠正的数据输出到输入/输出线io。纠错电路400可以在写入操作期间当输入/输出线io上加载的第一至第k内部数据id<1:k>中出现错误时生成使能的故障检测信号fail。纠错电路400可

以使用通过纠错码(ecc)来纠正错误的常见的ecc电路实现。

40.刷新控制电路500可以在读取操作期间响应于故障检测信号fail存储用于选择第一至第k内部数据id<1:k>的第一至第m地址信号add<1:m>。刷新控制电路500可以在写入操作期间响应于故障检测信号fail存储用于选择第一至第k内部数据id<1:k>的第一至第m地址信号add<1:m>。刷新控制电路500可以基于刷新信号ref生成用于顺次激活多个字线的第一至第m刷新地址信号ref_add<1:m>。在刷新操作期间,当刷新信号ref被输入第一预定次数时,刷新控制电路500可以从第一至第m地址信号add<1:m>生成第一至第m刷新地址信号ref_add<1:m>,用于激活连接到存储具有错误数据的第一至第k内部数据id<1:k>的至少一个存储器单元的字线。刷新信号ref被输入第一预定次数的情况可被设定为刷新信号ref被输入两次或更多次的情况。根据实施方式,第一预定次数可被设定为刷新信号ref以各种方式被连续输入的情况。

41.半导体器件20可以在读取操作期间与时钟信号clk同步以从其中存储的第一至第k内部数据id<1:k>生成第一至第k数据data<1:k>并且将第一至第k数据data<1:k>输出到控制器10。半导体器件20可以在写入操作期间与时钟信号clk同步地从控制器10接收第一至第k数据data<1:k>以生成并存储第一至第k内部数据id<1:k>。半导体器件20可以在刷新操作期间基于第一至第m刷新地址信号ref_add<1:m>顺次激活多个字线。在刷新操作期间,当刷新信号ref被生成第一预定次数时,半导体器件20可以额外激活连接到存储包括错误数据的第一至第k内部数据id<1:k>的至少一个存储器单元的字线。

42.图3是示出核心电路200的配置的框图。如图3中所示,核心电路200可以包括第一存储器区域210、第一内部控制电路220、第二存储器区域230、第二内部控制电路240、第三存储器区域250、第三内部控制电路260、第四存储器区域270和第四内部控制电路280。

43.第一存储器区域210可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第一存储器区域210时,第一存储器区域210可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第一存储器区域210时,第一存储器区域210可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第一存储器区域210中时,第一存储器区域210可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。

44.第一内部控制电路220可以电连接到第一存储器区域210。第一内部控制电路220可以在读取操作期间通过输入/输出线io输出从第一存储器区域210中读出的第一至第k内部数据id<1:k>。第一内部控制电路220可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第一存储器区域210。第一内部控制电路220可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。

45.第二存储器区域230也可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第二存储器区域230时,第二存储器区域230可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第二存储器区域230时,第二存储器区域230可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:

m>激活的字线的存储器单元中。当刷新信号ref被输入到第二存储器区域230中时,第二存储器区域230可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的任何一个或更多个字线。

46.第二内部控制电路240可以电连接到第二存储器区域230。第二内部控制电路240可以在读取操作期间通过输入/输出线io输出从第二存储器区域230中读出的第一至第k内部数据id<1:k>。第二内部控制电路240可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第二存储器区域230。第二内部控制电路240可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。

47.第三存储器区域250也可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第三存储器区域250时,第三存储器区域250可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第三存储器区域250时,第三存储器区域250可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第三存储器区域250中时,第三存储器区域250可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的任何一个或更多个字线。

48.第三内部控制电路260可以电连接到第三存储器区域250。第三内部控制电路260可以在读取操作期间通过输入/输出线io输出从第三存储器区域250中读出的第一至第k内部数据id<1:k>。第三内部控制电路260可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第三存储器区域250。第三内部控制电路260可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。

49.第四存储器区域270也可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第四存储器区域270时,第四存储器区域270可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第四存储器区域270时,第四存储器区域270可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第四存储器区域270中时,第四存储器区域270可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的任何一个或更多个字线。

50.第四内部控制电路280可以电连接到第四存储器区域270。第四内部控制电路280可以在读取操作期间通过输入/输出线io输出从第四存储器区域270中读出的第一至第k内部数据id<1:k>。第四内部控制电路280可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第四存储器区域270。第四内部控制电路280可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。

51.图4是示出刷新控制电路500的配置的框图。如图4中所示,刷新控制电路500可以包括地址存储电路510、控制信号生成电路520、计数器530和选择传输电路540。

52.地址存储电路510可以基于故障检测信号fail存储第一至第m地址信号add<1:m>。地址存储电路510可以存储在故障检测信号fail被使能时的时间点输入的第一至第m地址信号add<1:m>。地址存储电路510可以存储在故障检测信号fail被使能时的时间点存储的

第一至第m地址信号add<1:m>,作为第一至第m故障地址信号fadd<1:m>。

53.控制信号生成电路520可以基于刷新信号ref生成控制信号tcon。控制信号生成电路520可以生成在刷新信号ref被输入第一预定次数时使能的控制信号tcon。控制信号生成电路520可以生成在刷新信号ref被连续输入两次或更多次时使能为具有逻辑“高”电平的控制信号tcon。

54.计数器530可以基于刷新信号ref生成第一至第m计数信号cnt<1:m>。计数器530可以生成在刷新信号ref被输入到计数器530时顺次计数的第一至第m计数信号cnt<1:m>。

55.选择传输电路540可以基于控制信号tcon从第一至第m故障地址信号fadd<1:m>或者第一至第m计数信号cnt<1:m>生成第一至第m刷新地址信号ref_add<1:m>。当控制信号tcon被禁用为具有逻辑“低”电平时,选择传输电路540可以输出第一至第m计数信号cnt<1:m>作为第一至第m刷新地址信号ref_add<1:m>。当控制信号tcon被使能为具有逻辑“高”电平时,选择传输电路540可以输出第一至第m故障地址信号fadd<1:m>作为第一至第m刷新地址信号ref_add<1:m>。

56.下面将参照图5描述根据本公开内容的一个实施方式的半导体系统的纠错方法。

57.参照图5,纠错方法可以包括读取操作步骤s1、纠错步骤s2和刷新步骤s3。

58.读取操作步骤s1可以包括命令输入步骤s11、读取操作检测步骤s12和内部数据输出步骤s13。

59.命令输入步骤s11可以对应于从控制器10向半导体器件20传送时钟信号clk、命令信号cmd和第一至第m地址信号add<1:m>用于执行读取操作的步骤。

60.读取操作检测步骤s12可以对应于基于从控制器10输出的时钟信号clk和命令信号cmd生成读取信号rd的步骤。

61.内部数据输出步骤s13可以对应于基于读取信号rd和第一至第m地址信号add<1:m>将核心电路200中存储的第一至第k内部数据id<1:k>输出到输入/输出线io的步骤。

62.纠错步骤s2可以包括错误检测步骤s21、数据纠错步骤s22、地址锁存步骤s23和数据输出步骤s24。

63.错误检测步骤s21可以对应于通过使用纠错电路400检测在输入/输出线io上加载的第一至第k内部数据id<1:k>的错误的步骤。当在错误检测步骤s21处从第一至第k内部数据id<1:k>中检测到错误时(是),纠错电路400可以生成故障检测信号fail。刷新控制电路500可以基于故障检测信号fail存储第一至第m地址信号add<1:m>。当在错误检测步骤s21处没有从第一至第k内部数据id<1:k>中检测到错误时(否),可以执行数据输出步骤s24。

64.数据纠错步骤s22可以对应于在纠错电路400中使用纠错码(ecc)纠正故障的第一至第k内部数据id<1:k>的错误的步骤。

65.地址锁存步骤s23可以对应于在故障检测信号fail被使能时将第一至第m地址信号add<1:m>存储在刷新控制电路500中作为第一至第m故障地址信号fadd<1:m>的步骤。

66.数据输出步骤s24可以对应于在数据输入/输出电路300中通过缓冲在数据纠错步骤s22处纠正的第一至第k内部数据id<1:k>来生成第一至第k数据data<1:k>的步骤。数据输出步骤s24还可以对应于将数据输入/输出电路300生成的第一至第k数据data<1:k>输出到控制器10的步骤。

67.刷新步骤s3可以包括刷新操作检测步骤s31、计数操作步骤s32、计数检测步骤

s33、故障刷新步骤s34和正常刷新步骤s35。

68.刷新操作检测步骤s31可以对应于基于从控制器10输出的时钟信号clk和命令信号cmd生成刷新信号ref的步骤。

69.计数操作步骤s32可以对应于每当刷新信号ref被输入到刷新控制电路500时检测刷新信号ref的步骤。

70.计数检测步骤s33可以对应于检测刷新信号ref是否被输入到刷新控制电路500第一预定次数的步骤。

71.当在计数检测步骤s33处刷新信号ref被输入到刷新控制电路500第一预定次数时(是),可以执行故障刷新步骤s34。

72.当在计数检测步骤s33处刷新信号ref被输入到刷新控制电路500的次数小于第一预定次数时(否),可以执行正常刷新步骤s35。

73.故障刷新步骤s34可以对应于在刷新控制电路500中从第一至第m地址信号add<1:m>生成用于激活连接到存储包括错误的第一至第k内部数据id<1:k>的存储器单元的字线的第一至第m刷新地址信号ref_add<1:m>的步骤。故障刷新步骤s34可以对应于在核心电路200中基于第一至第m刷新地址信号ref_add<1:m>通过额外激活连接到存储包括错误的第一至第k内部数据id<1:k>的存储器单元的字线来执行刷新操作的步骤。

74.正常刷新步骤s35可以对应于在刷新控制电路500中生成第一至第m刷新地址信号ref_add<1:m>以顺次激活核心电路200中的多个字线的步骤。正常刷新步骤s35可以对应于基于刷新信号ref和顺次计数的第一至第m刷新地址信号ref_add<1:m>通过顺次激活核心电路200中的多个字线来执行刷新操作的步骤。

75.具有前述配置的半导体系统1可以通过在刷新操作期间在刷新信号被重复输入第一预定次数时额外刷新存储故障的内部数据的存储器单元来呈现内部数据的可靠性。

76.图6是示出与图2中所示的半导体器件20的另一示例对应的半导体器件20a的配置的框图。如图6中所示,半导体器件20a可以包括命令解码器100a、核心电路200a、数据输入/输出电路300a、纠错电路400a和刷新控制电路500a。

77.命令解码器100a可以与时钟信号clk同步以生成读取信号rd、写入信号wt和刷新信号ref,上述信号之一根据命令信号cmd而被选择性地使能。命令解码器100a可以通过与时钟信号clk同步地对命令信号cmd解码来生成用于执行读取操作的读取信号rd。命令解码器100a可以通过与时钟信号clk同步地对命令信号cmd解码来生成用于执行写入操作的写入信号wt。命令解码器100a可以通过与时钟信号clk同步地对命令信号cmd解码来生成用于执行刷新操作的刷新信号ref。

78.核心电路200a可以在读取操作期间基于读取信号rd和第一至第m地址信号add<1:m>输出其中存储的第一至第k内部数据id<1:k>。核心电路200a可以在写入操作期间基于写入信号wt和第一至第m地址信号add<1:m>存储第一至第k内部数据id<1:k>。核心电路200a可以在刷新操作期间基于刷新信号ref和第一至第m刷新地址信号ref_add<1:m>激活多个字线。核心电路200a可以在刷新操作期间基于修复信号sppr执行修复操作,用于将连接到存储包括错误数据的故障的第一至第k内部数据id<1:k>的存储器单元的字线用修复线替代。核心电路200a中存储的第一至第k内部数据id<1:k>可以在读取操作期间通过输入/输出线io输出。第一至第k内部数据id<1:k>可以在写入操作期间通过输入/输出线io输入到

核心电路200a。

79.数据输入/输出电路300a可以在读取操作期间缓冲在输入/输出线io上加载的第一至第k内部数据id<1:k>以生成第一至第k数据data<1:k>。数据输入/输出电路300a可以在读取操作期间向控制器10输出第一至第k数据data<1:k>。数据输入/输出电路300a可以在写入操作期间缓冲第一至第k数据data<1:k>以生成第一至第k内部数据id<1:k>。数据输入/输出电路300a可以在写入操作期间向输入/输出线io输出第一至第k内部数据id<1:k>。尽管图6示出了具有单个线的输入/输出线io,但是输入/输出线io可被配置成包括多个线。

80.纠错电路400a可以在读取操作期间检测在输入/输出线io上加载的第一至第k内部数据id<1:k>的错误。纠错电路400a可以在读取操作期间纠正第一至第k内部数据id<1:k>的错误并且可以将第一至第k内部数据id<1:k>的经纠正的数据输出到输入/输出线io。纠错电路400a可以在读取操作期间生成在输入/输出线io上加载的第一至第k内部数据id<1:k>中存在错误时使能的故障检测信号fail。纠错电路400a可以在读取操作期间检测在输入/输出线io上加载的第一至第k内部数据id<1:k>的错误。纠错电路400a可以在写入操作期间纠正第一至第k内部数据id<1:k>的错误并且可以将第一至第k内部数据id<1:k>的经纠正的数据输出到输入/输出线io。纠错电路400a可以在写入操作期间生成在输入/输出线io上加载的第一至第k内部数据id<1:k>中存在错误时使能的故障检测信号fail。纠错电路400a可以使用通过纠错码(ecc)来纠正错误的常见的ecc电路实现。

81.刷新控制电路500a可以在读取操作期间响应于故障检测信号fail存储用于选择第一至第k内部数据id<1:k>的第一至第m地址信号add<1:m>。刷新控制电路500a可以在写入操作期间响应于故障检测信号fail存储用于选择第一至第k内部数据id<1:k>的第一至第m地址信号add<1:m>。在刷新操作期间在刷新信号ref被输入到刷新控制电路500a第一预定次数时,刷新控制电路500a可以从第一至第m地址信号add<1:m>生成用于激活连接到存储包括错误数据的故障的第一至第k内部数据id<1:k>的存储器单元的字线的第一至第m刷新地址信号ref_add<1:m>。在刷新操作期间在用于选择连接到存储包括错误数据的第一至第k内部数据id<1:k>的存储器单元的字线的第一至第m地址信号add<1:m>被输入到刷新控制电路500a第二预定次数时,刷新控制电路500a可以生成用于激活连接到存储包括错误数据的第一至第k内部数据id<1:k>的存储器单元的字线的第一至第m刷新地址信号ref_add<1:m>。在包括错误数据的第一至第k内部数据id<1:k>被输入到刷新控制电路500a第三预定次数时,刷新控制电路500a可以生成被使能的修复信号sppr。刷新信号ref被输入第一预定次数的情况可被设定为刷新信号ref被输入两次或更多次的情况。第一预定次数可以对应于刷新信号ref被连续输入的次数。第一至第m地址信号add<1:m>被输入第二预定次数的情况可被设定为具有用于选择包括错误数据的第一至第k内部数据id<1:k>的逻辑电平组合的第一至第m地址信号add<1:m>被输入两次的情况。第二预定次数可以对应于具有相同逻辑电平组合的第一至第m地址信号add<1:m>被连续输入的次数。包括错误数据的第一至第k内部数据id<1:k>被输入第三预定次数的情况可被设定为具有用于选择具有错误数据的第一至第k内部数据id<1:k>的逻辑电平组合的第一至第m地址信号add<1:m>被输入至少三次的情况。

82.具有上述配置的半导体器件20a可以在读取操作期间与时钟信号clk同步地从其中存储的第一至第k内部数据id<1:k>生成第一至第k数据data<1:k>并且可以将第一至第k

数据data<1:k>输出到控制器10。在写入操作期间,半导体器件20a可以与时钟信号clk同步地从控制器10接收第一至第k数据data<1:k>以从第一至第k数据data<1:k>生成第一至第k内部数据id<1:k>并且将第一至第k内部数据id<1:k>存储在其中。在刷新操作期间,半导体器件20a可以基于第一至第m刷新地址信号ref_add<1:m>顺次激活核心电路200a中的多个字线。在刷新操作期间,当刷新信号ref被生成第一预定次数时,半导体器件20a可以重新激活连接到存储包括错误数据的第一至第k内部数据id<1:k>的存储器单元的字线。在刷新操作期间,当具有用于选择包括错误数据的第一至第k内部数据id<1:k>的逻辑电平组合的第一至第m地址信号add<1:m>被输入两次时,半导体器件20a可以重新激活连接到存储包括错误数据的第一至第k内部数据id<1:k>的存储器单元的字线。在刷新操作期间,当具有用于选择包括错误数据的第一至第k内部数据id<1:k>的逻辑电平组合的第一至第m地址信号add<1:m>被输入三次或更多次时,半导体器件20a可以将连接到存储包括错误数据的第一至第k内部数据id<1:k>的存储器单元的字线用修复线替代。

83.图7是示出核心电路200a的配置的框图。如图7中所示,核心电路200a可以包括第一存储器区域210a、第一内部控制电路220a、第二存储器区域230a、第二内部控制电路240a、第三存储器区域250a、第三内部控制电路260a、第四存储器区域270a和第四内部控制电路280a。

84.第一存储器区域210a可以包括第一至第n字线wl<1:n>以及第一和第二修复线sr<1:2>。当读取信号rd被输入到第一存储器区域210a时,第一存储器区域210a可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第一存储器区域210a时,第一存储器区域210a可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第一存储器区域210a中时,第一存储器区域210a可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的任何一个或更多个字线。当修复信号sppr被输入到第一存储器区域210a时,第一存储器区域210a可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。

85.第一内部控制电路220a可以电连接到第一存储器区域210a。第一内部控制电路220a可以在读取操作期间通过输入/输出线io输出从第一存储器区域210a中读出的第一至第k内部数据id<1:k>。第一内部控制电路220a可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第一存储器区域210a。第一内部控制电路220a可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第一内部控制电路220a时,第一内部控制电路220a可以控制第一存储器区域210a以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。当修复信号sppr被输入到第一内部控制电路220a时,第一内部控制电路220a可以复制第一至第k内部数据id<1:k>并且可以控制第一存储器区域210a以将复制的第一至第k内部数据id<1:k>存储到第一和第二修复线sr<1:2>中。

86.第二存储器区域230a也可以包括第一至第n字线wl<1:n>以及第一和第二修复线

sr<1:2>。当读取信号rd被输入到第二存储器区域230a时,第二存储器区域230a可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第二存储器区域230a时,第二存储器区域230a可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第二存储器区域230a中时,第二存储器区域230a可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第二存储器区域230a时,第二存储器区域230a可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。

87.第二内部控制电路240a可以电连接到第二存储器区域230a。第二内部控制电路240a可以在读取操作期间通过输入/输出线io输出从第二存储器区域230a中读出的第一至第k内部数据id<1:k>。第二内部控制电路240a可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第二存储器区域230a。第二内部控制电路240a可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第二内部控制电路240a时,第二内部控制电路240a可以控制第二存储器区域230a以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。当修复信号sppr被输入到第二内部控制电路240a时,第二内部控制电路240a可以复制第一至第k内部数据id<1:k>并且可以控制第二存储器区域230a以将复制的第一至第k内部数据id<1:k>存储到第一和第二修复线sr<1:2>中。

88.第三存储器区域250a也可以包括第一至第n字线wl<1:n>以及第一和第二修复线sr<1:2>。当读取信号rd被输入到第三存储器区域250a时,第三存储器区域250a可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第三存储器区域250a时,第三存储器区域250a可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第三存储器区域250a中时,第三存储器区域250a可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第三存储器区域250a时,第三存储器区域250a可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。

89.第三内部控制电路260a可以电连接到第三存储器区域250a。第三内部控制电路260a可以在读取操作期间通过输入/输出线io输出从第三存储器区域250a中读出的第一至第k内部数据id<1:k>。第三内部控制电路260a可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第三存储器区域250a。第三内部控制电路260a可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第三内部控制电路260a时,第三内部控制电路260a可以控制第三存储器区域250a以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故

障的字线替代为第一和第二修复线sr<1:2>中的任何一个。当修复信号sppr被输入到第三内部控制电路260a时,第三内部控制电路260a可以复制第一至第k内部数据id<1:k>并且可以控制第三存储器区域250a以将复制的第一至第k内部数据id<1:k>存储到第一和第二修复线sr<1:2>中。

90.第四存储器区域270a也可以包括第一至第n字线wl<1:n>以及第一和第二修复线sr<1:2>。当读取信号rd被输入到第四存储器区域270a时,第四存储器区域270a可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第四存储器区域270a时,第四存储器区域270a可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第四存储器区域270a中时,第四存储器区域270a可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第四存储器区域270a时,第四存储器区域270a可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。

91.第四内部控制电路280a可以电连接到第四存储器区域270a。第四内部控制电路280a可以在读取操作期间通过输入/输出线io输出从第四存储器区域270a中读出的第一至第k内部数据id<1:k>。第四内部控制电路280a可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第四存储器区域270a。第四内部控制电路280a可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第四内部控制电路280a时,第四内部控制电路280a可以控制第四存储器区域270a以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一和第二修复线sr<1:2>中的任何一个。当修复信号sppr被输入到第四内部控制电路280a时,第四内部控制电路280a可以复制第一至第k内部数据id<1:k>并且可以控制第四存储器区域270a以将复制的第一至第k内部数据id<1:k>存储到第一和第二修复线sr<1:2>中。

92.图8是示出与图7中所示的核心电路200a的另一示例对应的核心电路200b的配置的框图。如图8中所示,核心电路200b可以包括第一存储器区域210b、第一内部控制电路220b、第二存储器区域230b、第二内部控制电路240b、第一修复区域250b、第三存储器区域260b、第三内部控制电路270b、第四存储器区域280b、第四内部控制电路290b和第二修复区域300b。

93.第一存储器区域210b可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第一存储器区域210b时,第一存储器区域210b可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第一存储器区域210b时,第一存储器区域210b可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第一存储器区域210b中时,第一存储器区域210b可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第一存储器区域210b时,第一存储

器区域210b可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一修复区域250b中包括的第一和第二修复线sr<1:2>中的任何一个。

94.第一内部控制电路220b可以电连接到第一存储器区域210b和第一修复区域250b。第一内部控制电路220b可以在读取操作期间通过输入/输出线io输出从第一存储器区域210b中读出的第一至第k内部数据id<1:k>。第一内部控制电路220b可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第一存储器区域210b。第一内部控制电路220b可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第一内部控制电路220b时,第一内部控制电路220b可以控制第一存储器区域210b和第一修复区域250b以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一修复区域250b中包括的第一和第二修复线sr<1:2>中的任何一个。当修复信号sppr被输入到第一内部控制电路220b时,第一内部控制电路220b可以复制第一至第k内部数据id<1:k>并且可以控制第一存储器区域210b和第一修复区域250b以将复制的第一至第k内部数据id<1:k>存储到第一和第二修复线sr<1:2>中。

95.第二存储器区域230b可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第二存储器区域230b时,第二存储器区域230b可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第二存储器区域230b时,第二存储器区域230b可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第二存储器区域230b中时,第二存储器区域230b可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第二存储器区域230b时,第二存储器区域230b可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一修复区域250b中包括的第三和第四修复线sr<3:4>中的任何一个。

96.第二内部控制电路240b可以电连接到第二存储器区域230b和第一修复区域250b。第二内部控制电路240b可以在读取操作期间通过输入/输出线io输出从第二存储器区域230b中读出的第一至第k内部数据id<1:k>。第二内部控制电路240b可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第二存储器区域230b。第二内部控制电路240b可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第二内部控制电路240b时,第二内部控制电路240b可以控制第二存储器区域230b和第一修复区域250b以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第一修复区域250b中包括的第三和第四修复线sr<3:4>中的任何一个。当修复信号sppr被输入到第二内部控制电路240b时,第二内部控制电路240b可以复制第一至第k内部数据id<1:k>并且可以控制第二存储器区域230b和第一修复区域250b以将复制的第一至第k内部数据id<1:k>存储到第三和第四修复线sr<3:4>中。

97.第一修复区域250b可以包括第一至第四修复线sr<1:4>。第一修复区域250b中的

第一和第二修复线sr<1:2>可用于替代连接到第一存储器区域210b中包括的故障的存储器单元的字线。第一修复区域250b中的第三和第四修复线sr<3:4>可用于替代连接到第二存储器区域230b中包括的故障的存储器单元的字线。

98.第三存储器区域260b可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第三存储器区域260b时,第三存储器区域260b可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第三存储器区域260b时,第三存储器区域260b可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第三存储器区域260b中时,第三存储器区域260b可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第三存储器区域260b时,第三存储器区域260b可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第二修复区域300b中包括的第一和第二修复线sr<1:2>中的任何一个。

99.第三内部控制电路270b可以电连接到第三存储器区域260b和第二修复区域300b。第三内部控制电路270b可以在读取操作期间通过输入/输出线io输出从第三存储器区域260b中读出的第一至第k内部数据id<1:k>。第三内部控制电路270b可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第三存储器区域260b。第三内部控制电路270b可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第三内部控制电路270b时,第三内部控制电路270b可以控制第三存储器区域260b和第二修复区域300b以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第二修复区域300b中包括的第一和第二修复线sr<1:2>中的任何一个。当修复信号sppr被输入到第三内部控制电路270b时,第三内部控制电路270b可以复制第一至第k内部数据id<1:k>并且可以控制第三存储器区域260b和第二修复区域300b以将复制的第一至第k内部数据id<1:k>存储到第二修复区域300b中包括的第一和第二修复线sr<1:2>中。

100.第四存储器区域280b可以包括第一至第n字线wl<1:n>。当读取信号rd被输入到第四存储器区域280b时,第四存储器区域280b可以输出连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中存储的第一至第k内部数据id<1:k>。当写入信号wt被输入到第四存储器区域280b时,第四存储器区域280b可以将第一至第k内部数据id<1:k>存储到连接到第一至第n字线wl<1:n>中的、由第一至第m地址信号add<1:m>激活的字线的存储器单元中。当刷新信号ref被输入到第四存储器区域280b中时,第四存储器区域280b可以基于第一至第m刷新地址信号ref_add<1:m>激活第一至第n字线wl<1:n>中的一个或更多个字线。当修复信号sppr被输入到第四存储器区域280b时,第四存储器区域280b可以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第二修复区域300b中包括的第三和第四修复线sr<3:4>中的任何一个。

101.第四内部控制电路290b可以电连接到第四存储器区域280b和第二修复区域300b。第四内部控制电路290b可以在读取操作期间通过输入/输出线io输出从第四存储器区域

280b中读出的第一至第k内部数据id<1:k>。第四内部控制电路290b可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第四存储器区域280b。第四内部控制电路290b可以使用感测和放大第一至第k内部数据id<1:k>的常见的差分放大电路来实现。当修复信号sppr被输入到第四内部控制电路290b时,第四内部控制电路290b可以控制第四存储器区域280b和第二修复区域300b以将第一至第n字线wl<1:n>中的、由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线替代为第二修复区域300b中包括的第三和第四修复线sr<3:4>中的任何一个。当修复信号sppr被输入到第四内部控制电路290b时,第四内部控制电路290b可以复制第一至第k内部数据id<1:k>并且可以控制第四存储器区域280b和第二修复区域300b以将复制的第一至第k内部数据id<1:k>存储到第二修复区域300b中包括的第三和第四修复线sr<3:4>中。

102.第二修复区域300b可以包括第一至第四修复线sr<1:4>。第二修复区域300b中的第一和第二修复线sr<1:2>可用于替代连接到第三存储器区域260b中包括的故障的存储器单元的字线。第二修复区域300b中的第三和第四修复线sr<3:4>可用于替代连接到第四存储器区域280b中包括的故障的存储器单元的字线。

103.图9是示出与图4中所示的刷新控制电路500的另一示例对应的刷新控制电路500a的配置的框图。如图9中所示,刷新控制电路500a可以包括地址存储电路510a、控制信号生成电路520a、计数器530a、选择传输电路540a和修复控制电路550a。

104.地址存储电路510a可以基于故障检测信号fail存储第一至第m地址信号add<1:m>。地址存储电路510a可以存储在故障检测信号fail被使能时的时间点输入的第一至第m地址信号add<1:m>。地址存储电路510a可以存储在故障检测信号fail被使能时的时间点存储的第一至第m地址信号add<1:m>,作为第一至第m故障地址信号fadd<1:m>。

105.控制信号生成电路520a可以基于预控制信号pre_con和刷新信号ref生成控制信号tcon。控制信号生成电路520a可以生成在预控制信号pre_con被输入时使能的控制信号tcon。控制信号生成电路520a可以生成在预控制信号pre_con具有逻辑“高”电平时被使能为具有逻辑“高”电平的控制信号tcon。控制信号生成电路520a可以生成在刷新信号ref被输入第一预定次数时使能的控制信号tcon。例如,控制信号生成电路520a可以生成在刷新信号ref被连续输入两次或更多次时被使能为具有逻辑“高”电平的控制信号tcon。

106.计数器530a可以基于刷新信号ref生成第一至第m计数信号cnt<1:m>。计数器530a可以生成在刷新信号ref被输入时顺次计数的第一至第m计数信号cnt<1:m>。

107.选择传输电路540a可以基于控制信号tcon从第一至第m故障地址信号fadd<1:m>或者第一至第m计数信号cnt<1:m>生成第一至第m刷新地址信号ref_add<1:m>。当控制信号tcon被禁用为具有逻辑“低”电平时,选择传输电路540a可以输出第一至第m计数信号cnt<1:m>作为第一至第m刷新地址信号ref_add<1:m>。当控制信号tcon被使能为具有逻辑“高”电平时,选择传输电路540a可以输出第一至第m故障地址信号fadd<1:m>作为第一至第m刷新地址信号ref_add<1:m>。

108.修复控制电路550a可以响应于故障检测信号fail生成在具有相同的逻辑电平组合的第一至第m地址信号add<1:m>被输入第二预定次数时使能的预控制信号pre_con。修复控制电路550a可以响应于故障检测信号fail生成在具有相同的逻辑电平组合的第一至第m地址信号add<1:m>被输入第三预定次数时使能的修复信号sppr。

109.下面将结合每当第一存储器区域210a的第一字线wl<1>被选择时重复出现错误的情况参照图10描述在半导体器件20a的刷新操作期间执行的修复操作。

110.在时间点t1处,命令解码器100a可以与时钟信号clk同步以从命令信号cmd生成刷新信号ref。

111.地址存储电路510a可以输出在故障检测信号fail被使能时的时间点存储的第一至第m地址信号add<1:m>作为第一至第m故障地址信号fadd<1:m>。

112.在时间点t2处,由于具有相同的逻辑电平组合的第一至第m地址信号add<1:m>被输入第三预定次数,因此修复控制电路550a可以响应于故障检测信号fail生成被使能为具有逻辑“高”电平的修复信号sppr。

113.控制信号生成电路520a可以基于刷新信号ref生成被使能为具有逻辑“高”电平的控制信号tcon。

114.选择传输电路540a可以基于具有逻辑“高”电平的控制信号tcon输出第一至第m故障地址信号fadd<1:m>作为第一至第m刷新地址信号ref_add<1:m>。

115.在时间点t3处,命令解码器100a可以与时钟信号clk同步地从命令信号cmd生成写入信号wt。

116.第一内部控制电路220a可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第一存储器区域210a。响应于具有逻辑“高”电平的修复信号sppr,第一内部控制电路220a可以控制第一存储器区域210a以将与由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线对应的第一字线wl<1>替代为第一修复线sr<1>。

117.在时间点t4处,第一存储器区域210a可以基于具有逻辑“高”电平的修复信号sppr和第一至第m刷新地址信号ref_add<1:m>将故障的第一字线wl<1>替代为第一修复线sr<1>。

118.第一内部控制电路220a可以复制在时间点t3处输入的第一至第k内部数据id<1:k>并且可以将复制的内部数据存储到连接到第一修复线sr<1>的存储器单元中。

119.如上文所述,根据本公开内容的一个实施方式的半导体系统1可以在刷新操作期间在用于选择存储故障的内部数据的故障的存储器单元的地址信号被输入第三预定次数时通过将连接到故障的存储器单元的故障的字线用修复线替代来提高内部数据的可靠性。

120.下面将结合每当第一存储器区域210b的第一字线wl<1>和第二存储器区域230b的第三字线wl<3>被选择时重复出现错误的情况参照图11描述在半导体器件20a的刷新操作期间执行的修复操作。

121.在时间点t11处,命令解码器100a可以与时钟信号clk同步以从命令信号cmd生成刷新信号ref。

122.地址存储电路510a可以输出在故障检测信号fail被使能时的时间点存储的第一至第m地址信号add<1:m>作为第一至第m故障地址信号fadd<1:m>。

123.在时间点t12处,由于具有相同的逻辑电平组合的第一至第m地址信号add<1:m>被输入第三预定次数,因此修复控制电路550a可以响应于故障检测信号fail生成被使能为具有逻辑“高”电平的修复信号sppr。

124.控制信号生成电路520a可以基于刷新信号ref生成被使能为具有逻辑“高”电平的控制信号tcon。

125.选择传输电路540a可以基于具有逻辑“高”电平的控制信号tcon输出第一至第m故障地址信号fadd<1:m>作为第一至第m刷新地址信号ref_add<1:m>。

126.在时间点t13处,命令解码器100a可以与时钟信号clk同步地从命令信号cmd生成写入信号wt。

127.第一内部控制电路220b可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第一存储器区域210b。响应于具有逻辑“高”电平的修复信号sppr,第一内部控制电路220b可以控制第一存储器区域210b以将由第一至第m刷新地址信号ref_add<1:m>选择的故障的第一字线wl<1>替代为第一修复线sr<1>。

128.在时间点t14处,第一存储器区域210b可以基于具有逻辑“高”电平的修复信号sppr和第一至第m刷新地址信号ref_add<1:m>将故障的第一字线wl<1>替代为第一修复线sr<1>。

129.第一内部控制电路220b可以复制在时间点t13处输入的第一至第k内部数据id<1:k>并且可以将复制的内部数据存储到连接到第一修复线sr<1>的存储器单元中。

130.在时间点t15处,命令解码器100a可以与时钟信号clk同步地从命令信号cmd生成写入信号wt。

131.第二内部控制电路240b可以在写入操作期间将输入/输出线io上加载的第一至第k内部数据id<1:k>输出到第二存储器区域230b。第二内部控制电路240b可以基于具有逻辑“高”电平的修复信号sppr和第一至第m刷新地址信号ref_add<1:m>控制第二存储器区域230b以将故障的第三字线wl<3>替代为第二修复线sr<2>。

132.在时间点t16处,第二存储器区域230b可以基于具有逻辑“高”电平的修复信号sppr和第一至第m刷新地址信号ref_add<1:m>将故障的第三字线wl<3>替代为第二修复线sr<2>。

133.第二内部控制电路240b可以复制在时间点t15处输入的第一至第k内部数据id<1:k>并且可以将复制的内部数据存储到连接到第二修复线sr<2>的存储器单元中。

134.根据本公开内容的一个实施方式的半导体系统1的纠错方法可以在刷新操作期间在用于选择存储故障的内部数据的故障的存储器单元的地址信号被输入第三预定次数时通过将连接到故障的存储器单元的故障的字线用修复线替代来提高内部数据的可靠性。

135.下面将参照图12描述根据本公内容的另一实施方式的半导体系统的纠错方法。

136.纠错方法可以包括读取操作步骤s4、纠错步骤s5和刷新步骤s6。

137.读取操作步骤s4可以包括命令输入步骤s41、读取操作检测步骤s42和内部数据输出步骤s43。

138.命令输入步骤s41可以对应于从控制器10向半导体器件20a传送时钟信号clk、命令信号cmd和第一至第m地址信号add<1:m>用于执行读取操作的步骤。

139.读取操作检测步骤s42可以对应于基于从控制器10输出的时钟信号clk和命令信号cmd生成读取信号rd的步骤。

140.内部数据输出步骤s43可以对应于基于读取信号rd和第一至第m地址信号add<1:m>将核心电路200a中存储的第一至第k内部数据id<1:k>输出到输入/输出线io的步骤。

141.纠错步骤s5可以包括错误检测步骤s51、数据纠错步骤s52、地址锁存步骤s53和数据输出步骤s54。

142.错误检测步骤s51可以对应于通过使用纠错电路400a检测在输入/输出线io上加载的第一至第k内部数据id<1:k>的错误的步骤。当在错误检测步骤s51处在第一至第k内部数据id<1:k>中存在错误时(是),纠错电路400a可以生成故障检测信号fail。刷新控制电路500a可以基于故障检测信号fail存储第一至第m地址信号add<1:m>。当在错误检测步骤s51处在第一至第k内部数据id<1:k>中不存在错误时(否),可以执行数据输出步骤s54。

143.数据纠错步骤s52可以对应于在纠错电路400a中使用纠错码(ecc)纠正第一至第k内部数据id<1:k>的错误的步骤。

144.地址锁存步骤s53可以对应于在故障检测信号fail被使能时将第一至第m地址信号add<1:m>存储在刷新控制电路500a中作为第一至第m故障地址信号fadd<1:m>的步骤。

145.数据输出步骤s54可以对应于在数据输入/输出电路300a中通过缓冲在数据纠错步骤s52处纠正的第一至第k内部数据id<1:k>来生成第一至第k数据data<1:k>的步骤。数据输出步骤s54还可以对应于将由数据输入/输出电路300a生成的第一至第k数据data<1:k>输出到控制器10的步骤。

146.刷新步骤s6可以包括刷新操作检测步骤s61、计数操作步骤s62、计数检测步骤s63、预定次数检测步骤s64、修复检测步骤s65、修复操作步骤s66、故障刷新步骤s67和正常刷新步骤s68。

147.刷新操作检测步骤s61可以对应于基于从控制器10输出的时钟信号clk和命令信号cmd生成刷新信号ref的步骤。

148.计数操作步骤s62可以对应于每当刷新信号ref被输入到刷新控制电路500a时检测刷新信号ref的步骤。

149.计数检测步骤s63可以对应于检测刷新信号ref是否被输入到刷新控制电路500a第一预定次数的步骤。

150.当在计数检测步骤s63处刷新信号ref被输入到刷新控制电路500第一预定次数时(是),可以执行修复检测步骤s65。

151.预定次数检测步骤s64可以对应于检测在地址锁存步骤s53处的包括错误的第一至第k内部数据id<1:k>是否被输入第二预定次数的步骤。

152.当在预定次数检测步骤s64处包括错误的第一至第k内部数据id<1:k>被输入第二预定次数时(是),可以执行修复检测步骤s65。

153.当在计数检测步骤s63处刷新信号ref被输入到刷新控制电路500第一预定次数或更多次时(是),可以执行修复检测步骤s65。当在计数检测步骤s63处刷新信号ref被输入到刷新控制电路500的次数小于第一预定次数时(否),可以执行正常刷新步骤s68。

154.修复检测步骤s65可以对应于检测包括错误的第一至第k内部数据id<1:k>是否被输入第三预定次数的步骤。当在修复检测步骤s65处包括错误的第一至第k内部数据id<1:k>被输入第三预定次数时(是),可以执行修复操作步骤s66。

155.修复操作步骤s66可以执行将连接到存储包括错误的第一至第k内部数据id<1:k>的存储器单元的字线替代为核心电路200a中的修复线的修复操作。

156.当在修复检测步骤s65处包括错误的第一至第k内部数据id<1:k>未被输入第三预定次数时(否),可以执行故障刷新步骤s67。

157.故障刷新步骤s67可以对应于在刷新控制电路500a中从第一至第m地址信号add<

1:m>生成用于激活连接到存储包括错误的第一至第k内部数据id<1:k>的存储器单元的字线的第一至第m刷新地址信号ref_add<1:m>的步骤。故障刷新步骤s67可以对应于在核心电路200a中通过额外激活由第一至第m刷新地址信号ref_add<1:m>选择的故障的字线来执行刷新操作的步骤。

158.正常刷新步骤s68可以对应于在刷新控制电路500a中生成被顺次使能以顺次激活核心电路200中包括的多个字线的第一至第m刷新地址信号ref_add<1:m>的步骤。正常刷新步骤s68可以对应于基于刷新信号ref和顺次计数的第一至第m刷新地址信号ref_add<1:m>通过顺次激活核心电路200中的多个字线来执行刷新操作的步骤。

159.根据本公开内容的另一实施方式的半导体系统1的纠错方法可以在刷新操作期间在用于选择存储故障的内部数据的故障的存储器单元的地址信号被输入第三预定次数时通过将连接到故障的存储器单元的故障的字线用修复线替代来提高内部数据的可靠性。

160.如参照图1至图12描述的,根据本公开内容的实施方式的纠错方法以及在纠错方法中使用的半导体器件和半导体系统可以在刷新操作期间在刷新信号被重复输入第一预定次数时通过额外刷新连接到存储错误的内部数据的故障的存储器单元的字线来提高内部数据的可靠性。纠错方法以及在纠错方法中使用的半导体器件和半导体系统可以在刷新操作期间在用于选择故障的存储器单元的地址信号被输入第二预定次数时通过额外刷新连接到存储错误的内部数据的故障的存储器单元的字线来提高内部数据的可靠性。纠错方法以及在纠错方法中使用的半导体器件和半导体系统可以在刷新操作期间在用于选择故障的存储器单元的地址信号被输入第三预定次数时通过将连接到故障的存储器单元的字线用修复线替代来提高内部数据的可靠性。

161.图13是示出根据本公开内容的一个实施方式的电子系统1000的配置的框图。如图13中所示,电子系统1000可以包括主机1100和半导体系统1200。

162.主机1100和半导体系统1200可以使用接口协议彼此传送信号。用于主机1100和半导体系统1200之间的通信的接口协议可以包括各种接口协议中的任一者,诸如多媒体卡(mmc)、增强小型器件接口(esdi)、集成驱动电子器件(ide)、外围部件快速互连(pci-e)、增强技术附连(ata)、串行ata(sata)、并行ata(pata)、串行附连scsi(sas)和通用串行总线(usb)。

163.半导体系统1200可以包括控制器1300和半导体器件1400(k:1)。控制器1300可以控制半导体器件1400(k:1),使得半导体器件1400(k:1)执行读取操作、写入操作、刷新操作和修复操作。半导体器件1400(k:1)中的每个可以在刷新操作期间在刷新信号被重复输入第一预定次数时通过额外刷新连接到存储错误的内部数据的故障的存储器单元的字线来提高内部数据的可靠性。半导体器件1400(k:1)中的每个可以在刷新操作期间在用于选择故障的存储器单元的地址信号被输入第二预定次数时通过额外刷新连接到存储错误的内部数据的故障的存储器单元的字线来提高内部数据的可靠性。半导体器件1400(k:1)中的每个可以在刷新操作期间在用于选择故障的存储器单元的地址信号被输入第三预定次数时通过将连接到故障的存储器单元的字线用修复线替代来提高内部数据的可靠性。

164.控制器1300可以使用图1中所示的控制器实现。半导体器件1400(k:1)中的每个可以使用图1和图2中所示的半导体器件20来实现。在一些实施方式中,半导体器件1400(k:1)中的每个可以使用动态随机存取存储器(dram)、相变随机存取存储器(pram)、电阻随机存

取存储器(rram)、磁随机存取存储器(mram)和铁电随机存取存储器(fram)中的任一者来实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1