尖峰神经单元的制作方法

1.本公开大体上涉及存储器,且更特定来说,涉及与存储器中的尖峰神经单元相关联的设备及方法。

背景技术:

2.存储器装置通常被提供为计算机或其它电子装置中的内部半导体集成电路。存在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器可需要电力来维持其数据且包含随机存取存储器(ram)、动态随机存取存储器(dram)及同步动态随机存取存储器(sdram)等等。非易失性存储器可通过在未被供电时保留经存储数据来提供持久数据且可包含nand快闪存储器、nor快闪存储器、只读存储器(rom)、电可擦除可编程rom(eeprom)、可擦除可编程rom(eprom)及电阻可变存储器,例如相变随机存取存储器(pcram)、3d xpoint

tm

、电阻式随机存取存储器(rram)及磁阻式随机存取存储器(mram)等等。

3.存储器还用作广泛范围的电子应用的易失性及非易失性数据存储装置。包含但不限于个人计算机、便携式存储棒、数码相机、蜂窝电话、便携式音乐播放器(例如mp3播放器)、电影播放器及其它电子装置。存储器单元可布置成阵列,其中所述阵列用于存储器装置中。

4.人工神经网络是可通过对神经元(例如人脑中的神经元)网络进行建模以处理已在特定环境中感测到的信息(例如,刺激)来处理信息的网络。与人脑类似,神经网络通常包含多神经元拓扑(例如,其可被称为人工神经元)。

附图说明

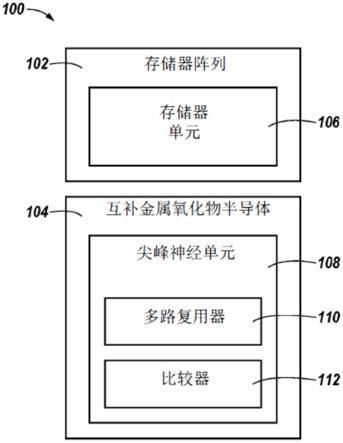

5.图1是根据本公开的数个实施例的包含存储器阵列及互补金属氧化物半导体(cmos)的设备的框图。

6.图2是根据本公开的数个实施例的包含多个尖峰神经单元的互补金属氧化物半导体(cmos)的框图。

7.图3是根据本公开的数个实施例的包含控制器及神经网络的系统的框图。

8.图4说明根据本公开的数个实施例的用于尖峰神经单元的方法的实例流程图。

9.图5说明根据本公开的数个实施例的人工神经元的实例。

10.图6是根据本公开的数个实施例的存储器装置的实例逻辑块的框图。

11.图7说明根据本公开的数个实施例的实例神经网络。

12.图8说明计算机系统的实例机器,可在所述计算机系统内执行用于致使所述机器执行本文中论述的各种方法的一组指令。

具体实施方式

13.本公开包含与存储器中的尖峰神经单元相关联的设备及方法。实施例包含:存储

器阵列;及互补金属氧化物半导体(cmos),其耦合到所述存储器阵列且定位在所述存储器阵列下,其中所述cmos包含尖峰神经单元,所述尖峰神经单元包括经配置以进行以下操作的逻辑:接收输入以增加存储在所述存储器阵列的存储器单元中的权重;从所述存储器阵列的所述存储器单元收集所述权重;使具有基于所述输入的增加量的所述权重累加;将所述经累加权重与阈值权重进行比较;及响应于所述经累加权重大于所述阈值权重而提供输出。在一些实例中,耦合到所述存储器阵列的所述cmos中的所述尖峰神经单元可减少处理时间并提高装置的性能。

14.尖峰神经单元可用于信息处理应用,包含机器学习(例如,深度学习)。例如,尖峰神经单元可用于图像辨识、声音辨识及/或自然语言处理。

15.尖峰神经单元可包含多路复用器及比较器。多路复用器可收集存储在存储器单元中的权重且比较器可将来自存储器单元的权重与阈值权重进行比较。在一些实例中,可响应于来自存储器单元的权重大于阈值权重而确定尖峰神经单元已尖峰化且学习已发生。例如,计算机感测、语音辨识(例如,来自用户)、机器翻译及/或社交网络过滤可使用尖峰神经单元来处理。

16.如本文中所使用,“数个”某物可指此类事物中的一或多者。例如,数个存储器装置可指一或多个存储器装置。“多个”某物意指两个或更多个。另外,如本文中所使用,特别是关于附图中的参考数字所使用的指定符,例如“k”、“l”、“m”、“n”、“p”、“q”、“r”及“s”指示如此指定的数个特定特征可被包含在本公开的数个实施例中。

17.本文中的图遵循编号约定,其中首位或前几位数字对应于附图图号且剩余数字识别附图中的元件或组件。不同图之间的类似元件或组件可通过使用类似数字来识别。例如,参考数字104可指代图1中的元件“04”,且类似元件可被引用为图2中的204。在一些例子中,相同图或不同图中的多个类似但功能上及/或结构上可区别的元件或组件可用相同元件编号循序地引用(例如,图2中的209-1、208-2、208-3及208-m)。如将明白,可添加、交换及/或消除本文中的各个实施例中所展示的元件以便提供本公开的数个额外实施例。另外,所述图中所提供的元件的比例及相对尺度意在说明本公开的各个实施例而非以限制意义进行使用。

18.图1是根据本公开的数个实施例的呈包含存储器阵列102及互补金属氧化物半导体(cmos)104的存储器装置100的形式的设备的框图。如本文中所使用,“设备”可指但不限于多种结构或结构组合。例如,存储器阵列102及cmos 104也可被单独地视为“设备”。如图1中所说明,cmos 104可定位在存储器阵列102下(例如,下方)。存储器阵列102可经形成在cmos 104上。例如,存储器阵列102的底表面可接触及/或耦合到cmos 104的顶表面。

19.存储器阵列102可包含一或多个存储器单元106且cmos 104可包含尖峰神经单元108。尖峰神经单元108可包括逻辑。例如,所述逻辑可为包含经配置以执行操作的多个逻辑块的逻辑组件。所述操作可包含:接收输入以增加存储在存储器阵列102的一或多个存储器单元106中的权重;从存储器阵列102的一或多个存储器单元106收集权重;使具有基于输入的增加量的权重累加;将经累加权重与阈值权重进行比较;以及响应于经累加权重大于阈值权重而提供输出。

20.在一些实例中,尖峰神经单元108可包含多路复用器110及/或比较器112。多路复用器110可耦合到存储器阵列102且可从存储器阵列102的一或多个存储器单元106收集权

重。收集权重可包含从一或多个存储器单元106感测对应于人工神经元的经加权输入的信号。一或多个感测放大器可对感测信号进行采样且将感测信号从存储器阵列102传输到包含在存储器阵列102下的cmos 104中的尖峰神经单元108。尽管图1中未展示,但在一些实例中,存储器阵列102及尖峰神经单元108可传输感测信号且经由一或多个通信线彼此耦合。

21.多路复用器110可响应于自先前收集具有增加量的权重以来经过特定时间段及/或响应于特定数目个信号经施加到一或多个存储器单元106而从一或多个存储器单元106收集权重。在一些实例中,多路复用器110可响应于尖峰神经单元108接收命令而收集权重。

22.响应于接收输入以增加权重,可计算具有基于输入的增加量的经累加权重。例如,可执行求和函数以使具有基于输入的增加量的权重累加。

23.比较器112可将经累加权重与阈值权重进行比较。可使用阈值函数(例如,阶跃函数)以将经累加权重与阈值权重进行比较。阈值函数可确定经累加权重是高于还是低于阈值权重。例如,如果经累加权重大于或等于阈值权重,那么阈值函数可在所述输出上产生逻辑高输出(例如,逻辑1),且如果经累加权重低于阈值权重,那么可在所述输出上产生逻辑低(例如,逻辑0)。阈值权重可为足以指示学习已发生的权重。

24.在数个实施例中,尖峰神经单元108可将经累加权重存储在存储器阵列102中。尖峰神经单元108可响应于经累加权重小于阈值而将经累加权重存储在存储器阵列102中。例如,存储器阵列102的一或多个存储器单元106可在尖峰神经单元108尚未尖峰化且学习尚未发生时继续增加权重且存储经累加权重。

25.可刷新(例如,加强)存储权重的一或多个存储器单元106以存储经累加权重。在存储经累加权重之后,可刷新一或多个存储器单元106以防止经累加权重随时间推移而改变(例如,漂移)。可响应于一或多个存储器单元106接收输入以增加存储在一或多个存储器单元中的权重及/或响应于刷新命令而刷新一或多个存储器单元106。在一些实例中,可响应于从先前刷新一或多个存储器单元106以来经过特定时间段而刷新一或多个存储器单元106。

26.在数个实施例中,可擦除一或多个存储器单元106。例如,可删除存储在一或多个存储器单元106中的经累加权重。可响应于经累加权重大于阈值权重及/或响应于提供输出而删除存储在一或多个存储器单元106中的经累加权重。例如,可在尖峰神经单元108已尖峰化且学习已发生时擦除一或多个存储器单元106。然而,实施例不限于此,因为在至少一个实施例中,一或多个存储器单元106可在尖峰神经单元108已尖峰化之后继续存储经累加权重。

27.图2是根据本公开的数个实施例的包含多个尖峰神经单元208-1、208-2、208-3、

…

、208-m的互补金属氧化物半导体204(cmos)的框图。多个神经尖峰单元208-1、

…

、208-m可传输数据且经由通信线220-1、220-2、220-3、

…

、220-4彼此耦合。通信线220-1、

…

、220-4可在行及列中互连尖峰神经单元208-1、

…

、208-m。尖峰神经单元208-1、

…

、208-m还可包含延伸到神经尖峰单元208-1、

…

、208-m及/或cmos 204外的通信线220-5、220-6、220-7、220-8、220-9、220-10、220-11、

…

、220-12。通信线220-5、

…

、220-12可将尖峰神经单元208-1、

…

、208-m耦合到不同cmos上的尖峰神经单元及/或耦合到控制器。通信线220-1、

…

、220-12可实现尖峰神经单元208-1、

…

、208-m之间、尖峰神经单元208-1、

…

、208-m与不同cmos上的尖峰神经单元及/或尖峰神经单元208-1、

…

、208-m与控制器之间的数据通信。

28.多个尖峰单元208-1、

…

、208-m可每一者包括逻辑。例如,所述逻辑可为包含经配置以执行操作的多个逻辑块的逻辑组件。所述操作可包含:经由多个尖峰单元208-1、

…

、208-m中的一者接收输入以增加存储在存储器阵列的一或多个存储器单元中的权重;经由多个尖峰单元208-1、

…

、208-m中的一者收集权重;使具有基于输入的增加量的权重累加;将经累加权重与阈值权重进行比较;以及响应于经累加权重大于阈值权重而提供输出。可响应于经累加权重小于阈值权重而将经累加权重存储回存储器阵列的一或多个存储器单元中。

29.多个尖峰单元208-1、

…

、208-m中的每一者可经配置以接收输入以增加存储在存储器阵列的多个存储器单元中的权重。所述输入可经由通信线220-1、

…

、220-4通过多个尖峰单元208-1、

…

、208-m中的一或多者从控制器发送。所述输入可为电信号,例如,施加到多个尖峰单元208-1、

…

、208-m中的一或多者的电压。

30.可由多个尖峰单元208-1、

…

、208-m中的一者收集权重。可响应于自先前收集权重以来经过特定时间段、响应于特定数目个信号经施加到一或多个存储器单元及/或响应于多个尖峰神经单元208-1、

…

、208-m中的一者接收命令而收集权重。在一些实例中,可使用多路复用器来收集权重。

31.多个尖峰单元208-1、

…

、208-m中的每一者可使具有基于输入的相应增加量的相应权重累加,且将经累加权重与阈值权重进行比较。阈值权重可为足以使学习发生的权重。可响应于累加权重及/或响应于多个尖峰神经单元208-1、

…

、208-m中的一者接收命令而将经累加权重与阈值权重进行比较。可基于多个尖峰单元208-1、

…

、208-m累加权重达到阈值权重所花费的平均时间来设置特定时间段。在一些实例中,可使用比较器来将经累加权重与阈值权重进行比较。

32.输出(例如,经累加权重与阈值权重的比较结果)可经由第二尖峰神经单元208-2从第一尖峰神经单元208-1提供到控制器及/或直接从第一尖峰单元208-1提供到控制器。在一些实例中,可响应于经累加权重大于阈值权重而提供输出。例如,尖峰神经单元208-1可将输出发送到控制器以通知控制器学习已发生。在一些实例中,控制器可在存储器阵列及cmos 204外部。

33.在数个实施例中,多个尖峰神经单元208-1、

…

、208-m可被包含在神经网络中。神经网络可执行各种机器学习算法以处理输入。可由神经网络处理的实例任务可包含计算机视觉、语音辨识、机器翻译、社交网络过滤及/或医学诊断。

34.神经网络可包含多个层,所述多个层每一者包含多个尖峰神经单元208-1、

…

、208-m中的一或多者,如结合图7进一步描述。来自层上的多个尖峰神经单元中的一者,例如第一尖峰神经单元208-1的输出可由不同层上的不同尖峰神经单元,例如第二尖峰神经单元208-2来接收。可刷新一或多个存储器单元。刷新可包含对一或多个存储器单元的读取及写入操作。例如,刷新可重写存储在一或多个存储器单元中的权重以保存权重数据。可响应于经累加权重小于阈值权重而对一或多个存储器单元执行刷新。如先前所论述,阈值权重可为足以使学习发生的权重。

35.可擦除一或多个存储器单元。擦除可从一或多个存储器单元移除数据。可响应于经累加权重达到阈值权重而有效地擦除存储在一或多个存储器单元中的权重。可在读取而非刷新数据时有效地擦除一或多个存储器单元。在使用除dram之外的存储器单元的一些实

例中,可通过主动擦除机制来擦除一或多个存储器单元。

36.图3是根据本公开的数个实施例的呈包含控制器332及神经网络334的计算机系统330的形式的系统的框图。例如,系统330可为服务器系统及/或高性能计算(hpc)系统及/或其一部分。控制器332可包括状态机、定序器及/或某种其它类型的控制电路系统,且包含呈专用集成电路(asic)、现场可编程门阵列等的形式的硬件及/或固件(例如,微代码指令)。控制器332可定位在多个存储器装置300-1、300-2、300-3、

…

、300-n中的每一者的本地。换句话说,尽管图3中说明一个控制器332,但存储器系统330可包含每一者定位在相应存储器装置300-1、

…

、300-n的本地的多个控制器。在一些实例中,神经网络334可为动态随机存取存储器(dram)。神经网络334可包含多个存储器装置300-1、

…

、300-n。

37.在各个实施例中,多个存储器装置300-1、

…

、300-n可为三维的(3d)且可包含堆叠在一起的多个层。作为实例,多个存储器装置300-1、

…

、300-n中的每一者可包含:第一层,其包含逻辑组件(例如,逻辑块、行驱动器及/或列驱动器);及第二层,其堆叠在第一层上且包含例如阵列或存储器单元的存储器组件。多个存储器装置300-1、

…

、300-n可包括布置成通过存取线(其在本文中可被称为字线或选择线)耦合的行及通过感测线(其在本文中可被称为数字线或数据线)耦合的列的存储器单元。例如,存储器单元阵列可包含但不限于dram阵列、sram阵列、stt ram阵列、pcram阵列、tram阵列、rram阵列、nand快闪存储器阵列及/或nor快闪存储器阵列。多个存储器装置300-1、

…

、300-n可呈形成为芯片上的集成电路的多个个别存储器裸片及/或相异存储器层的形式。在一些实例中,存储器装置300-1、

…

、300-n中的每一者可包含耦合到互补金属氧化物半导体(cmos)304-1、304-2、304-3、

…

、304-q的存储器阵列302-1、

…

、302-p。每一cmos 304-1、

…

、304-q可包含多个尖峰神经单元,如图2中所说明。

38.存储器装置300-1、

…

、300-n可经由通信线336-1、

…

、336-6将数据传输到控制器332及从控制器332传输数据。控制器332可经由通信线336-1、

…

、336-6及多个存储器装置300-1、

…

、300-n中的一或多者发送命令(例如,输入)。所述命令可为从控制器332发送到多个存储器装置300-1、

…

、300-n中的一或多者的电信号。在一些实例中,控制器332可发送命令以增加存储在存储器装置300-n的存储器阵列302-p的多个存储器单元中的权重。所述命令可经由通信线336-3、存储器装置300-3及通信线336-4从控制器332发送到存储器装置300-n。

39.在数个实施例中,多个存储器装置300-1、

…

、300-n可从控制器332接收数个不同命令。例如,多个存储器装置300-1、

…

、300-n可接收命令以从存储器阵列的多个存储器单元收集权重,使具有基于输入的增加量的权重累加,将经累加权重与阈值权重进行比较,及/或响应于经累加权重大于阈值权重而将输出提供到控制器332。

40.在一些实例中,存储器装置300-1、

…

、300-n中的一或多者可经由通信线336-1、

…

、336-6及一或多个存储器装置300-1、

…

、300-n将输出(例如,电信号)提供到控制器332。例如,存储器装置300-2可经由通信线336-2、存储器装置300-1及通信线336-1将输出发送到控制器332。响应于从控制器332接收命令以提供输出,可由多个存储器装置300-1、

…

、300-n中的一或多者提供输出。

41.控制器332还可将刷新及/或擦除命令发送到多个存储器装置300-1、

…

、300-n。刷新命令可引导多个存储器装置300-1、

…

、300-n中的一或多者刷新一或多个存储器单元。刷

新可包含对一或多个存储器单元的读取及写入操作。例如,刷新可重写存储在一或多个存储器单元中的权重以保存权重数据。控制器332可响应于所述权重小于及/或等于阈值权重而发送刷新命令。如结合图2所论述,阈值权重可为足以使学习发生的权重。

42.擦除命令可引导多个存储器装置300-1、

…

、300-n中的一或多者擦除一或多个存储器单元。擦除可从一或多个存储器单元移除数据。例如,擦除可消散存储在一或多个存储器单元中的权重。可响应于所述权重大于及/或等于阈值权重而移除存储在一或多个存储器单元中的权重。

43.尽管图3中未展示,但存储器系统330还可包含可由控制器332控制以解码例如从主机接收的地址信号的解码器(例如,行/列解码器)。可经由控制器332将经解码地址信号进一步提供到行/列驱动器,所述行/列驱动器可激活多个存储器装置300-1、

…

、300-n的存储器单元阵列的行/列。

44.图4说明根据本公开的数个实施例的用于尖峰神经单元的实例方法440。方法440可例如由分别结合图1及3所描述的存储器装置100及/或300执行。

45.在框442处,方法440包含经由包括逻辑的尖峰神经单元接收输入,以增加存储在存储器阵列的存储器单元中的权重。所述输入可为电信号。例如,所述输入可为施加到耦合到所述尖峰神经单元的阵列的一或多个存储器单元的电压。所述输入可从不同尖峰神经单元及/或控制器发送。所述尖峰神经单元与所述不同尖峰神经单元及/或控制器之间的一或多个数据线可传输所述输入。

46.在框444处,方法440包含经由尖峰神经单元收集权重。所述权重可经由多路复用器收集。可响应于自先前收集权重以来经过特定时间段、响应于特定数目个信号经施加到一或多个存储器单元及/或响应于多个尖峰神经单元中的一者接收命令而收集权重。

47.在框446处,方法440包含使具有基于输入的增加量的权重累加。可通过执行求和计算来累加权重。例如,尖峰神经单元可执行求和计算以确定具有基于输入的增加量的权重。

48.在框448处,方法440包含将经累加权重与阈值权重进行比较。可由尖峰神经单元将经累加权重与阈值权重进行比较。阈值权重可为足以使学习发生的权重。可响应于自先前比较以来经过特定时间段、响应于累加权重及/或响应于尖峰神经单元接收命令而将经累加权重与阈值权重进行比较。在一些实例中,可使用比较器来将经累加权重与阈值权重进行比较。

49.在框450处,方法440包含响应于经累加权重大于阈值权重而将输出提供到控制器。输出(例如,经累加权重与阈值权重的比较结果)可从尖峰神经单元提供到不同尖峰神经单元。例如,所述尖峰神经单元可将输出发送到所述不同尖峰神经单元及/或经由所述不同尖峰神经单元发送到控制器。在一些实例中,可响应于经累加权重大于阈值权重而提供输出。例如,所述尖峰神经单元可将输出发送到控制器以通知控制器学习已发生。

50.图5说明根据本公开的数个实施例的人工神经元552的实例。人工神经元552可用以模拟(例如,人脑的)生物神经元。此类神经元有时可被称为感知器。可被称为刺激的数个输入x1到xn可分别施加到神经元552的输入554-1、554-2、

…

、554-r。对应于输入x1到xn的信号,例如电压、电流或特定数据值(例如,二进制数字)可响应于感测某种形式的刺激而产生且可施加输入554-1、554-2、

…

、554-r。

51.在各种例子中,输入x1到xn可分别由可被称为突触权重的权重w1到wn来加权。例如,输入x1到xn可分别乘以权重w1到wn以分别对输入x1到xn进行加权。例如,每一经加权输入可被称为突触,且所述权重可对应于人脑行为中的记忆。

52.神经元552可包含求和函数556,所述求和函数可对经加权输入执行加法运算以产生输出558,例如sum=x1w1+x2w2+

…

+xnwn。例如,在神经网络理论中,“sum”可被称为“net”(例如,来自术语“network”)。例如,可对对应于经加权输入x1w1到xnwn的经加权信号进行求和。在一些实例中,所述求和函数可被称为传递函数。神经元552进一步包含经配置以响应于求和sum且在输出562处产生输出值y的函数560,例如函数在一些实例中,函数560可被称为激活函数。神经元的输出有时可被称为类。

53.各种函数可用于函数560。例如,函数560可包含阈值函数(例如,阶跃函数)以确定sum是高于还是低于特定阈值水平。如果sum大于或等于特定阈值量,那么此阈值函数可在输出562上产生逻辑高输出(例如,逻辑1),且如果sum低于特定阈值量,那么可在输出562上产生逻辑低(例如,逻辑0)。

54.在一些实例中,函数560可为s型函数,其中s型函数可被表达为s(z)=1/(1+e

λz

),其中λ是常数且z可为sum。例如,函数560可为非线性函数。在一些实例中,输出562处的经产生输出值y可施加到神经元的神经网络(例如,图3中的神经网络334)的数个额外神经元,例如不同神经元的输入554。函数560可进一步包含符号函数及/或线性函数等等。

55.图6是根据本公开的数个实施例的存储器装置的实例逻辑块664的框图。逻辑块664可为包含在存储器装置,例如如先前分别结合图1及3所描述的存储器装置100及/或300内的多个逻辑块中的一者。

56.逻辑块可为可配置逻辑块(clb),其为现场可编程门阵列(fpga)的基本构建块。fpga是指有能力改变其数据路径及/或在现场重新编程的芯片。借助此能力,fpga可在例如中央处理单元(cpu)与图形处理单元(gpu)之间灵活切换。作为实例,可在现场对已用作微处理器的fpga进行重新编程以将其用作图形卡及/或加密单元。

57.如图6中所说明,逻辑块664包含逻辑670。逻辑670可为基于lut的逻辑。作为实例,逻辑670的物理位置(例如,地址)可经映射到逻辑地址且映射信息可经存储在查找表中。

58.逻辑块664可进一步包含可经启用以激活如先前分别结合图1及3所描述的存储器阵列102及/或302的行(或若干行)及/或列(或若干列)的行驱动器666及列驱动器668。如本文中所描述,行驱动器666及列驱动器668可接收由相应行解码器及列解码器解码的地址信号,所述行解码器及列解码器可由控制器,例如先前结合图3所描述的控制器332来控制。尽管图6中未展示,但逻辑块664还可包含(例如,耦合到)将逻辑块664耦合到另一逻辑块及/或另一外部装置(例如,定位在存储器装置300的外部的装置)的多个数据总线。将逻辑块664耦合到另一逻辑块的逻辑块664的数据总线可包含互连光纤。

59.图7说明根据本公开的数个实施例的实例神经网络734。神经网络734可包含具有节点774-1到774-s(包含如先前分别结合图1及图2所描述的尖峰神经单元108及/或208)的神经网络层772(例如,输入层),所述节点接收各种输入,例如如先前结合图5所描述的输入x1到xn。每一神经网络层(例如,神经网络层772、774-1、774-2、774-3及776)的节点可对应于如本文中所描述的人工神经元。

60.神经网络734可包含神经网络层774-1、774-2、774-3。神经网络层774-1可包含节

点778-1到778-l。如互连区780-1中所说明,相应节点778-1到778-l中的每一者可经耦合以从节点774-1到774-s接收输入。神经网络层774-2可包含节点782-1到782-l。如互连区780-2中所说明,相应节点782-1到782-l中的每一者可经耦合以从节点778-1到778-l接收输入。神经网络层774-3可包含节点784-1到784-l。如互连区780-3中所说明,相应节点784-1到784-l中的每一者可经耦合以从节点782-1到782-l接收输入。神经网络734可在训练过程中进行配置,其中互连区780中的各种连接被指派权重值或用用于节点778、782或784处的操作或计算的新权重值更新。训练过程可取决于神经网络734的特定应用或使用而不同。例如,可针对图像辨识、语音辨识或任何数目个其它处理或计算任务训练神经网络。

61.神经网络734可包含具有输出节点786-1到786-k的输出层776。相应输出节点786-1到786-k中的每一者可经耦合以从节点784-1到784-l接收输入。接收作为馈送到神经网络层772处的节点774的输入的结果的在输出层776及输出节点786处的有用输出的过程可被称为推理或前向传播。即,可将表示某个现实世界现象或应用的输入信号馈送到经训练神经网络734中且通过作为由各种节点及互连实现的计算的结果而发生的推理,可输出结果。在针对语音辨识训练的神经网络734的情况下,输入可为表示一种语言中的人类语音的信号,且输出可为表示不同语言中的人类语音的信号。或对于针对图像辨识训练的神经网络734,输入可为表示照片的信号且输出可为表示照片中的主体的信号。

62.如本文中所描述,多个神经网络可经配置在存储器装置内。可单独地训练多个神经网络(本地或远程)且经训练神经网络可用于存储器装置内的推理。多个神经网络可执行相同或不同功能且可相对于彼此具有相同或不同的权重。

63.图8说明计算机系统830的实例机器,可在所述计算机系统内执行用于致使所述机器执行本文中所论述的各种方法的一组指令。在各个实施例中,计算机系统830(例如,图3中的计算机系统330)可耦合到或利用存储器子系统或可用以执行控制器(例如,图1中的控制器332)的操作。在替代实施例中,所述机器可经连接(例如,联网)到lan、内联网、外联网及/或因特网中的其它机器。所述机器可在客户端-服务器网络环境中以服务器或客户端机器的身份操作,作为对等(或分布式)网络环境中的对等机器,或作为云计算基础架构或环境中的服务器或客户端机器。

64.所述机器可为个人计算机(pc)、平板pc、机顶盒(stb)、个人数字助理(pda)、蜂窝电话、网络设施、服务器、网络路由器、交换机或网桥,或能够执行一组指令(循序或其它)的任何机器,所述组指令指定将由那个机器采取的动作。此外,虽然说明单个机器,但术语“机器”也应被理解为包含个别地或联合执行一组(或多组)指令以执行本文中所论述的方法中的任何一或多者的机器的任何集合。

65.实例计算机系统830包含经由总线895彼此进行通信的处理装置888、主存储器890(例如,只读存储器(rom)、快闪存储器、动态随机存取存储器(dram),例如同步dram(sdram)或rambus dram(rdram)等)、静态存储器892(例如,快闪存储器、静态随机存取存储器(sram)等)及数据存储系统894。

66.处理装置888表示一或多个通用处理装置,例如微处理器、中央处理单元(cpu)等。更特定来说,所述处理装置可为复杂指令集计算(cisc)微处理器、精简指令集计算(risc)微处理器、超长指令字(vliw)微处理器,或实施其它指令集的处理器,或实施指令集组合的处理器。处理装置888也可为一或多个专用处理装置,例如专用集成电路(asic)、现场可编

程门阵列(fpga)、数字信号处理器(dsp)、网络处理器等。处理装置888经配置以执行指令896以执行本文中所论述的操作及步骤。计算机系统830可进一步包含网络接口装置898以通过网络897进行通信。

67.数据存储系统894可包含其上存储有体现本文中所描述的方法或功能中的任何一或多者的一组或多组指令896或软件的机器可读存储媒体899(也被称为计算机可读媒体)。指令896还可在由计算机系统830执行期间完全或至少部分地驻留在主存储器890及/或处理装置888内,主存储器890及处理装置888也构成机器可读存储媒体。

68.在一个实施例中,指令896包含用以实施对应于存储器装置(例如,图1中的存储器装置100)的功能性的指令。虽然机器可读存储媒体899在实例实施例中被展示为单个媒体,但术语“机器可读存储媒体”应被理解为包含存储一或多组指令的单个媒体或多个媒体。术语“机器可读存储媒体”还应被理解为包含能够存储或编码一组指令以供机器执行且致使机器执行本公开的方法中的任何一或多者的任何媒体。因此,术语“机器可读存储媒体”应被理解为包含但不限于固态存储器、光学媒体及磁性媒体。

69.尽管本文中已说明及描述特定实施例,但所属领域的一般技术人员将明白,经计算以实现相同结果的布置可替换所展示的特定实施例。本公开意在涵盖本公开的各个实施例的调适或变动。应理解,以上描述是以说明性方式而非限制性方式进行。在审阅以上描述后,以上实施例的组合及本文中未具体地描述的其它实施例对于所属领域的一般技术人员来说将是显而易见的。本公开的各个实施例的范围包含其中使用以上结构及方法的其它应用。因此,本公开的各个实施例的范围应参考所附权利要求书及此权利要求书被赋予的等效物的全范围来确定。

70.在前述具体实施方式中,出于简化本公开的目的而将各种特征分组在单个实施例中。本公开方法不应被解释为反映本公开的所公开实施例必须使用比每一权利要求中明确地陈述的特征更多的特征的意图。相反,如所附权利要求书所反映,发明标的物在于少于单个所公开实施例的所有特征。因此,所附权利要求书由此并入到具体实施方式中,其中每一权利要求独立作为单独实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1