存储控制器、存储器和存储系统的制作方法

1.本发明涉及一种存储控制器(memory controller)、存储器(memory)和存储系统(memory system),尤其涉及一种可以减少存储器接收读取命令(或写入命令)以及开启对应的位开关(bit switch)之间的时间间隔的存储控制器、存储器和存储系统。

背景技术:

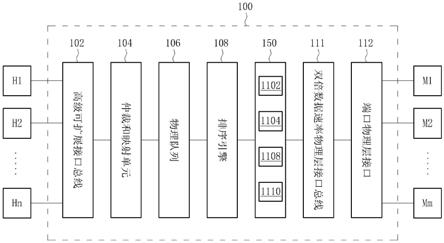

2.请参照图1,图1是现有技术所公开的一种动态随机存取存储(dynamic random access memory,dram)控制器10的示意图。如图1所示,动态随机存取存储控制器10的一边可通过动态随机存取存储控制器10的高级可扩展接口(advanced extensible interface,axi)总线102耦接多个主机h1

‑

hn,以及动态随机存取存储控制器10的另一边可通过动态随机存取存储控制器10的物理层接口(port physical layer(phy)interface)112耦接多个存储器m1

‑

mm,其中多个存储器m1

‑

mm可以是双倍数据速率(double data rate,(ddr~ddr4或更高阶)存储器,低功耗(low power)双倍数据速率(lpddr~lpddr4或更高阶)存储器等。另外,n和m为大于1的整数。

3.如图1所示,动态随机存取存储控制器10还包含仲裁和映射单元(arbitration and mapping unit)104,物理队列(physical queue)106,排序引擎(sequence engine)108,命令处理器110,和双倍数据速率物理层接口(double data rate phy interface,dfi)总线111。仲裁和映射单元104可决定产生自多个主机h1

‑

hn的多个访问命令(或命令)的优先顺序,以及将所述多个命令从高级可扩展接口(axi)地址映像至存储器地址。然后,物理队列106可根据映射的所述存储器地址的优先顺序(对应所述多个命令的优先顺序),将所述多个命令储存为一命令队列202(如图2所示)。例如,如图2所示,命令队列202具有16个对列0

‑

15(分别对应命令c0

‑

c15),其中每个队列有36位(bit),以及所述36位包括命令位、区块(bank)地址数据、行地址数据和列地址数据。另外,命令c0

‑

c15中的每个命令可对应来自动态随机存取存储器的8位(8

‑

bits)长度的读取(read)或写入(write)命令。然后物理队列106可以依序传送多个命令c0

‑

c15至排序引擎108。例如物理队列106可以依序传送命令c0

‑

c2至排序引擎108内的寄存器fifoo0

‑

fifoo2(如图3所示)。也就是说命令c0

‑

c2是依序分别储存在寄存器fifoo0

‑

fifoo2。另外,如图3所示,包含在排序引擎108中的有限状态机(finite state machine)1082可根据对应寄存器fifoo0

‑

fifoo2的顺序,执行储存在寄存器fifoo0

‑

fifoo2的命令c0

‑

c2。例如有限状态机1082首先执行储存在寄存器fifoo0的命令c0(具有顺序1),然后依序执行储存在寄存器fifoo1的命令c1(具有顺序2)以及储存在寄存器fifoo2的命令c2(具有顺序3)。之后命令处理器110也依序处理命令c0、命令c1和命令c2,其中命令处理器110处理命令c0、命令c1和命令c2的操作时序可参照图4。如图4所示,以存储器m1为例,命令c0为对应存储器m1的区块0的行11和列11地址(k0_row11/col11)的读取命令,命令c1为对应存储器m1的区块7的行22和列22地址(k7_row22/col22)的读取命令,以及命令c2为对应存储器m1的区块5的行33和列33地址(k5_row33/col33)的读取命令。当有限状态机1082执行命令c0时,有限状态机1082首先检查区块0的行11是否被激活。如果

区块0的行11没被激活以及区块0的其他行被激活,则有限状态机1082进入一预充电状态以及控制命令处理器110(在图4所示的时间t1)产生一预充电命令prech_k0。如图4所示,在命令处理器110产生预充电命令prech_k0之后的时间间隔trp(由电子设备工程联合委员会(joint electron device engineering council,jedec)的双倍数据速率存储器规范所定义)之后,命令处理器110可产生一激活命令act_k0_r11(如图4所示的时间t4)以选择区块0的行11,其中行11的地址将伴随激活命令act_k0_r11同时被存储器m1接收。在命令处理器110产生激活命令act_k0_r11之后的时间间隔trcd(由电子设备工程联合委员会的双倍数据速率存储器规范所定义)之后,命令处理器110可产生一读取命令rd_k0_c11以选择区块0的列11(如图4所示的时间t6),其中列11的地址也将伴随着读取命令rd_k0_c11同时被存储器m1接收。在存储器m1接收读取命令rd_k0_c11后,耦接存储器m1的区块0的行11和列11的存储单元所储存的数据将被读取。然而如果命令c0是要写入数据至耦接存储器m1的区块0的行11和列11的存储单元内,则此时命令处理器110将产生对应区块0的行11和列11的写入命令(未绘示于图4)给存储器m1。然后存储器m1将根据所述写入命令使所述数据写入至耦接存储器m1的区块0的行11和列11的存储单元内。

4.在时间间隔trp和时间间隔trcd期间,命令处理器110可基于一些预先规则(look ahead rules)先处理命令c1和/或命令c2的部分。例如在对应命令c0的激活命令act_k0_r11产生之前,有限状态机1082可控制命令处理器110产生对应命令c1的预充电命令prech_k7(如图4所示的时间t2)以及之后产生对应命令c2的激活命令act_k5_r33(如图4所示的时间t3)。另外,在时间间隔trcd期间,有限状态机1082可控制命令处理器110产生对应命令c1的激活命令act_k7_r22(如图4所示的时间t5)。另外,值得注意的是,在图4的操作时序中,不像命令c0和命令c1,因为根据命令c2要被读取或者写入的区块5可能已经在时间t1之前被预充电(或已被执行自动刷新命令(auto

‑

refresh command)或预充所有命令(pre

‑

charge all command)),所以命令处理器110在时间t1

‑

t3之间并没有产生对应命令c2的预充电命令。另外,当对应命令c0的读取命令rd_k0_c11被发出时,储存在寄存器fifoo1内的命令c1将会转移并储存至寄存器fifoo0,储存在寄存器fifoo2内的命令c2将会转移并储存至寄存器fifoo1,以及寄存器fifoo2将储存来自物理队列106内的命令队列202中的一个新命令(例如命令c3)。

5.另外,请参照图5,图5是说明在现有技术中命令处理器(command processor)110发出激活命令act_k0_r11、act_k5_r33、act_k7_r22和读取命令rd_k0_c11、rd_k7_c22、rd_k5_c33的操作时序的示意图。如图5所示,时间间隔trcd必须存在于激活命令act_k0_r11和读取命令rd_k0_c11之间(也就是说在激活命令act_k0_r11和读取命令rd_k0_c11之间的时间间隔不小于时间间隔trcd),以及一时间间隔tccd(由电子设备工程联合委员会的双倍数据速率存储器规范所定义)必须存在于读取命令rd_k0_c11和读取命令rd_k7_c22之间(也就是说在读取命令rd_k0_c11和读取命令rd_k7_c22之间的时间间隔不小于时间间隔tccd),其中在电子设备工程联合委员会的双倍数据速率存储器规范中,当应用于存储器m1

‑

mm的内部时钟的一个时钟周期等于1纳秒(1ns)时,时间间隔tccd不小于4纳秒(4ns)。另外,时间间隔tccd也必须存在于读取命令rd_k7_c22和读取命令rd_k5_c33之间。另外,当命令处理器110依序处理命令c3时,命令处理器110可根据命令c3发出一读取命令rd_k6_c44,其中如图5所示,在读取命令rd_k6_c44和读取命令rd_k5_c33之间的时间间隔tccd(11纳

秒)是大于4纳秒。

6.接下来请参照图6,图6是现有技术所公开的命令的数据结构以及在命令处理器110内的读取或写入命令产生电路1101的示意图。如图6(a)所示,以命令c0为例,命令c0有36位b0

‑

b35,其中位b0

‑

b10储存列地址数据cad,位b11

‑

b26储存行地址数据rad,位b27

‑

b29储存区块地址数据bad,位b32

‑

b34储存命令码cc,以及位b30、b31、b35为保留位r。例如,列地址数据cad表示列11,行地址数据rad表示行11,区块地址数据bad表示存储器m1的区块0,以及命令码cc表示对应一读取命令(也就是读取命令rd_k0_c11)的命令c0。另外,命令c1,c2中的每一命令的数据结构和命令c0的数据结构相同,所以在此不再赘述。如图6(b)所示,读取或写入命令产生电路1101可根据区块地址数据bad,列地址数据cad,及/或一读取或写入命令确认信号rwss产生读取命令rd_k0_c11,其中区块地址数据bad和列地址数据cad是由排序引擎108传送过来。另外,命令处理器110可通过双倍数据速率物理层接口总线111和物理层接口112传送读取命令rd_k0_c11至存储器m1。

7.接下来请参照图7,图7是现有技术所公开的有限状态机1082控制命令处理器110的操作时序的示意图。如图7所示,关于读取命令rd_k0_c11,rd_k7_c22,以及一写入命令wr_k5_c33,当包含在有限状态机1082内的一第一有限状态机控制器10822控制命令处理器110产生读取命令rd_k0_c11,rd_k7_c22,以及写入命令wr_k5_c33时,在命令处理器110产生激活命令act_k0_r11和读取命令rd_k0_c11之间应该满足时间间隔trcd,在命令处理器110产生读取命令rd_k0_c11和读取命令rd_k7_c22之间应该满足时间间隔tccd,以及在命令处理器110产生读取命令rd_k7_c22和写入命令wr_k5_c33之间应该满足一时间间隔trtw(由电子设备工程联合委员会的双倍数据速率存储器规范所定义)。另外,如图7所示,关于激活命令act_k5_r33,act_k0_r11,act_k7_r22和一预充电命令prech_k5,当包含在有限状态机1082内的一第二有限状态机控制器10824控制命令处理器110产生激活命令act_k5_r33,act_k0_r11,act_k7_r22和预充电命令prech_k5时,在命令处理器110产生两不同激活命令之间应该满足时间间隔trrd(由电子设备工程联合委员会的双倍数据速率存储器规范所定义),以及在命令处理器110产生预充电命令prech_k5之前应该满足一时间间隔twr(由电子设备工程联合委员会的双倍数据速率存储器规范所定义),其中如图7所示,时间间隔twr存在于预充电命令prech_k5和对应写入命令wr_k5_c33的一最后位开关的开启时间lbston之间。

8.如图8所示,以命令c0为例,在存储器m1接收读取命令rd_k0_c11后,一时间间隔t1是给存储器m1内的一解码器802接收和解码读取命令rd_k0_c11的时间,其中解码器802是根据应用于存储器m1的一时钟信号clk(rd or wr)运作。之后,一时间间隔t2(也就是一延迟链(delay chain))是给一列地址锁存器(column address latch)806锁存/输出列11的地址的时间,以及也是给一列冗余比较器(column redundancy comparison)808以及一列地址预先解码器(column address pre

‑

decoder)810根据列11的地址和产生自解码器802的一位开关启用信号bs_enable_pls准备就绪的时间。然后一时间间隔t3是给一列位开关解码器(column bit

‑

switch decoder)812根据列11的地址解码一对应的位开关的时间。另外,如图8所示,一地址xadd[0:n]包含区块0的地址、行11的地址以及列11的地址,以及一地址锁存器804是用于锁存区块0的地址、行11的地址以及列11的地址,其中地址锁存器804也是根据时钟信号clk(rd or wr)运作。

[0009]

然而,如图4所示,在命令处理器110中,命令c0已包含区块0的行11和列11的地址信息,命令c1也已包含区块7的行22和列22的地址信息,以及命令c2也已包含区块5的行33和列33的地址信息。另外,如图4所示,因为未被占用时间仍然存在于对应命令c0的读取命令rd_k0_c11和激活命令act_k0_r11之间以及储存在寄存器fifoo0内的列11的地址是已知,所以如何利用所述未被占用时间和已知的列11的地址去除时间间隔t2(也就是所述延迟链)已成为动态随机存取存储控制器10的设计者的一项重要课题。

技术实现要素:

[0010]

本发明公开一种存储控制器、存储器和存储系统。因为所述存储控制器可在产生一读取命令(或写入命令)和产生一激活命令之间产生一预先列地址命令至所述存储器,所以相较于现有技术,所述存储器可利用所述预先列地址命令快速地开启一对应的位开关。

[0011]

本发明的一实施例公开一种应用于存储器的存储控制器。所述存储控制器包含一命令处理器。当所述存储控制器执行一访问命令时,所述命令处理器在产生一读取或写入命令至所述存储器之间产生一列地址信息至所述存储器,其中所述列地址信息和所述读取或写入命令是基于所述访问命令产生。

[0012]

根据本发明的另一实施例,所述命令处理器在产生一激活命令以及产生所述读取或写入命令之间产生所述列地址信息至所述存储器,其中所述激活命令是基于所述访问命令产生。

[0013]

根据本发明的另一实施例,所述命令处理器还用于在产生所述激活命令之前基于所述访问命令产生一预充电命令。

[0014]

根据本发明的另一实施例,所述命令处理器还用于在所述存储器接收所述读取或写入命令之前产生一预先列地址命令至所述存储器,所述命令处理器基于所述访问命令产生所述预先列地址命令,以及在所述预先列地址命令和所述读取或写入命令之间存在一预定时间。

[0015]

根据本发明的另一实施例,所述列地址信息和所述预先列地址命令是在一个时钟周期内或同时产生至所述存储器。

[0016]

根据本发明的另一实施例,在对应另一访问命令的另一读取或写入命令产生后,对应所述访问命令的所述预先列地址命令和所述列地址信息产生,其中所述存储控制器在所述访问命令之前执行所述另一访问命令

[0017]

根据本发明的另一实施例,所述存储控制器还包含一排序引擎,其中所述排序引擎是耦接所述命令处理器,其中所述访问命令储存在所述排序引擎,以及所述排序引擎根据所述访问命令,控制所述命令处理器依序产生所述列地址信息和所述读取或写入命令。

[0018]

本发明的另一实施例公开一种可以从存储控制器接收访问命令的存储器。所述存储器包含一第一解码器。所述第一解码器是用于解码对应所述访问命令的一读取或写入命令;所述存储器在接收所述读取或写入命令之前,接收对应所述访问命令的一列地址信息。

[0019]

根据本发明的另一实施例,所述存储器还包含一第二解码器,其中所述第二解码器是用于解码对应所述访问命令的一激活命令,以及所述存储器在接收所述激活命令后的一时钟下降沿或一时钟上升沿接收所述列地址信息。

[0020]

根据本发明的另一实施例,所述存储器还包含一第三解码器,其中所述第三解码

器是用于解码对应所述访问命令的一预先列地址命令,以及所述预先列地址命令是在所述存储器接收所述读取或写入命令之前被所述存储器接收。

[0021]

根据本发明的另一实施例,所述存储器是在一个时钟周期内或同时接收所述列地址信息和所述预先列地址命令。

[0022]

根据本发明的另一实施例,所述存储器还包含一列地址锁存器,其中所述第三解码器解码所述预先列地址命令以及在所述存储器接收所述读取或写入命令之前产生一锁存信号至所述列地址锁存器以锁存所述列地址信息。

[0023]

根据本发明的另一实施例,所述存储器还包含一第四解码器,其中所述第四解码器是用于解码对应所述访问命令的一预充电命令,以及所述存储器在接收所述预充电命令之后以及在接收所述激活命令之前接收一行地址信息。

[0024]

根据本发明的另一实施例,所述存储器是在一个时钟周期内或同时接收所述行地址信息和一预先行地址命令。

[0025]

根据本发明的另一实施例,所述存储器还包含一第五解码器,其中所述第五解码器是用于解码对应所述访问命令的所述预先行地址命令,以及所述预先行地址命令是在所述存储器接收所述激活命令之前被所述存储器接收。

[0026]

根据本发明的另一实施例,所述存储器还包含一行地址锁存器,其中所述第五解码器解码所述预先行地址命令以及在所述存储器接收所述激活命令之前产生一锁存信号至所述行地址锁存器以锁存所述行地址信息。

[0027]

本发明的另一实施例公开一种存储系统。所述存储系统包含一存储控制器和一存储器。所述存储控制器包含一命令处理器。所述存储器是耦接于所述存储控制器。当所述存储控制器执行一访问命令时,所述命令处理器在产生一读取或写入命令至所述存储器之前,产生一列地址信息至所述存储器;其中所述命令处理器基于所述访问命令产生所述列地址信息和所述读取或写入命令。

[0028]

根据本发明的另一实施例,所述命令处理器还用于在所述存储器接收所述读取或写入命令之前产生一预先列地址命令至所述存储器以锁存所述列地址信息。

[0029]

根据本发明的另一实施例,所述列地址信息和所述预先列地址命令是在一个时钟周期内或同时产生至所述存储器。

[0030]

根据本发明的另一实施例,在对应另一访问命令的另一读取或写入命令产生后,对应所述访问命令的所述预先列地址命令和所述列地址信息产生,其中所述存储控制器在所述访问命令之前执行所述另一访问命令。

附图说明

[0031]

图1是现有技术所公开的一种动态随机存取存储控制器的示意图。

[0032]

图2是说明命令队列的示意图。

[0033]

图3是说明排序引擎的示意图。

[0034]

图4是说明动态随机存取存储控制器内的命令处理器基于现有技术的操作时序的示意图。

[0035]

图5是说明在现有技术中命令处理器发出激活命令和读取命令的操作时序的示意图。

[0036]

图6是现有技术所公开的命令的数据结构以及在命令处理器内的读取或写入命令

产生电路的示意图。

[0037]

图7是现有技术所公开的有限状态机控制命令处理器的操作时序的示意图。

[0038]

图8是说明在存储器接收读取命令后,存储器的操作的示意图。

[0039]

图9是本发明的一实施例所公开的一种存储控制器的示意图。

[0040]

图7是说明命令的数据结构的示意图。

[0041]

图8是说明命令处理器的示意图。

[0042]

图9是说明命令处理器的操作时序的示意图。

[0043]

图10a、10b是说明命令处理器的示意图。

[0044]

图11

‑

14是说明命令处理器产生激活命令和对应的读取命令的操作时序的示意图。

[0045]

图15是本发明的一实施例所公开的有限状态机控制命令处理器的操作时序的示意图。

[0046]

图16是说明在存储器接收读取命令后,存储器的操作的示意图。

[0047]

图17是说明存储器基于预先列地址命令的操作时序以及存储器基基于现有技术的操作时序的示意图。

[0048]

其中,附图标记说明如下:

[0049]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

动态随机存取存储控制器

[0050]

100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储控制器

[0051]

102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

高级可扩展接口总线

[0052]

104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

仲裁和映射单元

[0053]

106

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理队列

[0054]

108

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

排序引擎

[0055]

110、150、160

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

命令处理器

[0056]

111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

双倍数据速率物理层接口总线

[0057]

112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理层接口

[0058]

1082

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

有限状态机

[0059]

10822

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一有限状态机控制器

[0060]

10824

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二有限状态机控制器

[0061]

10826

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三有限状态机控制器

[0062]

1101、1110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读取或写入命令产生电路

[0063]

1102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

激活命令产生电路

[0064]

1104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预充电命令产生电路

[0065]

1106

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预先行地址命令产生电路

[0066]

1108

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预先列地址命令产生电路

[0067]

802、1602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

解码器

[0068]

804

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

地址锁存器

[0069]

806

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列地址锁存器

[0070]

808

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列冗余比较器

[0071]

810

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列地址预先解码器

[0072]

812

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列位开关解码器

[0073]

act_k0_r11、act_k5_r33、

ꢀꢀꢀꢀꢀꢀꢀ

激活命令

[0074]

act_k7_r22

[0075]

ass

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

激活确认信号

[0076]

a13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

引脚

[0077]

bs_enable_pls

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

位开关启用信号

[0078]

bad

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

区块地址数据

[0079]

c0

‑

c15

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

命令

[0080]

col11、col22、col33

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列地址

[0081]

clk(rd or wr)、clk(pca)

ꢀꢀꢀꢀꢀꢀꢀ

时钟信号

[0082]

cc

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

命令码

[0083]

cad

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列地址数据

[0084]

delay chain

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

延迟链

[0085]

fifoo0

‑

fifoo2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

寄存器

[0086]

h1

‑

hn

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机

[0087]

k0、k7、k5

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

区块地址

[0088]

lbston

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

开启时间

[0089]

m1

‑

mm

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器

[0090]

prech_k0、prech_k7、prech_k5

ꢀꢀꢀꢀ

预充电命令

[0091]

pcss

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预充电确认信号

[0092]

prass

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预先行地址确认信号

[0093]

pcass

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预先列地址确认信号

[0094]

pra0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预先行地址命令

[0095]

pca_k0_c11、pca_k7_c22、

ꢀꢀꢀꢀꢀꢀꢀꢀ

预先列地址命令

[0096]

pca_k5_c33、pca_k6_c44

[0097]

pre_col_add_en

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

预先列地址启用信号

[0098]

q

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据

[0099]

r

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

保留位

[0100]

rd_k0_c11、rd_k7_c22、

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读取命令

[0101]

rd_k5_c33、rd_k6_c44

[0102]

rd

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读取

[0103]

row11、row22、row33

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行地址

[0104]

rad

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行地址数据

[0105]

rwss

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读取或写入命令确认信号

[0106]

trcd、trp、t1

‑

t3、trrd、tpca2c、 时间间隔

[0107]

tccd、trtw、twr

[0108]

t1

‑

t6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

时间

[0109]

wr_k5_c33、wr_k66_c44

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

写入命令

[0110]

xadd[0:n]

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

地址

具体实施方式

[0111]

请参照图9,图9是本发明的实施例所公开的一种存储控制器100的示意图。如图9所示,存储控制器100至少包含一高级可扩展接口(advanced extensible interface,axi)总线102、一仲裁和映射单元104、一物理队列106、一排序引擎108、一命令处理器150,一双倍数据速率物理层接口总线111,以及物理层接口112,其中图9所示的高级可扩展接口总线102、仲裁和映射单元104、物理队列106、排序引擎108、双倍数据速率物理层接口总线111以及物理层接口112和图1所示的高级可扩展接口总线102、仲裁和映射单元104、物理队列106、排序引擎108、双倍数据速率物理层接口总线111以及物理层接口112相同,所以在此不再赘述。另外,存储控制器100和动态随机存取存储控制器10之间的差异在于图9中的命令处理器150不同于图1中的命令处理器110。另外,高级可扩展接口总线102、仲裁和映射单元104、物理队列106、排序引擎108、命令处理器150、双倍数据速率物理层接口总线111以及物理层接口112之间的耦接关系可参照图1,所以在此也不再赘述。另外,因为存储控制器100内除了上述组件之外的其他电路并非本发明所关注的技术特征,所以在此也不再赘述。

[0112]

另外,储存在排序引擎108内寄存器(例如寄存器fifoo0

‑

fifoo2)的命令c0

‑

c2中的每一个命令的数据结构可参照图6(a),所以在此不再赘述。因此,当命令处理器150开始执行命令c0时,所有的地址信息(包含行地址数据rad和列地址数据cad)都已经在排序引擎108中储存就绪,并且可以被传送到命令处理器150。

[0113]

另外,请参照图10a、10b,图10a是说明命令处理器150的示意图以及图10b是说明命令处理器160的示意图。如图10a所示,命令处理器150包含一激活命令产生电路(active command generating circuit)1102,一预充电命令产生电路(pre

‑

charge command generating circuit)1104,一预先列地址命令产生电路(pre

‑

column address command generating circuit)1108,以及一读取或写入命令产生电路(read or write command generating circuit)1110。现在,以命令c0为例,激活命令产生电路1102可根据存储器m1的区块0的区块地址数据bad,区块0的行地址数据rad,以及一激活确认信号ass,产生激活命令act_k0_r11,其中区块地址数据bad和行地址数据rad可由排序引擎108传送过来;预充电命令产生电路1104可根据区块地址数据bad和一预充电确认信号pcss,产生预充电命令prech_k0,其中区块地址数据bad可由排序引擎108传送过来;预先列地址命令产生电路1108可根据区块地址数据bad,列地址数据cad,以及一预先列地址确认信号pcass,产生预先列地址命令pca_k0_c11,其中区块地址数据bad和列地址数据cad可由排序引擎108传送过来;读取或写入命令产生电路1110可根据区块地址数据bad和读取或写入命令确认信号rwss,产生读取命令rd_k0_c11,其中区块地址数据bad可由排序引擎108传送过来。另外,命令处理器150可通过双倍数据速率物理层接口总线111和物理层接口112传送预充电命令prech_k0,预先列地址命令pca_k0_c11,读取命令rd_k0_c11,以及激活命令act_k0_r11至存储器m1,其中存储器m1内的一第四解码器是用于解码对应命令c0的预充电命令prech_k0。另外,在本发明的另一实施例中(如图10b所示),命令处理器160和命令处理器150之间的差异在于命令处理器160还包含一预先行地址命令产生电路1106,其中预先行地址命令产生电路1106可根据区块地址数据bad,行地址数据rad,以及一预先行地址确认信号prass,产生一预先行地址命令pra0,区块地址数据bad和行地址数据rad可由排序引擎108传送过来,以及存储器m1内的一第五解码器是用于解码对应命令c0的一预先行地址命令

pra0。另外,命令处理器160可通过双倍数据速率物理层接口总线111和物理层接口112传送预先行地址命令pra0,预充电命令prech_k0,预先列地址命令pca_k0_c11,读取命令rd_k0_c11,以及激活命令act_k0_r11至存储器m1,其中命令处理器160在产生激活命令act_k0_r11之前产生预先行地址命令pra0。

[0114]

在本发明的一实施例中,储存在寄存器fifoo0的命令c0对应顺序1,储存在寄存器fifoo1的命令c1对应顺序2,以及储存在寄存器fifoo2的命令c2对应顺序3。排序引擎108内的有限状态机1082可控制命令处理器150执行命令c0,此时有限状态机1082可预先执行命令c1和命令c2的部分以有效地将可用地址信息发送到命令处理器150使命令处理器150在适当的时间产生预先列地址命令pca_k0_c11和/或预先行地址命令pra0。

[0115]

另外,在本发明中每一命令(例如命令c0,命令c1,或命令c2)对应一个读取命令或写入命令,以及后续仅用读取命令做为说明本发明的例子。如图11所示,以命令c0对应读取耦接存储器m1的区块0的行11和列11的存储单元,命令c1对应读取耦接存储器m1的区块7的行22和列22的存储单元,以及命令c2对应读取耦接存储器m1的区块5的行33和列33的存储单元为例,图11和图5之间的差异在于因为命令c0包含列地址信息(也就是列11),所以有限状态机1082还可控制命令处理器150在产生激活命令act_k0_r11和读取命令rd_k0_c11之间产生预先列地址命令pca_k0_c11,其中命令处理器150可在应用于存储器m1

‑

mm的内部时钟的时钟下降沿或时钟上升沿产生预先列地址命令pca_k0_c11至存储器m1,且存储器m1内的一第二解码器可用于解码对应命令c0的激活命令act_k0_r11。例如,命令处理器150可在产生读取命令rd_k0_c11至存储器m1之前产生预先列地址命令pca_k0_c11至存储器m1,其中在预先列地址命令pca_k0_c11和读取命令rd_k0_c11之间存在预定时间(也就是一时间间隔tpca2c),以及在本发明的一实施例中,时间间隔tpca2c不小于应用于存储器m1

‑

mm的内部时钟的4个时钟周期(4clks)。因此,根据如图11所示的操作时序,因为命令处理器150可在产生读取命令rd_k0_c11之前产生具有列11地址信息的预先列地址命令pca_k0_c11,所以存储器m1可在接收读取命令rd_k0_c11之前,先根据预先列地址命令pca_k0_c11解码列11地址信息,导致在一读取访问时间(例如由电子设备工程联合委员会的双倍数据速率存储器规范所定义的cas latency)中或在一写入恢复时间(例如由电子设备工程联合委员会的双倍数据速率存储器规范所定义的twr)中节省约2纳秒(ns)。同样地,如图11所示,命令处理器150可在产生读取命令rd_k7_c22至存储器m1之前产生具有列22地址信息的一预先列地址命令pca_k7_c22,其中时间间隔tpca2c存在于预先列地址命令pca_k7_c22和读取命令rd_k7_c22之间;命令处理器150可在产生读取命令rd_k5_c33至存储器m1之前产生具有列33地址信息的一预先列地址命令pca_k5_c33,其中时间间隔tpca2c存在于预先列地址命令pca_k5_c33和读取命令rd_k5_c33之间;命令处理器150可在产生读取命令rd_k6_c44至存储器m1之前产生具有列44地址信息的一预先列地址命令pca_k6_c44,其中时间间隔tpca2c存在于预先列地址命令pca_k6_c44和读取命令rd_k6_c44之间。

[0116]

另外,在电子设备工程联合委员会的双倍数据速率存储器规范中,存储器m1的引脚a0

‑

a13可用来解码地址信息,但是引脚a13,a11本来就不用于解码列地址信息,所以在本发明中,存储器m1的引脚a13,a0

‑

a9(或引脚a11,a0

‑

a9,或引脚a13,a11,a0

‑

a9)可被用来解码包含在预先列地址命令pca_k0_c11,pca_k7_c22,pca_k5_c33中的列地址信息,其中在本发明的一实施例中,包含在预先列地址命令pca_k0_c11,pca_k7_c22,pca_k5_c33中的列地

址信息对应存储器m1的引脚a0

‑

a9。但本发明并不受限于存储器m1利用上述引脚的配置解码包含在预先列地址命令pca_k0_c11,pca_k7_c22,pca_k5_c33中的列地址信息。

[0117]

接下来以引脚a13,a0

‑

a9为例,如图12所示,当所述列地址信息中的引脚a13具有高电平时,命令处理器150可产生预先列地址命令pca_k0_c11,pca_k7_c22,pca_k5_c33,或pca_k6_c44时,其中如图12所示,已产生的预先列地址命令pca_k0_c11,pca_k7_c22,及/或pca_k5_c33分别对应读取命令rd_k0_c11,rd_k7_c22,rd_k5_c33,以及预先列地址命令pca_k6_c44对应读取命令rd_k6_c44(或写入命令wr_k6_c44)。另外,存在于一个预先列地址命令和一个对应的读取命令(或一个对应的写入命令)之间的时间间隔不小于时间间隔tpca2c,以及存在于两个相邻的读取命令之间的时间间隔不小于时间间隔tccd。

[0118]

另外,本发明并不受限于命令处理器150的预先列地址命令产生电路1108在激活命令act_k0_r11和读取命令rd_k0_c11之间的时钟下降沿或时钟上升沿产生预先列地址命令pca_k0_c11。也就是说只要预先列地址命令产生电路1108可在读取命令rd_k0_c11之前产生预先列地址命令pca_k0_c11就落入本发明的范围。

[0119]

另外,以命令处理器150产生预先列地址命令pca_k6_c44为例,如图13所示,在本发明的一实施例中,命令处理器150产生预先列地址命令pca_k6_c44的时间不会超过如图13所示的操作时序中的前一个读取命令(也就是读取命令rd_k5_c33),所以在预先列地址命令pca_k6_c44和读取命令rd_k6_c44之间的时间间隔tpca2c的最大值tpca2cmax等于时间间隔tccd(例如如图13所示,在预先列地址命令pca_k6_c44和读取命令rd_k6_c44之间的时间间隔tccd等于11个时钟周期(11clks)或11纳秒(ns)),以及在预先列地址命令pca_k6_c44和读取命令rd_k6_c44之间的时间间隔tpca2c的最小值tpca2cmin等于所述内部时钟的4个时钟周期(4clks)。另外,如图13所示,以预先列地址命令pca_k0_c11为例,具有预先列地址命令pca_k0_c11时,存储器m1可将所述读取访问时间改善约2纳秒(ns)(例如,由模式寄存器设定的cas latency“cl”可从12改变至10)。当然,当预先列地址命令pca_k0_c11对应一写入命令时,存储器m1也可将所述写入恢复时间改善约2纳秒(ns)(例如,由所述模式寄存器设定的“wr”也可从12改变至10)。另外,图13所示的符号q表示数据。

[0120]

另外,在本发明的另一实施例中,以命令处理器150产生预先列地址命令pca_k6_c44为例,如图14所示,命令处理器150产生预先列地址命令pca_k6_c44的时间可超过如图14所示的操作时序中的前一个读取命令(也就是读取命令rd_k5_c33),但是不能超过对应预先列地址命令pca_k6_c44的激活命令(未绘示于图14),或如果可能的话也不能超过对应预先列地址命令pca_k6_c44的预充电命令。另外,预先列地址命令pca_k5_c33可超过如图14所示的操作时序中的前一个读取命令(也就是读取命令rd_k7_c22),但是不能超过对应预先列地址命令pca_k5_c33的激活命令,或如果可能的话也不能超过对应预先列地址命令pca_k5_c33的预充电命令。

[0121]

接下来请参照图15,图15是本发明的一实施例所公开的有限状态机1082控制命令处理器150的操作时序的示意图,其中将产生两个读取命令和一个随后的写入命令。如图15所示,以在产生对应的激活命令和对应的读取命令(或对应的写入命令)之间产生预先列地址命令,以及所述预先列地址命令不能超过前一个读取命令(或前一个写入命令)为例,因为命令处理器150可产生预先列地址命令pca_k0_c11,pca_k7_c22,pca_k5_c33,所以当包含在有限状态机1082内的第二有限状态机控制器10824控制命令处理器150产生预充电命

令prech_k5时,在命令处理器150发出预充电命令prech_k5之前,时间间隔twr将被减少至一时间间隔twr

‑

2clks,其中如图15所示,时间间隔twr

‑

2clks存在于预充电命令prech_k5和对应写入命令wr_k5_c33的最后位开关的开启时间lbston。另外,如图15所示,在图15的实施例中,时间间隔tpca2c的最大值tpca2cmax等于时间间隔tccd(在两个读取命令之间)或时间间隔trtw(在前一个读取命令和下一个写入命令之间)。当包含在有限状态机1082内的一第三有限状态机控制器10826控制命令处理器150产生预先列地址命令pca_k0_c11时,在预先列地址命令pca_k0_c11和激活命令act_k0_r11之间存在一时间间隔trcd

‑

4clks,其中时间间隔tpca2c等于最小值tpca2cmin(也就是4clks);当第三有限状态机控制器10826控制命令处理器150产生预先列地址命令pca_k7_c22时,在预先列地址命令pca_k7_c22和读取命令rd_k7_c22之间存在时间间隔tccd;当第三有限状态机控制器10826控制命令处理器150产生预先列地址命令pca_k5_c33时,在预先列地址命令pca_k5_c33和写入命令wr_k5_c33之间存在时间间隔trtw。另外,第一有限状态机控制器10822的操作原理可参照图7,所以在此不再赘述。另外,图15所示的操作时序仅是用以说明(非限制)本发明的一个实施例。

[0122]

接下来如图16所示,以命令c0为例,当命令处理器150产生预先列地址命令pca_k0_c11后,基于引脚a13(或其他没有在传统列地址使用的引脚)及/或预先列地址命令pca_k0_c11,存储器m1内的一解码器1602(也就是一第三解码器且根据一时钟信号clk(pca)运作)可产生一预先列地址启用信号pre_col_add_en至存储器m1内的列地址锁存器806,以及存储器m1内的地址锁存器804锁存地址xadd[0:n](例如区块0的地址、行11的地址以及列11的地址,其中地址锁存器804也是根据时钟信号clk(pca)运作),所以列地址锁存器806可锁存列11的地址以及提早输出列11的地址至列冗余比较器808和列地址预先解码器810,导致列冗余比较器808和列地址预先解码器810在存储器m1接收读取命令rd_k0_c11之前(或在存储器m1接收读取命令rd_k0_c11期间)先行准备就绪,或在存储器m1的解码器802(也就是一第一解码器)解码读取命令rd_k0_c11之前(或在存储器m1的解码器802解码读取命令rd_k0_c11期间)先行准备就绪。

[0123]

如图16所示,因为列冗余比较器808和列地址预先解码器810可在存储器m1接收读取命令rd_k0_c11之前(或在存储器m1的解码器802解码读取命令rd_k0_c11之前)先行准备就绪,所以图8所示的延迟链可以在图16中被移除,其中所述延迟链是给列地址锁存器806锁存列11的地址的时间,以及给列冗余比较器808和列地址预先解码器810准备就绪的时间。也就是说图16并不存在如图8所示的时间间隔t2。

[0124]

请参照图17,图17是说明存储器m1基于预先列地址命令pca_k0_c11的操作时序以及存储器基m1基于现有技术的操作时序的示意图。如图17(a)所示,在现有技术中,在存储器m1接收读取命令rd_k0_c11后,如果预先列地址命令pca_k0_c11没有应用至存储器m1,则在存储器m1接收读取命令rd_k0_c11后,在存储器m1根据列地址数据cad开启所述对应的位开关之前必须存在时间间隔t1

‑

t3,其中时间间隔t1是给存储器m1接收读取命令rd_k0_c11和解码读取命令rd_k0_c11的时间,时间间隔t2是给存储器m1锁存列地址数据cad,预先解码列地址数据cad,以及执行列冗余比较器808的时间,以及时间间隔t3是给存储器m1根据列地址数据cad解码所述对应的位开关以开启所述对应的位开关的时间。

[0125]

然而,如图17(b)所示,在存储器m1接收读取命令rd_k0_c11后,如果预先列地址命

令pca_k0_c11应用至存储器m1,则因为存储器m1已解码预先列地址命令pca_k0_c11以得到列地址数据cad,已锁存列地址数据cad,已预先解码列地址数据cad,以及在存储器m1接收读取命令rd_k0_c11之前已执行列冗余比较器808,所以在存储器m1接收读取命令rd_k0_c11以及在存储器m1开启所述对应的位开关之间仅会有时间间隔t1、t3存在。也就是说当存储器m1接收读取命令rd_k0_c11时,存储器m1可以根据列11快速地开启所述对应的位开关。

[0126]

另外,仲裁和映像单元104,排序引擎108,以及命令处理器150可以是具有上述仲裁和映像单元104,排序引擎108,以及命令处理器150的功能的现场可编程序逻辑门阵列(field programmable gate array,fpga),或是具有上述仲裁和映像单元104,排序引擎108,以及命令处理器150的功能的特殊应用集成电路(application

‑

specific integrated circuit,asic),或是具有上述仲裁和映像单元104,排序引擎108,以及命令处理器150的功能的软件模块,或是具有上述仲裁和映像单元104,排序引擎108,以及命令处理器150的模拟集成电路。

[0127]

另外,因为本发明领域的技术人员可以将具有仲裁和映像单元104,排序引擎108和命令处理器150的上述功能的代码输入到现场可编程序逻辑门阵列(fpga),或利用具有仲裁和映像单元104,排序引擎108和命令处理器150的上述功能的知识产权核心(ip)实现具有仲裁电路104,排序引擎108和命令处理器110的上述功能的专用集成电路(asic),以及现场可编程序逻辑门阵列(fpga)和专用集成电路(asic)对于本发明领域的技术人员而言是现成的,所以仲裁和映像单元104,排序引擎108和命令处理器150的电路架构不须要被公开。

[0128]

综上所述,因为所述未被占用时间存在于所述读取命令(或所述写入命令)和所述激活命令之间,所以本发明可利用所述命令处理器中的预先列地址命令产生电路在所述读取命令(或所述写入命令)和所述激活命令之间产生所述预先列地址命令至所述存储器。因此,相较于现有技术,所述存储器可利用所述预先列地址命令减少所述存储器接收所述读取命令(或所述写入命令)和开启所述对应的位开关之间的时间间隔。

[0129]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1