存储装置、存储器件及其操作方法与流程

1.本发明的实施例涉及存储装置、存储器件及其操作方法。

背景技术:

2.诸如随机存取存储器(ram)之类的存储器件通常用于临时存储数据。 ram有几种类型,包括动态随机存取存储器(dram)和静态随机存取存 储器(sram)。ic技术向纳米区域的发展增加了这些存储器件的功耗。 功耗增加会导致几个问题,包括电池寿命缩短、昂贵的封装和冷却解决方 案,还会导致芯片故障。

技术实现要素:

3.根据本发明实施例的一个方面,提供了一种操作存储器件的方法,包 括:接收时钟信号,其中,时钟信号的每个时钟循环启动存储器件中的写 入操作或读取操作;确定功率小憩周期;确定功率小憩周期小于时钟信号 的时钟循环周期;以及响应于确定功率小憩周期小于时钟循环周期而产生 标头控制信号,其中,标头控制信号关闭存储器件的组件的标头。

4.根据本发明实施例的另一个方面,提供了一种存储装置,包括:存储 器件;以及处理单元,连接到存储器件。其中,处理单元可操作来:确定 复制位线的预充电和复制位线上的剩余电荷下降到预定电平以下之间的时 间周期,其中时钟信号的每个时钟循环启动存储器件的单元阵列中的写入 操作或读取操作;确定复制位线的预充电和复制位线上的剩余电荷下降到 预定电平以下之间的时间周期小于时钟信号的时钟循环周期,其中,时钟 信号的每个时钟循环启动存储器件的单元阵列中的写入操作或读取操作; 以及响应于确定复制位线的预充电和复制位线上的剩余电荷下降到低于预 定电平之间的时间周期小于时钟循环周期,关闭存储器件的组件的标头。

5.根据本发明实施例的又一个方面,提供了一种存储器件,包括:单元 阵列,包括多个位单元;字线驱动器,连接到单元阵列,其中,字线驱动 器可操作来响应于用于读取操作或写入操作的时钟信号来选择单元阵列的 字线,并将所选择的字线充电到预定电压;输入/输出电路,连接到单元阵 列,输入/输出电路可操作来从单元阵列读取数据和向单元阵列写入数据; 以及功率控制电路,连接到单元阵列、字线驱动器和输入/输出电路中的每 一个,其中,功率控制电路可操作来选择性地关闭以下至少一个的标头: 单元阵列、字线驱动器和输入/输出电路。

附图说明

6.当与附图一起阅读时,根据以下详细描述可以最好地理解本发明的各 个实施例。应注意,根据行业中的标准做法,各种部件未按比例绘制。实 际上,为了论述清楚,各种部件的尺寸可以任意增加或减小。

7.图1是示出根据一些实施例的示例存储器件的框图。

8.图2a是示出根据一些实施例的第一频率的时钟信号和相应的标头控 制信号的曲线图。

9.图2b是示出根据一些实施例的第二频率的时钟信号和相应的标头控 制信号的曲线图。

10.图3示出了根据一些实施例的具有处于“小憩(nap)”模式的示例标头 功率控制机制的存储器件。

11.图4a是示出根据一些实施例的第一频率的时钟信号和对应于第一频 率的时钟信号的图3的存储器件的其他信号的曲线图。

12.图4b是示出根据一些实施例的第二频率的时钟信号和对应于第二频 率的时钟信号的图3的存储器件的其他信号的曲线图。

13.图5示出了根据一些实施例的具有处于小憩模式的另一示例标头功率 控制机制的存储器件。

14.图6示出了根据一些实施例的具有处于小憩模式的又一示例标头功率 控制机制的存储器件。

15.图7a示出了根据本发明的一些实施例的第一类型0

‑

单元。

16.图7b示出了根据本发明的一些实施例的第二类型0

‑

单元。

17.图7c示出了根据本发明的一些实施例的第一类型1

‑

单元。

18.图7d示出了根据本发明的一些实施例的第二种类型的1

‑

单元。

19.图8a是示出根据一些实施例的第一频率的时钟信号和对应于第一频 率的时钟信号的图5和图6的存储器件的其他信号的曲线图。

20.图8b是示出根据一些实施例的第二频率的时钟信号和对应于第二频 率的时钟信号的图5和图6的存储器件的其他信号的曲线图。

21.图9是示出根据一些实施例的对应于不同数量的0

‑

单元的图5和图6 的存储器件的时钟信号和其他信号的曲线图。

22.图10示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件。

23.图11是示出根据一些实施例的图10的存储器件的时钟信号和对应于 时钟信号的其他信号的曲线图。

24.图12示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件。

25.图13示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件。

26.图14a是示出根据一些实施例的第一频率的时钟信号和对应于第一频 率的时钟信号的图12和图13的存储器件的其他信号的曲线图。

27.图14b是示出根据一些实施例的第二频率的时钟信号和对应于第二频 率的时钟信号的图12和图13的存储器件的其他信号的曲线图。

28.图15是示出根据一些实施例的对应于不同数量的复制vdd晶体管的 图12和图13的存储器件的时钟信号和其他信号的曲线图。

29.图16示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制

也在本发明的范围内。如图1所示,存储器件100包括字线驱动器电路102、 单元阵列104、输入/输出(i/o)电路106、时序控制单元108和功率控制 电路110。然而,对于本领域普通技术人员来说,在阅读了本发明之后将 显而易见的是,存储器件100可以包括比图1所示更多的组件。

40.单元阵列104包括多个单元(也称为位单元或存储器单元)。单元阵 列104的每个单元可以存储一位信息(即,位值为0或位值为1)。在一 些示例中,单元阵列104的多个单元布置成多个行和多个列的矩阵。多个 行中的每一行包括多个单元中的第一多个单元。多个列中的每一列包括多 个单元中的第二多个单元。单元阵列104包括标头104a(也称为单元阵列 标头104a)。单元阵列标头104a提供虚拟电源来给单元阵列104的组件加 电。

41.多个单元中的一个示例单元包括一对交叉耦合的反相器(也称为q和 q

‑

bar,其中q

‑

bar与q互补),用于存储一位信息。交叉耦合反相器连接 到一对存取晶体管,该对存取晶体管允许存取存储在交叉耦合反相器中的 信息。单元阵列104的多个单元可以使用四个晶体管、六个晶体管、八个 晶体管、十个晶体管等来形成。此外,单元阵列104的多个单元是单端口 单元或多端口(例如,双端口和三端口)单元。

42.字线驱动器电路102连接到单元阵列104,并且可操作来选择单元阵 列104的字线,并且将所选择的字线充电到用于读取操作或写入操作的逻 辑高电平。在一些示例中,字线驱动器电路102是解码器电路,其包括多 个逻辑运算器来解码地址线上的电位以识别要激活的字线。地址线被充电 到逻辑高电平(即,近似等于第一预定电位)或逻辑低电平(即,近似等 于第二预定电位)。第一预定电位近似等于电源电压(即,vdd)。第二 预定电位近似等于地电位或零伏。然而,可以采用其他合适的逻辑低电平 电压。逻辑高电平由位1表示,逻辑低电平由位0表示。字线驱动器电路 102还包括字线驱动器标头102a(也称为字线驱动器102的标头102a)。 字线驱动器标头102a为字线驱动器电路102的组件提供虚拟电源,用于读 取操作和写入操作。

43.i/o电路106连接到单元阵列104,并可操作来从单元阵列104读取数 据和向单元阵列104写入数据。例如,i/o电路106可以包括:多路复用器 电路,用于选择单元阵列104的列;预充电电路,用于对与所选择的列相 关联的位线对进行预充电;读取电路,可操作来从位于所选列中的一个或 多个单元读取数据;写入电路,用于将数据写入位于所选列中的一个或多 个单元等。i/o电路106包括i/o标头106a(也称为i/o电路106的标头106a), 其可操作来为i/o电路106的组件加电以进行读取操作和写入操作。

44.时序控制单元108可操作来为存储器件100的组件产生时钟信号。例 如,时序控制单元108可操作来为字线驱动器102和i/o电路106产生信 号。该信号基于来自时钟信号(标记为clk)的输入而产生。时钟信号的 每个周期可以指示读取操作或写入操作的开始。

45.功率控制电路110可操作来选择性地关闭字线驱动器102、单元阵列 104和i/o电路106中至少一个的标头或部分标头。例如,并且如在本发明 的以下部分中更详细地讨论的,功率控制电路110可操作来确定功率小憩 周期,确定功率小憩周期比时钟信号的时钟循环周期更短或更少,并且响 应于确定功率小憩周期比时钟循环周期更短而产生标头控制信号。标头控 制信号关闭单元阵列104、字线驱动器102和i/o电路106中的一个或多个 的标头或部分标头。

46.图2a是示出根据一些实施例的第一频率的示例时钟信号202和对应的 标头控制

的预定电压。

51.如图3所示,预充电电路304包括预充电第一晶体管322和预充电第 二晶体管324。预充电第一晶体管322和预充电第二晶体管324中的每一 个的源极连接到电源电压(即,vdd)。预充电第一晶体管322的漏极连 接到位线bl,预充电第二晶体管324的漏极连接到互补位线blb。预充电 第一晶体管322的栅极连接到预充电第二晶体管324的栅极,第二晶体管 324又连接到not逻辑电路312的输出端。

52.预充电第一晶体管322和预充电第二晶体管324的每一个都是p型沟 道金属氧化物半导体(pmos)晶体管。然而,其他类型的晶体管也在本发 明的范围内。例如,预充电第一晶体管322和预充电第二晶体管324中的 每一个可以是金属氧化物半导体场效应晶体管、n型沟道金属氧化物半导 体晶体管和互补金属氧化物半导体晶体管。此外,每个预充电第一晶体管 322和预充电第二晶体管324是对称的。也就是说,预充电第一晶体管322 和预充电第二晶体管324中的每一个的源极可以是漏极,预充电第一晶体 管322和预充电第二晶体管324中的每一个的漏极可以是源极。

53.继续参考图3,位线bl和互补位线blb连接到电压检测器306。电压 检测器306可操作来连续地将位线bl和互补位线blb的每一个上的剩余 电位或剩余电压与预定电压电平进行比较。基于该比较,当位线bl和互 补位线blb上的剩余电压都小于预定电压电平时,电压检测器306输出第 一逻辑值(例如,逻辑值高)。此外,基于该比较,当位线bl或互补位 线blb上的剩余电压大于预定电压电平时,电压检测器306输出第二逻辑 值(例如,逻辑值低)。电压检测器电路306的输出也被称为io_标头信 号316(也被称为标头控制信号204)。在示例性实施例中,电压检测器 306可以包括or逻辑电路320。在一些例子中,or逻辑电路329是or 逻辑门。然而,其他类型的逻辑门也在本发明的范围内。

54.电压检测器306的输出端连接到nor逻辑电路308的第一输入端。 nor逻辑电路308的第二输入端连接到定时控制单元108的第一输出端。 定时控制单元108的第一输出端也连接到not逻辑电路312的输入端。时 序控制单元的第二输出端连接到字线驱动器电路102。

55.nor逻辑电路308的输出端连接到功率控制晶体管310的栅极(即, i/o标头106a或i/o标头106a的一部分)。功率控制晶体管310的源极连 接到电源电压(即vdd),功率控制晶体管310的漏极连接到i/o电路106。 功率控制晶体管310是pmos晶体管。然而,对于本领域普通技术人员来 说,在阅读本发明之后将显而易见的是,功率控制晶体管310可以是 mosfet、nmos晶体管或cmos晶体管。另外,功率控制晶体管310是 对称的。也就是说,功率控制晶体管310的源极可以是漏极,漏极可以是 源极。

56.在读取或写入操作期间,定时控制单元108可操作来基于时钟信号202 产生pre信号314。例如,当时钟信号202上升到逻辑高电平时,pre信 号314上升到逻辑高电平。当pre信号314上升到逻辑高电平时,not逻 辑电路312的输出端变为逻辑低电平,因此blpreb信号变为逻辑低电平。 当not逻辑电路312的输出端处于逻辑低电平时,预充电第一晶体管322 和预充电第二晶体管324的栅极都处于逻辑低电平,这开启预充电第一晶 体管322和预充电第二晶体管324。这又将位线bl和互补位线blb连接 到电源电压(即vdd),从而将位线bl和互补位线blb预充电到预定电 压电平(或vdd)。

57.当预充电时,位线bl和互补位线blb都高于预定电压电平,因此, 电压检测器306

的输出端(即,io_标头信号316或标头控制信号204)处 于逻辑高电平。通过扩展,nor逻辑电路308的第一输入端处于逻辑高电 平,因此,nor逻辑电路308的输出端(即,nor逻辑电路308的输出端) 处于逻辑低电平。此外,当nor逻辑电路308的输出端处于逻辑低电平时, 功率控制晶体管310的栅极处于逻辑低电平,这开启功率控制晶体管310 (即,i/o标头106a或i/o标头106a的一部分)。功率控制晶体管310的 开启导致功率控制晶体管310的漏极连接到电源电压(即,vdd),并且 处于逻辑高电平。这使得vdd_io信号318(即虚拟电源信号)处于逻辑 高电平。因此,当位线bl或互补位线blb上的剩余电压高于预定电压电 平时,io_标头信号316(即标头控制信号204)和vdd_io信号318(即 i/o电路106的虚拟电源信号)处于逻辑高电平。

58.在从pre信号314上升到逻辑高电平的预定时间之后,pre信号314 下降到逻辑低电平(指示时钟循环或写周期的结束)。当pre信号314下 降到逻辑低电平时,not逻辑电路312的输出端(和blpreb信号)上升 到逻辑高电平。当not逻辑电路312的输出端处于逻辑高电平时,预充电 第一晶体管322和预充电第二晶体管324的栅极都处于逻辑高电平,这关 闭了预充电第一晶体管322和预充电第二晶体管324。这又将位线bl和互 补位线blb中的每一个从电源电压(即vdd)关闭。与电源电压的关闭 通过第一多个单元302a1、302a2、

…

、302an启动位线bl和互补位线blb 中的每一个的放电。

59.当位线bl和互补位线blb上的剩余电压下降到低于预定电压电平时, 电压检测器306的输出端(即,io_标头信号316或标头控制信号204)下 降到逻辑低电平。通过扩展,nor逻辑电路308的第一输入端下降到逻辑 低电平,这驱动nor逻辑电路308的输出端到逻辑高电平。此外,当nor 逻辑电路308的输出端处于逻辑高电平时,功率控制晶体管310的栅极也 处于逻辑高电平,这关闭了功率控制晶体管310(即,i/o标头106a或i/o 标头106a的一部分)。这导致功率控制晶体管310的漏极(即,vdd_io 信号318)下降到逻辑低电平。因此,当位线bl和互补位线blb上的剩 余电压低于预定电压电平时,io_标头信号316(即标头控制信号204)和 vdd_io信号318(即虚拟电源信号)处于逻辑低电平。在位线bl和互补 位线blb的预充电时间和位线bl和互补位线blb上的剩余电压都下降到 预定电压电平以下的时间之间的时间周期被称为功率小憩周期t_nap。

60.图4a是示出根据一些实施例的第一频率的时钟信号202和对应于第一 频率的时钟信号202的图3的存储器件100的其他信号的曲线图400。例 如,曲线图400的第一曲线402表示时钟信号202,曲线图400的第二曲 线404表示pre信号314,曲线图400的第三曲线406表示字线wl上的 剩余电压,曲线图400的第四曲线408表示位线bl上的剩余电压,曲线 图400的第五曲线410表示互补位线blb上的剩余电压,曲线图400的第 六曲线412表示vdd_io信号318(即,虚拟电源信号)。

61.如曲线图400的第一曲线402和第二曲线404所示,当时钟信号202 上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外,如第三曲 线406所示,在从时钟信号202上升到逻辑高电平的预定时间之后,字线 wl上的电压上升到逻辑高电平。此外,如第四曲线408和第五曲线410 所示,当pre信号314从逻辑高电平下降到逻辑低电平时,位线bl和互 补位线blb中的每一个上的剩余电压开始下降。在对位线bl和互补位线 blb预充电之后,pre信号314从逻辑高电平变为逻辑低电平。

62.然而,如第四曲线408所示,在下一个时钟循环开始之前,位线bl 上的剩余电压不

会下降到预定电压电平420以下。并且当时钟信号202在 下一个时钟循环上升到逻辑高电平时,位线bl和互补位线blb上的剩余 电压开始上升。因此,如第六曲线412所示,作为位线bl和互补位线blb 上的剩余电压的逻辑或的vdd_io信号318保持在逻辑高电平。因而,根 据示例性实施例,当时钟信号202的周期小于功率小憩周期t_nap时,i/o 电路标头106a保持开启。通过扩展,当时钟信号202的循环周期小于功率 小憩周期t_nap时,虚拟电源信号(即,vdd_io信号318)保持在逻辑 高电平。

63.图4b是示出根据一些实施例的第二频率的时钟信号202和对应于第二 频率的时钟信号202的存储器件100的其他信号的曲线图450。例如,曲 线图450的第一曲线452表示第二频率的时钟信号202,曲线图450的第 二曲线454表示pre信号314,曲线图450的第三曲线456表示字线wl 上的电压,曲线图450的第四曲线458表示位线bl上的电压,曲线图450 的第五曲线460表示互补位线blb上的电压,曲线图450的第六曲线462 表示io_标头信号316,曲线图450的第七曲线464表示vdd_io信号318。

64.如图4b的第一曲线452所示,时钟信号202的第二频率低于图4a的 第一曲线408中描绘的第一频率。因此,对应于第二频率的时钟信号202 的时钟循环周期t2大于第一频率的时钟循环202的时钟循环周期t1。如 曲线图450的第三曲线456和第四曲线458所示,较长的时钟循环周期为 位线bl和互补位线blb上的剩余电压提供了足够的时间(即,功率小憩 周期t_nap),以降低到预定电压电平420以下。如曲线图450的第六曲 线462所示,这导致io_标头信号316(即标头控制信号204)在功率小憩 周期t_nap结束时从逻辑高电平变为逻辑低电平。io_标头信号316变为逻 辑低电平导致功率控制晶体管310关闭。因此,根据示例性实施例,当时 钟信号202的周期大于功率小憩周期t_nap时,i/o标头106a或i/o标头 106a的一部分被关闭。

65.此外,如曲线图450的第七曲线464所示,功率控制晶体管310的关 闭导致vdd_io信号318在功率小憩周期t_nap结束时从逻辑高电平变为 逻辑低电平。因此,当时钟信号202的循环周期大于功率小憩周期t_nap 时,i/o电路106的虚拟电源信号(即,vdd_io信号318)下降至逻辑低 电平。

66.继续参考图4b,如曲线图450的第二曲线454所示,在第一时钟循环 周期结束时,pre信号314响应于下一时钟循环周期的开始而从逻辑低电 平上升到逻辑高电平。如图450的第三曲线456和第四曲线458所示,这 导致位线bl和互补位线blb的预充电。随着位线bl和互补位线blb的 预充电,位线bl和互补位线blb上的剩余电压上升到预定电压电平420 以上。因此,如第六曲线462所示,io_标头信号316(即标头控制信号204) 在下一个时钟循环开始时从逻辑低电平变为逻辑高电平,这导致功率控制 晶体管310(即输入输出标头106a)开启。

67.类似地,如曲线图450的第七曲线464所示,功率控制晶体管310的 开启导致vdd_io信号318在下一个时钟循环开始时从逻辑低电平变为逻 辑高电平。也就是说,i/o电路106的虚拟电源信号在功率小憩周期t_nap 结束时上升到逻辑高电平。因此,对于时钟信号202,i/o电路标头106a 从功率控制周期t_nap的结束到当前时钟循环的结束或下一个时钟循环的 开始被关闭。通过扩展,i/o电路106的虚拟电源从功率控制周期t_nap 的结束到当前时钟循环的结束或时钟信号202的下一个时钟循环的开始关 闭。

68.图5示出了根据一些实施例的具有处于小憩模式的另一示例标头功率 控制机制

的存储器件100。如图5所示,存储器件100包括字线驱动器电 路102、单元阵列104、i/o电路106和时序控制单元108。此外,如图5 所示,存储器件100包括复制列502、预充电电路304和电压检测器306。 此外,对于本领域普通技术人员来说,在阅读本发明之后将显而易见的是, 存储器件100可以包括比图5中所示的更多或更少的组件。

69.i/o电路106被示为包括一组组件506。组件组506还被示为包括组件 506a的第一子组(也标记为i/o<1>)和组件506b的第二子组(也标记为 i/o<2>)。尽管图5的i/o电路106仅示出了一组组件和两个子组组件, 但是对于本领域普通技术人员来说,在阅读本发明之后,显而易见的是, i/o电路106可以包括多于一组的组件和多于两个子组的组件。

70.组件506a的第一子组的虚拟电源(即,第一vdd_io信号318a)由 第一功率控制晶体管308a(也称为第一标头)控制。组件506b的第二子组 的虚拟电源(即,第二vdd_io信号318b)由第二功率控制晶体管308b (也称为第二标头)控制。第一标头和第二标头都由io_标头信号316控 制。然而,对于本领域技术人员来说,在阅读本发明之后,显而易见的是, 可以分别通过第一io_标头信号和第二io_标头信号来彼此独立地控制第 一标头和第二标头。

71.复制列502包括标记为504a1、504a2、

…

、504an的多个单元。在示 例性实施例中,如参考图7a、图7b、图7c和图7d更详细解释的,复制 列502的多个单元中的每一个被强制存储位值0(称为0

‑

单元)或位值1 (称为1

‑

单元)。多个单元中的每一个连接到复制位线bl和复制互补位 线blb。复制位线bl和复制互补位线blb都连接到预充电电路304。预 充电电路304通过not逻辑电路312连接到定时控制单元108的第一输出 端。电压检测器306连接到复制位线bl。然而,对于本领域普通技术人员 来说,在阅读本发明之后显而易见的是,电压检测器306可以连接到复制 互补位线blb。

72.对于读取或写入操作,定时控制单元108在第一输出端产生pre信号 314。在示例中,当时钟信号202上升到逻辑高电平时,pre信号314上升 到逻辑高电平。这使得预充电电路304通过将复制位线bl和复制互补位 线blb中的每一个连接到电源电压(即vdd),将复制位线bl和复制互 补位线blb中的每一个预充电到预定电压。在预定时间之后,pre信号 314下降到逻辑低电平,这使得复制位线bl和复制互补位线blb中的每 一个与电源电压关闭(即,vdd)。在从电源电压(即vdd)关闭之后, 复制位线bl和复制互补位线blb中的每一个开始通过标记为504a1、 504a2、

…

、504an的多个单元放电。在示例性实施例中,复制位线bl和 复制互补位线blb的放电速率取决于复制列502中连接的多个单元的总数。 此外,放电速率还取决于连接在复制列502中的0

‑

单元的数量和1

‑

单元的 数量的比值。

73.电压检测器306连接到复制位线bl,并连续比较复制位线bl上的剩 余电压和预定电压电平420。然而,对于本领域普通技术人员来说,在阅 读本发明之后将显而易见的是,电压检测器306可以连接到复制互补位线 bl,并且连续地将复制位线bl上的剩余电压与预定电压电平420进行比 较。

74.当复制位线bl上的剩余电压高于预定电压电平420时,电压检测器 306的输出端(即,io_标头信号316或标头控制信号204)处于逻辑高电 平。通过扩展,第一nor逻辑电路308a和第二nor逻辑电路308b中的 每一个的第一输入端处于逻辑高电平。因此,第一nor逻辑电路308a和 第二nor逻辑电路308b中的每一个的输出端(即,第一nor逻辑电路 308a和第二nor逻辑电路308b中的每一个的输出端)处于逻辑低电平。 当第一nor逻辑电路308a和

第二nor逻辑电路308b中的每一个的输出 端处于逻辑低电平时,第一功率控制晶体管310a和第二功率控制晶体管 310b中的每一个的栅极处于逻辑低电平,这开启了第一功率控制晶体管 310a和第二功率控制晶体管310b。因此,当复制位线bl上的剩余电压保 持在预定电压电平420之上时,第一标头(即,第一功率控制晶体管310a) 和第二标头(即,第二功率控制晶体管310b)都保持开启。

75.通过扩展,第一功率控制晶体管310a和第二功率控制晶体管310b中 的每一个的漏极连接到电源电压(即,vdd),并保持在逻辑高电平。这 使得第一子组组件506a(即,io<1>)和第二子组组件506b(即,io<2>) 的vdd_io信号318(即,虚拟电源信号)保持在逻辑高电平。因此,当 复制位线bl上的剩余电压保持高于预定电压电平420时,第一子组组件 506a和第二子组组件506b中的每一个的虚拟电源保持在逻辑高电平。

76.然而,当复制位线bl上的剩余电压下降到低于预定电压电平420时, 电压检测器306的输出端(即,io_标头信号316或标头控制信号204)下 降到逻辑低电平。通过扩展,第一nor逻辑电路308a和第二nor逻辑电 路308b中的每一个的第一输入端也处于逻辑低电平,这将第一nor逻辑 电路308a和第二nor逻辑电路308b中的每一个的输出驱动到逻辑高电平。 也就是说,第一nor逻辑电路308a和第二nor逻辑电路308b中的每一 个的输出端上升到逻辑高电平。当第一nor逻辑电路308a和第二nor逻 辑电路308b的输出端处于逻辑高电平时,第一功率控制晶体管310a和第 二功率控制晶体管310b中的每一个的栅极都处于逻辑高电平,这使得第一 功率控制晶体管310a(即第一标头)和第二功率控制晶体管310b(即第一 标头)都关闭。因此,根据示例性实施例,i/o电路106的第一组件子组506a和第二组件子组506b中的每一个的标头从功率小憩周期t_nap关闭, 直到时钟信号202的下一个时钟循环的开始。

77.第一功率控制晶体管310a和第二功率控制晶体管310b中的每一个的 关闭导致第一功率控制晶体管310a和第二功率控制晶体管310b中的每一 个的漏极(即,第一vdd_io信号318a和第二vdd_io信号318b中的每 一个)下降到逻辑低电平。也就是说,i/o电路106的第一组件子组506a 和第二组件子组506b中的每一个的虚拟电源信号也从功率小憩周期t_nap 下降到逻辑低电平,直到时钟信号202的下一个时钟循环的开始。

78.功率控制电路110也用于控制字线驱动器电路102的标头或部分标头。 例如,图6示出了根据示例性实施例的具有用于关闭字线驱动器电路102 的标头或部分标头的功率控制机制的存储器件100。如图6所示,存储器 件100包括字线驱动器电路102、单元阵列104、i/o电路106和时序控制 单元108。此外,如图6所示,存储器件100包括复制列502、预充电电路 304、电压检测器306和not逻辑电路312。此外,图6的存储器件100 包括nor逻辑电路604和功率控制晶体管606。功率控制晶体管606形成 字线驱动器标头102a或字线驱动器标头102a的一部分。对于本领域普通 技术人员来说,在阅读本发明之后,显而易见的是存储器件100可以包括 比图5中所示的更多或更少的组件。

79.复制列502包括连接到预充电电路304的复制位线bl和复制互补位 线blb。预充电电路304通过not逻辑电路312连接到定时控制单元108 的第一输出端。电压检测器306连接到复制位线bl。然而,对于本领域普 通技术人员来说,在阅读本发明之后显而易见的是,电压检测器306可以 连接到复制互补位线blb。

80.电压检测器306的输出连接到nor逻辑电路604的第一输入。电压检 测器306和nor

逻辑电路604可以形成功率控制电路110。nor逻辑电路 604的第二输入端连接到定时控制单元108的第一输出端。定时控制单元 108的第一输出端也连接到not逻辑电路312的输入端。时序控制单元的 第二输出端连接到字线驱动器电路102。

81.nor逻辑电路604的输出端连接到功率控制晶体管606的栅极(即, 字线驱动器标头104a或字线驱动器标头104a的一部分)。功率控制晶体 管606的源极连接到电源电压(即vdd),功率控制晶体管606的漏极连 接到字线驱动器电路104。功率控制晶体管606是pmos晶体管。然而, 对于本领域普通技术人员来说,在阅读本发明之后将显而易见的是,功率 控制晶体管606可以是mosfet、nmos晶体管或cmos晶体管。另外, 功率控制晶体管606是对称的。也就是说,功率控制晶体管606的源极可 以是漏极,漏极可以是源极。

82.对于读取或写入操作,定时控制单元108在第一输出端产生pre信号 314。在示例中,当时钟信号202上升到逻辑高电平时,pre信号314上升 到逻辑高电平。pre信号314上升到逻辑高电平使得复制位线和复制互补 位线blb中的每一个通过预充电电路304连接到电源电压(即,vdd)。 这使得复制位线bl和复制互补位线blb中的每一个被预充电到预定电位 或预定电压。在预定时间之后,pre信号314下降到逻辑低电平,这使得 复制位线bl和复制互补位线blb中的每一个与电源电压关闭(即,vdd)。

83.在从电源电压(即,vdd)关闭之后,复制位线bl和复制互补位线 blb中的每一个开始放电。例如,复制位线bl和复制互补位线blb通过 连接到复制位线bl和复制互补位线blb的多个0

‑

单元和1

‑

单元放电。复 制位线bl和复制互补位线blb的放电速率取决于连接到复制位线bl和 复制互补位线blb的多个0

‑

单元和1

‑

单元的数量。

84.电压检测器306连续比较复制位线bl上的剩余电压和预定电压电平 420。当复制位线bl上的电压高于预定电压电平420时,电压检测器306 的输出端(即,wl_标头信号602或标头控制信号204)处于逻辑高电平。 通过扩展,nor逻辑电路604的第一输入端处于逻辑高电平,这使得nor 逻辑电路604的输出(即,nor逻辑电路604的输出端)处于逻辑低电平。 当nor逻辑电路604的输出端处于逻辑低电平时,功率控制晶体管606的 栅极处于逻辑低电平,这开启了功率控制晶体管606。因此,当复制位线 bl上的剩余电压高于预定电压电平420时,功率控制晶体管606(即,字 线驱动器标头102a)保持开启。此外,功率控制晶体管606的开启导致功 率控制晶体管606的漏极连接到电源电压(即,vdd),并且处于逻辑高 电平。这导致字线驱动器电路102的vdd_wl信号608(即,虚拟电源信 号)处于逻辑高电平。

85.然而,当复制位线bl上的剩余电压下降到低于预定电压电平420时 (在功率小憩周期t_nap时),电压检测器306的输出端(即,wl标头 信号602或功率控制信号204)下降到逻辑低电平。这导致nor逻辑电路 604的第一输入端处于逻辑低电平,这将nor逻辑电路604的输出(即 nor逻辑电路604的输出端)驱动到逻辑高电平。当nor逻辑电路604 的输出端处于逻辑高电平时,功率控制晶体管606的栅极处于逻辑高电平, 这关闭了功率控制晶体管606(即,字线驱动器标头102a或字线驱动器标 头104a的一部分)。

86.因此,根据示例性实施例,当复制位线bl上的剩余电压在时钟循环 期间下降到预定电压电平420以下时,字线驱动器电路102的标头或部分 标头从功率小憩周期t_nap关闭,直到时钟信号202的下一个时钟循环的 开始。功率控制晶体管606的关闭导致功率控制晶体管606的漏极以及 vdd_wl信号608(通过扩展)下降到逻辑低电平。也就是说,根据示例 性实施例,当复制位线bl上的剩余电压在时钟循环期间下降到预定电压 电平420以下时,

字线驱动器电路102的虚拟电源信号从功率小憩周期 t_nap下降到逻辑低电平,直到时钟信号202的下一个时钟循环的开始

87.在示例性实施例中,功率控制晶体管606是p型沟道金属氧化物半导 体(pmos)晶体管。然而,其他类型的晶体管也在本发明的范围内。例如, 功率控制晶体管606可以是mosfet、nmos晶体管或mos晶体管。另外, 功率控制晶体管606是对称的。也就是说,功率控制晶体管606的源极可 以是漏极,漏极可以是源极。

88.图7a是根据本发明的一些实施例的第一类型0

‑

单元的图700。如图 7a所示,第一种类型的0

‑

单元包括第一反相器702和第二反相器704。第 一反相器702包括第一反相器第一晶体管702a和第一反相器第二晶体管 702b。第一反相器第一晶体管702a是pmos晶体管,第一反相器第二晶体 管702b是nmos晶体管。第一反相器第一晶体管702a的源极连接到电源 电压(即,vdd),第一反相器第一晶体管702a的漏极连接到q节点。 第一反相器第一晶体管702a的源极连接到q节点,第一反相器第一晶体管 702a的漏极接地(即,vss)。第一反相器第一晶体管702a和第一反相器 第二晶体管702b中的每一个的栅极连接到电源电压(即,vdd)。q节点 通过第一存取晶体管706连接到复制位线bl。

89.第二反相器704包括第二反相器第一晶体管704a和第二反相器第二晶 体管704b。第二反相器第一晶体管704a是pmos晶体管,第二反相器第 二晶体管704b是nmos晶体管。第二反相器第一晶体管704a的源极连接 到电源电压(即,vdd),第二反相器第一晶体管704a的漏极连接到qb 节点。第二反相器第一晶体管704a的源极连接到qb节点,第二反相器第 一晶体管704a的漏极接地(即,vss)。第二反相器第一晶体管704a和第 二反相器第二晶体管704b中的每一个的栅极接地(即,vss)。qb节点 通过第二存取晶体管708连接到复制互补位线blb。第一存取晶体管706 和第二存取晶体管708中每一个的栅极连接到字线wl。

90.如图7a的图表700所示,第一种类型的0

‑

单元被强制在q节点存储 位值0,在qb节点存储位值1。也就是说,在第一种类型的0

‑

单元中,q 节点被强制保持在逻辑0,qb节点被强制保持在逻辑1。在示例性实施例 中,其他类型的晶体管,即,mosfet、nmos晶体管、pmos晶体管或 cmos晶体管可以用于第一反相器第一晶体管702a、第一反相器第二晶体 管702b、第二反相器第一晶体管704a、第二反相器第二晶体管704b、第一 存取晶体管706和第二存取晶体管708中的每一个。另外,第一反相器第 一晶体管702a、第一反相器第二晶体管702b、第二反相器第一晶体管704a、 第二反相器第二晶体管704b、第一存取晶体管708和第二存取晶体管708 中的每一个都是对称的。也就是说,源极可以是漏极,漏极可以是源极。

91.图7b是根据本发明的一些实施例的第一类型1

‑

单元的图720。如图 7b所示,第一类型的1

‑

单元还包括第一反相器702和第二反相器704。然 而,对于第一类型的1

‑

单元,第一反相器第一晶体管702a和第一反相器第 二晶体管702b中的每一个的栅极接地(即,vss)。另外,第二反相器第 一晶体管704a和第二反相器第二晶体管704b中的每一个的栅极连接到电 源电压(即,vdd)。因此,第一种类型的1

‑

单元被强制在q节点存储位 值1,在qb节点存储位值0。

92.图7c是根据本发明的一些实施例的第二类型的0

‑

单元的图740。如图 7c所示,第二种类型的0

‑

单元还包括第一反相器702和第二反相器704。 然而,对于第二类型的0

‑

单元,第一反相器第一晶体管702a和第一反相器 第二晶体管702b中的每一个的栅极连接到电源电压(即,vdd)。此外, 第二反相器第一晶体管704a和第二反相器第二晶体管704b中的

每一个的 栅极连接到q节点。因此,第二种类型的0

‑

单元被强制在q节点存储位值 0,在qb节点存储位值1。

93.图7d是根据本发明的一些实施例的第二类型的1

‑

单元的图760。如图 7c所示,第二种类型的1

‑

单元还包括第一反相器702和第二反相器704。 然而,对于第二类型的1

‑

单元,第一反相器第一晶体管702a和第一反相器 第二晶体管702b中的每一个的栅极接地(即,vss)。此外,第二反相器 第一晶体管704a和第二反相器第二晶体管704b中的每一个的栅极连接到 q节点。因此,第二种类型的1

‑

单元被强制在q节点存储位值1,在qb 节点存储位值0。

94.对于本领域普通技术人员来说,参考图7a、图7b、图7c和图7d描 述的第一类型和第二类型的0

‑

单元和1

‑

单元仅仅是示例,其他类型的0

‑

单 元和1

‑

单元也在本发明的范围内。

95.图8a是示出了根据一些实施例的,第一频率的时钟信号202以及与第 一频率的时钟信号202相对应的图5和图6的存储器件100的其他信号的 曲线图800。例如,曲线图800的第一曲线802表示时钟信号202,曲线图 800的第二曲线804表示pre信号314,曲线图800的第三曲线806表示 复制位线bl上的剩余电压,曲线图800的第四曲线808表示vdd_io信 号318和vdd_wl信号608。

96.如图8a的曲线图800的第一曲线802和第二曲线804所示,当时钟信 号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外,如 第三曲线806所示,当pre信号314从逻辑高电平下降到逻辑低电平时, 复制位线bl上的剩余电压开始下降。pre信号314在对复制位线bl预充 电后变为逻辑低电平。

97.然而,如第三曲线806所示,在时钟信号202上升到下一时钟循环的 逻辑高电平之前,复制位线bl上的剩余电压不会下降到预定电压电平420 以下。并且当时钟信号202在下一个时钟循环上升到逻辑高电平时,复制 位线bl上的剩余电压被预充电到逻辑高电平。因此,如第四曲线808所 示,vdd_io信号318和vdd_wl信号608都保持在逻辑高电平,指示i/o 电路106和字线驱动器电路102的标头保持开启。因此,根据示例性实施 例,当时钟信号202的周期小于功率小憩周期t_nap时,标头i/o电路106 字线驱动器电路102在整个时钟循环内保持开启。

98.图8b是示出根据一些实施例的第二频率的时钟信号202和与第二频率 的时钟信号202相对应的存储器件100的其他信号的曲线图850。例如, 曲线图850的第一曲线852表示第二频率的时钟信号202,曲线图850的 第二曲线854表示pre信号314,曲线图850的第三曲线856表示复制位 线bl上的剩余电压,曲线图850的第四曲线858表示io_标头信号316和 wl标头信号602,曲线图850的第五曲线860表示vdd_io信号318和 vdd_wl信号608。

99.如图8b的第一曲线852所示,时钟信号202的第二频率低于图8a的 第一曲线802中描绘的第一频率。因此,对应于第二频率的时钟信号202 的时钟循环周期t2大于第一频率的时钟循环202的时钟循环周期t1。如 曲线图850的第三曲线856所示,较长的时钟循环周期为复制位线bl上 的剩余电压下降到预定电压电平420以下提供了足够的时间(即,功率小 憩周期t_nap)。如曲线图850的第四曲线858所示,这导致io_标头信号 316和wl标头信号602在功率小憩周期t_nap结束时从逻辑高电平变为 逻辑低电平。作为响应,如曲线图850的第五曲线860所示,vdd_io信 号318和vdd_wl信号608在功率小憩周期t_nap结束时从

逻辑高电平变 为逻辑低电平。

100.vdd_io信号318和vdd_wl信号608从逻辑高电平到逻辑低电平的 变化导致i/o电路106的标头或部分标头(即,第一功率控制晶体管310a 和第二功率控制晶体管310b)和标头字线驱动器电路102的标头或部分标 头(即,功率控制晶体管606)在功率小憩周期t_nap结束时被关闭。因 此,根据示例性实施例,当时钟信号202的周期大于功率小憩周期t_nap 时,在功率小憩周期t_nap之后,i/o电路106的标头或部分标头被关闭。 此外,根据示例性实施例,当时钟信号202的周期大于功率小憩周期t_nap 时,在功率小憩周期t_nap之后,字线驱动器电路102的标头或部分标头 被关闭。

101.继续参考图8b,如曲线图850的第二曲线854所示,在第一时钟循环 周期结束时,pre信号314响应于下一时钟循环的开始而从逻辑低电平上 升到逻辑高电平。如图850的第三曲线856所示,这导致复制位线bl的 预充电。随着复制位线bl的预充电,复制位线bl上的剩余电压上升到预 定电压电平420以上。因此,如曲线图850的第四曲线858和第五曲线860 所示,io_标头信号316和vdd_io信号318都从逻辑低电平变为逻辑高 电平。此外,如曲线图850的第四曲线858和第五曲线860所示,wl标 头信号602和vdd wl信号608都从逻辑低电平变为逻辑高电平。io_标 头信号316上升到逻辑高电平导致第一组件子组506a和第二组件子组506b 的标头重新开启。类似地,wl_标头信号602上升到逻辑高电平导致字线 驱动器电路102的标头重新开启。因此,根据示例性实施例,从功率控制 周期t_nap的结束到循环周期的结束,第一子组组件506a和第二子组组件 506b的标头以及标头字线驱动器电路102被关闭。

102.图9是示出根据一些实施例的图5和图6的存储器件100的时钟信号 202和与连接到复制位线bl的不同数量的0

‑

单元相对应的其他信号的曲线 图900。例如,曲线图900的第一曲线902表示时钟信号202,曲线图900 的第二曲线904表示pre信号314。此外,曲线图900的第三曲线906表 示具有第一多个0

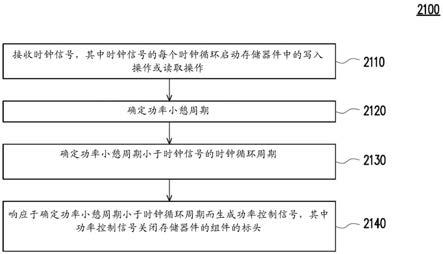

‑

单元的复制位线bl上的剩余电压。此外,曲线图900 的第四曲线908表示具有第二多个0

‑

单元的复制位线bl上的剩余电压。

103.曲线图900的第五曲线910表示对应于具有第一多个0

‑

单元的复制位 线bl的io_标头信号316和wl_标头信号602。此外,曲线图900的第六 曲线912表示对应于具有第二多个0

‑

单元的复制位线bl的io_标头信号 316和wl_标头信号602。此外,曲线图900的第七曲线914表示对应于 具有第一多个0

‑

单元的复制位线bl的vdd_io信号318和vdd_wl信号608。此外,曲线图900的第八曲线916表示对应于具有第二多个0

‑

单元的 复制位线bl的vdd_io信号318和vdd_wl信号608。与具有相同数量 的1

‑

单元的第一多个0

‑

单元相比,第二多个0

‑

单元包括更多的0

‑

单元。

104.如图9的曲线图900的第一曲线902和第二曲线904所示,当时钟信 号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外,如 第三曲线906和第四曲线908所示,当pre信号314从逻辑高电平下降到 逻辑低电平时,复制位线bl上的电压开始下降。然而,如第三曲线906 和第四曲线908所示,具有第一多个0

‑

单元的复制位线bl上的电压以比 具有第二多个0

‑

单元的复制位线bl更慢的速率下降。pre信号314在对 复制位线bl预充电后变为逻辑低电平。

105.如曲线图900的第三曲线906所示,较慢的放电速率没有为具有第一 多个0

‑

单元复制的位线bl上的剩余电压提供足够的时间(即,功率小憩 周期t_nap),使其在下一时钟

循环开始之前下降到预定电压电平420以 下。并且当时钟信号202上升到下一时钟循环的逻辑高电平时,具有第一 多个0

‑

单元的位线bl和具有第二多个0

‑

单元的位线bl上的剩余电压开始 上升。因此,如第五曲线910所示,io_标头信号316和wl_标头信号602 都保持在逻辑高电平。并且通过扩展,vdd_io信号318和vdd_wl信号 608也保持在逻辑高电平。因此,在下一个时钟循环开始时,标头第一子 组组件506a、第二子组组件506b和字线驱动器电路102保持开启。也就是 说,当复制位线bl在时钟信号202的周期期间与第一多个0

‑

单元相关联 时,第一子组组件506a、第二子组组件506b和字线驱动器电路102的标头 保持开启。

106.与之相反,如曲线图900的第四曲线908所示,更快的放电速率为具 有第二多个0

‑

单元的复制位线bl上的剩余电压在下一时钟循环开始之前 下降到预定电压电平420以下提供了足够的时间(即,功率小憩周期t_nap)。 因此,如第六曲线912所示,io_标头信号316和wl_标头信号602都从 逻辑高电平下降到逻辑低电平。并且通过扩展,vdd_io信号318和 vdd_wl信号608在功率小憩周期t_nap结束时都下降到逻辑低电平。作 为响应,如曲线图900的第八曲线916所示,vdd_io信号318和vdd_wl 信号608在功率小憩周期t_nap结束时从逻辑高电平变为逻辑低电平。将 io_标头信号316改变为逻辑低电平导致第一功率控制晶体管310a和第二 功率控制晶体管310b(即,第一组件子组506a、第二组件子组506b的标 头或部分标头)的关闭。类似地,将wl_标头信号602改变为逻辑低电平 导致功率控制晶体管606(即,字线驱动器电路102的标头或部分标头) 的关闭。。

107.继续参考图9,如曲线图900的第二曲线904所示,在第一时钟循环 周期结束时,pre信号314响应于下一时钟循环的开始而从逻辑低电平上 升到逻辑高电平。如曲线图900的第四曲线908所示,这导致具有第二多 个0

‑

单元的复制位线bl的预充电。随着具有第二多个0

‑

单元的复制位线 bl的预充电,具有第二多个0

‑

单元的复制位线bl上的剩余电压升高到预 定电压电平420以上。因此,如曲线图900的第六曲线912和第八曲线916 所示,io_标头信号316和vdd_io信号318都从逻辑低电平变为逻辑高 电平。此外,如曲线图900的第六曲线912和第八曲线916所示,wl标 头信号602和vdd wl信号608都从逻辑低电平变为逻辑高电平。

108.io_标头信号316上升到逻辑高电平导致第一功率控制晶体管310a和 第二功率控制晶体管310b(即,第一子组组件506a的标头和第二子组组件 506b的标头)重新开启。类似地,wl标头信号602上升到逻辑高电平导 致功率控制晶体管606(即,字线驱动器电路102的标头)开启。因此, 第一子组组件506a、第二子组组件506b和字线驱动器电路102的标头或部 分标头从功率控制周期t_nap的结束到具有第二多个0

‑

单元的复制位线bl 的时钟信号202的周期的结束被关闭。

109.因此,对于时钟信号202的相同频率,连接到复制位线bl的更多数 量的0

‑

单元增加了复制位线bl的放电速率,从而减少了功率控制周期 t_nap。因此,根据示例性实施例,可以通过控制连接到复制位线bl的0

‑ꢀ

单元或1

‑

单元的数量来控制功率控制周期t_nap。

110.图10示出了根据一些实施例的具有处于小憩模式的另一示例标头功 率控制机制的存储器件100。如图10所示,存储器件100包括字线驱动器 电路102、单元阵列104、i/o电路106和时序控制单元108。此外,如图10所示,存储器件100包括复制列502、预充电电路304、第一电压检测 器306a和第二电压检测器306b。此外,对于本领域普通技术人员来说,在 阅读本发明之后将显而易见的是,存储器件100可以包括比图10中所示的 更多或更少

的组件。

111.i/o电路106被示为包括第一组组件1002a和第n组组件1002n。第一 组元件1002a的标头由io_标头_1信号316a控制,第n组元件1002n的标 头由io_标头_2信号316b控制。此外,第一电压检测器306a产生io_标 头_1信号316a,第二电压检测器306b产生io_标头_2信号316b。对于本 领域普通技术人员来说,在阅读本发明之后显而易见的是,i/o电路106可 以包括多于两组的组件和多于两组的电压检测器电路306。

112.预充电电路304通过not逻辑电路312连接到定时控制单元108的第 一输出端。第一电压检测器306a和第二电压检测器306b中的每一个都连 接到复制位线bl。然而,对于本领域普通技术人员来说,在阅读本发明之 后将显而易见的是,第一电压检测器306a和第二电压检测器306b两者或 其中之一可以连接到复制互补位线blb。

113.第一电压检测器306a和第二电压检测器306b中的每一个都与不同的 预定电压电平相关联。例如,第一电压检测器306a与用于产生io_标头_1 信号316a的第一预定电压电平相关联,第二电压检测器306b与用于产生 io_标头_2信号316b的第二预定电压电平相关联。第一预定电压电平不同 于第二预定电压电平。例如,第一预定电压电平大于或大于第二预定电压 电平。

114.在示例性实施例中,当复制位线bl的电压下降到低于第一预定电压 电平时,第一电压检测器306a的输出端下降到逻辑低电平,这导致io_标 头_1信号316a下降到逻辑低电平。io_标头_1信号316a下降到逻辑低电 平导致与i/o电路106的第一组组件1002a相关联的标头或部分标头的切 换。类似地,当复制位线bl的电压下降到低于第二预定电压电平时,第 二电压检测器306b的输出端下降到逻辑低电平,这导致io_标头_2信号 316b下降到逻辑低电平。io_标头_2信号316b下降到逻辑低电平,这导致 关闭与i/o电路106的第二组组件1002b相关联的标头或部分标头。

115.图11是示出根据一些实施例的图10的存储器件100的时钟信号202 和对应于时钟信号202的其他信号的曲线图1100。例如,曲线图1100的 第一曲线1102表示时钟信号202,曲线图1100的第二曲线1104表示pre 信号314。曲线图1100的第三曲线1106表示复制位线bl上的剩余电压。 曲线图1100的第四曲线1108表示io_标头_1信号316a,曲线图1100的 第五曲线1110表示io_标头_2信号316b。

116.如图11的曲线图1100的第一曲线1102和第二曲线1104所示,当时 钟信号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外, 如曲线图1100的第三曲线1106所示,当pre信号314从逻辑高电平下降 到逻辑低电平时,复制位线bl上的剩余电压开始下降。pre信号314在 对复制位线bl预充电后变为逻辑低电平。

117.继续参考图11,如曲线图1100的第四曲线1108所示,当复制位线bl 上的剩余电压下降到低于第一预定电压电平420a时(在对应于第一电压检 测器306a的第一功率小憩周期t_nap 1结束时),io_标头_1信号316a从 逻辑高电平变为逻辑低电平。这导致关闭i/o电路106的第一组组件1102a 的标头或部分标头。另外,如曲线图1100的第五曲线1110所示,当复制 位线bl上的剩余电压下降到低于第二预定电压电平420b时(在对应于第 二电压检测器306b的第二功率小憩周期t_nap 2结束时),io_标头_2信 号316b从逻辑高电平变为逻辑低电平。这导致关闭i/o电路106的第n组 组件1102n的标头或部分标头。

118.因此,根据示例性实施例,i/o电路104的不同组件组的标头或部分标 头(并且通

过扩展字线驱动器电路和单元阵列104)可以在不同的功率小 憩周期tnap关闭,且因此关闭不同的时间。可以通过改变与不同电压检测 器306相关联的预定电压电平420来改变与不同组件组相关联的标头的关 闭时间。

119.图12示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件100。如图12所示,存储器件100包括字线驱动器 电路102、单元阵列104、i/o电路106和时序控制单元108。此外,如图 12所示,存储器件100包括复制vdd_io 1202和电压检测器306。此外, 对于本领域普通技术人员来说,在阅读本发明之后将显而易见的是,存储 器件100可以包括比图12中所示的更多或更少的组件。

120.定时控制单元108的第一输出端连接到not逻辑电路312的输入端。 not逻辑电路304的输出端连接到vdd io晶体管1206的栅极。vdd io 晶体管1206的源极连接到电源电压(即vdd),vdd io晶体管1206的 漏极连接到复制vdd_io 1202。多个复制vdd晶体管(例如,第一复制 vdd晶体管1204a1、第二复制vdd晶体管1204a2、

……

等)连接到复制 vdd_io 1202。多个复制vdd晶体管的每一个的栅极连接到电源电压(即, vdd)。多个复制vdd晶体管的每一个的源极连接到复制vdd_io 1202。 此外,多个复制vdd晶体管的每一个的漏极接地。电压检测器306连接到 复制vdd_io 1202,并且可操作来将复制vdd_io 1202上的电压与预定电 压电平420进行比较。

121.在示例性实施例中,vdd io晶体管1206和多个复制vdd晶体管中 的每一个(即,第一复制vdd晶体管1204a1、第二复制vdd晶体管 1204a2、

……

等)是p型沟道金属氧化物半导体(pmos)晶体管。然而, 其他类型的晶体管也在本发明的范围内。例如,vdd io晶体管1206和多 个复制vdd晶体管中的每一个可以是mosfet、nmos晶体管或cmos 晶体管。此外,vdd io晶体管1206和多个复制vdd晶体管中的每一个 是对称的。也就是说,vdd io晶体管1206的源极和多个复制vdd晶体 管的每一个可以是漏极,漏极可以是源极。

122.对于读取或写入操作,定时控制单元108基于时钟信号202在第一输 出端产生pre信号314。当时钟信号202上升到逻辑高电平时,pre信号 314上升到逻辑高电平。这导致not逻辑电路312的输出端以及vdd io 晶体管1206的栅极下降到逻辑低电平。这开启了vdd io晶体管1206,从 而将复制vdd_io 1202连接到电源电压(即vdd),该电源电压将复制 vdd_io 1202预充电到预定电位或电压。

123.在从上升到逻辑高电平的预定时间之后,pre信号314下降到逻辑低 电平,这导致not逻辑电路312的输出端以及vdd io晶体管1206的栅 极下降到逻辑低电平。这关闭了vdd io晶体管1206,从而将复制vdd_io 1202从电源电压(即vdd)关闭。在从电源电压(即,vdd)关闭之后, 复制vdd_io 1202开始通过多个复制晶体管(即,第一复制vdd晶体管 1204a1、第二复制vdd晶体管1204a2、

……

等)放电。在示例性实施例 中,复制vdd_io 1202的放电速率取决于连接到复制vdd_io 1202的多 个复制晶体管的数量。

124.电压检测器306连续地将复制vdd_io 1202上的剩余电压与预定电压 电平420进行比较。当复制vdd_io 1202上的剩余电压高于预定电压电平 420时,电压检测器306的输出端(即,io_标头信号316)处于逻辑高电 平。这使得i/o电路106的标头保持开启,直到下一个时钟循环开始。因 此,根据示例性实施例,当复制vdd_io 1202上的剩余电压高于预定电压 电平420时,i/o电路106的标头保持开启。

125.然而,当复制vdd_输入输出1202上的电压下降到低于预定电压电平 420时,电压

检测器306的输出端(即io_标头信号316)下降到逻辑低电 平。这会关闭i/o电路106的标头或部分标头。因此,根据示例性实施例, i/o电路106的标头或部分标头从功率小憩周期t_nap被关闭,直到时钟信 号202的下一个时钟循环的开始。

126.图13示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件100。如图13所示,存储器件100包括字线驱动器 电路102、单元阵列104、i/o电路106和时序控制单元108。此外,如图 13所示,存储器件100包括复制vdd_wl 1302和电压检测器306。此外, 对于本领域普通技术人员来说,在阅读本发明之后将显而易见的是,存储 器件100可以包括比图13中所示的更多或更少的组件。

127.定时控制单元108的第一输出端连接到not逻辑电路312的输入端。 not逻辑电路312的输出端连接到vdd wl晶体管1306的栅极。vdd wl 晶体管1306的源极连接到电源电压(即vdd),vdd wl晶体管1306的 漏极连接到复制vdd_wl 1302。多个复制vdd晶体管(例如,第一复制 vdd晶体管1304a1、

……

等)连接到复制vdd_wl 1302。多个复制vdd 晶体管的每一个的栅极连接到电源电压(即,vdd)。多个复制vdd晶 体管的每一个的源极连接到vdd_wl 1302。此外,多个复制vdd晶体管 的每一个的漏极接地。电压检测器306连接到复制vdd_wl 1302,并且可 操作来将复制vdd_wl 1302上的电压与预定电压电平420进行比较。

128.在示例性实施例中,vdd wl晶体管1306和多个复制vdd晶体管中 的每一个(即,第一复制vdd晶体管1304a1、

……

等)。,)是p型沟 道金属氧化物半导体(pmos)晶体管。然而,其他类型的晶体管也在本发 明的范围内。例如,vdd wl晶体管1306和多个复制vdd晶体管中的每 一个可以是mosfet、nmos晶体管或cmos晶体管。此外,vdd wl晶 体管1306和多个复制vdd晶体管中的每一个是对称的。也就是说,源极 可以是漏极,漏极可以是源极。

129.对于读取或写入操作,定时控制单元108基于时钟信号202在第一输 出端产生pre信号314。当时钟信号202上升到逻辑高电平时,pre信号 314上升到逻辑高电平。这导致not逻辑电路312的输出端以及vdd wl 晶体管1306的栅极下降到逻辑低电平。这开启了vdd wl晶体管1306, 从而将复制vdd_wl 1302连接到电源电压(即,vdd),该电源电压将 复制vdd_io 1202充电到预定电位或电压。

130.在从上升到逻辑高电平的预定时间之后,pre信号314下降到逻辑低 电平,这导致not逻辑电路312的输出端以及vdd wl晶体管1306的栅 极下降到逻辑低电平。这关闭了vdd wl晶体管1306,从而将复制 vdd_wl 1302从电源电压(即,vdd)关闭。在从电源电压(即,vdd) 关闭之后,复制vdd_wl 1302开始通过多个复制晶体管(即,第一复制 vdd晶体管1304a1、

……

等)放电。在示例性实施例中,复制vdd_wl 1302 的放电速率取决于连接到复制vdd_wl 1302的多个复制晶体管的数量。

131.电压检测器306连续地将复制vdd_wl 1302上的剩余电压与预定电 压电平420进行比较。当vdd_wl 1302上的剩余电压高于预定电压电平 420时,电压检测器306的输出端(即wl_标头信号602)处于逻辑高电 平。通过扩展,nor逻辑电路1308的第一输入端处于逻辑高电平,因此, nor逻辑电路1308的输出端(即,nor逻辑电路1308的输出端)处于逻 辑低电平。此外,当nor逻辑电路1308的输出端处于逻辑低电平时,栅 极功率控制晶体管1310处于逻辑低电平,这开启功率控制晶体管1310。 因此,当复制vdd_wl 1302上的剩余电压高于预定电压电平420时,字 线驱动器电路102的标头保持开启。此外,功率控制晶体管1310的漏极连 接到电源电压(即,vdd),并且处于逻辑高电平。这使得vdd_wl信 号608(即,到字线

驱动器电路102的虚拟电源信号)处于逻辑高电平。

132.然而,当vdd_io 1302上的剩余电压下降到低于预定电压电平420时, 电压检测器306的输出端(即,wl_标头信号602)下降到逻辑低电平。 通过扩展,nor逻辑电路1308的第一输入端处于逻辑低电平,并且nor 逻辑电路1308的输出端(即,nor逻辑电路1308的输出端)处于逻辑高 电平。此外,当nor逻辑电路1308的输出端处于逻辑高电平时,功率控 制晶体管1310的栅极处于逻辑高电平,这关闭了功率控制晶体管1310。 因此,根据示例性实施例,当复制vdd_wl 1302上的剩余电压下降到预 定电压电平420以下时,字线驱动器电路102的标头或部分标头被关闭。 此外,功率控制晶体管1310的漏极与电源电压(即,vdd)关闭,并且处 于逻辑低电平。这导致vdd_wl信号608下降到逻辑低电平,并且通过扩 展,当复制vdd_wl 1302上的剩余电压下降到预定电压电平420以下时, 字线驱动器电路102的虚拟电源信号下降到逻辑低电平。

133.图14a是示出根据一些实施例的第一频率的时钟信号202以及与第一 频率的时钟信号202相对应的图12和13的存储器件100的其他信号的曲 线图1400。例如,曲线图1400的第一曲线1402表示时钟信号202。曲线 图1400的第二曲线1404表示pre信号314。曲线图1400的第三曲线1406 表示复制vdd_io 1202和复制ndd_wl 1302上的剩余电压。曲线图1400 的第四曲线1408表示vdd_io信号318和vdd_wl信号608。

134.如图14a的曲线图1400的第一曲线1402和第二曲线1404所示,当时 钟信号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外, 如曲线图1400的第三曲线1406所示,当pre信号314下降到逻辑低电平 时,复制vdd_io 1202和复制vdd_wl 1302上的剩余电压开始下降。pre 信号314在从上升到逻辑高电平的预定时间后变为逻辑低电平。

135.继续参考图14a,如第三曲线1406所示,在时钟信号202的第一频率 的第一时钟循环周期内,复制vdd_io 1202或复制vdd_wl 1302上的剩 余电压均未降至预定电压电平420以下。并且当时钟信号202上升到下一 个时钟循环的逻辑高电平时,复制vdd_io 1202和复制vdd_wl 1302中 的每一个上的剩余电压上升到预定电压电平420之上。因此,如第四曲线 1408所示,vdd_io信号318和vdd_wl信号608都保持在逻辑高电平。 因而,当时钟信号202的循环周期小于功率修整周期t_nap时,i/o电路 106和字线驱动器电路102的标头保持开启。

136.图14b是示出根据一些实施例的第二频率处的时钟信号202以及与第 二频率处的时钟信号202相对应的图12和13的存储器件100的其他信号 的曲线图1450。例如,曲线图1450的第一曲线1452表示第二频率的时钟 信号202,曲线图1450的第二曲线1454表示pre信号314。曲线图1450 的第三曲线1456表示复制vdd_io 1202和复制vdd_wl 1302上的剩余 电压。曲线图1450的第四曲线1458表示io_标头信号316和wl_标头信 号602。曲线图1450的第五曲线1460表示vdd_io信号318和vdd_wl 信号608。

137.如图14b的第一曲线1452所示,时钟信号202的第二频率低于图14a 的第一曲线1402中所示的第一频率。因此,对应于第二频率的时钟信号 202的时钟循环周期t2大于对应于第一频率的时钟循环202的时钟循环周 期t1。如曲线图1450的第三曲线1456所示,较长的时钟循环周期为复制 vdd_io 1202和复制vdd_wl 1302上的剩余电压提供了足够的时间(即, 功率小憩周期t_nap)来降低到预定电压电平420以下。如曲线图1450的 第四曲线1458所示,这导致io_标头信号316和wl标头信号602在功率 小憩周期t_nap结束时从逻辑高电平变为逻辑低电平。

138.将io_标头信号316改变为逻辑低电平导致关闭i/o电路106的标头或 部分标头。作为响应,如曲线图1450的第五曲线1460所示,vdd_io信 号318(即,i/o电路106的虚拟电源信号)在功率小憩周期t_nap结束时 从逻辑高电平变为逻辑低电平。类似地,将wl标头信号602变为逻辑低 电平导致关闭字线驱动器电路102的标头或部分标头。作为响应,如曲线 图1450的第五曲线1460所示,vdd_wl信号608(即,字线驱动器电路 102的虚拟电源信号)在功率小憩周期t_nap结束时从逻辑高电平变为逻 辑低电平。

139.继续参考图14b,如曲线图1450的第二曲线1454所示,在第一时钟 循环周期结束时,pre信号314响应于下一时钟循环的开始而从逻辑低电 平上升到逻辑高电平。如图1450的第三曲线1456所示,这导致复制 vdd_io 1202和复制vdd_wl 1302的预充电。随着复制vdd_io 1202和 复制vdd_wl 1302的预充电,复制vdd_io 1202和复制vdd_wl 1302 上的剩余电压上升到预定电压电平420以上。因此,如曲线图1450的第四 曲线1458和第五曲线1460所示,在下一个时钟循环开始时,io_标头信号 316和vdd_io信号318都从逻辑低电平变为逻辑高电平。io_标头信号 316上升到逻辑高电平导致重新开启i/o电路106的标头。类似地,wl_ 标头信号602上升到逻辑高电平导致字线驱动器电路102的标头开启。因 而,i/o电路106的标头或部分标头从第二频率的时钟信号202的功率控制 周期t_nap的结束到循环周期的结束被关闭。

140.类似地,字线驱动器电路102的标头或部分标头从第二频率的时钟信 号202的功率控制周期t_nap的结束到循环周期的结束被关闭。因此,根 据示例性实施例,对于较低频率的时钟信号202的当前周期,从功率控制 周期t_nap的结束到循环周期的结束,i/o电路106的标头或部分标头以及 字线驱动器电路102的标头或部分标头被关闭。

141.此外,如曲线图1450的第四曲线1458和第五曲线1460所示,在下一 个时钟循环开始时,wl标头信号602和vdd wl信号608都从逻辑低电 平变为逻辑高电平。vdd_io信号318上升到逻辑高电平导致i/o电路106 的虚拟电源信号上升到逻辑高电平。类似地,vdd_wl信号608上升到逻 辑高电平导致字线驱动器电路102的虚拟电源信号上升到逻辑高电平。

142.图15是根据一些实施例的曲线图1500,示出了连接到复制vdd_io1202和复制vdd_wl 1302的不同数量的多个复制vdd晶体管的图12和 13的存储器件100的时钟信号202和其他信号。例如,曲线图1500的第 一曲线1502表示时钟信号202,曲线图1500的第二曲线1504表示pre信 号314。曲线图1500的第三曲线1506表示具有第一多个复制vdd晶体管 的复制vdd_io 1202和复制vdd_wl 1302上的剩余电压。曲线图1500 的第四曲线1508表示具有第二多个复制vdd晶体管的复制vdd_io 1202 和复制vdd_wl 1302上的剩余电压。曲线图1500的第五曲线1510表示 与具有第一多个复制vdd晶体管的复制vdd_io 1202和复制vdd_wl 1302相对应的io_标头信号316和wl标头信号602。

143.另外,曲线图1500的第六曲线1512表示与具有第二多个复制vdd晶 体管的复制vdd_io 1202和复制vdd_wl 1302相对应的io_标头信号316 和wl标头信号602。曲线图1500的第七曲线1514表示与具有多个第一 复制vdd晶体管的复制vdd_io 1202和复制vdd_wl 1302相对应的 vdd_io信号318和vdd_wl信号608。曲线图1500的第八曲线1516表 示与具有第二多个复制vdd晶体管的复制vdd_io 1202和复制vdd_wl 1302相对应的vdd_io信号318和vdd_wl信号608。第二多个复制vdd 晶体管包括比第一多个复制vdd晶体管更多数量的复制vdd晶体管。

144.如图15的曲线图1500的第一曲线1502和第二曲线1504所示,当时 钟信号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外, 如第三曲线1506和第四曲线1508所示,当pre信号314从逻辑高电平下 降到逻辑低电平时,复制vdd_io 1202和复制vdd_wl 1302上的剩余电 压开始下降。然而,如第三曲线1506和第四曲线1508所示,具有第一多 个复制vdd晶体管的复制vdd_io 1202和复制vdd_wl 1302中的每一 个上的剩余电压以比具有第二多个复制vdd晶体管的复制vdd_io 1202 和复制vdd_wl 1302中的每一个上的剩余电压更慢的速率下降。pre信 号314在从上升到逻辑高电平的预定时间之后或者在分别对复制vdd_io1202和复制vdd_wl 1302预充电之后变为逻辑低电平。

145.如曲线图1500的第三曲线1506所示,较慢的放电速率不能为具有第 一多个复制vdd晶体管的复制vdd_io 1202上的剩余电压提供足够的时 间,使其在下一个时钟循环开始之前下降到预定电压电平420以下(即, 功率小憩周期)。类似地,如曲线图1500的第三曲线1506所示,较慢的 放电速率不能为具有第一多个复制vdd晶体管的复制vdd_wl 1302上的 剩余电压提供足够的时间(即,功率小憩周期t_nap),使其在下一个时 钟循环开始之前下降到预定电压电平420以下。并且当时钟信号202上升 到下一时钟循环的逻辑高电平时,具有第一多个复制vdd晶体管的复制 vdd_io 1202和复制vdd_wl 1302中的每一个上的剩余电压开始再次上 升。

146.因而,如第五曲线1510所示,io_标头信号316和wl_标头信号602 都保持逻辑高电平。因此,当时钟信号202的循环周期小于功率小憩周期 t_nap时,i/o电路106和字线驱动器电路102的标头保持开启。也就是说, 当时钟信号202的周期小于功率小憩周期t_nap时,在下一个时钟循环开 始之前,字线驱动器电路102的标头和标头i/o电路106不被关闭。并且 通过扩展,vdd_io信号318(即,i/o电路106的虚拟电源信号)和wl 信号608(即,字线驱动器电路102的虚拟电源信号)都保持在逻辑高电 平。

147.与之相反,较快的放电速率(如曲线图1500的第四幅图1508所示) 为具有第二多个复制vdd晶体管的复制vdd_io 1202和复制vdd_wl 1302中的每一个上的剩余电压提供了足够的时间(即,功率小憩周期 t_nap),使其在下一个时钟循环开始之前下降到预定电压电平420以下。 因此,如第六曲线1510所示,io_标头信号316和wl_标头信号602都从 逻辑高电平下降到逻辑低电平。将io_标头信号316改变为逻辑低电平导 致在功率小憩周期结束时关闭i/o电路106的标头或部分标头。类似地, 将wl标头信号602改变为逻辑低电平导致在功率小憩周期t_nap结束时 关闭字线驱动器电路102的标头或部分标头。另外,如曲线图1500的第八 曲线1506所示,vdd_io信号318(即,i/o电路106的虚拟电源信号) 和vdd_wl信号608(即,字线驱动器电路102的虚拟电源信号)在功率 小憩周期t_nap结束时从逻辑高电平变为逻辑低电平。

148.继续参考图15,如曲线图1500的第二曲线1504所示,在第一时钟循 环周期结束时,pre信号314响应于下一时钟循环的开始从逻辑低电平上 升到逻辑高电平。如曲线图1500的第四曲线1508所示,pre信号314上 升到逻辑高电平,导致具有第二多个复制vdd晶体管的复制vdd_io 1202 和复制vdd_wl 1302的预充电。通过对具有第二多个复制vdd晶体管的 复制vdd_io 1202和复制vdd_wl 1302进行预充电,复制vdd_io 1202 和具有第二多个复制vdd晶体管的复制vdd_wl 1302上的剩余电压上升 到预定电压电平420以上。

149.结果,如曲线图1500的第六曲线1512所示,在下一个时钟循环开始 时,io_标头信

号316和wl_标头信号602都从逻辑低电平变为逻辑高电 平。io_标头信号316变为逻辑高电平导致i/o电路106的标头重新开启。 类似地,wl_标头信号602变为逻辑高电平导致字线驱动器电路102的标 头重新开启。因此,根据示例性实施例,i/o电路106和字线驱动器电路 102的标头或部分标头从功率控制周期t_nap的结束到具有第二多个复制 vdd晶体管的复制vdd_io 1202和复制vdd_wl 1302的时钟信号202 的周期的结束被关闭。此外,如曲线图1500的第八曲线1516所示,vdd_io 信号318(即i/o电路106的虚拟电源信号)和vdd_wl信号608(即字 线驱动器电路102的虚拟电源信号)在下一个时钟循环开始时从逻辑低电 平变为逻辑高电平。

150.因此,对于时钟信号202的相同频率,连接到复制vdd_io 1202和复 制vdd_wl 1302的更多数量的复制vdd晶体管增加了复制vdd_io 1202 和复制vdd_wl 1302的放电速率,从而减少了功率控制周期t_nap。因 此,根据示例性实施例,功率控制周期t_nap可以通过控制连接到复制 vdd_io 1202和复制vdd_wl 1302的多个复制vdd晶体管的数量来控 制。

151.图16示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件100。如图16所示,存储器件100包括字线驱动器 电路102、单元阵列104、i/o电路106和时序控制单元108。此外,如图 16所示,存储器件100包括复制vdd_io 1202、第一电压检测器306a和 第二电压检测器306b。此外,对于本领域普通技术人员来说,在阅读本发 明之后将显而易见的是,存储器件100可以包括比图16中所示的更多或更 少的组件。

152.i/o电路106被示为包括第一组组件1002a和第n组组件1002n。第一 组组件1002a的标头由io_标头_1信号316a控制,第n组组件1002n的标 头由io_标头_2信号316b控制。此外,第一电压检测器306a产生io_标 头_1信号316a,第二电压检测器306b产生io_标头_2信号316b。对于本 领域普通技术人员来说,在阅读本发明之后,显而易见的是,i/o电路106 包括两组以上的组件和两个以上的电压检测器电路306。

153.定时控制单元108的第一输出端连接到not逻辑电路312的输入端。 not逻辑电路312的输出端连接到vdd晶体管1206的栅极。vdd晶体 管1206的源极连接到电源电压,vdd晶体管1206的漏极连接到复制 vdd_io 1202。第一电压检测器306a和第二电压检测器306b中的每一个 都连接到复制vdd_io 1202。

154.第一电压检测器306a和第二电压检测器306b中的每一个都与不同的 预定电压电平相关联。例如,第一电压检测器306a与第一预定电压电平 420a相关联。第一电压检测器306a可操作来响应于将复制vdd_io 1202 上的剩余电压与第一预定电压电平420a进行比较而产生io_标头_1信号 316a。类似地,第二电压检测器306b与第二预定电压电平420b相关联。 第二电压检测器306b可操作来响应于将复制vdd_io 1202上的剩余电压 与第二预定电压电平420b进行比较而产生io_标头_2信号316b。第一预 定电压电平420a不同于第二预定电压电平420b。例如,第一预定电压电平 420a低于或高于第二预定电压电平420b。

155.在示例性实施例中,当复制vdd_io 1202的剩余电压下降到低于第一 预定电压电平420a时,第一电压检测器306a的输出端下降到逻辑低电平, 这导致io_标头_1信号316a下降到逻辑低电平。io_标头_1信号316a下 降到逻辑低电平导致与i/o电路106的第一组组件1002a相关联的标头或 部分标头被关闭。类似地,当复制vdd_io 1202的剩余电压下降到低于第 二预定电压电平420b时,第二电压检测器306b的输出端下降到逻辑低电 平,这导

致io_标头_2信号316b下降到逻辑低电平。io_标头_2信号316b 下降到逻辑低电平导致关闭与i/o电路106的第二组组件1002b相关联的 标头或部分标头。

156.图17是示出根据一些实施例的时钟信号202和图16的存储器件100 的与时钟信号202相对应的其他信号的图1700。例如,曲线图1700的第 一曲线1702表示时钟信号202,曲线图1700的第二曲线1704表示pre信 号314。曲线图1700的第三曲线图1706表示复制vdd_io 1202上的剩余 电压。曲线图1700的第四曲线1708表示输入输出标头1信号316a。曲线 图1700的第五曲线1710表示输入输出标头2信号316b。

157.如曲线图1700的第一曲线1702和第二曲线1704所示,当时钟信号 202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外,如曲 线图1700的第三曲线1706所示,当pre信号314从逻辑高电平下降到逻 辑低电平时,复制vdd_输入输出1202上的剩余电压开始下降。pre信号 314在从上升到逻辑低电平的预定时间之后或者在复制vdd_io 1202预充 电之后变为逻辑低电平。

158.继续参考图17,如曲线图1700的第四曲线1708所示,当在对应于第 一电压检测器306a的第一功率小憩周期t_nap 1结束时,复制vdd_io1202上的剩余电压下降到低于第一预定电压电平420a时,io_标头_1信号 316a从逻辑高电平变为逻辑低电平。这导致关闭i/o电路106的第一组组 件1102a的标头或部分标头。此外,如曲线图1700的第五曲线1710所示, 当在对应于第二电压检测器306b的第二功率小憩周期t_nap 2结束时,复 制vdd_io 1202上的剩余电压下降到低于第二预定电压电平420b时,io_ 标头_2信号316b从逻辑高电平变为逻辑低电平。这导致关闭i/o电路106 的第二组组件1102b的标头或部分标头。因此,根据示例性实施例,i/o电 路106(以及字线驱动器电路102)的不同组的组件可以在时钟循环的不同 时间被关闭。

159.图18示出了根据一些实施例的具有处于小憩模式的又一示例标头功 率控制机制的存储器件100。如图18所示,存储器件100包括字线驱动器 电路102、单元阵列104、i/o电路106和时序控制单元108。此外,如图 18所示,存储器件100包括复制单元列1802和电压检测器306。此外,对 于本领域普通技术人员来说,在阅读本发明之后将显而易见的是,存储器 件100可以包括比图18中所示的更多或更少的组件。

160.复制单元列1802包括多个复制单元,例如,第一复制单元1804a1、第 二复制单元1804a2、

…

、第n复制单元1804an。多个复制单元中的每一个 都连接到复制vdd_单元1806。定时控制单元108的第一输出端连接到not逻辑电路312的输入端。not逻辑电路312的输出端连接到第一单元 晶体管1816的栅极。第一单元晶体管1816的源极连接到电源电压(即, vdd),第一单元晶体管1816的漏极连接到复制vdd_单元1806。电压 检测器306连接到复制vdd_单元1806,并可操作来将复制vdd单元_1806 上的剩余电压与预定电压电平420进行比较。

161.电压检测器306的输出端连接到第一nor逻辑电路1818a和第二nor 逻辑电路1818b中的每一个的第一输入端。对于本领域普通技术人员来说, 在阅读本发明之后将显而易见的是,电压检测器306的输出端可以连接到 存储器100的其他nor逻辑电路。第一nor逻辑电路1818a和第二nor 逻辑电路1818b中的每一个的第二输入端连接到定时控制单元108的第一 输出端。对于本领域普通技术人员来说,在阅读本发明之后,显而易见的 是,定时控制单元108的第一输出端可以连接到存储器100的其他nor逻 辑电路。

率晶体管1820b的关闭导致vdd_单元1810与电源电压(即,vdd)被 关闭,并且单元阵列104的相应标头被关闭。因此,根据示例性实施例, 当复制vdd_单元1806上的剩余电压下降到预定电压电平420以下时,单 元阵列104的标头或部分标头被关闭。

169.图19a是示出根据一些实施例的第一频率的时钟信号202和对应于第 一频率的时钟信号202的图18的存储器件100的其他信号的曲线图1900。 例如,曲线图1900的第一曲线1902表示时钟信号202,曲线图1900的第 二曲线1904表示pre信号314。曲线图1900的第三曲线1906表示复制 vdd_单元1806上的电压,曲线图1900的第四曲线1908表示vdd_单元 1810上的电压。

170.如图19a的曲线图1900的第一曲线1902和第二曲线1904所示,当时 钟信号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外, 如曲线图1900的第三曲线1906所示,当pre信号314从逻辑高电平下降 到逻辑低电平时,复制vdd_单元1806上的剩余电压开始下降。然而,如 第三曲线1906所示,在下一个时钟循环开始之前,复制vdd_单元1806 上的剩余电压不会下降到预定电压电平420以下。并且当时钟信号202在 下一个时钟循环上升到逻辑高电平时,复制vdd_单元1806上的剩余电压 开始上升。因此,如第四曲线1908所示,vdd_单元1810上的电压保持在 逻辑高电平。因而,当时钟信号202的循环周期小于功率小憩周期t_nap 时,单元阵列104的标头保持开启。

171.图19b是示出根据一些实施例的第二频率的时钟信号202和与第二频 率的时钟信号202相对应的存储器件100的其他信号的曲线图1950。例如, 曲线图1950的第一曲线1952表示第二频率的时钟信号202,曲线图1950 的第二曲线1954表示pre信号314。曲线图1950的第三曲线1956表示复 制vdd_单元1806上的电压。曲线图1950的第四曲线1958表示开关_vdd_ 单元信号1808。曲线图1950的第五曲线1960表示vdd_单元1810的电压。

172.如图19b的第一曲线1952所示,时钟信号202的第二频率低于与图19a的第一曲线1902相关联的第一频率。因此,对应于第二频率的时钟信 号202的时钟循环周期t2大于第一频率的时钟循环202的时钟循环周期 t1。如曲线图1950的第三曲线1956所示,较长的时钟循环周期为复制 vdd_单元1806上的电压下降到预定电压电平420以下提供了足够的时间 (即,功率小憩周期t_nap)。如曲线图1950的第四曲线1958所示,这 导致开关_vdd_单元信号1808在功率小憩周期t_nap结束时从逻辑高电平 变为逻辑低电平。作为响应,如曲线图1950的第五曲线1960所示,vdd_ 单元1810的电压在功率小憩周期t_nap结束时从逻辑高电平变为逻辑低电 平。将vdd_单元1810上的电压改变为逻辑低电平导致关闭单元阵列104 的标头或部分标头。

173.继续参考图19b,如曲线图1950的第二曲线1954所示,在第一时钟 循环周期结束时,pre信号314响应于下一时钟循环的开始而从逻辑低电 平上升到逻辑高电平。将pre信号314改变为逻辑高电平,如曲线图1950 的第三曲线1956所示,导致复制vdd_单元1806充电。随着复制vdd_ 单元1806的充电,复制vdd_单元1806上的剩余电压上升到预定电压电 平420之上。因此,如曲线图1950的第四曲线1958所示,开关_vdd_单 元信号1808从逻辑低电平变为逻辑高电平。此外,如曲线图1950的第五 曲线1960所示,vdd_单元1810上的电压从逻辑低电平变为逻辑高电平。 vdd_单元1810上的电压上升到逻辑高电平,导致单元阵列104的标头开 启。因此,从功率控制周期t_nap的结束到时钟信号202的周期的结束, 单元阵列104的标头被关闭。

174.图20是示出根据一些实施例的连接到复制vdd_单元1806的不同数 量的多个复制单元的时钟信号202的曲线图2000。例如,曲线图2000的 第一曲线2002表示时钟信号202,曲线图2000的第二曲线2004表示pre 信号314。曲线图2000的第三曲线2006表示具有第一多个复制单元的复 制vdd_单元1806上的电压。曲线图2000的第四曲线2008表示具有第二 多个复制单元的复制vdd_单元1806上的电压。曲线图2000的第五曲线 2010表示具有第一多个复制单元的开关_vdd_单元信号1808。曲线图2000 的第六曲线2012表示具有第二多个复制单元的开关_vdd_单元信号1808。 曲线图2000的第七曲线2014表示具有第一多个复制单元的vdd_单元 1810上的电压。曲线图2000的第八曲线2016表示具有第二多个复制单元 的vdd_单元1810上的电压。第二多个复制单元比第一多个复制单元具有 更多数量的复制单元。

175.如图20的曲线图2000的第一曲线2002和第二曲线2004所示,当时 钟信号202上升到逻辑高电平时,pre信号314上升到逻辑高电平。此外, 如第三曲线2006和第四曲线2008所示,当pre信号314下降到逻辑低电 平时,复制vdd_单元1806上的剩余电压开始下降。然而,如第三曲线2006 和第四曲线2008所示,具有第一多个复制单元的复制vdd_单元1806上 的剩余电压以比具有第二多个复制单元的复制vdd_单元1806更慢的速率 下降。

176.如曲线图2000的第三曲线2006所示,较慢的放电速率没有为具有第 一多个复制单元的复制vdd_单元1806上的剩余电压提供足够的时间(即, 功率小憩周期t_nap),使其在下一个时钟循环开始之前下降到预定电压 电平420以下。并且当时钟信号202在下一个时钟循环上升到逻辑高电平 时,具有第一多个vdd晶体管的复制vdd_单元1806上的剩余电压继续 保持在预定电压电平420之上。因此,如第五曲线2010所示,开关_vdd_ 单元信号1808保持在逻辑高电平。并且通过扩展,vdd_单元1810上的电 压保持在逻辑高电平。因而,在下一个时钟循环开始之前,单元阵列104 的标头或部分标头没有被关闭。也就是说,当时钟信号202的周期小于功 率小憩周期t_nap时,单元阵列104的标头保持开启。

177.与之相反,如曲线图2000的第四曲线2008所示,更快的放电速率为 具有第二多个复制单元的复制vdd_单元1806上的剩余电压提供了足够的 时间(即,功率小憩周期t_nap),使其在下一个时钟循环开始之前下降 到预定电压电平420以下。因此,如第六曲线2010所示,开关_vdd_单元 信号1808从逻辑高电平下降到逻辑低电平。并且通过扩展,vdd_单元1810 上的电压在功率小憩周期t_nap结束时下降到逻辑低电平。将vdd_单元 1810上的电压改变为逻辑低电平导致关闭单元阵列104的标头或部分标头。

178.继续参考图20,如曲线图2000的第二曲线2004所示,在第一时钟循 环周期结束时,pre信号314响应于下一时钟循环的开始而从逻辑低电平 上升到逻辑高电平。如曲线图2000的第四曲线2008所示,pre信号314 上升到逻辑高电平导致具有第二多个复制单元的复制vdd_单元1806的预 充电。随着具有第二多个复制单元对复制vdd_单元1806的预充电,具有 第二多个复制单元的复制vdd_单元1806上的剩余电压上升到预定电压电 平420以上。因此,如曲线图2000的第六曲线2012和第八曲线2016所示, 开关_vdd_单元信号1808和vdd_单元1810上的电压从逻辑低电平变为 逻辑高电平。vdd_单元1810上的电压上升到逻辑高电平,导致标头单元 阵列104的标头或标头单元阵列104的一部分开启。因此,从功率控制周 期t_nap的结束到时钟信号202的周期的结束,单元阵列104的标头被关 闭。

179.在示例性实施例中,对于时钟信号202的相同频率,连接到复制vdd_ 单元1806的

更多数量的复制单元增加了复制vdd_单元1806的放电速率, 从而减少了功率控制周期t_nap。因此,根据示例性实施例,可以通过控 制连接到单元1802的复制列的复制vdd_单元1806的多个复制单元的数 量来控制功率控制周期t_nap。

180.图21是示出根据一些实施例的用于操作存储器件的方法2100的流程 图。例如,图21是示出如上参考图1

‑

图20所述的操作存储器件100的方 法2100的流程图。方法2100可以由连接到存储器件的处理器来执行。此 外,方法700可以作为指令存储在存储器件上,例如非暂时性数据存储器 件或非暂时性计算机可读介质,当由处理器执行时,可以使处理器执行方 法2100。

181.在方法2100的框2110处接收时钟信号。时钟信号的每个时钟循环启 动存储器件中的写入操作或读取操作。例如,接收时钟信号202,并且时 钟信号202的每个时钟循环启动存储器件100中的读取或写入操作。

182.在方法2100的框2120处确定功率小憩时段。例如,通过确定位线bl 和互补位线blb的剩余电压的逻辑or来确定功率小憩周期t_nap。在一 些示例中,通过将复制位线bl上的剩余电压与预定电压电平进行比较来 确定功率小憩周期t_nap 420。在其他示例中,通过将复制互补位线blb 上的剩余电压与预定电压电平进行比较来确定功率小憩周期t_nap 420。

183.在方法2100的框2130处,确定功率小憩周期小于时钟信号的时钟循 环周期。在方法2100的框2140处,响应于确定功率小憩周期小于时钟循 环周期而产生标头控制信号204。标头控制信号204关闭存储器件的组件 的标头。例如,响应于确定功率小憩周期小于时钟循环周期而产生io_标 头信号316和wl_标头信号602。io_标头信号316和wl_标头信号602 分别关闭i/o电路106和字线驱动器电路102的标头或部分标头。

184.根据示例性实施例,一种方法包括:接收时钟信号,其中,所述时钟 信号的每个时钟循环启动存储器件中的写入操作或读取操作;确定功率小 憩周期;确定功率小憩周期小于时钟信号的时钟循环周期;以及响应于确 定所述功率小憩周期小于所述时钟循环周期而产生标头控制信号,其中, 所述标头控制信号关闭所述存储器件的组件的标头。

185.在上述方法中,确定功率小憩周期包括确定存储器件的位线对的预充 电与位线对上的电荷下降到预定水平以下之间的时间周期。

186.在上述方法中,还包括响应于确定功率小憩周期小于时钟循环周期而 产生标头控制信号,其中,标头控制信号关闭存储器件的输入/输出电路的 标头。

187.在上述方法中,确定功率小憩周期包括确定复制位线的预充电和复制 位线上的电荷下降到预定水平以下之间的时间周期。

188.在上述方法中,还包括响应于确定功率小憩周期小于时钟循环周期而 产生标头控制信号,其中,标头控制信号关闭存储器件的输入/输出电路标 头。

189.在上述方法中,还包括响应于确定功率小憩周期小于时钟循环周期而 产生标头控制信号,其中,标头控制信号关闭存储器件的字线驱动器电路 标头。

190.在上述方法中,复制位线连接到至少一个第一类型存储器单元和至少 一个第二类型存储器单元。

191.在上述方法中,至少一个第一类型的存储器单元被强制在q节点存储 位值0,在qbar节点存储位值1,并且其中,至少一个第二类型的存储器 单元被强制在q节点存储位值

1,在qbar节点存储位值1。

192.在上述方法中,确定功率小憩周期包括:确定第一功率小憩周期,第 一功率小憩周期包括在复制位线的预充电和复制位线上的电荷下降到低于 第一预定电平之间的第一时间周期;以及确定第二功率小憩周期,第二功 率小憩周期包括在复制位线的预充电和复制位线上的电荷下降到低于第二 预定水平之间的第二时间周期。

193.在上述方法中,还包括:响应于确定第一功率小憩周期小于时钟循环 周期而产生第一标头控制信号,其中,第一标头控制信号关闭存储器件的 输入/输出电路标头的第一部分;以及响应于确定第二功率小憩周期小于时 钟循环周期而产生标头控制信号,其中,第二标头控制信号关闭输入/输出 电路标头的第二部分。

194.在示例性实施例中,一种装置包括:存储器件;以及连接到存储器件 的处理单元,该处理单元可操作来:确定复制位线的预充电和复制位线上 的剩余电荷下降到预定水平以下之间的时间周期;确定复制位线的预充电 和复制位线上的剩余电荷下降到预定电平以下之间的时间周期小于时钟信 号的时钟循环周期,其中,时钟信号的每个时钟循环周期启动存储器件的 单元阵列中的写入操作或读取操作;以及响应于确定复制位线的预充电和 复制位线上的剩余电荷下降到预定电平以下之间的时间周期小于时钟循环 周期,关闭存储器件的组件的标头。

195.在上述装置中,处理单元可操作来确定复制位线的预充电和复制位线 上的剩余电荷下降到预定电平以下之间的时间周期小于时钟循环周期,处 理单元可操作来连续比较复制位线上的剩余电荷和预定电平。

196.在上述装置中,处理单元还是可操作的,以在复制位线的预充电和复 制位线上的剩余电荷下降到低于预定水平之间的所确定的时间周期小于时 钟循环周期时而产生标头控制信号,其中,标头控制信号关闭输入/输出电 路标头。

197.在上述装置中,用于确定功率小憩周期的处理单元可操作来:确定复 制位线的预充电和复制位线上的剩余电荷下降到低于第一预定电平之间的 第一时间周期;以及确定复制位线的预充电和复制位线上的剩余电荷下降 到低于第二预定电平之间的第二时间周期。

198.在上述装置中,处理单元还可操作来:响应于确定第一时间周期小于 时钟循环周期而产生第一标头控制信号,其中,第一功率标头信号关闭与 单元阵列相关联的输入/输出电路标头的第一部分;以及响应于确定第二时 间周期小于时钟循环周期而产生第二标头控制信号,其中,第二标头控制 信号关闭输入/输出电路标头的第二部分。

199.在上述装置中,复制电源电压端子连接到多个晶体管,其中,多个晶 体管可操作来从复制电源电压端子对预充电电压进行放电。

200.根据示例性实施例,存储器件包括:单元阵列,包括多个位单元;连 接到单元阵列的字线驱动器,其中,字线驱动器可操作来响应于用于读取 操作或写入操作的时钟信号来选择单元阵列的字线,并将所选择的字线充 电到预定电压;连接到单元阵列的i/o电路,i/o电路可操作用于从单元阵 列读取数据和向单元阵列写入数据;以及连接到单元阵列、字线驱动器和 i/o电路中的每一个的功率控制电路,其中功率控制电路可操作来选择性地 关闭以下至少一个的标头:单元阵列、字线驱动器和i/o电路。

201.在上述存储器件中,功率控制电路可操作来选择性地关闭以下至少一 个的标头:

单元阵列、字线驱动器和输入/输出电路,功率控制电路可操作 来:确定功率小憩周期;确定功率小憩周期小于时钟信号的时钟循环周期; 响应于确定功率小憩周期小于时钟循环周期而产生标头控制信号,其中, 标头控制信号关闭以下至少一个的标头:单元阵列、字线驱动器和输入/输 出电路。

202.在上述存储器件中,功率控制电路可操作来确定功率小憩周期包括功 率控制电路可操作来确定在对字线驱动器的复制电源电压端子预充电和复 制电源电压端子上的电荷下降到低于预定水平之间的时间周期。

203.在上述存储器件中,功率控制电路可操作来确定功率小憩周期包括功 率控制电路可操作来确定在对单元阵列的复制电源电压端子预充电和复制 电源电压端子上的电荷下降到低于预定水平之间的时间周期。

204.本发明论述了若干实施例,使得本领域普通技术人员可以更好地理解 本发明的各个实施例。本领域技术人员应该理解,可以很容易地使用本发 明作为基础来设计或更改其他用于达到与这里所介绍实施例相同的目的和 /或实现相同优点的处理和结构。本领域技术人员还应该认识到,这样的等 效构造不脱离本发明的精神和范围,并且在不背离本发明的精神和范围的 情况下,其可以做出多种变化、替换以及改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1