根据存储器单元的大小生成改善的写入电压的存储器设备的制作方法

根据存储器单元的大小生成改善的写入电压的存储器设备

1.相关申请的交叉引用

2.本技术要求享有2020年8月12日在韩国知识产权局提交的韩国专利申请第10-2020-0101344号的优先权,该韩国专利申请的内容通过引用全文合并于此。

技术领域

3.一些示例实施例涉及半导体设备,更具体地,涉及包括磁隧道结元件的存储器设备和/或用于测试和操作该半导体设备的方法。

背景技术:

4.如今,正在使用各种类型的电子设备。由于期望高速低功率的电子设备,因此电子设备会需要满足以下至少一些的存储器设备:高可靠性、高速度和低功耗。为了满足这些期望,已经提出了磁性存储器元件作为存储器设备的存储元件。因为磁性存储器元件以高速操作并且是非易失性的,所以磁性存储器元件作为下一代半导体存储器元件受到关注。

5.一般,磁性存储器元件可以包括磁隧道结(mtj),例如mtj元件。mtj元件可以包括两种磁性材料和插置在其间的绝缘层。mtj元件的电阻值可以取决于这两种磁性材料的磁化方向而变化。例如,当这两种磁性材料的磁化方向彼此反平行时,mtj元件可以具有大的电阻值,当这两种磁性材料的磁化方向彼此平行时,mtj元件可以具有较小的电阻值。可以通过使用电阻值之间的差异来写入或读取数据。

6.同时,关于磁性存储器元件所期望的可靠性和/或耐久性,当通过使用过大幅度的电压和/或电流对存储器设备进行写入时,存储器设备的耐久性可能是有问题的,当通过使用不足幅度的电压和/或电流对存储器设备进行写入时,存储器设备的可行性可能是有问题的。特别地,因为写入电压和/或电流的值在测试(例如,晶片测试)过程期间由存储器供应商/供货方存储在存储器设备中,所以如果一旦确定,则写入电压和/或电流的值会对存储器设备的性能有很大影响。

技术实现要素:

7.一些示例实施例提供了能够通过少量(例如,最少)次数的写入操作来确定改善的(例如,最优的)参考电阻器的值以及基于由此确定的参考电阻器的值来确定改善的(例如,最优的)写入电压的值的设备和/或方法。

8.根据一些示例实施例,一种存储器设备包括:存储器单元阵列,包括第一区域和第二区域,第二区域配置为存储写入电压的值,写入电压基于用于确定被编程的存储器单元处于平行状态还是反平行状态的参考电阻器的值;电压发生器,配置为基于写入电压的值来生成代码值;以及写入驱动器,配置为基于代码值来驱动写入电流,写入电流是用于将数据存储在第一区域中的电流。

9.根据一些示例实施例,一种存储器设备的操作方法包括:将存储器设备写入为第一状态;通过使用具有不同值的第一多个电阻器对被编程为第一状态的存储器设备的故障

比特计数,第一多个电阻器对应于多个参考电阻器中的每个;将存储器设备写入为第二状态;通过使用第一多个电阻器对被编程为第二状态的存储器设备的故障比特计数;基于(a)与第一状态相关联的计数结果和(b)与第二状态相关联的计数结果从第一多个电阻器中选择所选择的参考电阻器;以及基于所选择的参考电阻器的值为存储器设备确定写入电压的值。

10.根据一些示例实施例,一种存储器设备包括:存储器单元阵列,包括第一区域和第二区域,第二区域配置为存储参考电阻器的值和写入电压的值,写入电压的值基于参考电阻器的值来确定,参考电阻器的值基于以下来确定:(a)对于多个电阻值中的每个电阻值、对被编程为第一状态的第一区域的故障比特数量计数的第一结果,以及(b)对于所述多个电阻值中的每个电阻值、对被编程为第二状态的第一区域的故障比特数量计数的第二结果;列解码器,配置为选择与存储器单元连接的位线,存储器单元选自第一区域的存储器单元;行解码器,配置为驱动与所选择的存储器单元连接的字线;电压发生器,配置为基于写入电压的值生成代码值;以及写入驱动器,配置为驱动写入电流并通过所选择的位线将驱动的写入电流提供给所选择的存储器单元,写入电流是用于将数据存储在所选择的存储器单元中的电流,写入电流基于代码值。

附图说明

11.示例实施例的以上及其他目的和特征将通过参照附图详细描述其实施例而变得明显。

12.图1示出其中集成根据发明构思的一些示例实施例的存储器设备的基板。

13.图2示出了图1的存储器设备的配置。

14.图3是示出图2的存储器单元阵列的配置的电路图。

15.图4是示出图2的存储器单元阵列的配置的电路图

16.图5和图6示出了图3的存储器单元的配置。

17.图7是示出与图4的存储器单元相关联的配置的概念图。

18.图8示出了与图5或图6的存储器单元的写入状态相关联的曲线图。

19.图9概念性地示出了根据发明构思的一些示例实施例、如何为存储器设备确定最优参考电阻器的值。

20.图10概念性地示出了在针对存储器设备的测试操作中确定的最优参考电阻器的值和与其相对应的最优写入电压的值之间的关系。

21.图11概念性地示出了根据发明构思的一些示例实施例、如何测试存储器设备。

22.图12概念性地示出了根据发明构思的一些示例实施例、如何对存储器设备执行测试操作。

23.图13概念性地示出了根据发明构思的一些示例实施例、如何测试存储器设备。

24.图14示出了图11的驱动器的配置。

25.图15和图16示出了基于从图14的电压发生器输出的代码值而操作的驱动器的操作。

26.图17是示出根据发明构思的一些示例实施例的存储器设备的测试方法的流程图。

27.图18示出了根据发明构思的一些示例实施例的测试系统。

具体实施例

28.下面,可以以本领域普通技术人员可以容易地实现一些示例实施例的程度详细且清楚地描述发明构思的一些示例实施例。

29.在详细描述中参照术语“单元”、“模块”、“块”、“电路”、“~器”或“~件”、“表”、“设备”、“区域”等描述的一些组件和/或附图所示的功能块可以用软件、硬件或其组合来实现。例如,软件可以是或包括机器代码、固件、嵌入式代码或应用软件,并且可以以暂时的或非暂时的方式存储。例如,硬件可以包括处理电路,诸如电气电路、电子电路、处理器、计算机、集成电路、集成电路核心、fpga、压力传感器、惯性传感器、微机电系统(mems)、无源元件或其组合。

30.图1示出了其中集成根据发明构思的一些示例实施例的存储器设备的基板1。基板1可以包括多个管芯或设备(诸如包括第一存储器设备c1和第二存储器设备c2的存储器设备)以及在存储器设备之间的划片槽区域3。存储器设备可以在第一方向d1和第二方向d2上二维地布置。每个存储器设备可以被划片槽区域3围绕。例如,划片槽区域3可以被限定在沿第一方向d1相邻的存储器设备之间以及在沿第二方向d2相邻的存储器设备之间。另外,尽管在图1中示出了一定数量的管芯,但是示例实施例不限于图1所示的数量,并且可以多于或少于图1所示的数量。此外,尽管管芯被示出为是正方形的,但是示例实施例不限于此,并且管芯的形状可以是另一种形状,诸如另一种矩形形状。

31.在一些示例实施例中,基板1可以是或包括诸如半导体晶片的半导体基板。基板1可以是或包括体硅基板、绝缘体上硅(soi)基板、锗基板、绝缘体上锗(goi)基板、硅锗基板和/或通过选择性外延生长(seg)形成的外延薄膜的基板。例如,基板1可以包括硅(si)、锗(ge)、硅锗(sige)、砷化镓(gaas)、砷化铟镓(ingaas)、砷化铝镓(algaas)或其混合物中的至少一种。基板1可以具有单晶结构。基板1可以被掺杂,例如可以被p型杂质轻掺杂;然而,示例实施例不限于此。此外,尽管基板1被示出为是圆形的,但是示例实施例不限于此。例如,基板1可以具有诸如平坦的边缘,和/或可以在圆的圆周上具有凹口位置。此外,基板1可以具有100mm、150mm、200mm、300mm或450mm的直径;然而,示例实施例不限于此。

32.在一些示例实施例中,第一存储器设备c1可以指示形成在相对靠近边缘的区域(诸如基板1的外围)中的存储器设备,第二存储器设备c2可以指示相对靠近基板1的中心形成的存储器设备。

33.同时,存储器设备的写入特性和/或参考电阻器特性可以变化,例如,可以取决于基板1上的在此形成存储器设备的位置而变化。例如,在形成于基板1上的存储器设备包括mram单元的情况下,mram单元的尺寸可以取决于存储器设备在基板1中的位置而变化。

34.例如,由于生产/制造工艺,相对靠近基板1的外围放置的第一存储器设备c1的mram单元的尺寸可以相对较小。相反,由于生产/制造工艺,相对靠近基板1的中心放置的第二存储器设备c2的mram单元的尺寸可以相对较大。根据发明构思的一些示例实施例,可以考虑到存储器设备在基板1中的相对位置来确定写入电压的电平,诸如用于存储器设备(或芯片)的改善的或最优的写入电压的电平。例如,可以基于基板1中存储器设备的径向位置和/或角位置和/或相邻设备的数量来确定写入电压的电平。因此,如下面更全面所述,可以提供具有改善的可靠性和耐久性的存储器设备。

35.图2示出了图1的存储器设备c1和c2的配置。在一些示例实施例中,图2的存储器设

备100可以是实现图1的存储器设备c1和c2的示例。存储器设备100可以包括存储器单元阵列110、行解码器120、列解码器130、写入驱动器140、感测电路150、源极线驱动器160、输入/输出电路170以及控制逻辑电路和电压发生器180。

36.存储器单元阵列110可以包括多个存储器单元,每个存储器单元配置为存储数据。例如,每个存储器单元可以包括可变电阻元件,并且存储在可变电阻元件中的数据的值可以基于可变电阻元件的电阻值来确定。例如,每个存储器单元可以包括mram(磁阻ram)单元、stt-mram(自旋转移矩mram)单元、pram(相变ram)单元、reram(电阻ram)单元等中的至少一个。在下面的说明书中,将在每个存储器单元包括mram单元的假设下给出描述;然而,示例实施例不限于此。

37.构成存储器单元阵列110/包括在存储器单元阵列110中的存储器单元可以与源极线sl、位线bl和字线wl连接。例如,沿行布置的存储器单元可以共同连接到与该行相对应的字线,沿列布置的存储器单元可以共同连接到与该列相对应的源极线和位线。

38.行解码器120可以选择(或驱动)与读取操作或写入操作所针对的存储器单元连接的字线wl。行解码器120可以基于行地址ra和行控制信号r_ctrl来驱动特定的字线wl。行解码器120可以向所选择的字线提供从控制逻辑电路和电压发生器180接收到的驱动电压。

39.列解码器130可以基于列地址ca和列控制信号c_ctrl来选择与读取操作或写入操作所针对的存储器单元连接的位线bl和/或源极线sl。

40.在写入操作中,写入驱动器140可以驱动写入电压和/或写入电流,以将写入数据存储在由行解码器120和列解码器130选择的存储器单元中。例如,在存储器设备100的写入操作中,写入驱动器140可以基于通过写入输入/输出线wio从输入/输出电路170提供的写入数据通过控制数据线dl的电压而将写入数据存储在所选择的存储器单元中。

41.同时,为了描述的方便和附图的简洁,示出了数据线dl,但是数据线dl可以被理解为对应于由列解码器130选择的位线bl和源极线sl。

42.在读取操作中,感测电路150可以感测通过数据线dl输出的信号,以确定存储在所选择的存储器单元中的数据的值。感测电路150可以通过数据线dl与列解码器130连接,并且可以通过读取输入/输出线rio与输入/输出电路170连接。感测电路150可以通过读取输入/输出线rio将感测到的读取数据输出到输入/输出电路170。

43.源极线驱动器160可以在控制逻辑电路和电压发生器180的控制下将源极线sl驱动至特定的电压电平。例如,可以从控制逻辑电路和电压发生器180向源极线驱动器160提供用于驱动源极线sl的电压。例如,从源极线驱动器160施加到源极线sl的电压的值可以在执行写入操作的情况下是可变,使得存储器单元具有大的电阻值(例如,反平行状态),或者在执行写入操作的情况下是可变的,使得存储器单元具有小的电阻值(例如,平行状态)。

44.同时,尽管未在图2中示出,但是存储器设备100还可以包括其他存储器,诸如熔丝阵列和/或反熔丝阵列。熔丝阵列可以沿着行和列布置,并且可以包括例如用激光熔断的熔丝。反熔丝阵列可以包括沿着行和列布置的反熔丝。例如,作为一次可编程(otp)存储器的熔丝阵列或反熔丝可以是非易失性的。关于存储器设备100的信息可以被写入反熔丝阵列中。例如,关于制造工艺的信息、特定批次和/或特定基板1、存储器设备100在基板1内的特定位置、关于存储器单元阵列110的故障地址的信息、关于储器设备100的内部电压(例如,写入电压和/或读取电压)的信息等可以被写入反熔丝阵列中。特别地,根据发明构思的一

些示例实施例,关于写入电压(诸如在存储器设备100的制造之后测试存储器设备100的过程中确定的最优写入电压)的值的信息可以被写入反熔丝阵列中。

45.图3是示出图2的存储器单元阵列110的配置的电路图。存储器单元阵列110a可以包括在行方向和列方向上布置的多个存储器单元。每个存储器单元可以包括磁隧道结(mtj)元件和单元晶体管ct。作为示例,每个存储器单元可以是1t1mtj存储器单元;然而,示例实施例不限于此。当每个存储器单元的mtj元件被写入为具有特定电阻值时,与该特定电阻值相对应的数据可以被存储在每个存储器单元中。在一些示例实施例中,所述多个存储器单元之中的由虚线框指示的存储器单元由“mc1”标记。

46.所述多个存储器单元可以与字线wl1至wlm、位线bl1至bln和源极线sl1至sln连接。在第一存储器单元mc1中,mtj元件的第一端可以与第一位线bl1连接或直接连接,mtj元件的第二端可以与单元晶体管ct的第一端连接或直接连接。mtj元件可以串联布置在单元晶体管ct和位线bl之间。单元晶体管ct的第二端可以与源极线sl1连接,单元晶体管ct的栅电极可以与第一字线wl1连接。

47.图4是示出图2的存储器单元阵列110的配置的电路图。存储器单元阵列110b可以包括在行方向和列方向上布置的多个存储器单元。每个存储器单元可以包括mtj元件和两个单元晶体管。例如,存储器单元可以是2t1mtj存储器单元。图4所示的一些示例实施例作为所述多个存储器单元之中的由虚线框指示的第一存储器单元mc1包括mtj元件、第一单元晶体管ct1和第二单元晶体管ct2。

48.第一存储器单元mc1可以具有其中两个单元晶体管ct1和ct2共享一个mtj元件的结构。在第一存储器单元mc1中,mtj元件的第一端可以与第一位线bl1联接例如直接串联连接,mtj元件的第二端可以第一和第二单元晶体管ct1和ct2的第一端连接例如直接串联连接。单元晶体管ct1和ct2的第二端可以连接或直接连接到第一源极线sl1。第一单元晶体管ct1的栅电极可以与第一字线wl1连接或直接连接,第二单元晶体管ct2的栅电极可以与第一子字线wl1'连接。单元晶体管ct1和ct2中的每个可以通过经由第一字线wl1或第一子字线wl1'提供的信号(或电压)而导通或关断。

49.示例实施例不限于图3和图4所示的那些,图3和图4的特征也不意味着是互斥的。例如,存储器设备100可以包括如参照图3描述的第一存储器单元阵列110以及如图4中描述的第二存储器单元阵列110b。

50.图5和图6示出了图3的存储器单元的配置。

51.参照图5和图6,mtj元件可以包括第一磁性层l1、第二磁性层l2以及插置在第一磁性层l1和第二磁性层l2之间的势垒层bl(或隧穿层)。势垒层bl可以由镁(mg)氧化物、钛(末端)氧化物、铝(al)氧化物、镁-锌(mg-zn)氧化物或镁-硼(mg-b)氧化物中的至少一种或其组合构成,或包括镁(mg)氧化物、钛(末端)氧化物、铝(al)氧化物、镁-锌(mg-zn)氧化物或镁-硼(mg-b)氧化物中的至少一种或其组合。第一磁性层l1和第二磁性层l2中的每个可以包括至少一个磁性层。

52.详细地,第一磁性层l1可以包括具有固定(例如,钉扎)在特定方向上的磁化方向的参考层(例如,钉扎层pl),第二磁性层l2可以包括具有可改变为与参考层的磁化方向平行或反平行的磁化方向的自由层fl。然而,图5和图6通过示例公开了第一磁性层l1包括参考层pl并且第二磁性层l2包括自由层fl的情况,但是示例实施例不限于此。例如,与图5和

图6所示的实施例不同,第一磁性层l1可以包括自由层,第二磁性层l2可以包括钉扎层。

53.在一些示例实施例中,如图5所示,磁化方向可以大体上平行于势垒层bl和第一磁性层l1的界面。在这种情况下,参考层pl和自由层fl中的每个可以由铁磁材料构成或包括铁磁材料,并且可以包括相同或不同的材料。例如,参考层pl还可以包括用于钉扎铁磁材料的磁化方向的反铁磁材料。

54.在一些示例实施例中,如图6所示,磁化方向可以大体上垂直于势垒层bl和第一磁性层l1的界面。在这种情况下,参考层pl和自由层fl中的每个可以由垂直磁性材料(例如,cofetb、cofegd或cofedy)、具有l10结构的垂直磁性材料、具有六方密堆积晶格结构的基于copt的材料以及垂直磁性结构中的至少一种或其组合构成,或包括垂直磁性材料(例如,cofetb、cofegd或cofedy)、具有l10结构的垂直磁性材料、具有六方密堆积晶格结构的基于copt的材料以及垂直磁性结构中的至少一种或其组合。具有l10结构的垂直磁性材料可以包括具有l10结构的fept、具有l10结构的fepd、具有l10结构的copd或具有l10结构的copt中的至少一种或其组合。垂直磁性结构可以包括交替且重复地堆叠的磁性层和非磁性层。例如,垂直磁性结构可以包括(co/pt)n、(cofe/pt)n、(cofe/pd)n、(co/pd)n、(co/ni)n、(coni/pt)n、(cocr/pt)n或(cocr/pd)n(其中n是堆叠的成对层的数量)中的至少一种或其组合。这里,参考层pl的厚度可以大于自由层fl的厚度,或者参考层pl的矫顽力可以大于自由层fl的矫顽力。

55.在一些示例实施例中,当相对高电平的电压被施加到位线bl1并且相对低电平的电压被施加到源极线sl1时,写入电流i1可以流动。在这种情况下,第二磁性层l2的磁化方向可以与第一磁性层l1的磁化方向相同,并且mtj元件可以具有低电阻值(即,平行状态)。

56.相反,当相对高电平的电压被施加到源极线sl1并且相对低电平的电压被施加到位线bl1时,写入电流i2可以流动。在这种情况下,第二磁性层l2的磁化方向可以与第一磁性层l1的磁化方向相反,并且mtj元件可以具有大的电阻值(即,反平行状态)。

57.在一些示例实施例中,在mtj元件处于平行状态的情况下,存储器单元mc可以被视为存储第一值(例如,逻辑“0”)的数据。相反,在mtj元件处于反平行状态的情况下,存储器单元mc可以被视为存储第二值(例如,逻辑“1”)的数据。

58.同时,在图5和图6仅示出了一个单元晶体管ct,但是图5和图6所示的组件也可以应用于图4的存储器单元。在这种情况下,单元晶体管ct1和ct2可以与mtj元件的一端连接。除了电流路径取决于单元晶体管ct1和ct2之中的导通的单元晶体管而改变以外,mtj元件的基本原理、操作等可以相同地应用于图4的存储器单元。

59.示例实施例不限于图5和图6所示的那些,图5和图6的特征也未必意味着是互斥的。例如,存储器设备100可以包括参照图5的第一存储器单元mc和如图6中描述的第二存储器单元mc。

60.图7是示出与图4的存储器单元相关联的配置的概念图。

61.单元晶体管ct可以包括主体基板111、栅电极112以及结113和114。结113可以形成在主体基板111上,并且可以与源极线sl1连接。结114可以形成在主体基板111上,并且可以通过mtj元件与位线bl1连接。栅电极112可以在结113和114之间形成在主体基板111上,并且可以与字线wl1连接。同时,图7的配置是示例性的。像参照图4描述的示例实施例那样,在两个单元晶体管共享一个mtj元件的情况下,可以采用图7所示的配置的修改版本。此外,尽

管图7示出了平面单元晶体管ct的情况,但是示例实施例不限于平面晶体管。

62.图8示出了与图5或图6的存储器单元的写入状态相关联的曲线图。

63.如以上参照图1所提及的,存储器设备的写入特性可以取决于基板1上的在此形成存储器设备的位置而变化。例如,与第一存储器设备c1相对应的电阻分布图可以不同于与第二存储器设备c2相对应的电阻分布图。例如,第一存储器设备c1具有的电阻值可以大体上小于第二存储器设备c2具有的电阻值。该差异的原因可以是,属于第一存储器设备c1的mram单元的尺寸大体上小于属于第二存储器设备c2的mram单元的尺寸。

64.首先,参照与第一存储器设备c1相对应的曲线图,可以通过第一参考电阻器rref1的值来区分被写入为平行状态的存储器单元的电阻分布rp1和被写入为反平行状态的存储器单元的电阻分布rap1。例如,第一参考电阻器rref1可以用作用于确定存储在mram单元中的数据值的参考。例如,具有比第一参考电阻器rref1小的电阻值的存储器单元可以被视为存储第一值,具有比第一参考电阻器rref1大的电阻值的存储器单元可以被视为存储第二值。

65.接下来,参照与第二存储器设备c2相对应的曲线图,可以通过第二参考电阻rref2的值来区分被写入为平行状态的存储器单元的电阻分布rp2和被写入为反平行状态的存储器单元的电阻分布rap2。例如,第二参考电阻器rref2可以用作用于确定存储在mram单元中的数据值的参考。例如,具有比第二参考电阻器rref2小的电阻值的存储器单元可以被视为存储第一值,具有比第二参考电阻器rref2大的电阻值的存储器单元可以被视为存储第二值。

66.根据以上内容,当相同的写入条件被施加到从相同基板1提供的存储器设备c1和c2时,在写入操作中可能发生错误。例如,假设在第二参考电阻器rref2施加到第一存储器设备c1的条件下执行写入操作,被写入为具有反平行状态rap1的电阻值的存储器单元(详细地,属于图8的区域“a”的存储器单元)可以被视为具有平行状态rp1,而不是预期的反平行状态。相反,假设在第一参考电阻器rref1施加到第二存储器设备c2的条件下执行写入操作,被写入为具有平行状态rp1的电阻值的存储器单元(详细地,属于图8的区域“b”的存储器单元)可以被认为具有反平行状态rap2,而不是预期的平行状态。例如,在相同的参考电阻器值施加到与同一基板1分离的所有存储器设备的情况下,可能发生非预期的写入错误。

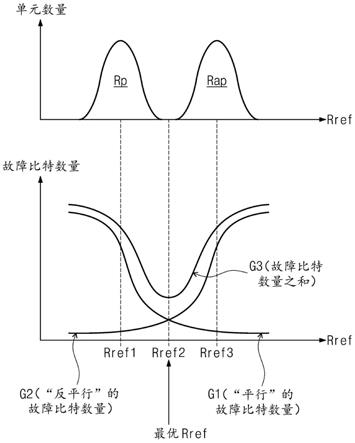

67.图9概念性地示出了根据发明构思的一些示例实施例如何为存储器设备确定改善的(例如,最优的)参考电阻器的值。

68.参照图9,在针对存储器设备的测试操作中,可以对存储器设备执行预写入操作。这里,预写入操作可以表示或对应于在存储器设备的测试过程中搜索用于区分平行状态和反平行状态的最优参考电阻器的写入操作,而不是存储数据的写入操作。例如,在预写入操作中施加到存储器设备的写入电压的电平可以大于产品装运之后在正常写入操作中使用的写入电压的电平。出于准确地执行测试操作的目的,这可以与防止或减少写入故障的可能性相关联。

69.首先,存储器设备的存储器单元的全部或子集可以通过使用测试设备(例如,自动测试机(ate))被写入为平行状态。测试设备可以测试基板1上的存储器设备;替代地,测试设备可以在存储器设备被切割和封装之后测试存储器设备。参照图9,“rp”指示被写入为平行状态的存储器单元的电阻值的分布。此后,可以通过使用测试设备对存储器设备的故障

比特的数量计数。例如,在通过使用相对较小值的参考电阻器(例如,第一参考电阻器rref1)对故障比特计数的情况下,具有比第一参考电阻器rref1大的电阻值的存储器单元可以被处理为写入故障。因此,故障比特的数量可以非常大。随着参考电阻器的值变大,存储器设备的故障比特的数量可以减少。由g1指示的曲线图显示出计数的故障比特的数量趋势。

70.存储器设备的存储器单元的全部或子集可以通过使用测试设备被写入为反平行状态。在图9中,“rap”指示被写入为反平行状态的存储器单元的电阻值的分布。此后,可以通过使用测试设备对存储器设备的故障比特的数量计数。例如,在通过使用相对较小值的参考电阻器(例如,第一参考电阻器rref1)对故障比特计数的情况下,故障比特的数量可以非常小。然而,随着参考电阻器的值变大(例如,增大到第二参考电阻器rref2的值和第三参考电阻器rref3的值之间的点),存储器设备的故障比特的数量可以增加。由g2指示的曲线图显示出计数的故障比特的数量趋势。

71.此后,测试设备可以通过使用计数的故障比特的数量来确定改善的或最优的参考电阻器的值。例如,测试设备可以将指示在平行(p)状态下测得的故障比特数量的曲线图g1和指示在反平行(ap)状态下测得的故障比特数量的曲线图g2求和。由g3指示的曲线图可以被绘制为求和结果。在由g3指示的曲线图中,与低数量(例如,最小数量或非常接近最小数量)的故障比特对应的参考电阻器(即,rref2)的值可以是存储器设备的最优参考电阻器的值。

72.此后,测试设备可以基于最佳参考电阻器(例如,rref2)的值为存储器设备决定改善的(例如,最优的)写入电压。可以从预先测得的mram单元的尺寸的趋势、根据mram单元的尺寸的参考电阻器值、以及根据参考电阻器值的写入电压值得出写入电压值。

73.在一些示例实施例中,改善的/最优的参考电阻器的值相对较小(例如,rref1)的情况可以对应于或指示存储器设备的mram单元的尺寸相对较大,这可以指示需要相对较大的写入电压值。相反,改善的/最优的参考电阻器的值相对较大(例如,rref3)的情况可以对应于或指示存储器设备的mram单元的尺寸相对较小,这可以意味着需要相对较小的写入电压值。

74.假设以上互操作应用于图1的第一存储器设备c1和第二存储器设备c2,可以得出第一存储器设备c1的改善的/最优的参考电阻器的值相对较大(例如,rref3),因此在第一存储器设备c1的写入操作中使用或需要相对较小的写入电压。如在以上描述中,可以得出第二存储器设备c2的改善的/最优的参考电阻器的值相对较小(例如,rref1),因此在第二存储器设备c2的写入操作中使用或需要相对较大的写入电压。

75.最后,测试设备可以将测得的参考电阻器值和与之相对应的写入电压值存储在存储器设备中。在存储器设备由终端用户使用之后,可以在正常写入操作中使用存储在存储器设备中的改善的/最优的写入电压的值。根据一些示例实施例,可以通过对存储器设备仅执行两次预写入操作来确定改善的/最优的参考电阻器的值和与之相对应的写入电压的值,因此,可以减少执行用于决定写入电压值的测试操作所必要的时间和/或成本。替代地或附加地,由于在产品装运之后取决于基板1上的在此形成存储器设备的位置来选择改善的/最优的写入电压(或电流)的值,因此可以改善存储器设备在写入操作中的可靠性,和/或可以改善存储器设备的耐久性。

76.图10概念性地示出了在针对存储器设备的测试操作中确定的改善的/最优的参考电阻器的值和与之相对应的改善的/最优的写入电压的值之间的关系。

77.在一些示例实施例中,存储器设备的参考电阻器的值可以与存储器设备的对应于该参考电阻器值的改善的/最优的写入电压(或电流)的值成反比。然而,存储器设备的参考电阻值可能不与存储器设备的最佳写入电压的值精确地成反比。应理解,写入电压的值可以随着参考电阻器的值增大而减小。

78.图10的图概念性地显示出相对较大值的第一参考电阻器rref1对应于相对靠近图1的基板1的外围形成的第一存储器设备c1,并且与之相对应的改善的/最优的写入电压的值是相对较小的“v1”。原因是由于第一存储器设备c1的mram单元的尺寸相对较小的尺寸而需要相对较小值的写入电压。

79.相反,图10的图概念地显示出相对较小值的第二参考电阻器rref2对应于相对靠近图1的基板1的中心形成的第二存储器设备c2,并且与之相对应的改善的/最优的写入电压的值是相对较大的“v2”。原因是由于第二存储器设备c2的mram单元的相对较大的尺寸而需要相对较大值的写入电压。

80.同时,可以以表格的形式来管理存储器设备的改善的/最佳的参考电阻器的值和写入电压的值之间的关系。在一些示例实施例中,参考电阻器的值和写入电压(或电流)的值可以由4比特表示,但是示例实施例不限于此。在参考电阻器的值由4比特表示的情况下,对于针对平行状态的故障比特计数操作和针对反平行状态的故障比特计数操作中的每个,参照图9描述的故障比特计数操作可以被执行多达16次或更少。例如,写入电压(或电流)可以在与“1111”相对应的第一值和与“0000”相对应的第二值之间是可变的。

81.在测试存储器设备的过程中,可以将改善的/最优的参考电阻器的值(例如,“1001”)和与之相对应的写入电压的值(例如,“0110”)存储在存储器设备中。替代地或附加地,图10所示的表可以被存储在存储器设备中。在这种情况下,当存储器设备由终端用户使用时,可以在写入操作中指出改善的/最优的参考电阻器的值(例如“1001”)和与该存储器设备相对应的写入电压的值(例如“0110”)。例如,可以将改善的/最优的参考电阻器的值、与之相对应的写入电压的值和/或表存储在存储器设备的反熔丝阵列等中,但是本公开不限于此。

82.图11概念性地示出了根据发明构思的一些示例实施例、如何测试存储器设备。详细地,图11可以与存储器设备的在测试存储器设备的过程中执行的预写入操作相关联。

83.存储器单元阵列110可以包括多个存储器单元,每个存储器单元包括mtj元件和单元晶体管。写入驱动器140、源极线驱动器160和电压发生器182与存储器单元阵列110一起被示出。例如,电压发生器182可以是图2的控制逻辑电路和电压发生器180的一部分。为了描述的方便和附图的简洁,仅示出了与第一位线bl1和第一源极线sl1连接的“n”个存储器单元。

84.首先,电压发生器182可以配置为产生用于将要对存储器单元阵列110执行的预写入操作的电压。这里,表述“用于预写入操作的电压”可以对应于其电平高到在存储器单元处不发生写入故障的程度的电压。例如,用于预写入操作的电压的值可以大于在能够由终端用户执行的正常(或普通)写入操作中使用的写入电压的值,但是示例实施例不限于此。例如,用于执行预写入操作的电压的值可以由用于导通/关断构成写入驱动器140的各个元

件(例如,各个晶体管)的代码值cv来实现。

85.写入驱动器140可以基于代码值cv针对存储器单元执行预写入操作。预写入操作可以包括将存储器单元写入为平行状态以及将存储器单元写入为反平行状态。例如,写入驱动器140可以输出与代码值cv相对应的写入电流“i”。例如,写入驱动器140可以包括配置为出于对存储器单元执行预写入操作的目的而生成写入电流“i”的驱动器电路。

86.图12概念性地示出了根据发明构思的一些示例实施例、如何对存储器设备执行测试操作。详细地,图12的实施例可以与在测试存储器设备的过程中执行的确定改善的/最优的参考电阻器的值相关联。例如,可以在参照图11描述的测试操作之后执行将参照图12描述的测试操作,并且为了描述的方便,假设图12的存储器单元被写入为平行状态。

87.存储器单元阵列110可以包括与多条位线和多条源极线连接的多个存储器单元。每个存储器单元可以包括mtj元件和至少一个单元晶体管。为了附图的简洁,仅示出了与第一位线bl1和第一源极线sl1连接的存储器单元。第一位线bl1可以与第一节点n1连接,第一源极线sl1可以与源极线驱动器160连接。

88.参考电阻器rref可以与读取存储在存储器单元阵列110的存储器单元中的数据所使用/所必要的参考电压vref相关联。例如,在生产/制造存储器设备100的过程中,可以用形成晶体管(例如,单元晶体管ct)的栅电极中使用的栅极多晶硅(例如,蛇形(serpentine)多晶硅)来实现参考电阻器rref。在这种情况下,可以通过调节所实现的栅极多晶硅的长度、掺杂剂浓度等容易地改变参考电阻器rref的值,因此,如参照图9和图10所述,可以对根据参考电阻器rref的值的故障比特计数。

89.感测电路150可以配置为读取存储在与第一位线bl1连接的存储器单元中的数据。例如,感测电路150可以包括生成第一读取电流ird1和第二读取电流ird2的电流源、以及感测放大器152。

90.第一读取电流ird1可以用于感测第一位线bl1的所选择的存储器单元中的电压降。例如,第一读取电流ird1可以被输入到与第一位线bl1连接/连接到第一位线bl1的所选择的存储器单元的字线(即,wl2)。结果,在与第二字线wl2连接/连接到第二字线wl2的mtj元件处会发生电压降。

91.第二读取电流ird2可以用于确定通过参考位线rref bl与第二节点n2连接的参考电阻器rref中的电压降。例如,第二读取电流ird2可以流过参考电阻器rref,因此,在参考电阻器rref处会发生电压降。图12中示出了参考电流iref以显示出流过参考电阻器rref的电流,但是参考电流iref可以被视为与第二读取电流ird2基本相同。

92.感测放大器152可以感测第一节点n1和第二节点n2之间的电压差,并且可以放大感测到的电压差。例如,第一节点n1的电压电平可以不同于第二节点n2的电压电平。放大的电压差可以作为输出电压vout输出,并且可以用于确定从存储器单元读取的数据。感测放大器152可以用交叉耦合的反相器来实现;然而,示例实施例不限于此。

93.在一些示例实施例中,在测试存储器设备100的过程中,每当参考电阻器rref的值改变时,就可以对存储器单元阵列110的至少一部分中的存储器单元的故障比特数量计数。例如,在存储器单元阵列110的至少一部分存储器单元被写入为具有平行状态的情况下,根据参考电阻器rref的值的故障比特数量可以具有与图9的曲线图g1相对应的趋势;在存储器单元阵列110的存储器单元被写入为具有反平行状态的情况下,根据参考电阻器rref的

值的故障比特数量可以具有与图9的曲线图g2相对应的趋势。测试设备可以基于图9的曲线图g1和g2获得(或绘制)曲线图g3和/或可以确定与低数量(例如,最小数量或非常接近最小数量)的故障比特相对应的改善的/最优的参考电阻器的值以及与之相对应的改善的/最优的写入电压的值。

94.图13概念性地示出了根据发明构思的一些示例实施例、如何测试存储器设备。详细地,图13的实施例可以与在测试存储器设备的过程中执行的确定改善的(例如,最优的)参考电阻器的值相关联。图13的实施例大体上类似于图12的实施例。

95.存储器单元阵列可以包括第一区域110a和第二区域110b。存储器单元阵列可以包括多个存储器单元,每个存储器单元包括mtj元件和单元晶体管。

96.作为其中存储数据的区域的第一区域110a可以包括与多条位线和多条源极线连接的存储器单元。然而,为了附图的简洁,第一区域110a的存储器单元被示出为与第一位线bl1和第一源极线sl1连接。

97.第二区域110b可以包括用于生成参考电压vref/生成参考电压vref所必要的组件或元件,该参考电压vref用于读取存储在第一区域110a的存储器单元中的数据。例如,第二区域110b可以包括与参考位线ref bl和参考源极线ref sl连接的多个存储器单元以及电阻“r”。

98.在一些示例实施例中,第一区域110a的存储器单元和第二区域110b的存储器单元可以基本相同,例如在结构和电特性上相同。参考位线ref bl可以在结构上与第一位线bl1基本相同,参考源极线ref sl可以在结构上与第一源极线sl1基本相同。即,可以通过相同的制造工艺来提供第一区域110a和第二区域110b。然而,取决于示例实施例,可以提供或可以不提供电阻“r”。

99.感测电路150可以配置为读取存储在与第一位线bl1连接的存储器单元中的数据。感测电路150可以包括生成第一读取电流ird1和第二读取电流ird2的至少一个电流源、以及感测放大器152。感测电路150可以通过使用第一读取电流ird1来确定第一位线bl1的所选择的存储器单元中的电压降。

100.替代地或附加地,感测电路150可以通过使用第二读取电流ird2来确定与参考位线ref bl连接的存储器单元中的电压降。例如,第二读取电流ird2可以通过参考位线ref bl输入到在单元晶体管ct导通时被选择的存储器单元。因此,第二区域110b中的电压降可以被视为参考电阻器rref引起的电压降。

101.根据一些示例实施例,可能不需要或不期望在如参照图12的实施例所述那样替换参考电阻器rref的同时针对每个参考电阻器在第一区域110a中执行故障比特计数。代替地,通过适当地控制第二区域110b的单元晶体管ct的开/关,可以在改变参考电阻器rref的值的同时对第一区域110a中的故障比特计数。

102.替代地或附加地,即使仅一条参考位线ref bl在图13中被示出为与第二节点n2连接,但是更多的参考位线可以与第二节点n2连接。例如,连接到具有与图13所示的第二区域110b相同结构的存储器单元的参考位线还可以与第二节点n2连接。

103.在如上参照图12和图13描述的一些示例实施例中,可以使用改善的/最优的参考电阻器的值来确定改善的/最优的写入电压的值。可以将由此确定的参考电阻器的值和写入电压的值存储在存储器设备100的特定区域(例如,反熔丝阵列或其他otp区域)中。

104.图14示出了图11的驱动器的配置。详细地,图14的一些示例实施例可以与取决于在测试存储器设备的过程中确定的改善的/最优的写入电压的值来执行写入操作相关联。

105.驱动器140可以包括(pmos)晶体管pu1至pup和(nmos)晶体管pd1至pdp。晶体管pu1至pup可以连接在第一位线bl1和第一电源电压vdd之间。晶体管pd1至pdp可以连接在第一位线bl1和第二电源电压vss之间。例如,第一电源电压vdd的电平可以高于第二电源电压vss的电平,源极线sl1的电压的电平可以在第一电源电压vdd的电平和第二电源电压vdd的电平之间。例如,可以从电压发生器182或者可以从单独的电压发生器提供电源电压vdd和vss。

106.驱动器140可以通过由列解码器130(参照图2)选择的第一位线bl1与存储器单元mc连接。在一些示例实施例中,可以为与第一位线bl1不同的各个位线分别提供与驱动器140相同地实现的附加驱动器。然而,为了附图的简洁,将省略与附加驱动器相关联的描述。

107.电压发生器182可以生成用于控制驱动器140的代码值cv。代码值cv可以基于其中定义了存储器设备的改善的/最优的参考电阻器的值和改善的/最优的写入电压的值的映射表(例如,参照图10描述的表)。代码值cv可以包括第一代码值cvu和第二代码值cvd。第一代码值cvu和第二代码值cvd可以用单个代码值cv来实现,或者可以彼此独立地提供。实施例在图14中被示出为第一代码值cvu和第二代码值cvd被提供为单独的代码值。

108.晶体管pu1至pup中的每个可以基于第一代码值cvu而导通或关断。例如,在晶体管pu1至pup中的每个是p沟道金属氧化物半导体场效应晶体管(mosfet)的情况下,晶体管pu1至pup中的每个可以响应于逻辑“0”的比特而导通。并且可以响应于逻辑“1”的比特而关断。

109.晶体管pdl至pdp中的每个可以基于第二代码值cvd而导通或关断。例如,在晶体管pd1至pdp中的每个是n沟道金属氧化物半导体场效应晶体管(mosfet)的情况下,晶体管pd1至pdp中的每个可以响应于逻辑“1”的比特而导通。并且可以响应于逻辑“0”的比特而关断。然而,图14的驱动器140的配置可以是一配置,并且可以理解的是,可以将驱动器140的配置各种各样地修改或改变为不同于图14的配置。

110.导通的晶体管可以为写入电流i1/i2提供电流路径。因此,晶体管pu1至pup和晶体管pd1至pdp可以基于第一代码值cvu和第二代码值cvd来驱动写入电流i1/i2。

111.例如,在晶体管pu1至pup中的一个或更多个导通并且晶体管pd1至pdp关断的情况下,第一位线bl1的电压可以被上拉至第一电源电压vdd。在这种情况下,可以从第一位线bl1向第一源极线sl1提供写入电流i1。

112.相反,在晶体管pu1至pup关断并且晶体管pd1至pdp中的一个或更多个导通的情况下,第一位线bl1的电压可以被下拉至第二电源电压vss。在这种情况下,可以从第一源极线sl1向第二位线bl1提供写入电流i2。存储器单元mc的数据状态可以取决于写入电流i1/i2。

113.晶体管pu1至pup之中将要导通的晶体管的数量可以取决于第一代码值cvu的比特而变化。晶体管pd1至pdp之中的将要导通的晶体管的数量可以取决于第二代码值cvd的比特而变化。写入电流i1/i2的强度可以取决于导通的晶体管的数量而变化。

114.随着导通的晶体管的数量增加,写入电流i1/i2的强度可以增大。写入电流i1/i2的强度可以对应于由导通的晶体管驱动的电流的强度之和。因此,可以基于第一代码值cvu和第二代码值cvd来调节写入电流i1/i2的强度。

115.根据以上描述,写入驱动器140可以配置为驱动具有不同幅度/强度的写入电流。

流过存储器单元mc的写入电流i1/i2的值可以被调节为具有由写入驱动器140提供的不同强度之一。

116.图15和图16示出了基于从图14的电压发生器182输出的代码值cv操作的驱动器140的操作。

117.参照图15和图16,驱动器140可以包括晶体管pu1至pu4和晶体管pd1至pd4。例如,晶体管pu1和pd1中的每个可以具有用于驱动40μa的电流的沟道宽度,晶体管pu2至pu4和pd2至pd4中的每个可以具有用于驱动10μa的电流的沟道宽度。

118.在一些示例实施例中,图15可以与驱动器140将第一位线bl1的电压上拉至第一电源电压vdd的情况相关联。在图15的实施例中,可以从电压发生器182(参照图14)向驱动器140提供与第一代码值cvu“0011”相对应的电压和与第二代码值cvd“0000”相对应的电压。

119.参照图15,晶体管pd1至pd4可以响应于第二代码值cvd而关断。晶体管pu1和pu2可以响应于第一代码值cvu的比特之中的具有逻辑“0”的比特而导通,晶体管pu3和pu4可以响应于第一代码值cvu的比特之中的具有逻辑“1”的比特而关断。因此,可以通过导通的晶体管pu1和pu2来驱动50μa的写入电流i1。

120.在一些示例实施例中,图16可以与驱动器140将第一位线bl1的电压下拉至第二电源电压vss的情况相关联。在图16的实施例中,可以从电压发生器182向驱动器140提供第一代码值cvu“1111”的和第二代码值cvd“1100”。

121.参照图16,晶体管pu1至pu4可以响应于第一代码值cvu而关断。晶体管pd1和pd2可以响应于第二代码值cvd的比特之中的具有逻辑“1”的比特而导通,晶体管pd3和pd4可以响应于第二代码值cvd的比特之中的具有逻辑“0”的比特而关断。因此,可以通过导通的晶体管pd1和pd2来驱动50μa的写入电流i2。

122.在一些示例实施例中,图15的示例实施例可以与在存储器单元mc中存储逻辑“0”的数据的情况相关联,图16的实施例可以与在存储器单元mc中存储逻辑“1”的数据的情况相关联。例如,为了将图10所示的映射表的代码值提供给构成驱动器140的晶体管pu1至pu4和pd1至pd4,电压发生器182可以包括诸如开关和多路复用器的组件。

123.如参照图14至图16所述,通过经由使用在测试存储器设备的过程中确定的改善的/最优的写入电压(或电流)来执行写入操作,可以减少故障比特的发生。结果,可以改善存储器设备的可靠性。替代地或附加地,通过防止或减少经由使用过大的写入电压(或电流)执行写入操作的可能性,可以改善存储器设备的耐久性。

124.图17是示出根据发明构思的一些示例实施例的存储器设备的测试方法的流程图。

125.在操作s105中,可以对存储器设备执行写入操作。例如,测试设备可以将构成存储器设备的存储器单元写入为具有图9的平行状态的电阻分布rp。

126.在操作s110中,可以对存储器设备执行故障比特计数。在一些示例实施例中,测试设备可以在改变参考电阻器rref的值的同时对存储器单元的故障比特数量计数。例如,参考电阻器rref的初始值为“1”的表述可以仅表示将要在测试操作中使用的参考电阻器的顺序,并且可以不与详细的参考电阻器值相关联。例如,首先被选择的参考电阻器rref的值可以不指示将要用于执行测试操作的参考电阻器值的低值(例如,最小值或非常接近最小值),并且可以是由存储器生产商/供应商选择的任何值。

127.此后,测试设备可以在改变参考电阻器rref的值的同时对存储器单元的故障比特

数量计数(即,可以重复地执行操作s110、操作s115和操作s120)。当完成使用为测试操作提供的所有参考电阻器的故障比特计数操作时,与平行状态相关联的故障比特计数操作可以结束。

128.在操作s125中,可以对存储器设备执行写入操作。例如,测试设备可以将构成存储器设备的存储器单元写入为具有图9的反平行状态的电阻分布rap。

129.在操作s130中,可以对存储器设备执行故障比特计数。在一些示例实施例中,测试设备可以在改变参考电阻器rref的值的同时对存储器单元的故障比特数量计数。如在与平行状态相关联的故障比特计数中那样,在故障比特计数中选择的参考电阻器rref的值可以从提供的参考电阻器值中随机选择,而不管参考电阻器值的顺序如何。

130.测试设备可以在改变参考电阻器rref的值的同时对存储器单元的故障比特数量计数(即,可以重复地执行操作s130、操作s135和操作s140);当完成使用为测试操作提供的所有参考电阻器值的故障比特计数操作时,与反平行状态相关联的故障比特计数操作可以结束。

131.在操作s145中,可以基于故障比特计数结果来确定改善的/最优的参考电阻器的值。例如,对于每个参考电阻器值,测试设备可以将在平行状态下计数的故障比特数量和在反平行状态下计数的故障比特数量相加,并且可以选择与低的相加结果(例如,最小相加结果或非常接近最小相加结果(例如,最小相加结果的+/-10%))作为改善的/最优的参考电阻器的值。

132.在操作s150中,可以确定与最佳参考电阻器的值相对应的改善的或最优的写入电压(或电流)的值。在一些示例实施例中,参考电阻器的值和写入电压的值可以具有像图10所示的图那样的趋势(例如,反比例关系或倒数关系)。因此,可以需要相对较小的写入电压(或电流)对相对靠近基板1(参照图1)的外围形成的存储器设备(例如,图1的c1)进行写入。相反,可以需要相对较大的写入电压(或电流)对相对靠近基板1的中心形成的存储器设备(例如,图1的c2)进行写入。

133.在操作s155中,可以将最佳写入电压(或电流)的值存储在存储器设备中。在一些示例实施例中,最佳参考电阻器的值和最佳写入电压(或电流)的值可以存储在存储器设备中。替代地或附加地,如图10所示,可以将其中定义了与每个参考电阻器的值相对应的写入电压的值的映射表存储在存储器设备中。在这种情况下,可以在写入操作中指出与提供给终端用户的存储器设备相对应的参考电阻器的值和写入电压的值。在一些示例实施例中,最佳参考电阻器的值、与之相对应的写入电压的值和/或表可以存储在存储器设备的反熔丝阵列等中,但是本公开不限于此。

134.图18示出了根据发明构思的一些示例实施例的测试系统。测试系统1000可以包括存储器设备1100和测试设备1200。

135.存储器设备1100包括存储器单元阵列1110。在一些示例实施例中,存储器设备1100可以是参照图1至图17描述的存储器设备100的实现示例。存储器单元阵列1110可以包括第一区域1112和第二区域1114。例如,作为用户区域的第一区域1112可以是其中存储用户所打算的数据的区域。作为供应商区域的第二区域1114可以是其中存储由存储器生产者/供应商所打算的数据的区域。例如,参照图1至图17描述的改善的/最优的参考电阻器的值和改善的/最优的写入电压的值可以存储在第二区域1114中。

136.测试设备1200可以对存储器设备1100执行各种测试操作。为此,测试设备1200可以将命令cmd发送到存储器设备1100。

137.在一些示例实施例中,命令cmd可以包括用于将存储器单元阵列1110的第一区域1112写入为特定写入状态(例如,平行状态或反平行状态)的命令。测试设备1200可以与发送命令cmd一起发送用于将第一区域1112写入为平行状态或反平行状态的虚设写入数据data_dw。

138.在一些示例实施例中,命令cmd可以指示用于针对特定的写入状态(例如,平行状态或反平行状态)对每个参考电阻器的故障比特数量计数的读取操作。可以从存储器设备1100接收读取数据data_rd作为读取结果。

139.在一些示例实施例中,测试设备1200可以基于从存储器设备1100接收到的读取数据data_rd对每个参考电阻器的故障比特数量计数,可以基于计数结果来确定改善的/最佳的参考电阻器rref的值,并且可以基于最佳参考电阻器rref的值来确定改善的/最优的写入电压(或电流)的值。

140.在一些示例实施例中,测试设备1200可以将改善的/最佳的参考电阻器rref的值和改善的/最佳的写入电压(或电流)的值以表格的形式存储在存储器设备1100中。例如,该表可以存储在存储器单元阵列110的第二区域1114中。例如,第二区域1114可以包括反熔丝单元阵列。

141.同时,一些示例实施例被描述为以存储器设备(例如,半导体芯片)为单位执行预写入操作、故障比特计数操作、确定改善的/最优的参考电阻器的值的操作、以及确定改善的/最优的写入电压的值的操作。然而,在一些示例实施例中,可以取决于不同的参考而不是存储器设备(即,半导体芯片)单元来确定改善的/最优的写入电压的值。例如,在一个存储器设备中,因为存储器单元离基板1的中心的距离不同,所以可以将存储器单元分类为多个区域,可以针对每个区域来确定改善的/最优的写入电压的值。

142.根据一些示例实施例,可以通过对存储器设备仅执行(例如,分别与平行状态和反平行状态相关联的)两次预写入操作来确定存储器设备的改善的/最优的参考电阻器的值和改善的/最优的写入电压(或电流)的值。因此,可以减少确定改善的/最优的写入电压的值所必要的时间和/或成本。替代地或附加地,因为通过使用其值根据存储器设备的特性(例如,mram单元的尺寸)来确定/优化的写入电压(或电流)来执行编程操作,所以可以改善存储器设备的可靠性和耐久性。

143.根据一些示例实施例,有可能通过少量/最小次数的写入操作来确定改善的/最优的参考电阻器的值,并基于由此确定的电阻器的值来确定改善的/最优的写入电压的值。

144.在这种情况下,防止存储器设备被过大的电压(或电流)写入或降低存储器设备被过大的电压(或电流)写入的可能性,因此,存储器设备的耐久性得到改善。

145.替代地或附加地,防止存储器设备被不足的电压(或电流)写入或降低存储器设备被不足的电压(或电流)写入的可能性,因此,存储器设备的可靠性得到改善。

146.虽然一些示例实施例已经参照其实施例被描述,但是对本领域普通技术人员将明显的是,在不背离如所附权利要求中阐明的本公开的精神和范围的情况下,可以对其进行各种改变和修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1