半导体存储装置及其动作方法与流程

1.本发明涉及快闪存储器等半导体存储装置及其动作方法,特别涉及半导体存储装置于电源输入时的开机动作。

背景技术:

2.nand型快闪存储器为了储存用于设定读取、编程、抹除等动作电压、时序、内部电压等参数(以下将关于设定此类动作的信息,称为设定信息),而使用熔丝存储器。例如是在存储单元阵列内设有无法被使用者存取的熔丝存储器区域。快闪存储器在电源输入时,会读取储存于熔丝存储器的设定信息作为开机动作,并将设定信息写入到暂存器中(以下,将此类储存设定信息的暂存器,称为便利组态(cf)暂存器)。开机动作后,控制器可根据储存于cf暂存器的设定信息控制各种动作。

技术实现要素:

3.图1为说明将电源输入快闪存储器时的开机动作的图示。作为一示例,设定从外部供给的电源电压vcc为3.0v,内部电路的动作保证电压为2.7~3.3v,开机检测电平为2.2v。在电源输入后的时刻t1,电源电压vcc上升至开机检测电平,控制器回应开机检测,从熔丝存储器读取设定信息,并将读出的设定信息写入到cf暂存器中。之后,在时刻t2时,电源电压vcc上升到动作保证电压,于是可以开始通常动作。

4.在开机动作中,由于对熔丝存储器的读取是在电源电压上升至动作保证电压前就执行,因此在从熔丝存储器读取设定信息时,可能会因为是以较低的电压电平进行,使得对熔丝存储器的读取变得不稳定。若使用者侧的电力供给能力不足,对熔丝存储器的读取会因为电源电压的变动或杂讯而无法正确进行,进而使得写入至cf暂存器的设定信息发生错误。因此,为了提升可靠度,会判定熔丝存储器的读取是否正确完成,在没有正确完成的情况下,会重新进行熔丝存储器的读取。

5.图2为显示现有技术中的开机动作时的熔丝存储器的读取动作的流程图。电源电压vcc达到开机检测电平时,即检测到开机(s100),内部的控制器进行熔丝存储器的读取(s110)。熔丝存储器在特定的地址存储设定信息等特征数据,这些信息可以被读取。

6.控制器检查特征数据是否正确(s120)。举例而言,特征数据是如“aah”或“55h”的“0”与“1”的数据型态。若特征数据正确,控制器判定熔丝存储器的读取正确,将设定信息设置于cf暂存器中,以结束熔丝存储器的读取(s130)。

7.另一方面,若特征数据错误,控制器会确认对熔丝存储器的读取次数是否达到最大值(s140)。若否,则重新进行熔丝存储器的读取(s110)。若读取次数已达到最大值,控制器将设定信息写入到cf暂存器中,并结束熔丝存储器的读取(s150)。

8.当从熔丝存储器读出的特征数据并不正确时,代表在步骤s150结束的情况中,自熔丝存储器读出并写入到cf暂存器中的设定信息可能含有错误,使得在读取、编程、抹除等动作时使用错误的设定信息(例如施加异常的电压电平,或者在不适当的时序施加电压

等),而造成错误动作。进而,在解析错误动作的原因时,可能因为不知道设定信息为错误动作的原因,而在调查原因时花费大量的时间及资源。

9.本发明为解决这样的习知课题,目的为提供可以得知开机动作时设定信息的读取是否正确完成的半导体存储装置。更进一步地,本发明的目的为提供开机动作后,具备进行设定信息的重新读取的功能的半导体存储装置。

10.关于本发明的半导体存储装置,包括:存储单元阵列;存储装置,包括被配置以储存与动作的设定有关的设定信息的存储区域;控制器,在检测到电源电压为开机检测电平时,从存储装置读取设定信息,将读取到的设定信息载入到暂存器,且回应外部的指令,将被配置以识别设定信息的读取是否被正确完成的识别数据储存于可读取的暂存器。

11.关于本发明的半导体存储装置的动作方法,包括:将与动作的设定有关的设定信息预先存储于非易失性的存储区域;在开机动作时检测电源电压,且在检测到电源电压达到开机检测电平时,从存储区域读取设定信息,判定设定信息的读取是否正确完成,且在判定未正确完成读取的情况下,重新进行设定信息的读取;将从存储区域读取的设定信息载入到暂存器;及储存识别数据于可读取的暂存器,其中识别数据被配置以识别对设定信息的读取次数是否达到最大值。

附图说明

12.图1为说明快闪存储器的开机动作的示意图。

13.图2显示现有技术中的开机动作时的快闪存储器的读取动作的流程图。

14.图3显示关于本发明实施例的快闪存储器的构成的方块图。

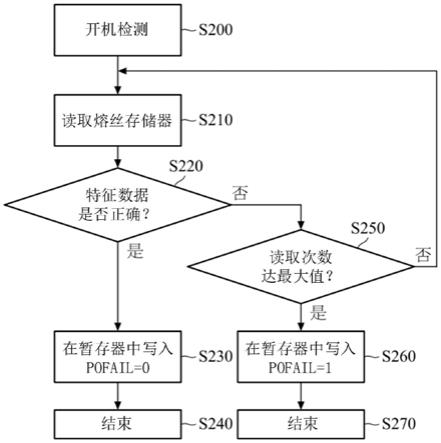

15.图4显示关于本发明实施例的开机动作时的快闪存储器的读取动作的流程图。

16.图5显示习知的快闪存储器的重设动作的流程图。

17.图6显示关于本发明第2实施例的快闪存储器的重设动作的流程图。

18.图7显示关于本发明第3实施例的快闪存储器的熔丝存储器的内部重设动作的流程图。

19.图8显示关于本发明第4实施例的快闪存储器的熔丝存储器的开机重试动作的流程图。

20.图9显示关于本发明第5实施例的快闪存储器的熔丝存储器的读取、编程或抹除动作的流程图。

21.附图标记说明:

22.100:快闪存储器

23.110:存储单元阵列

24.120:输入输出缓存

25.130:地址暂存器

26.140:控制器

27.150:字元线选择电路

28.160:页缓冲/感应电路

29.170:行选择电路

30.180:暂存器

31.190:电压检测部

32.200:内部电压产生电路

具体实施方式

33.为使本发明实施例的目的、技术方案和优点更加清楚明白,下面结合附图对本发明实施例做进一步详细说明。在此,本发明的示意性实施例及其说明用于解释本发明,但并不作为对本发明的限定。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互任意组合。

34.接着,针对关于本发明的半导体存储装置进行说明。虽然以nand型快闪存储器作为半导体存储装置的实施态样进行例示,但本发明不限于此。半导体存储装置也可以是具备在开机动作中将设定信息从非易失性存储器读取出来的架构的存储装置。

35.图3显示关于本发明实施例的nand型快闪存储器的构成的方块图。参照图3,快闪存储器100的构成包括:存储单元阵列110,由多个存储单元形成;输入输出缓存120,连接外部输入输出端子i/o;地址暂存器130,从输入输出缓存120接收地址数据;控制器140,从输入输出缓存120接收指令数据;字元线选择电路150,根据来自地址暂存器130的列地址ax,进行区块的选择以及字元线的选择等;页缓冲/感应电路160,保持被字元线选择电路选择的页的读取数据,或保持应被编程到被选择页的编程数据;行选择电路170,根据来自地址暂存器130的行地址信息ay,选择页缓冲/感应电路160的行等;暂存器180,例如为非易失性暂存器;电压检测部190,检测从外部供给的电源电压vcc是否到达开机检测电平,将该检测信号det提供给控制器140等;内部电压产生电路200,生成用以读取、编程以及抹除等所需要的各种电压(编程电压vpgm、读取电压vread、抹除电压vers、通过电压vpass等)。

36.存储单元阵列110,具有m个区块blk(0)、blk(1)、

…

、blk(m-1),一个区块由多个nand串列形成,一个nand串列中有多个存储单元串联连接。另外,存储单元阵列110中包括熔丝存储器,在没有被使用者使用的区域(或者无法被使用者存取的区域)储存用以设定快闪存储器的动作电压或时序等参数的设定信息。另外,熔丝存储器中除了储存这类的设定信息外,也会于特定地址储存特征数据。特征数据为开机动作时,用以验证熔丝存储器是否被正确读取的数据,在一实施例中,例如是“aah”或“55h”等数据。

37.控制器140除了从输入输出缓存120接收指令数据外,还会从熔丝存储器中接收上述的用以设定快闪存储器的动作电压或时序等参数的设定信息,并将该些设定信息写入到控制器140中的cf暂存器(未显示)中,以根据储存于cf暂存器的设定信息控制对快闪存储器执行的各种动作。

38.暂存器180储存显示快闪存储器100的各种状态的数据。在本实施例中,暂存器180的一部分中,储存用以识别开机动作时对熔丝存储器的读取是否正确完成的识别数据pofail。在一实施例中,控制器140从外部接收用以读取暂存器180的指令,读取储存于暂存器180的识别数据,且将读取出来的识别数据输出到外部。

39.电压检测部190检测电源电压vcc是否达到开机检测电平。举例而言,电源电压vcc为3.0v,电源输入后,当电源电压vcc到达开机检测电平(例如2.2v)时,电压检测部190向控制器140输出检测信号det。开机检测电平比快闪存储器的通常动作时的动作保证电压(例如2.7v~3.3v)更低。

40.举例而言,控制器140的构成包括cpu或rom/ram等的微控制器,或状态机。举例而言,在rom中储存用以执行开机动作、读取动作、编程动作、抹除动作等的程序,控制器140通过执行这些程序控制各动作。

41.当控制器140从电压检测部190接收到检测信号det时,执行开机动作。另外,控制器140接收来自外部的读取指令、编程指令、或抹除指令时,执行这些动作。在读取动作中,对位线施加正电压,对选择字元线施加例如为0v的电压,对非选择线施加通过电压,开启位线侧选择电晶体以及源线侧选择电晶体,对共通源线施加0v。在编程动作中,对选择字元线施加高电压之编程电压vpgm,对非选择字元线施加中间电位,开启位线侧选择电晶体,关闭源线侧选择电晶体,对位线供给回应数据“0”或“1”的电压。在抹除动作中,对区块内的被选择字元线施加0v,对p型井施加高电压,以区块为单位将数据抹除。

42.图4显示本实施例的开机动作的流程图。当电源被输入时,电压检测部190在检测到电源电压vcc到达开机检测电平(2.2v)后,向控制器140提供检测信号det(s200)。控制器140回应检测信号det开始读取存储单元阵列内的熔丝存储器,以读出储存于该熔丝存储器的设定信息以及特征数据(s210)。

43.控制器140比较读出的特征数据以及一预设值是否相同,以判定特征数据是否正确(s220)。若特征值与预设值相同,则在暂存器180中写入识别数据pofail=0,并在cf暂存器中写入从熔丝存储器读出的设定数据后(s230),结束熔丝存储器的读取(s240)。

44.另一方面,若在步骤s220中特征数据与预设值不同,表示熔丝存储器的读取出现错误。控制器140会先确认对熔丝存储器的读取次数是否达到一最大值(s250)。若否,控制器140会回到步骤s210~s220,重新进行熔丝存储器的读取以及特征数据的判定。若对熔丝存储器的读取次数已达到最大值,则在暂存器180中写入识别数据pofail=1,并在cf暂存器中写入从熔丝存储器读出的设定数据后(s260),结束熔丝存储器的读取(s270)。

45.值得一提的是,本实施例中,识别数据pofail用以表示对熔丝存储器的读取是否在达到最大值前正确完成。具体而言,识别数据pofail=0,表示对熔丝存储器的读取是在达到最大值前正确完成,则代表写入至cf暂存器的设定信息为可靠的;相对地,识别数据pofail=1,表示对熔丝存储器的读取在达到最大值前仍未正确完成(特征数据与期待值不同),因此写入cf暂存器的设定信息中可能会出现错误。

46.开机动作后,当电源电压vcc达到动作保证电压,快闪存储器100成为可以回应外部指令以进行动作的就绪状态。若使用者在任意的时序中输入读取暂存器180的指令,控制器140会回应该读取指令,读取暂存器180的数据,并由外部端子输出读取的数据。通过检查暂存器180的识别数据pofail,使用者可以得知开机动作时熔丝存储器的读取是否正确完成。若识别数据pofail=1,因为开机动作时熔丝存储器的读取未正确完成,写入至cf暂存器中的设定信息可能出现错误,使用者可以重新进行开机动作等。

47.根据本实施例,可根据储存于暂存器180的识别数据pofail判断熔丝存储器的读取是否正确完成,当发生起因于cf暂存器中设定信息错误而导致快闪存储器错误动作的情况时,使用者可以轻易地得知错误动作的原因。

48.图5显示一习知的重设动作的流程图。若从外部输入重设指令(s300),控制器140会确认快闪存储器是否为动作中(即忙碌状态)(s310),若为动作中则中止该动作(s320),并重设包括暂存器等内部电路。

49.图6显示本发明一实施例的重设动作的流程图,本实施例是回应来自使用者的重设指令以重新进行熔丝存储器的读取。图6的步骤s400~s420与图5的步骤s300~s320相同,在此不再赘述。更进一步地,在本实施例中,控制器140会在重设内部电路前检查暂存器180的识别数据pofail是否为0(s430)。若识别数据pofail=0,则直接重设内部电路(s440)。若识别数据pofail=1,则重新进行熔丝存储器的读取,并将读取出来的设定信息写入至cf暂存器180(s460)后,重设内部电路(s440)。

50.值得一提的是,在实施重设指令时,由于快闪存储器的电源电压vcc已到达动作保证电压,因此在重设动作时的熔丝存储器的读取比开机动作时的熔丝存储器的读取更稳定,可以进行可靠性更高的读取。因此在重设动作中若检测到识别数据pofail=1时(即开机动作时熔丝存储器的读取未正确完成),透过在重设动作中重新进行熔丝存储器的读取,能够将该设定信息改写为在重设动作时读取的设定信息,进而降低快闪存储器的错误动作的发生。

51.图7显示本发明另一实施例的内部重设动作的流程图,本实施例是在开机动作后,回应内部重设指令以重新进行熔丝存储器的读取。请参照图7,开机动作结束后(s500),若快闪存储器100的电源电压vcc到达动作保证电压,控制器140实施内部重设指令(s510)。在一实施例中,可以在从开机动作经过预定的时间后自动实施内部重设指令。接着,控制器140检查暂存器180的识别数据pofail是否为0(s520)。若识别数据pofail=0,则直接结束动作。若识别数据pofail=1,则重新进行熔丝存储器的读取,并将读取出来的设定信息写入至cf暂存器(s530)后,结束动作。

52.根据本实施例,通过在开机动作后(即,电源电压vcc到达动作保证电压)自动进行内部重设动作,可在发现开机动作时熔丝存储器的读取未正确完成时,重新进行熔丝存储器的读取,并将可靠度较高的设定信息重新写入至cf暂存器,进而防止快闪存储器的错误动作。

53.图8显示本发明又一实施例的开机重试动作的流程图,本实施例是回应有别于重设指令的预设的使用者指令以重新进行熔丝存储器的读取。请参照图8,当输入来自外部的开机重试指令时(s600),控制器140根据开机重试指令检查暂存器180的识别数据pofail是否为0(s610)。若识别数据pofail=0,则直接结束动作。若识别数据pofail=1,则重新进行熔丝存储器的读取,并将读取出来的设定信息写入至cf暂存器(s620)后,结束动作。

54.本实施例中,因为在实施开机重试指令时,快闪存储器也是以动作保证电压进行动作,故熔丝存储器的读取比开机动作时的可靠度更高,可以将正确的设定信息写入至cf暂存器。

55.图9显示本发明一实施例的读取、编程或抹除动作的流程图,本实施例是回应于读取、编程或抹除等指令

56.以重新进行熔丝存储器的读取。请参照图9,控制器140从外部接收读取、编程或抹除的指令时(s700),在这些动作开始前,会检查暂存器180的识别数据pofail是否为0(s710)。若识别数据pofail=0,则直接进行读取、编程或抹除等动作(s730)。若识别数据pofail=1,则重新进行熔丝存储器的读取,并将读取出来的设定信息写入至cf暂存器(s720)后,进行读取、编程或抹除等动作(s730)。

57.根据本实施例,可在实施读取、编程或抹除之前,根据识别数据pofail确认cf暂存

器中的设定信息是否可能有误,当检测到识别数据pofail=1时,则重新进行熔丝存储器的读取,以重新写入cf暂存器中的设定数据,故后续可根据更可靠的设定信息设定读取、编程或抹除动作的动作电压或动作时序等,进而防止快闪存储器的错误动作。

58.上述实施例中,虽然以nand型快闪存储器进行例示,但本发明也可适用进行开机动作的半导体存储装置。另外,在上述实施例中,虽然熔丝存储器是设置于存储单元阵列之内,但也可以设置于不同于存储单元阵列的非易失性存储区域。

59.本发明针对较佳的实施型态详述如上,然而本发明不限定于特定的实施型态,只要在记载于权利要求的本发明的要旨的范围内,可以做各种变形以及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1