存储设备的制作方法

存储设备

1.相关申请的交叉引用

2.本技术基于并要求2020年9月16日提交的日本专利申请no.2020-155568和2021年3月15日提交的美国专利申请no.17/200966的优先权的权益,其全部内容通过引用并入本文。

技术领域

3.本文所描述的实施例一般涉及存储设备。

背景技术:

4.使用可变电阻元件(例如,磁阻效应元件)作为存储元件的存储设备是已知的。

技术实现要素:

5.实施例提供一种存储设备,可以改进存储设备的特性。

6.一般地,根据一个实施例,存储设备包括:存储单元;以及读电路,其被配置为感测基于存储单元中的第一数据的第一信号,将第二数据写入存储单元,感测基于存储单元中的第二数据的第二信号,以及基于第一信号与第二信号之间的比较结果来读取存储单元中的数据。读电路包括被配置为感测第一信号和第二信号的第一感测放大器,并且第一感测放大器包括:电流镜电路,其被配置为使第一电流流入被连接到存储单元的第一节点,并基于第一节点的电位,使第二电流流入第二节点;第一开关元件,其包括被连接到第二节点的第一端子和被连接到第三节点的第二端子;第一晶体管,其包括被连接到第二节点的第三端子和被连接到第三节点的第一栅极;第二开关元件,其包括被连接到第二节点的第四端子和被连接到第四节点的第五端子;以及第一电路,其被连接到第二节点和第三节点,并被配置为基于第三节点的电位,使第三电流流入第二节点。

附图说明

7.图1是示出根据第一实施例的存储设备的配置的示例的框图。

8.图2是根据第一实施例的存储设备的存储单元阵列的等效电路图。

9.图3和图4是各自示出根据第一实施例的存储设备的存储单元阵列的结构的示例的截面图。

10.图5是示出根据第一实施例的存储设备的存储元件的配置的示例。

11.图6是示出根据第一实施例的存储设备的读电路的配置的示例的框图。

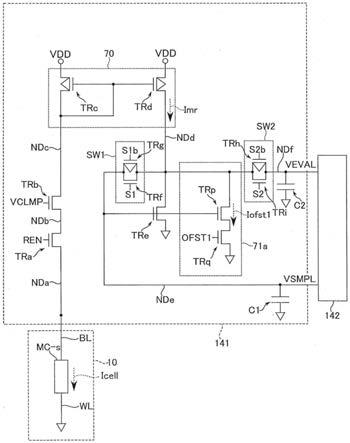

12.图7和图8是根据第一实施例的存储设备的读电路的等效电路图。

13.图9是示出根据第一实施例的存储设备的操作的示例的流程图。

14.图10是示出根据第一实施例的存储设备的操作的示例的时序图。

15.图11和图12是示出根据第一实施例的存储设备的操作的示例的图。

16.图13、图14、图15和图16是示出根据第一实施例的存储设备的特性的图。

17.图17是示出根据第二实施例的存储设备的配置的示例的等效电路图。

18.图18是示出根据第二实施例的存储设备的操作的示例的时序图。

19.图19和图20是示出根据第二实施例的存储设备的操作的示例的图。

20.图21是示出根据第三实施例的存储设备的操作的示例的图。

21.图22是示出根据第三实施例的存储设备的操作的示例的时序图。

22.图23是示出根据第四实施例的存储设备的操作的示例的图。

23.图24是示出根据第四实施例的存储设备的操作的示例的时序图。

24.图25是示出根据第五实施例的存储设备的配置的示例的等效电路图。

25.图26是示出根据第六实施例的存储设备的配置的示例的等效电路图。

26.图27是示出根据第七实施例的存储设备的配置的示例的等效电路图。

具体实施方式

27.下面将参考附图描述实施例。注意,在以下描述中,具有相同功能和配置的构成元件由共同的附图标记表示。另外,通过将后缀添加到共同的附图标记来区分具有共同的附图标记的多个构成元件。注意,当不需要区分多个构成元件时,多个构成元件仅用共同的附图标记表示而不添加任何后缀。在这种情况下,除了下标和上标之外,后缀还包括例如被添加到共同的附图标记的末尾以指示阵列的索引。

28.(1)第一实施例

29.将参考图1、图2、图3、图4、图5、图6、图7、图8、图9、图10、图11、图12、图13、图14、图15和图16描述根据第一实施例的存储设备。

30.(1a)配置示例

31.将参考图1、图2、图3、图4、图5、图6、图7和图8描述根据该实施例的存储设备的配置的示例。

32.图1是示出根据该实施例的存储设备的配置的示例的框图。

33.如图1所示,例如,存储设备1被连接到在存储设备1外部的设备(在下文中被称为外部设备)。外部设备9向存储设备1发送命令cmd、地址adr、和控制信号cnt。在写入时,外部设备9发送待写入在存储设备1的数据(在下文中被称为写入数据)。在读取时,外部设备9从存储设备1接收从存储设备1读出的数据(在下文中被称为读取数据)。

34.存储设备1包括存储单元阵列10、行控制电路11、列控制电路12、写电路13、读电路14、电压产生电路15、输入/输出电路16、和控制电路17。

35.存储单元阵列10包括多个存储单元mc、多个字线、和多个位线。

36.多个存储单元中的每一个与对应的一对行和列相关联。每个存储单元mc被连接到多个字线wl中的对应字线。每个存储单元mc被连接到多个位线bl中的对应位线。

37.行控制电路11经由字线wl被连接到存储单元阵列10。行控制电路11接收有关地址adr的行的解码结果(行地址)。行控制电路11基于有关地址adr的解码结果来控制多个字线wl。采用该操作,行控制电路11将多个字线wl(多个行)设定在选择状态和非选择状态。在以下描述中,被设定在选择状态的字线wl被称为选择字线wl,并且除了选择字线wl之外的字线wl被称为非选择字线wl。

38.列控制电路12经由位线bl被连接到存储单元阵列10。列控制电路12接收有关地址

adr的列的解码结果(列地址)。列控制电路12基于关于地址adr的解码结果来控制多个位线bl。采用该操作,列控制电路12将多个位线bl(多个列)设定在选择状态和非选择状态。在以下描述中,被设定在选择状态的位线bl被称为选择位线bl,并且除了选择位线bl之外的位线bl被称为非选择位线bl。

39.写电路13将数据写入存储单元mc中。写电路13包括例如写驱动器(未示出)。

40.读电路14从存储单元mc读取数据。读电路14包括例如前置放大器141和感测放大器142。稍后将描述前置放大器141和感测放大器142的详细配置。

41.电压产生电路15通过使用从外部设备9提供的电源电压来产生用于存储单元阵列10的各种类型的操作的电压。例如,电压产生电路15产生用于写操作的各种类型的电压。电压产生电路15将所产生的电压输出到写电路13。例如,电压产生电路15产生用于读操作的各种类型的电压。电压产生电路15将所产生的电压输出到读电路14。

42.输入/输出电路16用作用于存储设备1与外部设备9之间的各种类型的信号adr、cmd、cnt、和dt的接口电路。

43.输入/输出电路16将地址adr从外部设备9传递到控制电路17。输入/输出电路16将命令cmd从外部设备9传递到控制电路17。输入/输出电路16在外部设备9与控制电路17之间传递各种控制信号cnt。输入/输出电路16将数据dt从外部设备9传递到写电路13。输入/输出电路16将从读电路14传递的数据dt传递到外部设备9。

44.控制电路(也被称为定序器、状态机、或内部控制器)17对命令cmd解码。控制电路17基于命令cmd的解码结果、控制信号cnt、和命令cmd来控制存储设备1中的行控制电路11、列控制电路12、写电路13、读电路14、电压产生电路15、和输入/输出电路16的操作。

45.控制电路17对地址adr解码。控制电路17向行控制电路11、列控制电路12等发送地址解码结果。注意,可以在存储设备1中的控制电路17外部提供用于解码命令的电路(命令解码器)和用于解码地址的电路(地址解码器)。

46.(1a-1)存储单元阵列的配置的示例

47.图2是示出根据该实施例的存储设备的存储单元阵列的配置的示例的等效电路图。参考图2,通过后缀(索引)来区分字线wl、位线bl、和存储单元mc。

48.如图2所示,多个存储单元mc在存储单元阵列10中被布置成矩阵图案。每个存储单元mc被连接到多个位线bl(bl《0》,bl《1》,...,bl《n-1》)中的对应位线bl和多个字线wl(wl《0》,wl《1》,...,wl《m-1》)中的对应字线wl。在这种情况下,m和n是任意整数。存储单元mc《i,j》(0≤i≤m-1,0≤j≤n-1)被连接在字线wl《i》与位线bl《j》之间。

49.每个存储单元mc包括开关元件20和存储元件(可变电阻元件)21。

50.在向对应的存储元件21写入数据和从对应的存储元件21读取数据时,开关元件20用作控制向存储元件21提供电流(或电压)的选择元件。

51.当例如被施加到给定存储单元mc的电压低于存储单元mc中的开关元件20的阈值电压vth时,开关元件20被设定在off状态(高阻状态或绝缘状态)。在这种情况下,开关元件20切断到存储单元mc的电流。

52.当被施加到给定存储单元mc的电压等于或高于存储单元mc中的开关元件20的阈值电压vth时,开关元件20被设定在on状态(低阻状态或导通状态)。在这种情况下,开关元件20使电流流入存储单元mc。

53.开关元件20具有能够根据被施加到存储单元mc的电压的幅度来切换是否允许电流流动到存储单元mc而不管电流的流动方向的功能。

54.开关元件20例如是二端元件。作为二端元件的开关元件20包括在两个端子之间提供的层。开关元件20包括具有在层的电阻状态之间切换的功能的层(也被称为切换层或电阻改变层)。

55.当被施加在开关元件20的两个端子之间的电压低于开关元件20的阈值电压时,开关元件20处于高阻状态(off状态)。在这种情况下,开关元件20被设定在非导电状态。

56.当被施加在开关元件20的两个端子之间的电压等于或高于阈值电压时,开关元件20处于低阻状态(on状态)。在这种情况下,开关元件20被设定在非导电状态。

57.优选地,开关元件20具有关于被施加到开关元件20的电压的双极(即,正极和负极)的开关函数(特性)。然而注意,开关元件20可以具有关于被施加到开关元件20的正极和负极中的至少一个的开关函数(特性)。

58.例如,存储元件21是可变电阻元件。可变电阻元件21的电阻状态取决于其提供由开关元件20控制的电流(或电压)而改变成多个电阻状态(例如,低阻状态和高阻状态)。存储元件21可以通过将元件21的电阻状态与数据(例如,“0”数据和“1”数据)相关联来存储数据。

59.图3和图4用于说明根据该实施例的存储设备的存储单元阵列的结构的示例。图3是示出沿着x方向的存储阵列的剖面结构的示意性截面图。图4是示出沿着y方向的存储阵列的剖面结构的示意性截面图。

60.如图3和图4所示,存储单元阵列10被提供在基板100的上表面的上方。

61.在以下描述中,假定与基板100的上表面平行的平面被定义为x-y平面,并且与x-y方面垂直的方向(轴)被定义为z方向(z轴)。

62.在z方向上在基板100的上表面的上方提供多个导电层50。多个导电层50沿着y方向布置。每个导电层50沿着x方向延伸。多个导电层50用作例如字线wl。

63.图3和图4示出了其中多个导电层50与基板100接触的情况。然而注意,可在多个导电层50与基板100之间提供绝缘层(未示出)。

64.在z方向上在多个导电层50的上方提供多个导电层51。多个导电层51沿着x方向布置。每个导电层51沿着y方向延伸。多个导电层51用作例如位线bl。

65.在多个导电层50与多个导电层51之间提供多个存储单元mc。多个存储单元mc在x-y平面中被排列成矩阵图案。

66.在一个导电层50上提供在x方向上布置的多个存储单元mc。在x方向上布置的多个存储单元mc被连接到公共字线wl。

67.在一个导电层51下面提供在y方向上布置的多个存储单元mc。在y方向上布置的多个存储单元mc被连接到公共位线bl。

68.例如,在每个存储单元mc中,在z方向上在开关元件20上提供存储元件(可变电阻元件)21。在这种情况下,在导电层(字线)50上提供开关元件20。在可变电阻元件21上提供导电层(位线)51。

69.注意,开关元件20和存储元件21在z方向上的配置可以与图3和图4所示的布置相反。在这种情况下,在元件21上提供元件20。

70.根据存储单元阵列和存储单元配置,导电层50和导电层51可被分别用作位线bl和字线wl。

71.存储单元mc是包括开关元件20和存储元件21的层堆叠。

72.作为二端元件的开关元件20包括两个电极201、203和切换层(电阻改变层)202。在z方向上在两个电极201、203之间提供切换层202。

73.存储元件21是可变电阻元件。可变电阻元件21可以具有多个电阻状态(电阻值)。可变电阻元件21通过将可变电阻元件21的电阻状态与数据(例如,1位数据)相关联来用作存储元件。

74.例如,存储元件21是磁阻效应元件。在这种情况下,根据该实施例的存储设备是像mram(磁阻随机存取存储器)的磁存储器。

75.《磁阻效应元件》

76.将参考图5描述根据该实施例的存储设备的存储元件(磁阻效应元件)的配置的示例。

77.图5是示出磁阻效应元件的配置的示例的截面图。图5示出了例如沿着与图3和图4所示的存储元件21的z方向平行的平面(例如,x-z平面)的剖面的示例。

78.例如,磁阻效应元件21包括至少两个磁层211、213和非磁层212。在z方向上在两个磁层211、213之间提供非磁层212。例如,多个层(即磁层211、非磁层212、和磁层213)按该顺序从字线wl侧堆叠到位线bl侧。

79.在z方向上排列的两个磁层211、213和非磁层212形成磁隧道结(mtj)。在以下描述中,包括磁隧道结的磁阻效应元件21将通过以mtj元件21的使用为例来描述。mtj元件21的非磁层212将被称为隧道势垒层。

80.磁层211和213各自是例如铁磁层,其包括钴、铁、和/或硼。磁层211和213各自可以是单层膜或多层膜(例如,人工晶格膜)。隧道势垒层212是例如包括氧化镁的绝缘膜。隧道势垒层可以是单层膜或多层膜。

81.例如,磁层211和213各自具有垂直磁各向异性。每个磁层211、213的易磁化轴方向与每个磁层211、213的层表面(膜表面)垂直。每个磁层211、213的磁化方向平行于磁层211、213的阵列方向(z方向)。磁层211和213各自具有与每个磁层211、213的层表面垂直的磁化。

82.如上文所描述的,在该实施例中,mtj元件21是垂直磁化类型的磁阻效应元件。

83.两个磁层211和213中的一个具有可变的磁化方向,而另一个磁层具有不变的磁化方向。根据一个磁层的磁化方向与另一个磁层的磁化方向之间的相对关系(在下文中被称为磁化对准),mtj元件21可以具有多个电阻状态(电阻值)。

84.在图5所示的情况下,磁层213具有可变的磁化方向。磁层211具有不变(固定)的磁化方向。在以下描述中,具有可变的磁化方向的磁层213被称为存储层。在以下描述中,具有不变(固定)的磁化方向的磁层211被称为参考层。注意,存储层213有时被称为自由层、磁化自由层、或磁化可变层。磁层211有时被称为钉扎层(pin layer)、被钉扎层(pinned layer)、磁化不变层、或磁化固定层。

85.在该实施例中,“参考层(磁层)具有不变的磁化方向”或者“参考层(磁层)具有固定的磁化方向”意味着当用于改变存储层的磁化方向的电流或电压被提供给磁阻效应元件时,无论该电流或电压在电流/电压的提供之前或之后提供,参考层的磁化方向不改变。

86.例如,mtj元件21包括两个电极219a和219b。在z方向上在两个电极219a和219b之间提供磁层211、213和隧道势垒层212。在电极219a与隧道势垒层212之间提供参考层211。在电极219b与隧道势垒层212之间提供存储层213。

87.例如,在mtj元件21中可以提供移位消除层(未示出)。在参考层211与电极219a之间提供移位消除层。移位消除层是用于减轻来自参考层211的杂散磁场的影响的磁层。

88.在移位消除层与参考层211之间提供非磁层(未示出)。非磁层例如是金属层,诸如ru(钌)层。

89.参考层211通过非磁层被反铁磁性地结合到移位消除层。这使包括参考层211和移位消除层的层堆叠形成saf(合成反铁磁性)结构。在saf结构中,移位消除的磁化方向与参考层211的磁化方向相反。在saf结构中,参考层211的磁化方向被设定在固定状态。

90.例如,mtj元件21可以包括基础层(未示出)和覆盖层(未示出)中的至少一个。在磁层(在这种情况下是参考层)211与电极219a之间提供基础层。基础层是非磁层(例如,导电复合物层)。基础层是用于改进与基础层接触的磁层211的特性(例如,结晶性和/或磁特性)的层。覆盖层是在磁层(在这种情况下是存储层)213与电极219b之间的非磁层(例如,导电复合物层)。覆盖层是用于改进与覆盖层接触的磁层213的特性(例如,结晶性和磁特性)的层。注意,基础层和覆盖层可以被认为是电极219(219a和219b)的构成元件。

91.当存储层213的磁化方向与参考层211的磁化方向相同时,mtj元件21的磁化对准的状态是磁化平行状态(在下文中被称为p状态)。当存储层213的磁化方向与参考层211的磁化方向相反时,mtj元件21的磁化对准的状态是磁化反平行状态(在下文中被称为ap状态)。

92.mtj元件21的磁化对准状态与mtj元件21的电阻值(磁阻)之间的关系的示例是:处于p状态的mtj元件21的电阻值低于处于ap状态的mtj元件21的电阻值。在这种情况下,处于p状态的mtj元件的电阻状态对应于低阻状态,处于ap状态的mtj元件的电阻状态对应于高阻状态。

93.例如,“0”数据与处于p状态(低阻状态)的mtj元件21相关联,并且“1”数据与处于ap状态(高阻状态)的mtj元件21相关联。然而注意,将mtj元件21的磁化对准状态(电阻状态)与“1”/“0”数据相关联的方式不限于以上情况。

94.利用mtj元件21的这些特性,mtj元件21用作存储元件。

95.使用mtj元件21将数据写入存储单元mc是通过控制mtj元件21的存储层213的磁化方向来执行的。当数据被写入时,mtj元件21的电阻状态(电阻值)根据mtj元件21的磁化对准状态来改变。

96.当例如存储层213的磁化方向通过stt(自旋转移矩)来切换时,写入电流iwr(iwr0,iwr1)被提供给mtj元件21。

97.根据写入电流iwr是从存储层213流到参考层211还是从参考层211流到存储层213,控制mtj元件21的磁化对准状态从ap状态到p状态或从p状态到ap状态的改变。写入电流iwr的电流值被设定为小于参考层211的磁化翻转阈值并且等于或大于存储层213的磁化翻转阈值。注意,存储层213的磁化翻转阈值优选地大于用于将开关元件设定在低阻状态的阈值电流。

98.在mtj元件21中流动的写入电流iwr产生有助于存储层213的磁化翻转的自旋力

矩。所产生的自旋力矩被施加到存储层213。

99.当mtj元件21的磁化对准状态从ap状态改变为p状态(在下文中也被称为p写入)时,从存储层213流到参考层211的写入电流iwr0被提供给mtj元件21。这将在与参考层211的磁化方向相同的方向上的自旋(电子)的自旋力矩施加到存储层213的磁化。当存储层213的磁化方向与参考层211的磁化方向相反时,通过所施加的自旋力矩,存储213的磁化方向被改变到与参考层211的磁化方向相同的方向。

100.因此,mtj元件21的磁化对准状态被设定为p状态。在这种情况下,mtj元件21保持“0”数据。

101.当mtj元件21的磁化对准状态从p状态改变为ap状态(在下文中也被称为ap写入)时,从参考层211流到存储层213的写入电流iwr1被提供给mtj元件21。这将在与参考层211的磁化方向相反的方向上的自旋的自旋力矩施加到存储层213的磁化。当存储层213的磁化方向与参考层211的磁化方向相同时,通过所施加的自旋力矩,存储层213的磁化方向被改变到与参考层211的磁化方向相反的方向。

102.因此,mtj元件21的磁化对准状态被设定为ap状态。在这种情况下,mtj元件21保持“1”数据。

103.通过区分mtj元件21的磁化对准状态(电阻值),从存储单元mc中读取数据。在数据读取时,根据电压被施加到存储单元mc,电流在mtj元件21中流动。在数据读取时的电流的电流值被设定为小于存储层213的磁化翻转阈值的值。

104.基于在将电压施加到存储单元mc时来自mtj元件21的输出信号(例如,电流或电压)的幅度,mtj元件21的电阻值(磁化对准状态)被等效地区分。

105.采用该操作,存储单元mc中的数据被区分和读取。

106.在该实施例中,基于自参考方案来执行读操作。稍后将详细描述基于自参考方案的读操作。

107.(a-2)读电路的配置

108.将参考图6、图7和图8描述根据该实施例的存储设备(例如,mram)的读电路的配置的示例。

109.图6是用于说明根据该实施例的mram的读电路的配置的框图。

110.如图6所示,读电路14包括一个或多个前置放大器(也被称为前置级感测放大器电路)144和一个或多个感测放大器(也被称为后置级感测放大器电路)142。

111.例如,使前置放大器141和感测放大器142对应于位线bl(列)。一个前置放大器141和一个感测放大器142的一个对被提供用于一个位线bl。注意,一对前置放大器141和感测放大器142可以被提供用于一组两个或更多个位线bl。

112.前置放大器141经由对应的位线bl被连接到存储单元mc。前置放大器141可以感测基于存储单元mc中的数据的信号。

113.前置放大器141经由节点nde和ndf被连接到对应的感测放大器142。注意,每个节点是包括互连线、接触点、和端子的构成元件。

114.前置放大器141感测并放大来自存储单元mc的多个信号(电压或电流)。前置放大器141在节点nde和ndf中保持被感测放大的信号。

115.感测放大器142感测被提供给节点nde和ndf的信号(电压或电流),并放大被感测

的信号。

116.感测放大器142基于被感测放大的信号来区分存储单元mc中的数据。存储单元mc中的数据作为信号do和dob被输出到读电路14的外部。

117.如上文所描述的,读电路14使用前置放大器141和感测放大器142来读取存储单元mc(存储单元阵列)中的数据。

118.《感测放大器》

119.将参考图7描述根据该实施例的存储设备的感测放大器(后置级感测放大器电路)的配置的示例。

120.图7是用于说明根据该实施例的存储设备的感测放大器的配置的电路图。如图7所示,感测放大器142包括多个晶体管tr1至tr18。

121.晶体管tr1、tr2、tr3、tr4、tr5和tr6例如是具有p型传导性的场效应晶体管(例如,mos晶体管)。晶体管tr7、tr8、tr9、tr10、tr11、tr12、tr13、tr14、tr15、tr16、tr17和tr18例如是具有n型传导性的场效应晶体管(例如,mos晶体管)。

122.晶体管tr1至tr18中的每一个包括多个端子(例如,源极和漏极)和栅极。

123.晶体管tr1的一个端子(源极和漏极中的一个)被连接到电压(例如,电源电压)vdd被施加到的端子。电压vdd被提供到晶体管tr1的一个端子(源极和漏极中的一个)。电源电压vdd被施加到的端子(或节点)在下文中将被表示为电源端子(或电源节点)vdd。

124.晶体管tr1的另一个端子(源极和漏极中的另一个)被连接到节点nd1。

125.信号latnb被提供到晶体管tr1的栅极。信号latnb例如是(将在稍后描述的)信号latn的反信号。

126.晶体管tr2的一个端子被连接到节点nd1。晶体管tr2的另一个端子被连接到节点nd2。晶体管tr2的栅极被连接到节点nd3。

127.晶体管tr3的一个端子被连接到节点nd1。晶体管tr3的另一个端子被连接到节点nd3。晶体管tr3的栅极被连接到节点nd2。

128.晶体管tr4的一个端子被连接到节点nd3。晶体管tr4的另一个端子被连接到节点nd2。信号sen被提供到晶体管tr4的栅极。信号sen例如是指示感测被提供到节点nde和ndf的电压的处理(其在下文中将被称为感测处理)的开始(感测放大器142的激活)的信号。

129.晶体管tr5的一个端子被连接到电源端子vdd。电源电压vdd被提供到晶体管tr5的一个端子。晶体管tr5的另一个端子被连接到节点nd2。信号sen被提供到晶体管tr5的栅极。

130.晶体管tr6的一个端子被连接到电压端子vdd。电源电压vdd被提供到晶体管tr6的一个端子。晶体管tr6的另一个端子被连接到节点nd3。信号sen被提供到晶体管tr6的栅极。

131.晶体管tr7的一个端子被连接到节点nd2。晶体管tr7的另一个端子被连接到节点nd4。晶体管tr7的栅极被连接到节点nd3。

132.晶体管tr8的一个端子被连接到节点nd3。晶体管tr8的另一个端子被连接到节点nd5。晶体管tr8的栅极被连接到节点nd2。

133.晶体管tr9的一个端子被连接到节点nd4。晶体管tr9的另一个端子被连接到接地电压vss被施加到的端子。接地电压vss被提供到晶体管tr9的一个端子。接地电压vss被施加到的端子(或节点)在下文中将被表示为接地端子(或接地节点)vss。信号latn被提供到晶体管tr9的栅极。信号latn例如是指示感测处理的结束的信号。

134.晶体管tr10的一个端子被连接到节点nd5。晶体管tr10的另一个端子被连接到接地端子vss。信号latn被提供到晶体管tr10的栅极。

135.晶体管tr11的一个端子被连接到节点nd4。晶体管tr11的另一个端子被连接到节点nd6。信号sen2被提供到晶体管tr11的栅极。信号sen2例如是与信号sen一起指示感测处理的开始的信号。

136.晶体管tr12的一个端子被连接到节点nd5。晶体管tr12的另一个端子被连接到节点nd7。信号sen2被提供到晶体管tr11的栅极。

137.晶体管tr13的一个端子被连接到节点nd6。晶体管tr13的另一个端子被连接到接地端子vss。接地电压vss被提供到晶体管tr13的另一个端子。晶体管tr13的栅极被连接到节点nde。来自前置放大器141的信号(电压)vsmpl经由节点nde被提供到晶体管tr13的栅极。晶体管tr13的栅极变成感测放大器142的一个输入端子。晶体管tr13用作用于从前置放大器141到感测放大器142的信号(电压vsmpl)的输入部。

138.晶体管tr14的一个端子被连接到节点nd7。晶体管tr14的另一个端子被连接到接地端子vss。接地电压vss被提供到晶体管tr14的另一个端子。晶体管tr14的栅极被连接到节点ndf。来自前置放大器141的信号(电压)veval经由节点ndf被提供到晶体管tr14的栅极。晶体管tr14的栅极变成感测放大器142的另一个输入端子(输入部)。晶体管tr14用作用于从前置放大器141到感测放大器142的信号(电压veval)的输入单元。

139.晶体管tr15的一个端子被连接到节点nd6。晶体管tr15的另一个端子被连接到晶体管tr16的一个端子。信号shftdob被提供到晶体管tr15的栅极。信号shftdob例如是指示感测放大器142是否通过偏移(偏置)与节点nde的电压vsmpl对应的值来感测该值的信号。

140.晶体管tr16的另一个端子被连接到接地端子vss。电压vshfta被提供到晶体管tr16的栅极。电压vshfta例如是指示节点nde的电压vsmpl(或与电压vsmpl对应的值)的偏移值(偏置量)的信号电压。

141.晶体管tr17的一个端子被连接到节点nd7。晶体管tr17的另一个端子被连接到晶体管tr18的一个端子。信号shftdo被提供到晶体管tr17的栅极。信号shftdo是信号shftdo的反信号。信号shftdo例如是指示感测放大器142是否通过偏移(偏置)节点ndf的电压veval(或与电压veval对应的值)来感测该值的信号。

142.晶体管tr18的另一个端子被连接到接地端子vss。电压vshftb被提供到晶体管tr18的栅极。

143.电压vshftb是指示与节点ndf的电压veval对应的值的偏移值的电压。

144.感测放大器142的输出端子ot1被连接到节点nd2。信号do从输出端子ot1输出到感测放大器142的外部。

145.感测放大器142的输出端子ot2被连接到节点nd3。信号dob从输出端子ot2输出到感测放大器142的外部。信号dob是信号do的反信号。

146.在该实施例中,晶体管tr15和tr16用作偏移电路72a。

147.包括晶体管tr15和tr16的偏移电路72a将给定偏移值(偏移电流)添加到根据节点nde的电压vsmpl的来自晶体管tr13的输出(电流)。这使得可以在感测放大器142内等效地偏移电压vsmpl的值。要被偏移电路72a添加的偏移量根据信号vshft的电压值来设定。

148.在该实施例中,晶体管tr17和tr18用作偏移电路72b。

149.包括晶体管tr17和tr18的偏移电路72b将给定偏移值添加到与节点ndf的电压veval对应的来自晶体管tr14的输出(电流)。这使得可以在感测放大器142内等效地偏移电压veval的值。要被偏移电路72b添加的偏移量根据信号vshft的电压值来设定。

150.图7中的感测放大器142可以将节点nde的电压vsmpl的幅度与节点ndf的电压veval的幅度进行比较。

151.感测放大器142可以将基于比较结果的信号作为信号do和dob分别输出到输出端子ot1和ot2。

152.《前置放大器》

153.将参考图8描述根据该实施例的存储设备的前置放大器(前置级感测放大器电路)的配置的示例。

154.图8是用于说明根据该实施例的mram的前置放大器的配置的示例的电路图。

155.采用图8中的配置,前置放大器141可以感测、放大、和保持基于存储单元中的数据(mtj元件的电阻状态)的来自存储单元mc的信号作为感测结果。

156.如图8所示,感测放大器142包括多个晶体管tra、trb、trc、trd、tre、trf、trg、trh、tri、trp和trq。晶体管tra、trb、tre、trf、trh、trp和trq例如是具有n型传导性的场效应晶体管(例如,mos晶体管)。晶体管trc、trd、trg和tri例如是具有p型传导性的场效应晶体管(例如,mos晶体管)。

157.晶体管tra、trb、trc、trd、tre、trf、trg、trh、tri、trp和trq中的每一个包括多个端子(源极和漏极)和栅极。

158.晶体管tra的一个端子经由节点dna被连接到位线bl。晶体管tra的另一个端子被连接到节点ndb。信号ren被提供到晶体管tra的栅极。信号ren例如是指示来自存储单元mc的数据读操作的开始和结束的信号。

159.晶体管trb的一个端子被连接到节点ndb。晶体管trb的另一个端子被连接到节点ndc。信号vclmp被提供到晶体管trb的栅极。信号vclmp例如是用于将经由晶体管tra和trb被施加到存储单元mc的电压调节(钳位)到预定幅度的信号。

160.晶体管trc的一个端子被连接到节点ndc。晶体管trc的另一个端子被连接到电源端子vdd。晶体管trc的栅极被连接到节点ndc。

161.晶体管trd的一个端子被连接到电源端子vdd。晶体管trd的另一个端子被连接到节点ndd。晶体管trd的栅极被连接到节点ndc。

162.晶体管trc和trd用作电流镜电路70。包括晶体管trc和trd的电流镜电路70被配置为在执行读操作时使得与在存储单元mc中流动的电流(在下文中也被称为单元电流)对应的电流(在下文中也被称为镜像电流或复制电流)imr流入节点ndd。

163.电流镜电路70中的镜像电流imr与单元电流icell之间的电流比根据两个晶体管trc和trd的栅极尺寸(例如,栅极宽度)之间的比率来设定。在该实施例中,例如,晶体管trd的栅极宽度被设定为与晶体管trc的栅极宽度基本上相同的栅极宽度。在这种情况下,镜像电流imr的幅度与单元电流的幅度基本上相同。

164.晶体管tre的一个端子被连接到节点ndd。晶体管tre的另一个端子被连接到接地端子vss。晶体管tre的栅极被连接到节点nde。当(稍后将描述的)晶体管trg和trf处于on状态时,晶体管tre的栅极经由处于on状态的晶体管trg和trf被电连接到节点ndd(以及晶体

管tre的一个端子)。在这种情况下,晶体管tre被二极管连接到节点ndd。晶体管tre也将被称为二极管接法晶体管tre。

165.晶体管trf的一个端子被连接到节点ndd。晶体管trf的另一个端子被连接到节点nde。信号s1被提供到晶体管trf的栅极。

166.晶体管trg的一个端子被连接到节点ndd。晶体管trg的另一个端子被连接到节点nde。信号s1b被提供到晶体管trg的栅极。信号s1b是信号s1的反信号。

167.晶体管trg和trf用作mos开关(开关元件)sw1。mos开关sw1控制节点ndd与节点nde之间的电连接和电断开。可以控制晶体管trg和trf以通过具有互补关系的信号s1和s1b来被同时设定在on状态或off状态。

168.晶体管trh的一个端子被连接到节点ndd。晶体管trh的另一个端子被连接到节点ndf。信号s2被提供到晶体管trf的栅极。

169.晶体管tri的一个端子被连接到节点ndd。晶体管tri的另一个端子被连接到节点ndf。信号s2b被提供到晶体管tri的栅极。信号s2b是信号s2的反信号。

170.晶体管trh和tri用作mos开关sw2。mos开关sw2控制节点ndd与节点ndf之间的电连接和电断开。可以控制晶体管trh和tri以通过具有互补关系的信号s2和s2b来被同时设定在on状态或off状态。

171.节点nde和ndf用作前置放大器141的输出端子。

172.节点nde被连接到(如上所述的)感测放大器142的晶体管tr13的栅极(感测放大器142的一个输入端子)。节点nde包括电容分量c1。例如,电容分量c1是节点nde的互连电容(互连线和端子的寄生电容)。电容分量c1的大小(以及电容分量c1的充电时间)被设定成使得晶体管tre和tr13可通过被保持在电容分量c1中的电压(例如,节点nde的充电电压)来驱动。

173.节点ndf被连接到上文所描述的感测放大器142的晶体管tr14的栅极(感测放大器的另一个输入端子)。节点ndf包括电容分量c2。例如,电容分量c2是节点ndf的互连电容(互连线和端子的寄生电容)。电容分量c2的大小(以及电容分量c2的充电时间)被设定成使得晶体管tr14可通过被保持在电容分量c2中的电压(例如,节点ndf的充电电压)来驱动。

174.注意,电容分量c1和c2中的每一个不限于节点的互连电容,并且可以是被连接到节点nde或ndf的元件(例如,电容器)。

175.节点nde和ndf中的每一个可以保持由电容分量c1或c2感测到的信号。

176.节点nde可以用电容分量c1来保持在第一处理时对单元电流icell的感测结果。例如,用被提供到节点nde的电流来对节点nde充电。这使得节点nde保持电容分量c1中的电压vsmpl作为感测结果。

177.节点ndf可以用电容分量c2来保持在第一处理之后执行的第二处理时对单元电流icell的感测结果。例如,用被供到节点ndf的电流来对节点ndf充电。这使得节点ndf保持电容分量c2中的电压veval作为感测结果。

178.在根据该实施例的mram 1中,前置放大器141包括偏移电路71a。在实施例中,前置放大器141可以通过使用偏移电路71a来控制二极管接法晶体管tre的电流驱动力。

179.偏移电路71a被连接到节点ndd、节点nde和接地端子vss。

180.偏移电路71a包括晶体管trp和trq。

181.晶体管trp的一个端子被连接到节点ndd。晶体管trp的另一个端子被连接到晶体管trq的一个端子。晶体管trq的另一个端子被连接到接地端子vss。晶体管trp的栅极被连接到节点nde(和晶体管tre的栅极)。信号ofst1被提供给晶体管trq的栅极。

182.根据信号ofst1的信号电平来激活或不激活偏移电路71a。晶体管trq是根据信号ofst1的信号电平来被开/关控制的。

183.偏移电路71a将给定大小的偏移值添加到基于所选择的单元mc-s中的单元电流icell的镜像电流imr上以偏移由前置放大器141获得的感测结果。偏移电路71a使得偏移电流iofst1从节点ndd流到接地端子vss以将偏移值添加到电流imr上。

184.在处于激活状态的偏移电路71a中,偏移电流iofst1从节点ndd经由晶体管trp和trq的电流路径(沟道)流到接地端子vss。

185.当偏移电路71被设定在激活状态时,信号ofst1的信号电平被设定在“h(高)”电平。晶体管trq通过“h”电平信号ofst1被设定在on状态。处于on状态的晶体管trq将晶体管trp电连接到接地端子vss。在这种情况下,偏移电流iofst1在晶体管trp和trq的电流路径中流动。

186.偏移电路71a将电流iofst1从节点ndd拉到接地端子vss。

187.当偏移电路71a被设定在非激活状态时,信号ofst1的信号电平被设定在“l(低)”电平。“l”电平信号ofst1将晶体管trq设定在off状态。处于off状态的晶体管trq将晶体管trp与接地端子电断开。在这种情况下,偏移电流iofst1不在晶体管trp和trq的电流路径中流动。

188.例如,偏移电流iofst1的电流值小于镜像电流(从晶体管trd输出的电流)imr的电流值。偏移电流iofst1的电流值的大小根据晶体管trp的电流驱动力来设定。

189.晶体管trp的电流驱动力可以根据晶体管trp的栅极尺寸(晶体管trp的栅极宽度)来设定。晶体管trp的栅极宽度小于晶体管tre的栅极宽度。例如,晶体管trp的栅极宽度被设定为晶体管tre的栅极宽度的大约0.1倍至0.2倍。在这种情况下,偏移电流iofst1的电流值是从晶体管trd输出的电流imr的电流值的大约0.1倍至0.2倍。

190.以这种方式,基于晶体管trp的栅极尺寸来设定偏移电流iofst1的电流值的上限。

191.偏移电流iofst1的电流值根据被施加到晶体管trp的栅极的节点nde的电位改变,其中,基于晶体管trp的栅极尺寸的电流值是上限。

192.以这种方式,在该实施例中,偏移电路71a可以增加晶体管(二极管接法晶体管)tre的驱动力。

193.以上配置允许前置放大器141在(稍后将描述的)基于自参考方案的读操作时在节点nde和节点ndf中分别保持与给定存储单元mc中的多个单元电流分别对应的多个信号(电压)。

194.节点nde的电位于存储单元mc中的单元电流icell和前置放大器141中的镜像电流imr相对应。因此,节点nde的电位包括在存储单元mc和前置放大器141中的元件(例如,晶体管tr)之中的特性变化的影响。因此,在存储单元mc和晶体管tr之中的特性变化的影响可以被反映在偏移电流iofst1的电流值中。

195.由于该原因,根据该实施例的mram 1可以通过使用偏移电路71a来减小在存储单元mc和晶体管tr之中的pvt(工艺-电压-温度)变化对于感测结果的影响。

196.因此,根据该实施例的mram 1可以自动减小在存储单元mc和晶体管tr之中的特性变化对于感测结果的不利影响。这允许根据该实施例的mram 1缩短节点nde和ndf的充电时间(信号电压的上升时间和下降时间)。

197.根据该实施例的mram 1可以通过在前置放大器141中提供偏移电流iofst1来增加电压vsmpl与电压veval之间的电位差。这允许根据该实施例的mram 1提高读裕度。这允许根据该实施例的mram 1提高数据读取的可靠性。

198.根据该实施例的mram 1可以通过使用包括偏移电路71的前置放大器141来改进读操作特性。

199.(1b)操作

200.将参考图9、图10、图11和图12描述根据该实施例的存储设备(例如,mram)的操作的示例。下面将描述根据实施例的mram中的存储单元mc中的数据读操作。

201.注意,在根据该实施例的mram中,数据通过已知的数据写入技术被写入存储单元mc。因此,将省略数据写操作的描述。

202.(1b-1)基于自参考方案的读操作

203.图9是用于说明根据该实施例的mram中的基于自参考方案的读操作的流程图。图9示出了在从给定存储单元mc中读取数据时执行的各种类型的处理。

204.《st10》

205.如图9所示,在基于自参考方案的读操作中,在步骤st10中,mram1从存储单元(所选择的单元)mc-s读取第一数据作为数据读取目标(在下文中也将被称为第一单元访问处理)。控制电路17控制读电路14(例如,前置放大器141)以执行第一单元访问处理。

206.第一单元访问处理包括通过访问所选择的单元mc-s来将前置放大器141的节点nde充电到基于被存储在所选择的单元mc-s中的数据(在本文中被称为用户数据)的电压vsmpl的处理。

207.以这种方式,在第一单元访问处理中,控制电路17将节点nde充电到基于步骤st10中被存储在所选择的单元mc-s中的数据的电压vsmpl。作为结果,在第一单元访问处理中,前置放大器141感测电压vsmpl作为来自所选择的单元mc-s的信号。

208.《st20》

209.在基于自参考方案的读操作中,在步骤st20中,mram 1执行针对所选择的单元mc-s的预定数据写入(在下文中被称为重置写入处理)。

210.控制电路17控制写电路13以用于重置写入处理。

211.重置写入处理包括通过将预定数据(在下文中被称为参考数据或重置数据)写入所选择的单元mc-s来重置被存储在所选择的单元mc-s中的数据的处理。

212.在该实施例中,通过重置写入处理,“0”数据被写入所选择的单元mc-s。然而注意,通过重置写入处理,“1”数据也可被写入所选择的单元mc-s。

213.《st30》

214.在基于自参考方案的读操作中,在重置写入处理之后,在步骤st30中,mram 1执行关于所选择的单元mc-s的第二次数据读取(在下文中也被称为第二单元访问处理)。控制电路17控制读电路14(例如,前置放大器141)以用于第二单元访问处理。

215.第二单元访问处理包括访问所选择的单元mc-s并将前置放大器141的节点ndf充

电到基于所选择的单元mc-s中的数据的电压veval的处理。

216.以这种方式,在第二单元访问处理中,,控制电路17将节点ndf充电到基于在步骤st20中被写入所选择的单元mc-s的参考数据的电压veval。作为结果,在第二单元访问处理中,前置放大器141感测电压veval作为来自所选择的单元mc-s的信号。

217.在该实施例中,控制电路17在第二单元访问处理中控制前置放大器141的偏移电路71a的操作。偏移电路71a在第二单元访问处理时将给定大小的偏移值添加到感测结果(例如,基于单元电流的镜像电流)。

218.《st40》

219.在基于自参考方案的读操作中,在步骤st40中,mram 1执行感测处理。控制电路17控制读电路14(例如,感测放大器142)以用于感测处理。

220.感测处理包括将在步骤st10中被充电到节点nde的电压vsmpl与在步骤st30中被充电到节点ndf的电压veval进行比较的处理。采用该处理,感测放大器142确定被存储在所选择的单元mc-s中的数据(用户数据)是否与参考数据相同。

221.如上所述,根据该实施例的mram 1可以通过基于自参考方案的读操作来从所选择的单元mc-s中读取数据。

222.(1b-2)操作示例

223.图10是用于说明根据该实施例的mram的读操作的时序图。图10示出了在图9所示的基于自参考方案的读操作中的各种类型的处理中被提供给前置放大器141和感测放大器142的各种类型的信号和被充电到节点nde和ndf的电压。注意,在图10中的情况下,示出了在重置写入处理中“0”数据作为参考数据被写入所选择的单元mc-s作为读取目标的示例。

224.在发出对用于根据该实施例的mram 1的操作的请求时,外部设备9向根据实施例的mram 1发送命令cmd、地址adr、和控制信号cnt。mram 1接收命令cmd、地址adr、和控制信号cnt。控制电路17根据命令cmd执行针对基于地址adr的存储单元(所选择的单元)的操作。

225.当命令cmd指示读操作时,在根据该实施例的mram 1中,控制电路17执行用于执行基于自参考方案的读操作的各种类型的控制。

226.《时间t0至时间t3:s10》

227.如图10所示,在基于自参考方案的读操作时,控制电路17基于用于基于自参考方案的读操作的处理序列,在包括从时间t0至时间t2的间隔的时段中执行第一单元访问处理(第一次数据读取)。

228.控制电路17激活读电路14的前置放大器141。前置放大器141在控制电路17的控制下控制各种类型的信号的信号电平。

229.在时间t0,前置放大器141将信号ren的信号电平从“l”电平改变到“h”电平。在前置放大器141中,晶体管tr1被设定在on状态。前置放大器141将预定电压vclmp施加到晶体管tr2的栅极。晶体管tr2控制被连接到所选择的单元mc-s的位线(所选择的位线)bl的电位。

230.例如,读电路14(例如,前置放大器141)将接地电压vss施加到被连接到所选择的单元mc-s的字线(所选择的字线)wl。采用该操作,预定电压(在下文中也被称为读取电压)被施加到读取目标所选择的单元mc-s。

231.读取电压(或由读取电压产生的电流)的施加将所选择的单元mc-s中的开关元件

20设定在on状态。这使得所选择的单元mc-s访问前置放大器141。

232.图11示意性地示出在基于自参考方案的读操作中的第一单元访问处理时在根据该实施例的mram中的前置放大器的内部状态。

233.如图11所示,所选择的单元mc-s经由处于on状态的晶体管tra和trb被电连接到前置放大器141中的电流镜电路70的晶体管trc。

234.在时间t0之后,单元电流icell1在(位线bl与字线wl之间的)所选择的单元mc-s中流动。单元电流icell1的电流值与所选择的单元mc-s中的用户数据(mtj元件的电阻状态)相对应。节点ndc的电位(电压值)根据单元电流icell1的幅度来变化。

235.包括晶体管trc和trd的电流镜电路70使得基于单元电流icell1的镜像电流imr1(节点ndc的电位)流入节点ndd。当晶体管trd的栅极尺寸(例如,栅极宽度)与晶体管trc的栅极尺寸(例如,栅极宽度)基本上相同时,从晶体管trd输出的镜像电流imr1的电流值基本上等于单元电流icell1的电流值。

236.前置放大器141将信号s2的信号电平设定在“l”电平,并将信号s2b的信号电平设定在“h”电平。这将mos开关sw2的晶体管trh和tri设定在off状态。节点ndd通过处于off状态的mos开关sw2而与节点ndf电断开。

237.在时间t1,前置放大器141将信号s1的信号电平从“l”电平改变到“h”电平,并将信号s1b的信号电平从“h”电平改变到“l”电平。这将mos开关sw1的晶体管trf和trg设定在on状态。节点ndd经由处于on状态的mos开关sw1被电连接到节点nde。

238.在该实施例中,前置放大器141在第一单元访问处理时将信号ofst1的信号电平维持在“l”电平。这将偏移电路71a设定在非激活状态。在晶体管trp中没有电流流动。

239.因此,在第一访问处理时,偏移电路71a不向镜像电流imr1施加偏移电流iofst1。

240.镜像电流imr1作为电流ismpl1从节点ndd经由处于on状态的mos开关sw1流到节点nde。用所提供的电流ismpl1来对节点nde的电容分量c1充电。流入节点nde的电流ismpl1的电流值基本上等于从电流镜电路70输出的镜像电流imr1的电流值。

241.采用该操作,节点nde的电容分量c1被充电到具有给定电压值的电压(在下文中也被称为充电电压)vsmpl。例如,电压vsmpl的电压值(节点nde的电位)从接地电压vss上升到给定电压值。

242.充电电压vsmpl的电压值可以具有与电流ismpl1的电流值对应的大小。节点nde的电压vsmpl的电压值在所选择的单元mc-s中的用户数据是“0”数据时与所选择的单元mc-s中的用户数据是“1”数据时之间稍微不同。

243.例如,“0”数据被存储在所选择的单元mc-s中时的电压vsmpl的电压值是“v1”。“1”数据被存储在所选择的单元mc-s中时的电压vsmpl具有比电压值v1低了值δa(》0)的电压值(v1-δa)。

244.例如,节点nde的电压vsmpl的电压值在时间ta稳定。

245.随后,在时间2,前置放大器141将信号s1的信号电平从“h”电平改变到“l”电平,并将信号s1b的信号电平从“l”电平改变到“h”电平。

246.这将mos开关sw1的晶体管trg和trf设定在off状态。节点nde通过处于off状态的mos开关sw1而与节点ndd电断开。结果,节点nde的充电停止。

247.在时间t3,前置放大器141将信号ren的信号电平从“h”电平改变到“l”电平。这将

晶体管tra设定在off状态。前置放大器141通过处于off状态的晶体管tra而与所选择的单元mc-s电断开。

248.结果,电流(和电压)从前置放大器141到所选择的单元mc-s的提供停止。

249.以这种方式,基于自参考方案的读操作中的第一单元访问处理终止。

250.《时间t4至时间t5:s20》

251.在根据该实施例的mram 1中的基于自参考方案的读操作中,控制电路17在从时间t4至时间t5的间隔中执行重置写入处理。

252.在时间t4,控制电路17将用于写电路13的控制信号cnt-wr的信号电平从“l”电平改变到“h”电平。这将写电路13设定在激活状态。写电路13在提供了写电流时将参考数据(例如,“0”数据)写入所选择的单元mc-s。这将所选择的单元mc-s设定在重置状态(参考数据保持状态)。

253.注意,在重置写入处理中,前置放大器141的节点ndf被设定在浮动状态。由于该原因,节点ndf的电位可以降低到例如接近接地电压vss。

254.在时间t5,控制电路17将信号cnt-wr的信号电平从“h”电平改变到“l”电平。“l”电平信号cnt-wr将写电路13设定在非激活状态。写电路13停止向所选择的单元mc-s提供写电流。

255.以这种方式,基于自参考方案的读操作中的重置写入处理终止。

256.《时间t6至时间t9:s30》

257.在mram 1中的基于自参考方案的读操作时,控制电路17在从时间t6至时间t9的间隔中执行第二单元访问处理。

258.控制电路17激活前置放大器141。前置放大器141在控制电路17的控制下控制各种类型的信号的信号电平。

259.在时间t6,前置放大器141将信号ren从“l”电平改变到“h”电平。晶体管tra被设定在on状态。预定电压被施加到所选择的单元mc-s。所选择的单元mc-s中的开关元件20通过所施加的电压(或电流)而被设定在on状态。这使得前置放大器141访问所选择的单元mc-s。

260.图12示意性地示出在基于自参考方案的读操作中的第二单元访问处理时在根据该实施例的mram中的前置放大器的内部状态。

261.如图12所示,在第二访问处理时,基于参考数据(在这种情况下是“0”数据)的单元电流icell2在所选择的单元mc-s中流动。电流镜电路70使得基于单元电流icell2(参考电流iref)的镜像电流imr2流入节点ndd。

262.晶体管tre根据被施加到栅极的电压vsmpl而使电流ix从节点ndd流到接地端子vss。

263.前置放大器141将信号s1的信号电平设定在“l”电平,并将信号s1b的信号电平设定在“h”电平。这将mos开关sw1的晶体管trf和trg设定在off状态。节点nde通过处于off状态的mos开关sw1而与节点ndd电断开。节点nde维持充电状态(电压vsmpl的保持状态)。

264.在时间t7,前置放大器141将信号s2的信号电平从“l”电平改变到“h”电平,并将信号s2b的信号电平从“h”电平改变到“l”电平。这将mos开关sw2的晶体管trr和tri设定在on状态。节点ndd经由处于on状态的mos开关sw2被电连接到节点ndf。

265.这使电流ieval1流入节点ndf。

266.在该实施例中,在第二单元访问处理时,控制电路17使前置放大器141偏移(移位)单元电流icell2。

267.前置放大器141将信号ofst1的信号电平从“l”电平改变到“h”电平。“h”电平信号ofst1激活偏移电路71a。“h”电平信号ofst1被提供到偏移电路71a的晶体管trq的栅极。这将晶体管trq设定在on状态。

268.偏移电路71a的晶体管trp经由处于on状态的晶体管trq被连接到接地端子vss。这使晶体管trp输出偏移电流iofst1。

269.如上所述,偏移电流iofst1具有与晶体管trp的电流驱动力(例如,晶体管trp的栅极宽度)和栅极电压对应的电流值。例如,晶体管trp的栅极宽度被设定为晶体管trd的栅极宽度的大约0.1倍至0.2倍。在这种情况下,偏移电流iofst1的电流值是从晶体管trd输出的镜像电流imr2的电流值的大约0.1倍至0.2倍。

270.偏移电流iofst1的电流值根据被施加到晶体管tre的栅极的电压vsmpl而变化。

271.偏移电路71a将偏移电流iofst1施加到节点ndd。采用该操作,偏移电流iofst1被添加到基于单元电流icell的镜像电流imr2。偏移电流iofst1从节点ndd经由处于on状态的晶体管trp和trq流到接地端子vss。以这种方式,在偏移电路71a中,处于on状态的晶体管trp和trq将流入节点ndd的镜像电流imr2的一部分(偏移电流iofst1)拉到接地端子vss。

272.结果,在第二单元访问处理时的镜像电流imr2根据与晶体管tre的驱动力对应的电流ix和与晶体管trp的驱动力对应的偏移电流iofst1来偏移。

273.以这种方式,在该实施例中,晶体管trp可以增加晶体管tre的驱动力(输出电流)。

274.在第二单元访问处理时,晶体管trp被在第一单元访问处理时获得的充电电压vsmpl驱动。充电电压vsmpl可包括在所选择的单元和前置放大器中的元件之中的变化(例如,pvt变化)的影响。因此,特性变化的影响可以被反映在偏移电流iofst1的电流值中。

275.用偏移电流iofst1被施加到的电流ieval1来对节点ndf的电容分量c2充电。节点ndf的充电电压veval在时间tb饱和。

276.在第二单元访问处理时,来自由充电电压vsmpl驱动的晶体管tre的电流ix被施加到流入节点ndf的电流。将充电电压vsmpl施加到栅极将使晶体管tre流动电流ix。电流ix的电流值与充电电压vsmpl的电压值v1或电压值v1-δa相对应。

277.另外,在偏移电路71a中,充电电压vsmpl被施加到晶体管trp的栅极。因此,偏移电流iofst1的电流值与充电电压vsmpl的电压值v1或电压值v1-δa相对应。

278.如上所述,根据在第一单元访问处理时的所选择的单元mc-s中的用户数据,节点nde的充电电压vsmpl包括在用户数据是“1”数据时被设定的电压vsmpl的电压值与在用户数据是“1”数据时被设定的电压vsmpl的电压值之间的微小差异δa。该差异δa引起在第二单元访问处理时在晶体管tre和trp中流动的电流的幅度的变化。因此,流入节点ndf的电流(被提供到电容分量c2的电流)ieval1的幅度根据所选择的单元mc-s中的用户数据来改变。

279.以这种方式,在充电之后的节点ndf的电压veval的电压值根据通过第一单元访问处理获得的感测结果(vsmpl)来改变。

280.例如,在充电电压vsmpl的电压值是“v1”时(在用户数据是“0”数据时)的电流ix的电流值大于在充电电压vsmpl的电压值是“v1-δa”时(在用户数据是“1”数据时)的电流ix的电流值。

电平信号sen将晶体管tr4、tr5和tr6设定在off状态。采用该操作,处于off状态的晶体管tr5和tr6停止向节点nd2和nd3提供电源电压vdd。节点nd2通过处于off状态的晶体管tr4而与节点nd3电断开。

302.注意,在从时间t10至时间t11的间隔中,信号latn的信号电平被设定在“l”电平,并且信号latnb的信号电平被设定在“h”电平。这在从时间t10至时间t11的间隔中将晶体管tr1、tr11和tr12设定在off状态。

303.节点nd2和nd4经由处于on状态的晶体管tr9被电连接到节点nd6。节点nd3和nd5经由处于on状态的晶体管tr10被电连接到节点nd7。

304.节点nde的电压vsmpl被施加到晶体管tr13的栅极。晶体管tr13使与电压vsmpl的电压值对应的电流i1流入节点nd2。

305.节点ndf的电压veval被施加到晶体管tr14的栅极。晶体管tr14使与电压veval的电压值对应的电流i2流入节点nd3。

306.在该实施例中,在由感测放大器142进行感测处理时,偏移电路72a和72b基于信号shftdo和shftdob来操作。为了使电流i1和i2偏移,激活两个偏移电路72a和72b中的一个。

307.例如,在第二单元访问处理时,当前置放大器141已通过使用偏移电流iofst1来使单元电流icell2(镜像电流imr2)偏移时,信号shftdo的信号电平被设定在“h”电平,并且信号shftdob的信号电平被设定在“l”电平。这激活在晶体管tr14侧的偏移电路72b并且未激活在晶体管tr13侧的偏移电路72a。

308.在偏移电路72a中,“l”电平信号shftdob将晶体管tr15设定在off状态。晶体管tr16通过处于off状态的晶体管tr17而与节点nd6电断开。因此,偏移电路72a不使任何偏移电流流动。

309.在偏移电路72b中,“h”电平信号shftdo将晶体管tr17设定在on状态。晶体管tr18被电连接到节点nd7。晶体管tr18使与被施加到栅极的电压vshft对应的电流ishftb流动。偏移电流ishftb从节点nd7流到被连接到偏移电路72b的接地端子vss。

310.结果,作为电流i2和电流ishftb的和的电流i2+ishftb流入节点nd3。

311.以这种方式,根据该实施例的mram 1可通过使用偏移电路72a和72b来使感测放大器142中的电流i1和i2中的一个偏移。这允许感测放大器142可靠地使电压vsmpl(电流ismpl1和电流i1)的幅度与电压veval(电流ieval1和电流i2)的幅度不同。

312.这允许根据该实施例的mram 1进一步基于电压vsmpl和电压veval来增加读裕度。

313.注意,偏移电流ishft(ishfta,ishftb)的电流值根据电压vshft(vshfta,vshftb)的幅度来设定。电压vshft的幅度可以基于针对mram的测试过程、mram的规格、mram在使用后的调节等来适当地设定。然而注意,偏移电流ishft的电流值被设定为电流i1和i2的电流值的大约0.1倍至0.2倍。

314.节点nd2的电位根据电流i1的幅度来改变。节点nd3的电位根据电流i2+ishftb的幅度来改变。

315.电流i1与电流i2+ishftb之间的幅度关系根据电压vsmpl的电压值和电压veval的电压值来改变。

316.当电压vsmpl的电压值大于电压veval的电压值时,电流i1的电流值大于电流i2+ishftb的电流值。在这种情况下,节点nd2的电位的变化量(在这种情况下是放电量)大于节

点nd3的电位的变化量(在这种情况下是放电量)。因此,节点nd2的电位低于节点nd3的电位。

317.当电压vsmpl的电压值小于电压veval的电压值时,电流i1的电流值小于电流i2+ishftb的电流值。在这种情况下,节点nd2的放电量小于节点nd3的放电量。因此,节点nd2的电位高于节点nd3的电位。

318.以这种方式,基于由前置放大器141感测的电压vsmpl与电压veval之间的幅度关系,在节点nd2与节点nd3之间出现电位差。由于晶体管tr2、tr3、tr7和tr8的正反馈,节点dn2与节点nd3之间的电位差增加。

319.在时间t12,感测放大器142将信号latn的信号电平从“h”电平改变到“l”电平,并将信号latnb的信号电平从“l”电平改变到“h”电平。晶体管tr1、tr11和tr12被设定在on状态。通过处于on状态的晶体管,晶体管tr1、tr11和tr12将节点nd2和nd3电连接到电源端子vdd或接地端子vss。

320.根据节点nd2与nd3之间的幅度关系,这将节点nd2和节点nd3的电位放大到电源电压vdd或接地电压vss。

321.例如,当节点nd2的电位低于节点nd3的电位(电压vsmpl的电压值大于电压veval的电压值)时,节点nd2的电位下降到大约接地电压vss,并且节点nd3的电位上升到大约电源电压vdd。

322.在这种情况下,节点nd2被设定在“l”电平信号(数据)的保持状态,并且节点nd3被设定在“h”电平信号(数据)的保持状态。

323.例如,当节点nd2的电位高于节点nd3的电位(电压vsmpl的电压值小于电压veval的电压值)时,节点nd2的电位上升到大约电源电压vdd,并且节点nd3的电位下降到大约接地电压vss。

324.在这种情况下,节点nd2被设定在“h”电平信号的保持状态,并且节点nd3被设定在“l”电平信号的保持状态。

325.作为感测处理的结果,当节点nd2的电位低于节点nd3的电位时,信号do的信号电平是“l”电平,信号dob的信号电平是“h”电平。因此,“0”数据作为信号do从感测放大器142的输出端子ot1输出,“1”数据作为信号dob从感测放大器142的输出端子ot2输出。

326.与此相反,当节点nd2的电位高于节点nd3的电位时,信号do的信号电平是“h”电平,信号dob的信号电平是“l”电平。采用该操作,“1”数据作为信号do从感测放大器142的输出端子ot1输出,“0”数据作为信号dob从感测放大器142的输出端子ot2输出。

327.以这种方式,基于节点nd2和nd3的电位的信号被区分为所选择的单元mc-s中的用户数据(被读取数据)。

328.在时间t13,感测放大器142将信号latn的信号电平从“h”电平改变到“l”电平,并将信号latnb的信号电平从“l”电平改变到“h”电平。处于off状态的晶体管tr1、tr11和tr12将节点nd2和nd3与电源端子vdd和接地端子vss电断开。

329.在时间t14,感测放大器142将信号sen的信号电平从“h”电平改变到“l”电平。处于on状态的晶体管tr2、tr3和tr4将节点nd2和nd3电连接到电源端子vdd。

330.在时间t15,感测放大器142将信号sen2的信号电平从“h”电平改变到“l”电平。处于off状态的晶体管tr9和tr10将节点nd2与节点nd6电断开,并将节点nd3与节点nd7电断

开。

331.这未激活感测放大器142。节点nd2和nd3被设定在预充电状态。

332.以这种方式,基于自参考方案的读操作中的感测处理终止。

333.通过读操作获得的数据do和dob经由输入/输出电路16被从读电路14传送到外部设备9。

334.在该实施例中,被读取数据(信号do)可以在给定定时处(例如,在与下一命令对应的操作之前)通过回写处理被写入所选择的单元mc-s。这将所选择的单元mc-s从重置状态改变到用户数据的保持状态。

335.以上述方式,根据该实施例的mram中的基于自参考方案的读操作终止。

336.(1c)特性

337.将参考图13、图14和图15描述根据该实施例的mram的读电路(前置放大器和感测放大器)的特性。

338.图13的(a)和(b)是示出根据该实施例的mram中的前置放大器的操作点特性的图。

339.图13的(a)是示出根据比较例的前置放大器的操作特性的图。图13的(b)是示出根据该实施例的mram中的前置放大器的操作点分析的图。

340.参考图13的(a)和(b)中的每一个,图的横坐标对应于电压,图的纵坐标对应于电流。

341.图13的(a)和(b)中的每一个指示与存储单元(所选择的单元)的数据保持状态有关的前置放大器中的电流镜电路的晶体管trd的电压-电流特性。

342.图13的(a)和(b)中的每一个指示与电压-电流特性对应的多条线m1-0、m1-1,m2-0、m2-1、m2a-0和m2a-1。

343.线m1-0指示当在第一单元访问处理时所选择的单元保持“0”数据(mtj元件处于p状态)时的晶体管trd的电压-电流特性。线m1-1指示当在第一单元访问处理时所选择的单元保持“0”数据(mtj元件处于p状态)时的晶体管trd的电压-电流特性。

344.线m2-0和m2a-0指示当在第一单元访问处理时所选择的单元保持“0”数据作为用户数据时在第二单元访问处理时的晶体管trd(例如,包括晶体管trd、tre和trp的构成元件)的电压-电流特性。线m2-1和m2a-1指示当在第一单元访问处理时所选择的单元保持“1”数据作为用户数据时在第二单元访问处理时的晶体管trd(例如,包括晶体管trd、tre和trp的构成元件)的电压-电流特性。

345.线d1指示前置放大器的晶体管(二极管接法晶体管)tre的电压-电流特性。

346.图13的(a)示出根据比较例的前置放大器的特性。根据比较例的前置放大器不包括偏移电路。

347.图13的(b)示出根据该实施例的mram中的前置放大器的特性。如上文所描述的,在该实施例中,前置放大器141包括偏移电路71a。在基于自参考方案的读操作中的第二单元访问处理时,偏移电路71a将偏移电流施加到与在单元电流对应的电流。

348.如图13的(a)所示,基于每个元件的电压-电流特性,当用户数据是“0”数据时通过第二单元访问处理获得的电压veval-0x与通过第一单元访问处理获得的电压vsmpl-0和vsmpl-1基本上相同。

349.当用户数据是“1”数据时通过第二单元访问处理获得的电压veval-1x高于通过第

一单元访问处理获得的电压vsmpl-0和vsmpl-1。

350.如图13的(b)所示,在该实施例中,采用偏移电路的针对第二单元访问处理的偏移操作,线m2-0移位到相对于线m2x-0更大的电流值侧。同样,线m2-1移位到相对于线m2x-1更大的电流值侧。

351.这使电压veval-0低于电压vsmpl。电压veval-1高于电压vsmpl。

352.以这种方式,在该实施例中,确保电压veval-0与电压vsmpl之间相对大的裕度。

353.图14是用于说明根据该实施例的mram中通过第一单元访问处理获得的电压与通过第二单元访问处理获得的电压之间的关系的示意图。

354.参考图14,图的横坐标对应于时间,图的纵坐标对应于电压值。参考图14,由于在用户数据是“0”数据时被设定的电压值与在用户数据是“1”数据时被设定的电压值之间的微小差异,因此,电压vsmpl通过一条线表示。

355.如图14所示,,通过前置放大器141中的偏移电路71a的偏移操作,电压veval-0的电压值移位到相对于比较例中的电压veval-0x更低的电位侧。

356.因此,该实施例中的在第一单元访问处理时感测的电压vsmpl与在第二单元访问处理时感测的veval-0之间的差大于比较例中的电压vsmpl与电压veval-0x之间的差。

357.以这种方式,在根据该实施例的mram中,对于与通过第二单元访问处理获得的感测结果对应的电压值,可以对于与通过第一单元访问处理获得的感测结果对应的电压值确保更大的读裕度。

358.结果,根据该实施例的mram可以提高数据读取可靠性。

359.如图14所示,由于稍后描述的原因,在根据该实施例的mram中,与在根据比较例的前置放大器中对于电压veval到达预定电压值所花费的时间段t1x相比,包括偏移电路71a的前置放大器141可以缩短对于电压veval到达预定电压值(例如,最大电压值的80%或最小电压值的80%)所花费的时间段t1。

360.图15是示出根据该实施例的mram中的前置放大器中的电压的时间变化的图。

361.图15的(a)是示出根据第一比较例的前置放大器的内部电压的时间变化的图。根据第一比较例的前置放大器的电路配置不包括偏移电路。图15的(b)是示出根据第二比较例的前置放大器的内部电压的时间变化的图。根据第二比较例的前置放大器的电路配置包括用具有固定值的电压输出偏移电流的偏移电路。图15的(c)是示出根据该实施例的mram中的前置放大器的内部电压的时间变化的图。

362.参考图15的(a)、(b)和(c)中的每一个,图的横坐标对应于时间,图的纵坐标对应于电压。

363.参考图15的(a)、(b)和(c)中的每一个,,属于组g1的多条线对应于当用户数据是“0”数据时的节点nde的充电电压vsmpl-0。属于组g2的多条线对应于当用户数据是“1”数据时的节点nde的充电电压vsmpl-1。属于组g3的多条线对应于当用户数据是“0”数据时的节点ndf的充电电压veval-0。属于组g4的多条线对应于当用户数据是“1”数据时的节点ndf的充电电压veval-1。

364.参考图15的(a)、(b)和(c)中的每一个,前置放大器141中的被连接到节点ndd的晶体管trd和tre的阈值电压的幅度被设定为实验中的参数。

365.参考图15的(a),电压veval-0与电压vsmpl-0和vsmpl-1之间的电压差相对小。因

此,如在第一比较例中,当前置放大器不包括偏移电路时,读电路中的读裕度是小的。

366.如图15的(b)所示,当用具有固定值的电压产生偏移电流时,根据存储单元特性的变化以及晶体管trd和tre的阈值电压的变化,在针对相应的电压vsmpl和veval的角条件(电压脉冲的前沿和后沿)下,电压值极大地变化。

367.在图15的(b)所示的情况中的前置放大器中,由于元件之间的特性变化的影响,其中每个信号电压从电压的前沿(后沿)到达给定电压值的时间段(在下文中被称为sdt(信号发展时间))相对长。

368.如图15的(c)所示,在根据该实施例的mram中,包括偏移电路71a的前置放大器141允许电压veval-0与电压vsmpl之间和电压veval-1与电压vsmpl之间的相对大的电压差。因此,根据该实施例的mram可获得大的读裕度。

369.在该实施例中,在前置放大器141中的偏移电路71a中,与单元电流icell对应的电压被施加到输出偏移电流的晶体管trp的栅极。

370.结果,在该实施例中,在偏移电流的幅度中反映对可包括特性变化的来自存储单元的单元电流的监测结果。前置放大器141可以将更适合的偏移值(偏移电流)施加到感测结果(单元电流)。

371.因此,根据该实施例的mram 1可以通过使用前置放大器141的偏移电路71a来减小pvt(工艺-电压-时间)变化对于感测结果(电压vsmpl和veval)的不利影响。

372.根据该实施例的mram 1可以利用pvt变化的影响的减小来缩短由前置放大器感测的电压的sdt(例如,时间段t1)。这允许根据该实施例的mram 1缩短读操作时段。

373.结果,根据该实施例的mram可以加速读操作。

374.图16是用于说明根据该实施例的mram中的读电路的特性的图。

375.图16是用于评估根据该实施例的mram中的读电路中的前置放大器和感测放大器的特性的图。

376.图16的(a)示出当仅根据该实施例的感测放大器将偏移施加到由前置放大器获得的感测结果时的读电路的特性。图16的(b)示出当仅前置放大器将偏移施加到由前置放大器获得的感测结果时的根据该实施例的mram中的读电路的特性。图16的(c)示出当前置放大器和感测放大器两者将偏移施加到由前置放大器获得的感测结果时的根据该实施例的mram中的读电路的特性。

377.参考图16的(a)、(b)和(c)中的每一个,图的横坐标对应于在感测放大器的偏移电路中使用的偏移电压(vshft),图的纵坐标对应于标准偏差(σ)。图16的(a)、(b)和(c)中的每一个示出感测放大器的偏移电压的σ图。

378.参考图16的(a)、(b)和(c)中的每一个,偏移电压为正的区域对应于其中信号shftdo的信号电平被设定在“h”电平并且信号shftdob的信号电平被设定在“l”电平的情况。参考图16的(a)、(b)和(c)中的每一个,偏移电压为负的区域对应于其中信号shftdo的信号电平被设定在“l”电平并且信号shftdob的信号电平被设定在“h”电平的情况。

379.参考图15的(a)、(b)和(c),当读电路(前置放大器和感测放大器)具有理想特性时,表示感测放大器142的偏移电压vshft与偏差σ之间的关系的σ图用直线表示。

380.如图16的(a)所示,当仅感测放大器142将偏移值施加到感测结果时,在等于或低于感测放大器142的偏移电路72的n型晶体管的阈值电压的电压范围(例如,图16的(a)、(b)

和(c)中的每一个中的区域rx)内,该图不用直线表示。

381.如图16的(b)所示,在该实施例中,当仅前置放大器141将偏移值施加到感测结果时,σ图用直线表示。

382.如图16的(c)所示,在该实施例中,当前置放大器141和感测放大器142两者将偏移值施加到感测结果时,在高于n型晶体管的阈值电压的电压区域中获得直线σ图。

383.以这种方式,根据该实施例的mram可以通过使用前置放大器的偏移电路和感测放大器的偏移电路来提高读裕度。

384.如图13、图14、图15和图16所示,根据该实施例的mram可以提高读操作特性和可靠性。

385.因此,可以改进根据该实施例的存储设备的特性。

386.(2)第二实施例

387.将参考图17、图18、图19和图20描述根据第二实施例的存储设备。

388.在根据该实施例的存储设备(例如,mram)中,读电路的前置放大器的配置与在第一实施例中描述的前置放大器的配置不同。

389.(2a)配置示例

390.图17是示出根据该实施例的mram中的读电路的前置放大器的配置的示例的等效电路图。

391.如图17所示,在该实施例中,前置放大器141中的偏移电路71b的连接位置与根据第一实施例的前置放大器中的偏移电路的连接位置不同。

392.在该实施例中,前置放大器141可以通过使用偏移电路71b来控制电流镜电路70的驱动力。

393.偏移电路71b被连接到前置放大器141中的节点ndc、节点ndd和电源端子vdd。

394.偏移电路71b包括晶体管trr和trs。每个晶体管trr、trs是p型电场效应晶体管。每个晶体管trr、trs具有两个端子和栅极。

395.晶体管trr的一个端子被连接到节点ndd。晶体管trr的另一个端子被连接到晶体管trs的一个端子。晶体管trs的另一个端子被连接到电源端子vdd。

396.晶体管trr的栅极与晶体管trc和trd的栅极共同连接到节点ndc。

397.信号ofst2被提供到晶体管trs的栅极。晶体管trs根据信号ofst2的信号电平被开/关控制。

398.当偏移电路71b被设定在非激活状态时,信号ofst2的信号电平被设定在“h”电平。“h”电平信号ofst2将晶体管trs设定在off状态。在这种情况下,偏移电路71b不使偏移电流iofst2流动。

399.当偏移电路71b被设定在激活状态时,信号ofst2的信号电平被设定在“l”电平。“l”电平信号ofst2将晶体管trs设定在on状态。在这种情况下,晶体管trr经由处于on状态的晶体管trs被电连接到电源端子vdd。这使得偏移电路71b使偏移电流iofst2流动。

400.在处于激活状态的偏移电路71b中,偏移电流iofst2从电源端子vdd经由晶体管trr和trs的电流路径(沟道)流到节点ndd。

401.偏移电路71b将偏移电流iofst2从电源端子vdd提供到节点ndd。采用该操作,偏移电路71b使流入节点ndd的电流的电流值增加了偏移电流iofst2的电流值。

402.偏移电路71b基于所选择的单元mc-s的单元电流icell来使镜像电流imr的幅度偏移。偏移电路71b将具有给定电流值的偏移电流iofst2施加到镜像电流imr。

403.偏移电流iofst2的幅度对应于晶体管trr的电流驱动力。

404.晶体管trr的电流驱动力可以根据晶体管trr的栅极尺寸(例如,晶体管trr的栅极宽度)来设定。

405.晶体管trr的栅极宽度小于晶体管tre的栅极宽度。偏移电流iofst2的电流值小于从晶体管trd输出的镜像电流imr的电流值。

406.例如,晶体管trr的栅极宽度被设定为晶体管trd的栅极宽度的大约0.1倍至0.2倍。在这种情况下,偏移电流iofst2的电流值是镜像电流imr的电流值的大约0.1倍至0.2倍。

407.偏移电流iofst2的幅度根据节点ndc的电位(例如,第一单元访问处理中的单元电流icell)来改变。

408.在该实施例中,偏移电路71b在基于自参考方案的读操作中的第一单元访问处理时将偏移电流iofst2施加到从节点ndd流到节点nde的镜像电流imr。

409.以这种方式,在该实施例中,偏移电路71b可以增加电流镜电路40的晶体管trd的驱动力。

410.(2b)操作的示例

411.将参考图18、图19和图20描述根据该实施例的mram的操作的示例。

412.图18是用于说明根据该实施例的mram的操作的示例的时序图。

413.根据该实施例的mram 1以与第一实施例相同的方式执行图9中的基于自参考方案的读操作。

414.《时间t0至时间t3:s10》

415.如图18所示,在根据该实施例的mram 1中,控制电路17在基于自参考方案的读操作中在从时间t0至时间t3的间隔中执行第一单元访问处理。

416.控制电路17激活读电路14的前置放大器141。前置放大器141在控制电路17的控制下控制各种类型的信号的信号电平。

417.在时间t0,前置放大器141将信号ren的信号电平从“l”电平改变到“h”电平。前置放大器141将预定电压vclmp提供到晶体管trb的栅极。

418.这使单元电流icell1在所选择的单元mc-s中流动。单元电流icell1具有与所选择的单元mc-s中的用户数据对应的电流值。

419.图19示意性地示出在根据该实施例的mram中的在基于自参考方案的读操作中的第一单元访问处理时的前置放大器的内部状态。

420.在前置放大器141中,电流镜电路70使基于单元电流icell1的镜像电流imr1流入节点ndd。

421.在时间t1,前置放大器141将信号s1的信号电平设定在“h”电平,并将信号s1b的信号电平设定在“l”电平。这将mos开关sw1的晶体管trg和trh设定在on状态。处于on状态的mos开关sw1将节点nde电连接到节点ndd。

422.注意,处于off状态的mos开关sw2将节点ndf与节点ndd电断开。

423.在该实施例中,偏移电路71b在第一单元访问处理时被激活。

424.前置放大器141在第一单元访问处理时将信号ofst2的信号电平从“h”电平改变到“l”电平。“l”电平信号ofst2将偏移电路71b设定在激活状态。采用该操作,偏移电路71b在第一单元访问处理时使偏移电流iofst2流动。

425.当偏移电路71b被设定在激活状态时,节点ndc的电位被施加到晶体管trr的栅极。在第一单元访问处理时,偏移电路71b使偏移电流iofst2流动。

426.偏移电流iofst2从电源端子vdd经由晶体管trr和trs的电流路径流到节点ndd。

427.偏移电流iofst2的电流值对应于从晶体管trr输出的电流的电流值。因此,偏移电流iofst2的电流值根据节点ndc的电位(单元电流icell1的幅度)在与晶体管trr的电流驱动力对应的范围内改变。

428.以这种方式,在该实施例中,晶体管trr可以增加晶体管trd的驱动力(输出电流)。

429.包括镜像电流imr1和偏移电流iofst2的电流作为电流ismpl2从节点ndd经由处于on状态的mos开关sw1流动到节点nde。用电流ismpl2对节点nde充电。在该实施例中,流入节点nde的电流ismpl2的电流值基本上等于镜像电流imr1的电流值和偏移电流iofst2的电流值的总和。

430.用电流ismpl2(镜像电流imr2+iofst2)对节点nde充电将使节点nde的充电电压vsmpl从接地电压vss升高到给定电压值。

431.如上文所描述的,当所选择的单元mc-s保持“0”数据时,充电电压vsmpl具有电压值v3。当所选择的单元mc-s保持“1”数据时,充电电压vsmpl具有低于电压值v3的电压值v3-δc。

432.例如,在时间ta,节点nde的电位饱和。

433.在时间t2,前置放大器141将信号s1的信号电平从“h”电平改变到“l”电平,并将信号s1b的信号电平从“l”电平改变到“h”电平。这将mos开关sw1设定在off状态。处于off状态的mos开关sw1将节点nde与节点ndd电断开。

434.在时间t3,前置放大器141将信号ren的信号电平从“h”电平改变到“l”电平。这将前置放大器141与所选择的单元mc-s电断开。

435.以这种方式,基于自参考方案的读操作中的第一单元访问处理终止。

436.《时间t4至时间t5:s20》

437.在根据该实施例的mram 1中,控制电路17在基于自参考方案的读操作中在从时间t3至时间t4的间隔中执行如在第一实施例中的重置写入处理。

438.在第一单元访问处理之后,在时间t4,写电路13被“h”电平控制信号cnt-wr激活。写电路13将参考数据(在这种情况下是“0”数据)写入所选择的单元mc中。这将所选择的单元mc-s设定在重置状态(参考数据的保持状态)。

439.在时间t5,写电路13未被“l”电平控制信号cnt-wr激活。

440.以这种方式,基于自参考方案的读操作中的重置写入处理终止。

441.《时间t6至时间t9:s30》

442.在从时间t6至时间t9的间隔中,控制电路17执行第二单元访问处理。

443.控制电路17激活前置放大器141。前置放大器141在控制电路17的控制下控制各种类型的信号的信号电平。

444.在时间t6,前置放大器141将信号ren从“l”电平改变到“h”电平。采用该操作,如同

在第一实施例中,前置放大器141经由处于on状态的晶体管tra访问所选择的单元mc-s。

445.图20是示出在读操作中的第二单元访问处理时的根据该实施例的mram中的前置放大器的内部状态的示意图。

446.如图20所示,与参考数据(在这种情况下是“0”数据)对应的单元电流icell2在所选择的单元mc-s中流动。

447.电流镜电路70使基于单元电流icell2的镜像电流imr2流入节点ndd。

448.在时间t7,前置放大器141将信号s1的信号电平设定在“l”电平,并将信号s1b的信号电平设定在“h”电平。这将mos开关sw1设定在off状态。处于off状态的mos开关sw1将节点nde与节点ndd电断开。节点nde维持充电状态(电压vsmpl的保持状态)。

449.前置放大器141将信号s2的信号电平从“l”电平改变到“h”电平,并将信号s2b的信号电平从“h”电平改变到“l”电平。这将mos开关sw2设定在on状态。这将节点ndd经由处于on状态的mos开关sw2电连接到节点ndf。

450.在第二单元访问处理时,节点nde的电压vsmpl将晶体管tre设定在on状态。

451.因此,晶体管tre使具有与充电电压vsmpl的电压值(v3或v3-δc)对应的电流值的电流ix从节点ndd流到接地端子vss。

452.在该实施例中,前置放大器141在第二单元访问处理时未激活偏移电路71b。前置放大器141将信号ofst2的信号电平设定在“h”电平。这将偏移电路71b设定在非激活状态。结果,没有偏移电流被提供到节点ndd。

453.镜像电流imr2流入节点ndd。另外,电流ix从节点ndd流到接地端子vss。

454.因此,在该实施例中,流入节点ndf的电流ieval2对应于“imr2-ix”。

455.电流ieval2的提供对节点ndf的电容分量c2进行充电。节点ndf的充电电压在时间tb饱和。

456.例如,当所选择的单元mc-s中的用户数据是“0”数据时,充电电压veval的电压值是“v4”。当所选择的单元mc-s中的用户数据是“1”数据时,充电电压veval的电压值变成比电压值v4小了给定值δd的值(v4-δd)。

457.以这种方式,在该实施例中,如同在第一实施例中,在当所选择的单元mc-s保持“0”数据时的充电电压veval的电压值与当所选择的单元mc-s保持“1”数据时的充电电压veval的电压值之间确保比差δc足够大的差δd。

458.另外,在该实施例中,如同在第一实施例中,在当用户数据是“0”数据时的电压veval与电压vsmpl之间确保相对大的裕度(电位差)。

459.在节点ndf的电压veval稳定后,在时间t8,前置放大器141将信号s2的信号电平从“h”电平改变到“l”电平,并将信号s2b的信号电平从“l”电平改变到“h”电平。处于off状态的mos开关sw2将节点ndf与节点ndd电断开。这停止对节点ndf进行充电。

460.前置放大器141将信号ren的信号电平从“h”电平改变到“l”电平。“l”电平信号ren将晶体管tra设定在off状态。处于off状态的晶体管tra停止将电流从前置放大器141提供到所选择的单元mc-s。

461.以这种方式,基于自参考方案的读操作中的第二单元访问处理终止。

462.《时间t10至时间t15:s40》

463.在基于自参考方案的读操作中的第二单元访问处理之后,控制电路17以与第一实

施例相同的方式执行感测处理。

464.如同在第一实施例中,感测放大器142控制信号sen2、sen和latn的信号电平。

465.节点nd2被电连接到节点nd6,并且节点nd3被电连接到节点nd7。

466.晶体管tr13使电流i1流入节点nd6。晶体管tr14使电流i2流入节点nd7。

467.在该实施例中,通过第一单元访问处理获得的感测结果(电压vsmpl)被偏移。

468.因此,偏移电路72a被激活,并且偏移电路72b未被激活。“h”电平信号shftdob将偏移电路72a中的晶体管tr15设定在on状态。晶体管tr16使电流ishfta从节点nd6流到接地端子vss。电流ishfta的电流值对应于电压vshfta。

469.采用该操作,偏移电流ishfta根据电压vsmpl被施加到流入节点nd6的电流i1。电流i1+ishfta流入节点nd2。

470.节点nd2的电位和节点nd3的电位根据电流i1+ishfta和电流i2来变化。节点nd2和nd3的电位通过来自晶体管tr1、tr11和tr12的电压vdd和vss的提供和晶体管tr2、tr3、tr7和tr8的正反馈来放大。

471.这确定节点nd2的电位和节点nd3的电位(信号do和dob的信号电平)。

472.以这种方式,基于自参考方案的读操作中的感测处理终止。

473.通过读操作获得的数据do和dob从读电路14经由输入/输出电路16被传送到外部设备9。

474.以上述方式,根据该实施例的mram中的基于自参考方案的读操作终止。

475.根据该实施例的mram 1可以获得与参考图13、图14、图15和图16所描述的效果基本上相同的效果。

476.因此,根据第二实施例的存储设备可以改进存储设备的特性。

477.(3)第三实施例

478.将参考图21和图22描述根据第三实施例的存储设备。

479.图21是用于说明根据该实施例的存储设备的操作的示例的示意图。图22是用于说明根据实施例的存储设备的操作的示例的时序图。

480.如图21所示,在上文所描述的根据第一实施例的mram 1的读电路中,前置放大器141的偏移电路71a可以在第二单元访问处理时不使任何偏移电流流动,并且可以在第一单元访问处理时使偏移电流iofst1z流动。

481.采用该操作,根据该实施例的mram在第一单元访问处理时将偏移电流iofst1z施加到基于处于用户数据的保持状态的所选择的单元mc-s中的单元电流icell1的镜像电流imr1。

482.例如,如图22所示,在第一单元访问处理期间的时间t1,前置放大器141将信号ofst1的信号电平从“l”电平改变到“h”电平。这将偏移电路71a设定在激活状态。

483.如图21所示,在该实施例中,在第一单元访问处理期间,偏移电路71a使偏移电流iofst1z从节点ndd流到接地端子vss。这将偏移电流iofst1z施加到基于单元电流icell1的镜像电流imr1。

484.用被施加了偏移电流iofst1z的镜像电流imr1对节点nde充电。

485.在第二单元访问处理时,前置放大器141将信号ofst1的信号电平维持在“l”电平。这在第二单元访问处理时将偏移电路71a设定在非激活状态。因此,在该实施例中,偏移电

路71a在第二单元访问处理期间不使任何偏移电流流动。

486.用没有被施加偏移电流的镜像电流imr2对节点ndf充电。

487.随后,,感测放大器142如同在第一实施例中地执行感测处理。然而注意,在第二实施例中,在感测放大器142中,偏移电路72a被激活,并且偏移电路72b未被激活。偏移电路72a中的偏移电流ishfta被施加到电流i1。

488.采用该操作,在该实施例中,所选择的单元mc-s中的数据被区分。

489.例如,在该实施例中,关于由偏移电路71a获得的感测结果的偏移方向与关于在第一实施例中获得的感测结果的偏移方向不同。在这种情况下,电压veval-0移位到比电压vsmpl(vsmpl-0或vsmpl-1)更高的电压值。

490.以这种方式,包括图8中的偏移电路71a的前置放大器141可以通过控制激活偏移电路71a的定时来控制关于感测结果的偏移方向。

491.根据该实施例的mram可以获得与参考图13、图14、图15和图16所描述的效果基本上相同的效果。

492.因此,根据第三实施例的存储设备可以获得与上文所描述的实施例相同的效果。

493.(4)第四实施例

494.将参考图23和图24描述根据第四实施例的存储设备。

495.图23是用于说明根据该实施例的存储设备(例如,mram)的操作的示例的示意图。图24是用于说明根据实施例的存储设备的操作的示例的时序图。

496.如图23所示,在根据第二实施例的mram 1的读电路中,前置放大器141的偏移电路71b可以在第一单元访问处理时不使任何偏移电流流动,并且可以在第二单元访问处理时使偏移电流iofst2z流动。

497.采用该操作,根据该实施例的mram在第二访问处理时将偏移电流iofst2z施加到基于处于参考数据的保持状态的所选择的单元mc-s中的单元电流icell2的镜像电流imr2。

498.例如,如图24所示,在第一单元访问处理时,前置放大器141将信号ofst1的信号电平维持在“h”电平。这在第一单元访问处理时将偏移电路71b设定在非激活状态。因此,在该实施例中,偏移电路71a在第一单元访问处理期间不使任何偏移电流流动。

499.用没有被施加偏移电流的镜像电流imr1对节点nde充电。

500.在第二单元访问处理期间的时间t6,前置放大器141将信号ofst1的信号电平从“h”水平改变到“l”电平。这激活偏移电路71b。

501.如图23所示,在该实施例中,在第二单元访问处理期间,偏移电路71b使偏移电流iofst2z从电源端子vdd流到节点ndd。这将偏移电流iofst2z施加到基于单元电流icell2的镜像电流imr2。

502.用被施加了偏移电流iofst2z的镜像电流imr2对节点ndf充电。

503.随后,,感测放大器142如同在上述的第二实施例中地执行感测处理。然而注意,在该实施例中,在感测放大器142中,偏移电路72a未被激活,并且偏移电路72b被激活。偏移电路72b将偏移电流ishftb施加到电流i2。

504.采用该操作,在该实施例中,所选择的单元mc-s中的数据被区分。

505.例如,在该实施例中,关于由偏移电路71b获得的感测结果的偏移方向与关于在第二实施例中获得的感测结果的偏移方向不同。在这种情况下,电压veval-0移位到比电压

vsmpl(vsmpl-0或vsmpl-1)更高的电压值。

506.以这种方式,包括图17中的偏移电路71b的前置放大器141可以通过控制激活偏移电路71b的定时来控制关于感测结果的偏移方向。

507.根据该实施例的mram 1可以获得与参考图13、图14、图15和图16所描述的效果基本上相同的效果。

508.因此,根据第四实施例的存储设备可以获得与上文所描述的实施例相同的效果。

509.(5)第五实施例

510.将参考图25描述根据第五实施例的存储设备。

511.图25是示出根据该实施例的存储设备(例如,mram)的配置的示例的电路图。

512.如图25所示,偏移电路71a包括多个场效应晶体管trp《0》至trp《j-1》,其中,j是等于或大于1的整数。使偏移电流流动的晶体管trp包括多个场效应晶体管。

513.多个晶体管trp《0》至trp《j-1》具有相同的栅极尺寸(例如,栅极宽度)或不同的栅极尺寸。

514.多个晶体管trp《1》至trp《j-1》的电流路径与晶体管trp《0》的电流路径并联连接。晶体管trp《1》至trp《j-1》的栅极被连接到晶体管trp《0》的栅极。

515.多个晶体管trp《0》至trp《j-1》有效地用作输出偏移电流iofst的一个晶体管(在下文中被称为偏移晶体管)trp。

516.根据由偏移电流iofst设定的电流值,对晶体管trp《0》至trp《j-1》进行修整。

517.例如,多个晶体管trp《1》至trp《j-1》中给定数量(k)个晶体管的栅极通过熔断、开关电路等与晶体管trq《0》的栅极电分离。在这种情况下,k是等于或大于0并且等于或小于j-1的整数。

518.因此,包括(j-k)个晶体管tr《0》至trp《j-k-1》的偏移晶体管trp的有效栅极宽度小于包括j个晶体管trp《0》至trp《j-1》的偏移晶体管trp的有效栅极宽度。

519.结果,被包括(j-k)个晶体管trp《0》至trp《j-k-1》的偏移晶体管trp引起流动的偏移电流iofst的电流值小于被包括j个晶体管trp《0》至trp《j-1》的偏移晶体管trp引起流动的偏移电流iofst的电流值。

520.以这种方式,根据偏移电路71a的晶体管trp《0》至trp《j-1》的数量,调整被晶体管trp引起流动的偏移电流iofst的电流值。

521.注意,要被修整的晶体管trp《0》至trp《j-1》的数量(k)通过mram1的测试过程来适当确定。

522.当被偏移电路71a使得流动的偏移电流的电流值具有期望幅度时,对于多个晶体管trp《0》至trp《j-1》有时不执行修整。

523.注意,电流镜电路70的晶体管trd可以包括多个场效应晶体管trd《0》至trd《h-1》,像晶体管trp(trp《0》至trp《j-1》)。在这种情况下,h是等于或大于1的整数。

524.这使得可以调整镜像电流imr相对于单元电流icell的幅度。例如,晶体管trd的栅极尺寸(晶体管trc与晶体管trd之间的电流比)根据被用于存储元件的mtj元件的磁阻值(或mr比)来适当设定。

525.根据该实施例的存储设备可以获得与上文所描述的实施例相同的效果。

526.(6)第六实施例

527.将参考图26描述根据第六实施例的存储设备。

528.图26是示出根据该实施例的存储设备(例如,mram)的配置的示例的电路图。

529.如图26所示,偏移电路71b可包括具有并联连接的电流路径的多个晶体管trr《0》至trr《j-1》。

530.多个晶体管trr《0》至trr《j-1》有效地用作输出偏移电流iofst的一个晶体管(在下文中被称为偏移晶体管)trr。

531.在这种情况下,如同在图25所示的情况下,偏移电流iofst的电流值可以通过修整多个晶体管trr《0》至trr《j-1》中预定数量的晶体管来调整。

532.注意,要被修整的晶体管trp《0》至trp《j-1》的数量(k)通过mram1的测试过程来适当地确定。当被偏移电路71b引起流动的偏移电流的电流值具有期望幅度时,多个晶体管trp《0》至trp《j-1》有时不被修整。

533.根据该实施例的存储设备可以获得与上文所描述的实施例的效果基本上相同的效果。

534.(7)第七实施例

535.将参考图27描述根据第七实施例的存储设备。

536.图27是示出根据该实施例的存储设备(例如,mram)的配置的示例的电路图。

537.如图27所示,一个前置放大器141可包括多个偏移电路71a和71b。

538.在该实施例中,在一个读操作时,两个偏移电路71a和71b中的一个被激活。采用该操作,对第一单元访问处理和第二单元访问处理中的一个中的感测结果提供偏移电流(偏移值)。

539.根据该实施例的存储设备可以获得与上文所描述的实施例基本上相同的效果。

540.(8)其他

541.根据实施例的存储设备不限于以上实施例,并且可以进行各种修改。

542.例如,根据上文所描述的每个实施例的存储单元mc包括磁阻效应元件和二端开关元件。然而注意,存储单元mc也可以包括磁阻效应元件和三端开关元件(例如,场效应晶体管)。

543.注意,根据以上实施例的存储设备以使用磁阻效应元件作为存储元件的存储设备(例如,mram)为例。

544.然而注意,根据该实施例的存储设备可使用与磁阻效应元件不同的可变电阻元件作为存储元件。

545.例如,存储设备可以是电阻随机存取存储器(例如,reram)或相变存储器(例如,pcram),只要它是使用通过使用元件的电阻的变化来存储数据的元件的设备。

546.根据该实施例的存储设备可以是易失性存储器或非易失性存储器。

547.虽然已经描述了某些实施例,但是这些实施例仅以示例的方式呈现,并且不旨在限制本发明的范围。实际上,可以以各种其他形式实现本文所描述的新颖实施例;此外,可以在不脱离本发明的精神下,对本文所描述的实施例的形式进行各种省略、替代和改变。所附的权利要求及其等同旨在覆盖如落在本发明的范围和精神内的这种形式或修改。

548.标记的说明

549.1:存储设备,10:存储单元阵列,11:行控制电路,12:列控制电路,13:写电路,14:

读电路,15:电压产生电路,16:输入/输出电路,17:控制电路,141:前置放大器,142:感测放大器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1