用于三稳态存储的存储单元

1.本技术涉及半导体技术领域,特别涉及一种用于三稳态存储的存储单元。

背景技术:

2.相关技术中,静态随机存储器(static random-access memory,sram)以交叉连接的cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)反相器作为核心存储单元,以实现0-1的双稳态锁存,存储逻辑0或者逻辑1。

3.然而,由于内部的cmos稳态电平固定为vdd或vss,故只能在二进制表示这一框架下存储数据,限制了信息存储效率的进一步提升,亟待解决。

技术实现要素:

4.本技术提供一种用于三稳态存储的存储单元,以解决相关技术中只能进行二进制数据的存储,导致存储效率低的问题,可以进行三进制数据的存储,不仅可以提升信息存储效率,且不会显著增加使用的器件数量。

5.本技术提供一种用于三稳态存储的存储单元,包括:

6.第一匀质反相器,所述第一匀质反相器由第一双极型场效应晶体管构成,用于存储三进制数据;

7.第二匀质反相器,所述第二匀质反相器由第二双极型场效应晶体管构成,用于存储三进制数据;

8.其中,所述第一匀质反相器的输入端口与所述第二匀质反相器的输出端口相连,得到节点电压vx,所述第二匀质反相器的输入端口与所述第一匀质反相器的输出端口相连,得到节点电压vy,以在所述节点电压vx和所述节点电压vy呈现稳态时,所述第一匀质反相器和所述第二匀质反相器交叉连接,用于于三稳态存储。

9.可选地,所述第一匀质反相器的第一供电端f1和第二供电端nf1及所述第二匀质反相器的第三供电端f2和第四供电端nf2供电。

10.可选地,所述第二供电端nf1和所述第四供电端nf2固定代表所述第一供电端f1和所述第三供电端f2电平相对于供电电平的余数。

11.可选地,所述第一匀质反相器和所述第二匀质反相器为顺置反相器或者倒置反相器。

12.可选地,所述节点电压vx和所述节点电压vy呈现稳态包括两个顺置反相器交叉连接呈现的(0,1)稳态或者(1,0)稳态,或者两个倒置反相器交叉连接呈现的(1,2)稳态或者(2,1)稳态,或者一个顺置反相器和一个倒置反相器交叉连接呈现的(2,0)稳态或者(0,2)稳态。

13.可选地,所述倒置反相器的上拉下拉网络比例等于所述顺置反相器的上拉下拉网络比例的倒数。

14.由此,通过将双极型场效应晶体管构成的匀质反相器进行交叉连接,实现三电平

电压状态,可以进行三进制数据的存储,解决了相关技术中只能进行二进制数据的存储,导致存储效率低的问题,不仅可以提升信息存储效率,且不会显著增加使用的器件数量。

15.本技术附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

附图说明

16.本技术上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

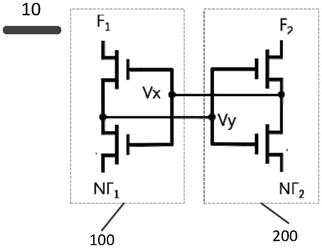

17.图1为根据本技术实施例提供的用于三稳态存储的存储单元的结构示意图;

18.图2为根据本技术一个实施例的顺置反相器的结构示例图。

19.图3为根据本技术一个实施例的顺置反相器的电压曲线示意图;

20.图4为根据本技术一个实施例的倒置反相器的结构示例图。

21.图5为根据本技术一个实施例的倒置反相器的电压曲线示意图;

22.图6为根据本技术一个实施例的三稳态存储的存储单元第一稳态时的曲线示意图;

23.图7为根据本技术一个实施例的三稳态存储的存储单元第二稳态时的曲线示意图;

24.图8为根据本技术一个实施例的三稳态存储的存储单元第三稳态时的曲线示意图;

25.图9为根据本技术另一个实施例的三稳态存储的存储单元第三稳态时的曲线示意图。

具体实施方式

26.下面详细描述本技术的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本技术,而不能理解为对本技术的限制。

27.下面参考附图描述本技术实施例的用于三稳态存储的存储单元。针对上述背景技术中心提到的相关技术中只能进行二进制数据的存储,导致存储效率低的问题,本技术提供了一种用于三稳态存储的存储单元,通过将双极型场效应晶体管构成的匀质反相器进行交叉连接,实现三电平电压状态,可以进行三进制数据的存储,解决了相关技术中只能进行二进制数据的存储,导致存储效率低的问题,不仅可以提升信息存储效率,且不会显著增加使用的器件数量。

28.具体而言,图1为本技术实施例所提供的一种用于三稳态存储的存储单元的结构示意图。

29.如图1所示,该用于三稳态存储的存储单元10包括:第一匀质反相器100和第二匀质反相器200。

30.其中,第一匀质反相器100由第一双极型场效应晶体管(ambipolar field effect transistor,afet)构成,用于存储三进制数据。第二匀质反相器200由第二双极型场效应晶体管构成,用于存储三进制数据;

31.其中,第一匀质反相器100和第二匀质反相器200的沟长相同,第一匀质反相器100的输入端口与第二匀质反相器200的输出端口相连,得到节点电压vx,第二匀质反相器200的输入端口与第一匀质反相器100的输出端口相连,得到节点电压vy,以在节点电压vx和节点电压vy呈现稳态时,第一匀质反相器100和第二匀质反相器200交叉连接,用于于三稳态存储。

32.具体地,如图1所示,本技术实施例中将将两个具有相同沟长组合的匀质反相器交叉连接,假设图1中左侧的反相器为第一匀质反相器100,右边的反相器为第二匀质反相器200,则第一匀质反相器100输入端口与第二匀质反相器200的输出端口相连,得到节点电压vx,第二匀质反相器200的输入端口与第一匀质反相器100的输出端口相连,得到节点电压vy。

33.可选地,在一些实施例中,第一匀质反相器100和第二匀质反相器200为顺置反相器或者倒置反相器。

34.可选地,在一些实施例中,倒置反相器的上拉下拉网络比例等于顺置反相器的上拉下拉网络比例的倒数。

35.应当理解的是,本技术的第一匀质反相器100和第二匀质反相器200完全由afet构成,由于双极型晶体管自身的特点,工作过程中,起始电平vmax’,上拉和下拉能够达到的最高电平vmax和最低电平vmin,以及终电平vmin’都不会完全达到供电电压的电平值,即vdd和vss;定义第一匀质反相器100和第二匀质反相器200中,vmax’和vmax统称上拉电平,vmin和vmin’统称下拉电平。设上拉器件的沟道长度为l2,下拉器件的沟道长度为l1,则上拉下拉网络之比z=l2/l1决定了vmax和vmin接近vdd和vss的程度;z越大,vmax越远离vdd,vmin越接近vss,反之亦然;另一方面,z还决定了反相器的阈值电平vt的电平位置,z越大,vt越靠近vss,反之则靠近vdd;

36.由此,本技术实施例可以得到具有合适电压传输曲线(voltage transfer curve,vtc)的匀质反相器。

37.为便于理解,本技术实施例取供电电压vdd=2v,vss=0v进行详细说明顺置反相器或者倒置反相器

38.如图2所示,设置合适的沟长比z=l2/l1后,在cadence中,以0.18um的工艺仿真实现了如图3所示的阈值电压vt在0.5v附近,上拉电平在1.0v附近,下拉电平在0v附近的匀质反相器,称这时的反相器为顺置反相器。

39.交换上述反相器的供电电平vdd和vss,获得如图4所示的电气配置,称这时的反相器为倒置反相器。

40.其中,倒置反相器的上拉下拉网络比例z等于顺置反相器的比例的倒数,因此,图4倒置反相器的vtc呈现出与图2所示的顺置反相器vtc对偶的性质,如图5所示,图5中曲线显示了阈值电压vt在1.5v附近,上拉电平在2.0v附近,下拉电平在1.0v附近;

41.由此,根据以上结果,假设电平0-0.5v可视作逻辑0,或简称0;电平0.75-1.25v可视作逻辑1,或简称1;电平1.5-2.0v可视作逻辑2,或简称2,即可得到表1所示的电平与逻辑值的对应的关系。

42.表1

43.电平逻辑值

0v-0.5v00.75v-1.25v11.5v-2.0v2

44.可选地,在一些实施例中,如图1所示,第一匀质反相器100的第一供电端f1和第二供电端nf1及第二匀质反相器200的第三供电端f2和第四供电端nf2供电。

45.其中,在一些实施例中,第二供电端nf1和第四供电端nf2固定代表第一供电端f1和第三供电端f2电平相对于供电电平的余数。

46.也就是说,本技术实施例可以将4个供电端分别给予f1、f2、nf1和nf2的供电,其中,nf1和nf2固定代表f1和f2电平相对于供电电平vdd的余数。

47.可选地,在一些实施例中,节点电压vx和节点电压vy呈现稳态包括两个顺置反相器交叉连接呈现的(0,1)稳态或者(1,0)稳态,或者两个倒置反相器交叉连接呈现的(1,2)稳态或者(2,1)稳态,或者一个顺置反相器和一个倒置反相器交叉连接呈现的(2,0)稳态或者(0,2)稳态。

48.具体地,当f1=2v,f2=2v时,如图6所示,图6中实线代表第一匀质反相器100的vtc,虚线代表第二匀质反相器200的vtc,这时相当于两个顺置反相器交叉连接,因此,(vx,vy)呈现出(0,1)或者(1,0)稳态。

49.当f1=0v,f2=0v时,如图7所示,图7中实线代表第一匀质反相器100的vtc,虚线代表第二匀质反相器200的vtc,这时相当于两个倒置反相器交叉连接,因此,(vx,vy)呈现出(1,2)或者(2,1)稳态。

50.当f1=2v,f2=0v,或f1=0v,f2=2v时,分别如图8和图9所示,图8和图9中实线代表第一匀质反相器100的vtc,虚线代表第二匀质反相器200的vtc,这时相当于顺置和倒置反相器交叉连接,因此,(vx,vy)呈现出(2,0)或者(0,2)稳态;

51.由此,通过对第一供电端f1和第三供电端f2进行指定,可以在同一硬件电路中实现3种不同的稳态电平,从而可以作为静态随机存储器的三态存储单元来使用。

52.根据本技术实施例提出的用于三稳态存储的存储单元,通过将双极型场效应晶体管构成的匀质反相器进行交叉连接,实现三电平电压状态,可以进行三进制数据的存储,解决了相关技术中只能进行二进制数据的存储,导致存储效率低的问题,不仅可以提升信息存储效率,且不会显著增加使用的器件数量。

53.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或n个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

54.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本技术的描述中,“n个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

55.应当理解,本技术的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,n个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。如,如果用硬件来实现和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

56.本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

57.此外,在本技术各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。所述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。

58.上述提到的存储介质可以是只读存储器,磁盘或光盘等。尽管上面已经示出和描述了本技术的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本技术的限制,本领域的普通技术人员在本技术的范围内可以对上述实施例进行变化、修改、替换和变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1