一种可校准的阻抗电路

1.本发明涉及阻抗电路技术领域,更为具体地说,涉及一种可校准的阻抗电路。

背景技术:

2.nand闪存物理接口是ssd(固态盘)或存储卡系统中数据通路的重要组成部分,为nand闪存和闪存控制器芯片之间的数据通信链路提供高速收发驱动接口电路。nand闪存物理接口电路的收发驱动电路通常需满足国际onfi标准的时序与阻抗匹配要求。对于onfi4.2,其中需支持nv-ddr、nv-ddr2和nv-ddr3等高速接口,因而对高速物理接口的信号完整性和阻抗匹配提出更为苛刻的要求。

3.高速nand闪存物理接口电路通常需包括ocd(on-chip driver)与odt(on-die termination)电路,为了驱动接口电路和实现阻抗匹配,ocd和odt电路的基本单元都是由非线性晶体管和线性无源阻抗串联组成。其中ocd的等效阻抗和odt的等效阻抗分别用ron和rtt表示。但由于受pvt(process、voltage、temperature)影响,接口电路中ocd和odt电路的输出性能会出现较大的起伏。在某些极端条件下,接口电路的阻抗变化会超出onfi 4.2标准规定的范畴,因此需要对接口电路中等效的ron和rtt阻抗进行校准。

技术实现要素:

4.有鉴于此,本发明提供了一种可校准的阻抗电路,有效解决现有技术存在的技术问题,在完成阻抗校准并且同时实现不同工作模式下需要的阻抗值的基础上,能够减少电路中驱动单元的数量,进而能够减小可校准的阻抗电路的占用面积。

5.为实现上述目的,本发明提供的技术方案如下:

6.一种可校准的阻抗电路,包括:控制电路和可控阻抗的驱动电路;

7.所述控制电路用于根据参考阻抗和不同工作模式下需要的等效阻抗值而输出选择信号、上拉转换校准码和下拉转换校准码;

8.所述可控阻抗的驱动电路包括:并联的多个驱动单元,所述驱动单元包括上拉可控阻抗模块和下拉可控阻抗模块,所述上拉可控阻抗模块一端与电源端相连、且另一端与io接口相连;及所述下拉可控阻抗模块的一端与接地端相连、且另一端与所述io接口相连,所述上拉可控阻抗模块和所述下拉可控阻抗模块均用于生成第一等效阻抗至第n等效阻抗,n为大于或等于2的整数;

9.所述可控阻抗的驱动电路用于根据工作模式信号中ocd_odt信号和所述选择信号,将所述上拉转换校准码转换为上拉驱动码,并通过所述上拉驱动码选择所述上拉可控阻抗模块工作而获取与所述参考阻抗匹配的等效阻抗;或将所述下拉转换校准码转换为下拉驱动码,并通过所述下拉驱动码选择所述下拉可控阻抗模块工作而获取与ocd工作模式下需要的等效阻抗值匹配的等效阻抗;

10.及,所述可控阻抗的驱动电路用于根据工作模式信号中ocd_odt信号、odt_en信号和所述选择信号,将所述上拉转换校准码转换为上拉驱动码,同时将所述下拉转换校准码

转换为下拉驱动码,并通过所述上拉驱动码选择所述上拉可控阻抗模块工作、且同时通过所述下拉驱动码选择所述下拉可控阻抗模块工作,而获取与odt工作模式下需要的等效阻抗值匹配的等效阻抗。

11.可选的,所述控制电路包括:逻辑电路、校准码产生电路和控制移位器;

12.所述校准码产生电路用于根据所述参考阻抗生成上拉校准码和下拉校准码;

13.所述逻辑电路用于根据所述不同工作模式下需要的等效阻抗值生成转换信号和所述选择信号,所述转换信号用于确定所述驱动单元的等效阻抗,其中,所述选择信号用于选择驱动单元进行工作;

14.所述控制移位器用于根据所述转换信号将所述上拉校准码转换为所述上拉转换校准码,及将所述下拉校准码转换为所述下拉转换校准码。

15.可选的,根据不同工作模式下需要的等效阻抗值和所述驱动单元生成的等效阻抗,确定所述转换信号和所述选择信号。

16.可选的,在所述ocd工作模式下,所述驱动单元的等效阻抗为所述第一等效阻抗至第n等效阻抗;其中,根据所述ocd工作模式下需要的等效阻抗值和所述驱动单元的等效阻抗,确定所述转换信号和所述选择信号,包括:

17.所述ocd工作模式下需要的等效阻抗值为50ω,且所述驱动单元生成的等效阻抗包括150ω,根据50=150/3,确定转换信号用于确定所述驱动单元生成等效阻抗为150ω,及所述选择信号用于选择3个生成等效阻抗为150ω的驱动单元工作;

18.所述ocd工作模式下需要的等效阻抗值为35ω,且所述驱动单元生成的等效阻抗包括150ω和300ω,根据35=(150/3)//(300/3),确定转换信号用于确定所述驱动单元生成等效阻抗为150ω或300ω,及所述选择信号用于选择3个生成等效阻抗为150ω的驱动单元和3个生成等效阻抗为300ω的驱动单元工作;

19.或者,所述ocd工作模式下需要的等效阻抗值为18ω,且所述驱动单元生成的等效阻抗包括(150//300//600)ω,在误差允许范围内根据18=(150//300//600)/5,确定转换信号用于确定所述驱动单元生成等效阻抗为(150//300//600),及所述选择信号用于选择5个生成等效阻抗为(150//300//600)的驱动单元。

20.可选的,在所述odt工作模式下,所述驱动单元的等效阻抗为所述第一等效阻抗/2至第n等效阻抗/2;其中,根据所述odt工作模式下需要的等效阻抗值和所述驱动单元的等效阻抗,确定所述转换信号和所述选择信号,包括:

21.所述odt工作模式下需要的等效阻抗值为30ω,且所述驱动单元生成的等效阻抗包括150ω,根据30=150/5,确定转换信号用于确定所述驱动单元生成等效阻抗为150ω,及所述选择信号用于选择5个生成等效阻抗为150ω的驱动单元。

22.可选的,所述可控阻抗的驱动电路包括多个模式选择电路,所述模式选择电路与所述驱动单元一一对应,所述模式选择电路用于接入所述工作模式信号、所述上拉转换校准码、所述下拉转换校准码和所述选择信号;

23.所述模式选择电路用于根据所述工作模式信号、所述上拉转换校准码、所述下拉转换校准码和所述选择信号生成所述上拉驱动码和/或所述下拉驱动码。

24.可选的,所述模式选择电路包括:第一与非门、第一非门、第二与非门、第一缓冲器、第一二选一选择器、第二二选一选择器、第二非门、或非门、第二缓冲器、第三与非门;

25.所述第一与非门的第一端接入所述选择信号,所述第一与非门的第二端接入所述上拉转换校准码,所述第一与非门的输出端与所述第一非门的输入端相连,所述第一非门的输出端与所述第二与非门的第一端相连,所述第二与非门的第二端与所述第一二选一选择器的输出端相连,所述第二与非门的输出端与所述第一缓冲器的输入端相连,所述第一缓冲器的输出端用于输出所述上拉驱动码;

26.所述第一二选一选择器的第一输入端接入ocd_odt控制信号,所述第一二选一选择器的第二输入端接入odt_en控制信号,所述第二二选一选择器的第一输入端接入所述ocd_odt控制信号,所述第二二选一选择器的第二输入端与所述第二非门的输出端相连,所述第二非门的输入端接入所述odt_en控制信号;

27.所述第二二选一选择器的输出端与所述或非门的第一端相连,所述或非门的输出端与所述第二缓冲器的输入端相连,所述第二缓冲器的输出端用于输出所述下拉驱动码,所述或非门的第二端与所述第三与非门的输出端相连,所述第三与非门的第一端接入所述选择信号,所述第三与非门的第二端接入所述下拉转换校准码。

28.可选的,所述上拉可控阻抗模块包括第一上拉晶体管至第m上拉晶体管及第一上拉阻抗至第m上拉阻抗,第i上拉晶体管的第一端与所述电源端相连,所述第i上拉晶体管的第二端与第i上拉阻抗的第一端相连,所述第i上拉阻抗的第二端与所述io接口相连,m为大于或等于2的整数,i为大于0且小于或等于m的整数;

29.所述下拉可控阻抗模块包括第一下拉晶体管至第m下拉晶体管及第一下拉阻抗至第m下拉阻抗,第i下拉晶体管的第一端与所述接地端相连,所述第i下拉晶体管的第二端与第i下拉阻抗的第一端相连,所述第i下拉阻抗的第二端与所述io接口相连。

30.可选的,所述第i上拉晶体管和所述第i下拉晶体管的导通类型相反。

31.相较于现有技术,本发明提供的技术方案至少具有以下优点:

32.本发明提供了一种可校准的阻抗电路,其中可控阻抗的驱动电路包括有多个等效阻抗的驱动单元,所述驱动单元包括上拉可控阻抗模块和下拉可控阻抗模块,且所有所述驱动单元的上拉可控阻抗模块之间并联,所述上拉可控阻抗模块一端与电源端相连、且另一端与io接口相连;及所有所述驱动单元的下拉可控阻抗模块之间并联,所述下拉可控阻抗模块的一端与接地端相连、且另一端与所述io接口相连,所述上拉可控阻抗模块和所述下拉可控阻抗模块均用于生成第一等效阻抗至第n等效阻抗。

33.由上述内容可知,本发明提供的技术方案,能够通过控制电路和可控阻抗的驱动电路配合实现不同工作模式下需要的等效阻抗。同时,本发明提供的可控阻抗的驱动电路包括有多个等效阻抗的驱动单元,且所有驱动单元的上拉可控阻抗模块之间并联,及所有驱动单元的下拉可控阻抗模块之间并联,进而能够通过独立的可控阻抗模块实现第一等效阻抗至第n等效阻抗,且能够通过并联的可控阻抗模块实现更多的等效阻抗,进而满足不同工作模式下需要的多个等效阻抗值,由此能够减少电路中驱动单元的数量,进而能够减小可校准的阻抗电路的占用面积。

附图说明

34.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本

发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

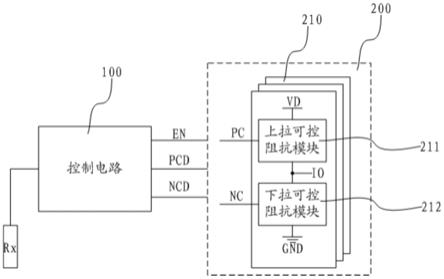

35.图1为本发明实施例提供的一种可校准的阻抗电路的结构示意图;

36.图2为本发明实施例提供的另一种可校准的阻抗电路的结构示意图;

37.图3为本发明实施例提供的一种模式选择电路的结构示意图;

38.图4为本发明实施例提供的一种驱动电路的结构示意图。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

40.正如背景技术所述,高速nand闪存物理接口电路通常需包括ocd(on-chip driver)与odt(on-die termination)电路,为了驱动接口电路和实现阻抗匹配,ocd和odt电路的基本单元都是由非线性晶体管和线性无源阻抗串联组成。其中ocd的等效阻抗和odt的等效阻抗分别用ron和rtt表示。但由于受pvt(process、voltage、temperature)影响,接口电路中ocd和odt电路的输出性能会出现较大的起伏。在某些极端条件下,接口电路的阻抗变化会超出onfi 4.2标准规定的范畴,因此需要对接口电路中等效的ron和rtt阻抗进行校准。

41.基于此,本发明实施例提供了一种可校准的阻抗电路,有效解决现有技术存在的技术问题,在完成阻抗校准并且同时实现不同工作模式下需要的等效阻抗的基础上,能够减少电路中驱动单元的数量,进而能够减小可校准的阻抗电路的占用面积。

42.为实现上述目的,本发明实施例提供的技术方案如下,具体结合图1至图4对本发明实施例提供的技术方案进行详细的描述。

43.参考图1所示,为本发明实施例提供的一种可校准的阻抗电路的结构示意图,其中,可校准的阻抗电路包括:控制电路100和可控阻抗的驱动电路200。

44.所述控制电路100用于根据参考阻抗rx和不同工作模式下需要的等效阻抗值的设置码rc《3:0》而输出选择信号en、上拉转换校准码pcd和下拉转换校准码ncd。

45.所述可控阻抗的驱动电路200包括并联的多个驱动单元210,所述驱动单元210包括上拉可控阻抗模块211和下拉可控阻抗模块212,所述上拉可控阻抗模块211一端与电源端vd相连、且另一端与io接口相连;及所述下拉可控阻抗模块212的一端与接地端gnd相连、且另一端与所述io接口相连,所述上拉可控阻抗模块211和所述下拉可控阻抗模块212均用于生成第一等效阻抗至第n等效阻抗,n为大于或等于2的整数。

46.所述可控阻抗的驱动电路200用于根据工作模式信号ocd_odt选择的ocd工作模式和所述选择信号en,将所述上拉转换校准码pcd转换为上拉驱动码pc,并通过所述上拉驱动码pc选择所述上拉可控阻抗模块211工作而获取ocd工作模式下需要的阻抗值相匹配的等效阻抗;或将所述下拉转换校准码ncd转换为下拉驱动码nc,并通过所述下拉驱动码nc选择所述下拉可控阻抗模块212工作而获取ocd工作模式下需要的等效阻抗值相匹配的等效阻抗。

47.及,所述可控阻抗的驱动电路200用于根据工作模式信号ocd_odt选择的odt工作模式和所述选择信号en,将所述上拉转换校准码pcd转换为上拉驱动码pc,同时将所述下拉转换校准码ncd转换为下拉校准码nc,并通过所述上拉驱动码pc选择所述上拉可控阻抗模块211工作、且同时通过所述下拉驱动码nc选择所述下拉可控阻抗模块212工作,而获取odt工作模式下需要的等效阻抗值相匹配的等效阻抗。

48.需要说明的是,本发明实施例提供的校准码产生电路包括有上拉驱动子电路、下拉驱动子电路和校准码控制子电路,上拉驱动子电路包括多条并联的上拉阻抗支路,且所有上拉阻抗支路的阻抗可以以2的倍数递增,及下拉驱动子电路包括多条并联的下拉阻抗支路,且所有下拉阻抗支路的阻抗可以以2的倍数递增;校准码控制子电路用于控制上拉驱动子电路的上拉阻抗支路的打开与关断,使得上拉驱动子电路的等效阻抗与参考阻抗匹配,并根据上拉阻抗支路的打开与关断情况生成上拉校准码;以及,校准码控制子电路用于控制下拉驱动子电路的下拉阻抗支路的打开与关断,使得下拉驱动子电路的等效阻抗与参考阻抗匹配,并根据下拉阻抗支路的打开与关断情况生成下拉校准码。其中,阻抗支路由阻抗和可控开关管并联组成,故而校准码由0、1数字信号组成。

49.本发明实施例提供的技术方案,能够通过控制电路和可控阻抗的驱动电路配合实现需要的阻抗值输出。同时,本发明实施例提供的可控阻抗的驱动电路包括有多个可控阻抗的驱动单元,且所有驱动单元的上拉可控阻抗模块之间并联,及所有驱动单元的下拉可控阻抗模块之间并联,进而能够通过独立的可控阻抗模块实现第一等效阻抗至第n等效阻抗,且能够通过并联的可控阻抗模块实现更多的等效阻抗,进而满足更多参考阻抗的等效匹配,由此能够减少电路中驱动单元的数量,进而能够减小可校准的阻抗电路的占用面积。

50.参考图2所示,为本发明实施例提供的另一种可校准的阻抗电路的结构示意图,其中,本发明实施例提供的所述控制电路100包括:逻辑电路110、校准码产生电路120和控制移位器130。

51.所述校准码产生电路120用于根据所述参考阻抗rx生成上拉校准码pq和下拉校准码nq。

52.所述逻辑电路110用于根据所述不同工作模式下需要的等效阻抗值的设置码rc《3:0》生成转换信号s和所述选择信号en,所述转换信号s用于确定所述驱动单元的等效阻抗,其中,所述选择信号en用于选择驱动单元进行工作。

53.所述控制移位器130用于根据所述转换信号s将所述上拉校准码pq转换为所述上拉转换校准码pcd,及将所述下拉校准码nq转换为所述下拉转换校准码ncd。

54.可以理解的,本发明实施例提供的可校准的阻抗电路,校准码产生电路控制其上拉驱动子电路的等效阻抗与参考阻抗匹配,并生成上拉校准码;及控制其下拉驱动子电路的等效阻抗与参考阻抗匹配,并生成下拉校准码。以及,逻辑电路根据参考阻抗生成转换信号和选择信号,其中,选择信号包括多个数字子信号,数字子信号与驱动电路一一对应,用于控制驱动电路是否工作。控制移位器接收该转换信号、上拉校准码和下拉校准码,并根据转换信号将上拉校准码转换为适用于可控阻抗的驱动电路的上拉转换校准码,及将下拉校准码转换为适用于可控阻抗的驱动电路的下拉转换校准码。

55.进而,可控阻抗的驱动电路接收该选择信号、上拉转换校准码和下拉转换校准码,以及接收工作模式信号,并根据选择信号、工作模式信号、上拉转换校准码和下拉转换校准

码,生成不同驱动电路各自相应的上拉驱动码和/或下拉驱动码,选择相应的驱动电路进行工作而得到与阻抗需要的阻抗值匹配的等效阻抗阻抗。

56.在本发明一实施例中,本发明根据不同工作模式下需要的等效阻抗值和所述驱动单元生成的等效阻抗,确定所述转换信号s和所述选择信号en。

57.具体的在所述ocd工作模式下,所述驱动单元的等效阻抗为所述第一等效阻抗至第n等效阻抗;其中,根据所述ocd工作模式下需要的等效阻抗值和所述驱动单元的等效阻抗,确定所述转换信号和所述选择信号,包括:

58.所述ocd工作模式下需要的等效阻抗值为50ω,且所述驱动单元生成的等效阻抗包括150ω,根据50=150/3,确定转换信号用于确定所述驱动单元生成等效阻抗为150ω,及所述选择信号用于选择3个生成等效阻抗为150ω的驱动单元工作;

59.所述ocd工作模式下需要的等效阻抗值为35ω,且所述驱动单元生成的等效阻抗包括150ω和300ω,根据35=(150/3)//(300/3),确定转换信号用于确定所述驱动单元生成等效阻抗为150ω或300ω,及所述选择信号用于选择3个生成等效阻抗为150ω的驱动单元和3个生成等效阻抗为300ω的驱动单元工作;

60.或者,所述ocd工作模式下需要的等效阻抗值为18ω,且所述驱动单元生成的等效阻抗包括(150//300//600)ω,在误差允许范围内根据18=(150//300//600)/5,确定转换信号用于确定所述驱动单元生成等效阻抗为(150//300//600),及所述选择信号用于选择5个生成等效阻抗为(150//300//600)的驱动单元。进一步参考表1所示,为本发明实施例还能够实现的ocd工作模式下的等效阻抗。

[0061][0062]

表1

[0063]

其中,表1中rc《3:0》即表示ocd工作模式下的ron(ω)等效阻抗;产生方式则表示为驱动单元包括的等效阻抗比所需驱动单元的数量;en《3:1》则为选择信号选择的驱动单元的数量,其中三个数字中0表示为0个,三个数字中第一个为1时表示3个、第二个为1时表示为2个且第三个为1表示为1个,即001表示为1个,111表示为6个;s《3:1》则为转换信号,00表示为驱动单元生成等效阻抗为150ω,01表示驱动单元生成等效阻抗为300ω,11表示驱动单元生成等效阻抗为其他。

[0064]

以及,在所述odt工作模式下,所述驱动单元的等效阻抗为所述第一等效阻抗/2至第n等效阻抗/2;其中,根据所述odt工作模式下需要的等效阻抗值和所述驱动单元的等效阻抗,确定所述转换信号和所述选择信号,包括:

[0065]

所述odt工作模式下需要的等效阻抗值为30ω,且所述驱动单元生成的等效阻抗包括150ω,根据30=150/5,确定转换信号用于确定所述驱动单元生成等效阻抗为150ω,及所述选择信号用于选择5个生成等效阻抗为150ω的驱动单元。进一步参考表2所示,为本发明实施例还能够实现的odt工作模式下的等效阻抗。

[0066]

rc《3:0》rtt(ω)产生方式en《3:1》s《1:0》0000150300/1001010001100600/301110001075300/201001001150300/301101010037.5300/4101010101不使用

ꢀꢀꢀ

011030300/511001011125300/611101

[0067]

表2

[0068]

其中,表2中rc《3:0》即表示odt工作模式下的rtt(ω)等效阻抗;产生方式则表示为驱动单元包括的等效阻抗(需要说明的是,表2中所示等效电阻(定义为显示等效阻抗)为上拉可控阻抗模块或下拉可控阻抗模块独立生成的等效电阻,由于上拉可控阻抗模块和下拉可控阻抗模块并联且同时工作,实质上驱动单元的等效电阻为显示等效阻抗/2)比所需驱动单元的数量;en《3:1》则为选择信号选择的驱动单元的数量,其中三个数字中0表示为0个,三个数字中第一个为1时表示3个、第二个为1时表示为2个且第三个为1表示为1个,即001表示为1个,111表示为6个;s《3:1》则为转换信号,01表示为驱动单元生成等效阻抗为150ω,10表示驱动单元生成等效阻抗为200ω。

[0069]

如图3所示,为本发明实施例提供的一种模式选择电路的结构示意图,其中,所述可控阻抗的驱动电路包括多个模式选择电路220,所述模式选择电路220与所述驱动单元210一一对应,所述模式选择电路220用于接入所述工作模式信号ocd_odt、所述上拉转换校准码pcd、所述下拉转换校准码ncd和所述选择信号en。

[0070]

所述模式选择电路220用于根据所述工作模式信号ocd_odt、所述上拉转换校准码pcd、所述下拉转换校准码ncd和所述选择信号en生成所述上拉驱动码pc和/或所述下拉驱动码nc。

[0071]

在本发明一实施例中,本发明提供的所述模式选择电路220包括:第一与非门221、第一非门222、第二与非门223、第一缓冲器224、第一二选一选择器225、第二二选一选择器226、第二非门227、或非门228、第二缓冲器229、第三与非门230。

[0072]

所述第一与非门221的第一端接入所述选择信号en,所述第一与非门221的第二端接入所述上拉转换校准码pcd,所述第一与非门221的输出端与所述第一非门222的输入端相连,所述第一非门222的输出端与所述第二与非门223的第一端相连,所述第二与非门223的第二端与所述第一二选一选择器225的输出端相连,所述第二与非门223的输出端与所述

第一缓冲器224的输入端相连,所述第一缓冲器224的输出端用于输出所述上拉驱动码pc。

[0073]

所述第一二选一选择器225的第一输入端接入ocd控制信号din,所述第一二选一选择器225的第二输入端接入odt控制信号odt_en,所述第二二选一选择器226的第一输入端接入所述ocd控制信号din,所述第二二选一选择器226的第二输入端与所述第二非门227的输出端相连,所述第二非门227的输入端接入所述odt控制信号dot_en。

[0074]

所述第二二选一选择器226的输出端与所述或非门228的第一端相连,所述或非门228的输出端与所述第二缓冲器229的输入端相连,所述第二缓冲器229的输出端用于输出所述下拉驱动码nc,所述或非门228的第二端与所述第三与非门230的输出端相连,所述第三与非门230的第一端接入所述选择信号en,所述第三与非门230的第二端接入所述下拉转换校准码ncd。

[0075]

可以理解的,本发明实施例提供的模式选择电路,若en为高(数字信号为1),则说明驱动电路被使能;ocd_odt通过二选一选择器确定工作模式,若ocd_odt=0,则电路工作在ocd模式;若ocd_odt=1,则电路工作在odt模式。

[0076]

当电路工作在ocd模式时,若din=1,则打开驱动电路中的上拉可控阻抗模块;若din=0,则打开驱动电路中的下拉可控阻抗模块。当电路工作在odt模式时,若odt_en=1,同时打开驱动电路中的上拉可控阻抗模块和下拉可控阻抗模块;若odt_en=0,则关断驱动电路。

[0077]

如图4所示,为本发明实施例提供的一种驱动电路的结构示意图,其中,,所述上拉可控阻抗模块211包括第一上拉晶体管t11至第m上拉晶体管t1m及第一上拉阻抗r11至第m上拉阻抗r1m,第i上拉晶体管的第一端与所述电源端vc相连,所述第i上拉晶体管的第二端与第i上拉阻抗的第一端相连,所述第i上拉阻抗的第二端与所述io接口相连,m为大于或等于2的整数,i为大于0且小于或等于m的整数。

[0078]

所述下拉可控阻抗模块212包括第一下拉晶体管t21至第m下拉晶体管t2m及第一下拉阻抗r21至第m下拉阻抗r2m,第i下拉晶体管的第一端与所述接地端gnd相连,所述第i下拉晶体管的第二端与第i下拉阻抗的第一端相连,所述第i下拉阻抗的第二端与所述io接口相连。

[0079]

在本发明一实施例中,本发明提供的第一上拉阻抗至第m上拉阻抗可以以2的指数倍的方式递增,如第一上拉阻抗的阻值为r,则第二上拉阻抗的阻值为2r,第三上拉阻抗的阻值为4r,以此类推。同样的,第一下拉阻抗至第m下拉阻抗可以以2的指数倍的方式递增,如第一下拉阻抗的阻值为r,则第二下拉阻抗的阻值为2r,第三下拉阻抗的阻值为4r,以此类推

[0080]

需要说明的是,本发明实施例对于驱动单元的数量、上拉阻抗的数量和下拉阻抗的数量不做具体限制,对此需要根据实际应用进行具体设计。以及,对于上拉驱动码和上拉可控阻抗模块而言,上拉驱动码包括第一上拉控制信号至第m上拉控制信号,第i上拉控制信号接入第i上拉晶体管的栅极,用于控制第i上拉晶体管的通断。以及,对于下拉驱动码和下拉可控阻抗模块而言,下拉驱动码包括第一下拉控制信号至第m下拉控制信号,第i下拉控制信号接入第i下拉晶体管的栅极,用于控制第i下拉晶体管的通断。

[0081]

在本发明一实施例中,本发明提供的所述第i上拉晶体管和所述第i下拉晶体管的导通类型相反。其中,上拉晶体管可以为p型晶体管,及下拉晶体管可以为n型晶体管,对此

本发明不做具体限制。

[0082]

本发明实施例提供了一种可校准的阻抗电路,其中可控阻抗的驱动电路包括含有多个等效阻抗的驱动单元,所述驱动单元包括上拉可控阻抗模块和下拉可控阻抗模块,且所有所述驱动单元的上拉可控阻抗模块之间并联,所述上拉可控阻抗模块一端与电源端相连、且另一端与io接口相连;及所有所述驱动单元的下拉可控阻抗模块之间并联,所述下拉可控阻抗模块的一端与接地端相连、且另一端与所述io接口相连,所述上拉可控阻抗模块和所述下拉可控阻抗模块均用于生成第一等效阻抗至第n等效阻抗。

[0083]

由上述内容可知,本发明实施例提供的技术方案,能够通过控制电路和可控阻抗的驱动电路配合实现不同工作模式下需要的等效阻抗。同时,本发明实施例提供的可控阻抗的驱动电路包括有多个等效阻抗的驱动单元,且所有驱动单元的上拉可控阻抗模块之间并联,及所有驱动单元的下拉可控阻抗模块之间并联,进而能够通过独立的可控阻抗模块实现第一等效阻抗至第n等效阻抗,且能够通过并联的可控阻抗模块实现更多的等效阻抗,进而满足不同工作模式下需要的多个等效阻抗值,由此能够减少电路中驱动单元的数量,进而能够减小可校准的阻抗电路的占用面积。

[0084]

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1