多比特存内内积暨异或单元、异或向量及操作方法

1.本发明涉及存储、计算、电路领域,具体涉及一种多比特存内内积暨异或单元、异或向量及操作方法。

背景技术:

2.在人工智能大量数据密集计算的背景下,各种二值神经网络(binary neural networks,bnn)及超高维度向量计算(hyperdimensional computing,hdc)已经被证明可以高效地应用于不同实际场景如:物体追踪,声音识别,图像聚类等等。由于传统冯-诺伊曼计算机架构计算单元与存储单元的分离会导致高延时和能耗,以存算一体架构替代传统冯-诺伊曼计算机架构成为研究热点;由各种新型非易失器件所组成的存算一体单元能实现不同的逻辑运算,如单一个铁电晶体管即可实现二值向量之间“与”的逻辑运算。

3.然而,真实应用下,二值向量并不能满足数据密集的运算场景;多比特内积的运算单元可以更广泛应用于人工智能场景如卷积神经网络。基于传统sram的多比特存内多比特内积单元近年来被广泛提出,但其在延时、能耗、面积、可扩展性等仍存在诸多缺陷,并且基于新型非易失存储器件的多比特存内内积暨异或架构仍未被提出;同时,在实现多比特内积之于,实际场景如二值卷积神经网络仍然会需要实现异或功能,又如汉明码距离本身即为按位异或运算,因此,本发明提出同时适用于多比特向量内积以及异或功能的存算单元。

技术实现要素:

4.本发明的目的在于提出一种多比特存内内积暨异或单元及其异或向量的技术方案,首次提出基于fefet的实现方式,且能耗、搜索延时、面积等指标与现在仅有的工作相比有所提升。

5.为实现上述目的,本发明提供了如下方案:

6.一种多比特存内内积暨异或单元,包括n个并联的1fefet1r结构、输入晶体管、第一反相器和第二反相器,n为大于1的自然数,所述1fefet1r结构包括电连接的fefet和电阻,每个1fefet1r结构的电阻均与输入晶体管电连接,所述输入晶体管的栅极通过第一反相器与其中一个1fefet1r结构中fefet的栅极电连接,该1fefet1r结构中fefet的栅极通过第二反相器与另一个1fefet1r结构中fefet的栅极电连接。

7.进一步地,每个1fefet1r结构中电阻的阻值不同,形成一连串输出电流为一系列二进制2

n-1

,2

n-2

,

…

,21,20存储单元。

8.进一步地,所述1fefet1r结构中电阻与fefet的漏极或源极电连接。

9.进一步地,所述输入晶体管工作于线性区,其将向量元素之权重映射为电压并输入于对应fefet的栅极。

10.进一步地,所述第一反相器用于输入向量元素的互补值。

11.进一步地,所述第二反相器用于两对应fefet存入互补值。

12.本发明还提供一种多比特存内内积暨异或向量,包括m个如上所述多比特存内内

积暨异或单元,该m个多比特存内内积暨异或单元并联。

13.本发明还提供一种如上所述多比特存内内积暨异或向量的操作方法,包括:

14.s1存储向量的每个向量元素先存入多比特存内内积暨异或单元,具体存入方法为:存入向量的每个向量元素为二进制,根据欲输入的向量元素二进制值,如果为

‘1’

,在对应的fefet栅极输入高电压,使fefet存入

‘1’

;如果为

‘0’

,则在对应的fefet栅极输入低电压,使fefet存入

‘0’

,同时,于另一异或1fefet1r结构通过反相器存入

15.s2存入向量的向量元素存入多比特存内内积暨异或单元后,当查询向量来临时,同时进行以下操作:

16.s2.1查询向量的向量元素以电压的形式施加于多比特存内内积暨异或单元中的输入晶体管的栅极;同时,查询向量的向量元素通过第一反相器对应1fefet1r结构;

17.s2.2对于实现多比特内积功能,每个fefet的栅极同时输入高电压,利用fefet本身即可实现“与”的特点,当存储值为

‘0’

时,输出为

‘0’

;当存储值为

‘1’

时,输出为

‘1’

;

18.s2.3对于实现多比特功能,两个反相器处于关断状态;对于实现异或功能,两个反相器接上电源,处于工作状态,且前n-1个fefet的栅极同时输入低电压,即存入

‘0’

。

19.本发明的有益效果如下:

20.本发明首次提出基于非易失存储器件且同时支持多比特存内内积暨异或的单元及其向量,在搜索能耗、搜索延时以及面积三大指标上均表现更优。

附图说明

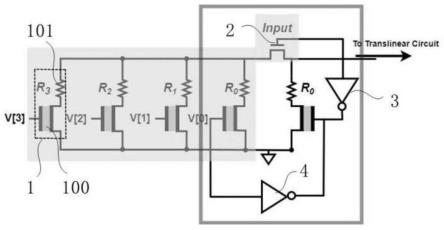

21.图1是n=4比特的多比特存内内积暨异或单元应用于余弦搜索架构示意图;

22.图2是本发明内容电路图,单个n=4比特的多比特存内内积暨异或单元电路图;

23.图3(a)是n=4比特下,单个多比特存内内积暨异或单元存储值由0000至1111的结果示意图;

24.图3(b)是n=4比特下,单个多比特存内内积暨异或单元存储值由0000至1111经过100次蒙特卡洛的结果示意图;

25.图4(a)和(b)分别为n=4/n=6扩展示意图,其中分析了多比特存内内积暨异或单元的可扩展性,图4(b)展示了即使到n=6,最坏情况只会有一比特运算无法区分;

26.图5是n=4比特下,单个多比特存内内积暨异或单元内电阻值降低的结果示意图;

27.图6是基于图1下多比特存内内积暨异或单元应用示意图。

具体实施方式

28.下面结合附图和具体实施例对本发明作进一步详细说明。

29.请参阅图1-6,一种多比特存内内积暨异或单元,包括n个并联的1fefet1r结构1、输入晶体管2、第一反相器3和第二反相器4,n为大于1的自然数,所述1fefet1r结构1包括fefet100和电阻101,电阻101与fefet100的漏极或源极电连接,每个1fefet1r结构1的电阻101均与输入晶体管2电连接,所述输入晶体管2的栅极通过第一反相器3与其中一个1fefet1r结构1中fefet100的栅极电连接,该1fefet1r结构1中fefet100的栅极通过第二反相器4与另一个1fefet1r结构1中fefet100的栅极电连接。

30.其中,对于工作于比特存内内积模式,要形成n+1比特的内积单元,只需要对n比特

结构新增一1fefet1r结构1,1fefet1r结构1的电阻101需有2n倍或2-1

倍的饱和漏源电流。因此,本发明中每个1fefet1r结构1中电阻101的阻值不同,形成一连串输出电流为一系列二进制2

n-1

,2

n-2

,

…

,21,20存储单元。

31.其中,所述输入晶体管2工作于线性区,其将向量元素之权重映射为电压并输入于对应fefet100的栅极。

32.其中,所述第一反相器3用于输入互补值。

33.其中,所述第二反相器4用于两对应fefet100存入互补值。

34.请参阅图2,本发明还提供一种多比特存内内积暨异或向量,包括m个如上所述多比特存内内积暨异或单元c,该m个多比特存内内积暨异或单元c并联,形成一拥有m个向量元素的的向量。

35.一种如上所述多比特存内内积暨异或向量的操作方法,包括:

36.s1存储向量的每个向量元素先存入多比特存内内积暨异或单元,具体存入方法为:存入向量的每个向量元素为二进制,以n=4比特的存内内积单元为例w=w3w2w1w0,高位为w3,表示23;低位为w0,表示20。根据欲输入的向量元素二进制值,如果为

‘1’

,在对应的fefet栅极输入高电压,使fefet存入

‘1’

;如果为

‘0’

,则在对应的fefet栅极输入低电压,使fefet存入

‘0’

。同时,于另一异或1fefet1r结构通过反相器存入

37.s2存入向量的向量元素存入多比特存内内积暨异或单元后,当查询向量来临时,同时进行以下操作:

38.s2.1查询向量的向量元素以电压的形式施加于多比特存内内积暨异或单元中的输入晶体管的栅极;同时,查询向量的向量元素通过第一反相器对应1fefet1r结构。

39.s2.2对于实现多比特内积功能,每个fefet的栅极同时输入高电压,利用fefet本身即可实现“与”的特点,当存储值为

‘0’

时,输出为

‘0’

;当存储值为

‘1’

时,输出为

‘1’

。

40.s2.3对于实现多比特功能,两个反相器处于关断状态;对于实现异或功能,两个反相器接上电源,处于工作状态,且前n-1个(即图2的v[3]到v[1])fefet的栅极同时输入低电压,即存入

‘0’

,使单元只有最右边两个1fefet1r工作。

[0041]

单元应用及架构仿真操作流程说明

[0042]

多比特存内内积暨异或单元组成的向量计算出余弦计算电路输入;如图1所示,以n=4比特为例,存储阵列中的每个存储单元的晶体管相连形成一含有m个向量元素的向量。此内积结果通过电流镜拷贝,作为余弦计算电路的输入。而图1右边的存储阵列用于计算出每个余弦值的l2范数,即余弦表达式的分母;余弦计算电路的输出再经过winner-take-all电路,找出与查询向量间余弦距离最大值的存储向量。其中,余弦计算电路的表达式为:电路,找出与查询向量间余弦距离最大值的存储向量。其中,余弦计算电路的表达式为:

[0043]

多比特存内内积暨异或单元具体运行过程如下

[0044]

1、在搜索开始前,对每个多比特存内内积暨异或单元输入存储向量;以n=4比特为例,通过每个多比特存内内积暨异或单元的v[3]~v[0],分别写入w3、w2、w1、w0;同时另一1fefet1r通过反相器存入

‘0’

用-4v电压脉冲写入,

‘1’

用+4v电压脉冲写入。将向量元素写入后,即可以开始搜索过程。

[0045]

2.1、搜索时,当单元工作在多比特存内内积模式下,每个实现多比特存内内积的1fefet1r,即v[3]~v[0](图2),用+4v电压脉冲写入,即写入

’1’

;同时,输入由输入晶体管的栅极输入(图2)。根据输入向量元素值的大小,在0~1.2v之间选取电压。

[0046]

2.2、搜索时,当单元工作在异或模式下,前n-1個实现多比特存内内积的1fefet1r,即v[3]~v[1](图2),用-4v电压脉冲写入,即写入

’0’

。

[0047]

本发明的功能和效果通过以下仿真实验进一步说明展示:

[0048]

1、仿真条件

[0049]

实验使用基于物理电路的兼容spectre和spice模型对由1fefet1r存储单元组成的存储阵列进行仿真,其中fefet是基于preisach模型。该模型实现了高效的设计与分析,已广泛应用于fefet电路设计中。利用ptm45-hp作为其余晶体管的仿真模型。

[0050]

仿真架构以图1所示。图1实现人工智能场景的一项应用:基于余弦搜索的最近邻搜索。其原理为,寻找出与输入向量在余弦距离上最相近的存储向量。图1的存储单元(以c表示)即为本发明提出的多比特存内内积暨异或单元;其中图2是以n=4比特为代表的多比特存内内积暨异或单元。

[0051]

2、仿真结果

[0052]

(1)根据图2之多比特存内内积暨异或单元原理图,当电流在纳安培级别时,于spectre仿真表明r0:r1:r2:r3为8:4:2:1。

[0053]

(2)图3(a)的横坐标为输入于多比特存内内积暨异或单元内晶体管栅极的电压,为连续值。曲线由下至上为存储值由0000至1111;图3(b)为考虑了fefet工艺误差(提取自非专利文献1t.solimanetal.,“ultra-lowpowerflexibleprecisionfefetbasedanalogin-memorycomputing”,ieeeiedm,2020.),考虑了大电阻误差(提取自非专利文献2d.saito etal.,“analogin-memorycomputinginfefet-based 1t1rarrayforedgeaiapplications”,ieee symposiumonvlsicircuits,2021)和晶体管误差,即领域默认10%大小误差、10%阈值电压误差,所得到的结果。图3(a)的横坐标为输入于多比特存内内积暨异或单元内晶体管栅极的电压,曲线由下至上为存储值0001(1

(10)

)、0011(3

(10)

)、0101(5

(10)

)、0111(7

(10)

)、1001(9

(10)

)、1011(11

(10)

)、1101(13

(10)

)、1111(15

(10)

)。结果表明,本发明内积结果准确性高,内积结果相差大于2且内积结果范围足够大(输入大于0101(5

(10)

),电压约为0.5v),运算则不产生重叠。

[0054]

(3)能耗和延時:

[0055]

将我们的结果与非专利文献3(m.ali et al.,“imac:in-memory multi-bit multiplication and accumulation in 6t sram array”,tcas-i,2020.)中提出的基于sram多比特存内内积暨异或单元进行对比,从图6对向量个数及向量维度分别扩展的结果,本发明得到了超过104倍每多比特存内内积暨异或单元能耗的下降,和4.67倍输出延时的下降。

[0056]

(4)消耗面积:

[0057]

本发明的面积消耗相比于上述非专利文献3有显著减少,主要是因为利用了新型非易失存储器件fefet且在设计上相比于传统sram更为简单。对于单个多比特存内内积暨异或单元,本发明相比于上述非专利文献3于面积上减少了488倍(sram 64.9μm2/cell,本发明0.133μm2/cell)。

[0058]

(5)可扩展性:

[0059]

图4将n=4比特的多比特存内内积暨异或单元扩展至n=6比特,展示了最坏情况下,只会有1的运算不精确;具体来说,对于n=6的单元,仿真结果表明000111(7

(10)

)以及001000(8

(10)

)会出现相同电流情况。

[0060]

图5展示了将1fefet1r的电阻调小,失工作电流上升,增加了多比特存内内积暨异或单元中各个支路流出的电流差;表明了在不需要限制电流大小的应用中,如汉明计算,本发明可扩展性进一步上升。

[0061]

上述实施例用来解释说明本发明,而不是对本发明进行限制,在本发明的精神和权利要求的保护范围内,对本发明做出的任何修改和改变,都落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1