存储系统及其操作方法与流程

1.本发明属于存储器技术领域,更具体地,涉及一种存储系统及其操作方法。

背景技术:

2.ddr5是第五代ddr sdram的简称,当前的双倍速率同步动态随机存取存储器(double data rate synchronous dynamic random access memory,ddr sdram)标准适用于ddr5存储器,并提供一个可支持双列直插式存储模块(dual-in-line memory module,dimm)设备的通道,其最高速率为3200mhz或者6400mt/s,在时钟的上升沿和下降沿记录数据。

3.chipkill这个术语传统上指的是纠正内存中多个位错误的能力,其中多个位错误是内存设备的总线宽度。例如,对于4或8位宽的sdram,支持chipkill功能的系统将能够纠正内存设备中的4或8位宽错误。因此,在支持chipkill的系统中,以

×

4或

×

8配置组织的整个sdram的芯片故障将不会导致系统故障。

4.ddr5内存标准的目标是至少将ddr4的最大速率提高一倍,以达到6400mt/s,甚至8400mi/s,同时保证高的可靠性并降低成本和功耗。但现有技术中的ddr4/ddr5混合dimm不具有chipkill功能,错误检测占用了较大的存储开销,且单次访问需要激活的芯片数量较多,导致无法满足可靠性、成本和功耗的要求。

技术实现要素:

5.针对现有技术的以上缺陷或改进需求,本发明提供了一种存储系统及其操作方法,具有两倍于普通ddr5 dimm的带宽,支持chipkill ecc(error correcting code,纠错码)功能,且芯片使用量少,成本和功耗低。

6.为实现上述目的,按照本发明的一个方面,提供了一种ddr5 dimm,包括第一子通道;第一子通道包括第一组数据缓存器和第一组dram芯片;第一组数据缓存器用于以第一速率通过第一组数据总线获取第一数据和第一ecc码,还用于以第二速率通过第二组数据总线将第一数据和第一ecc码存储至第一组dram芯片;第一组数据缓存器包括多个数据缓存器,第一组dram芯片包括多个dram芯片组,第一组数据总线包括多个主机侧数据总线,第二组数据总线包括多个存储侧数据总线;主机侧数据总线、数据缓存器、存储侧数据总线和dram芯片组一一对应。

7.在一些实施方式中,第一数据包括第一部分和第二部分,第一ecc码包括第一ecc数据和第二ecc数据;第一组数据缓存器用于在时钟的上升沿获取第一部分和第一ecc数据,还用于在时钟的下降沿获取第二部分和第二ecc数据;第一部分和第二部分均包括连续的多个半字节数据。

8.在一些实施方式中,第一组dram芯片均为

×

4 dram芯片,第一ecc数据和第二ecc数据的长度均为半字节;多个数据缓存器中的每一个用于在时钟的上升沿获取第一部分中的2个半字节数据或第一ecc数据,还用于在时钟的下降沿获取第二部分中的2个半字节数

据或第二ecc数据,还用于将获取的第一部分中的2个半字节数据和第二部分中的2个半字节数据存储至对应的dram芯片组,或者将获取的第一ecc数据和第二ecc数据存储至对应的dram芯片组。

9.在一些实施方式中,dram芯片组中的每一个dram芯片存储1个半字节数据,或者dram芯片组中的每一个dram芯片存储第一ecc数据或者第二ecc数据。

10.在一些实施方式中,第一组dram芯片均为

×

8 dram芯片,第一ecc数据和第二ecc数据的长度均为一个字节;多个数据缓存器中的每一个用于在时钟的上升沿获取第一部分中的2个半字节数据或第一ecc数据,还用于在时钟的下降沿获取第二部分中的2个半字节数据或第二ecc数据,还用于将获取的第一部分中的2个半字节数据和第二部分中的2个半字节数据存储至对应的dram芯片组,或者将获取的第一ecc数据和第二ecc数据存储至对应的dram芯片组。

11.在一些实施方式中,第一部分中的2个半字节数据存储至对应的dram芯片组的一个dram芯片中,第二部分中的2个半字节数据存储至对应的dram芯片组的另一个dram芯片中;第一ecc数据存储至对应的dram芯片组的一个dram芯片中,第二ecc数据存储至对应的dram芯片组的另一个dram芯片中。

12.在一些实施方式中,第一子通道还包括时钟锁存驱动器,ddr5 dimm还包括第二子通道,第二子通道具有与第一子通道相同的结构,时钟锁存驱动器为第一子通道和第二子通道共用。

13.根据本发明的另一方面,提供了一种存储系统,包括cpu、存储器控制器和上述ddr5 dimm。

14.根据本发明的又一方面,提供了一种存储系统的操作方法,该存储系统包括存储器控制器和ddr5 dimm,该操作方法包括:判断ddr5 dimm是否支持chipkill功能;在ddr5 dimm支持chipkill功能时,进一步判断ddr5 dimm是否为

×

4 dimm;在ddr5 dimm是

×

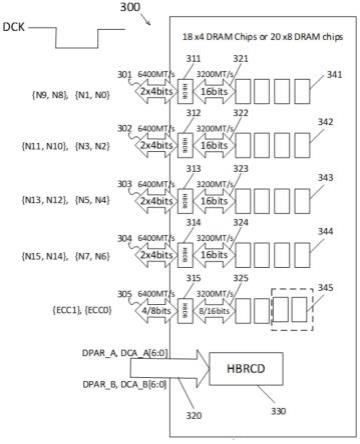

4 dimm时,将接收的4个连续的数据位组合成与dram的数据宽度相同的一个半字节数据,对16个连续的半字节数据执行gf(24)空间的rs(18,16)码以支持chipkill校正算法,并生成2个长度为半字节的ecc数据;在ddr5 dimm是

×

8 dimm时,将两个连续的数据半字节组合成与dram的数据宽度相同的一个字节数据,对8个连续的字节数据执行gf(28)的空间的rs(10,8)码以支持chipkill校正算法,并生成2个长度为一个字节的ecc数据。

15.在一些实施方式中,在ddr5 dimm是

×

4 dimm时,将16个连续的半字节数据和所述2个长度为半字节的ecc数据分别写入18个

×

4 dram芯片;在ddr5 dimm是

×

8 dimm时,将8个连续的字节数据和所述2个长度为一个字节的ecc数据分别写入10个

×

8 dram芯片。

16.总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:支持

×

4和

×

8配置,允许

×

4的ddr4/ddr5 dram芯片以及

×

8的ddr4/ddr5 dram芯片在具有chipkill可靠性的高端服务器中使用。在

×

4 dimm配置中,每个dram芯片的数据总线宽度为4位,每个通道的每次访问将激活18个dram芯片,其中16个数据芯片,2个芯片提供可靠性检测,占用的存储开销较低,通过选择合适的ecc模块进行编码并将两个ecc符号存储在2个4位dram芯片中,能实现chipkill错误检测功能;在

×

8 dimm配置中,每个dram芯片的数据总线宽度为8位,每个通道的每次访问仅需激活10个dram芯片,通过选择合适的ecc模块进行编码并将两个ecc符号存储在2个8位dram芯片中,能实现chipkill错误检测功能。

附图说明

17.图1是一种具有d5-lrdimm的计算机系统;

18.图2是一种具有d5-hbdimm的计算机系统;

19.图3是本发明实施例的d5-hbdimm的一个子通道结构示意图;

20.图4是mc将数据写入

×

4配置的图3所示的d5-hbdimm的子通道的示意图;

21.图5是mc将数据写入

×

8配置的图3所示的d5-hbdimm的子通道的示意图;

22.图6是里德-所罗门码的结构示意图;

23.图7是本发明实施例的在d5-hbdimm中实现chipkill的流程示意图。

具体实施方式

24.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。正如本领域技术人员可以认识到的那样,在不脱离本技术的精神或范围的情况下,可通过各种不同方式修改所描述的实施例。因此,附图和描述被认为本质上是示例性的而非限制性的。

25.ddr主机到内存模块的接口是64位数据加上16位纠错码(ecc)。这是一个双通道系统,其中64位数据总线被分成两个子通道,每个子通道包含32位数据和8位ecc,该子通道还包括一个命令/地址接口。

26.图1是一种计算机系统900,其包括中央处理单元(cpu)910、存储器控制器(memory controller,,mc)920,以及满足jedec标准的ddr5负载减少型dimm(ddr5 load reduced dimm,ddr5 lrdimm或者d5-lrdimm)。该d5-lrdimm包括两个子通道,图1给出了d5-lrdimm的其中一个子通道100。如图1所示,子通道100包括5个

×

4 dram芯片组141-145(其共包含20个

×

4 dram芯片)、以及5个数据缓存器(data buffer,db)111-115和时钟锁存驱动器(registering clock driver,rcd)130。其中,rcd 130由两个子通道(另一子通道图1中未示出)共用,命令/地址总线120连接mc 920和rcd 130,第一组数据总线101-105在子通道100的外部主机接口和db 111-115之间,第二组数据总线121-125在db 111-115和

×

4 dram芯片组141-145之间,两组数据总线具有相同的数据速率。

27.定义ddr5高带宽dimm(ddr5 hbdimm或d5-hbdimm)为具有倍速的ddr5 dimm,其使用较慢但交错的ddr4 dram芯片或者ddr5 dram芯片,也就是说,可用低成本的ddr4 dram芯片或者ddr5 dram芯片提供两倍于常规ddr5-dimm的带宽。对于

×

4 dimm,两列dimm上的dram芯片数量可分别为36和40,对于

×

8 dimm,两列dimm上的dram芯片数量可分别为18和20。

28.图2给出了一种计算机系统930,其包括cpu 940、mc 950以及满足jedec标准的d5-hbdimm。该d5-hbdimm包括两个子通道,图2给出了d5-hbdimm的其中一个子通道200。如图2所示,子通道200包括5个dram芯片组241-245(其共包含20或者18个dram芯片)、5个高带宽数据缓冲器(hbdb)211-215和高带宽时钟锁存驱动器(hbrcd)230。其中,hbrcd230由两个子通道共用,命令/地址总线220连接mc 950和hbrcd 230,第一组数据总线201-205在子通道200的外部主机接口和hbdb 211-215之间,第二组数据总线221-225在hbdb 211-215和dram芯片241-245之间,第二组数据总线221-225以第一组数据总线201-205一半的数据速率运

行,例如,第一组数据总线201-205的数据速率为6400mt/s,第二组数据总线221-225的数据速率为3200mt/s。

29.图3是本发明实施例的d5-hbdimm的一个子通道(第一子通道)结构示意图。如图3所示,第一子通道300包括第一组数据缓存器、时钟锁存驱动器和第一组dram芯片。在一些实施方式中,第一组数据缓存器包括5个高带宽数据缓存器(hbdb)311-315,时钟锁存驱动器包括高带宽时钟锁存驱动器(hbrcd)330,第一组dram芯片包括5个dram芯片组341-345,其包含20个

×

8 dram或者18个

×

4 dram芯片。d5-hbdimm还包括第二子通道(图3中未示出),第二子通道可以具有与第一子通道相同的结构,例如,对应地,第二子通道包括第二组数据缓存器、时钟锁存驱动器和第二组dram芯片。其中,时钟锁存驱动器由第一子通道和第二子通道共用。关于第二子通道的详细情况可参考第一子通道,在此不再赘述。

30.命令/地址总线320连接mc(图3中未示出)和高带宽时钟锁存驱动器330,第一组数据总线301-305在外部主机接口和第一子通道300的高带宽数据缓存器311-315之间,第二组数据总线321-325在高带宽数据缓存器311-315和dram芯片组341-345之间,第二组数据总线321-325以第一组数据总线301-305一半的数据速率运行,例如,第一组数据总线301-305的数据速率为6400mt/s,则第二组数据总线321-325的数据速率为3200mt/s。

31.应当了解,存储系统(或者计算机系统)可以包括cpu、mc、以及具有上述第一子通道和第二子通道的d5-hbdimm。其中,dimm(双列直插式内存模块)是一个模块,在一个小电路板上包含多个随机存取存储器(ram)芯片,存放cpu需要执行的程序和数据。cpu通过mc对dimm进行管理和读写。rcd用于供信号调节而在主机与dram之间进行调解。

32.图4是mc将数据写入

×

4配置的图3所示的d5-hbdimm的子通道的示意图。如图4所示,第一子通道300包括5个

×

4 dram芯片组341-345,具体包括第一

×

4 dram芯片组341、第二

×

4 dram芯片组342、第三

×

4 dram芯片组343、第四

×

4 dram芯片组344和第五

×

4 dram芯片组345,第一至第四

×

4 dram芯片组341-344各自包含4个

×

4 dram芯片,第五

×

4 dram芯片组345包含2个

×

4 dram芯片,

×

4 dram芯片组341-345共计包含18个

×

4 dram芯片。第一组数据总线301-305具体包括第一主机侧数据总线301、第二主机侧数据总线302、第三主机侧数据总线303、第四主机侧数据总线304和第五主机侧数据总线305。第二组数据总线321-325具体包括第一存储侧数据总线321、第二存储侧数据总线322、第三存储侧数据总线323、第四存储侧数据总线324和第五存储侧数据总线325。

33.第一主机侧数据总线301连接外部主机接口和第一高带宽数据缓存器311,第一存储侧数据总线321连接第一高带宽数据缓存器311和第一

×

4 dram芯片组341;第二主机侧数据总线302连接外部主机接口和第二高带宽数据缓存器312,第二存储侧数据总线322连接第二高带宽数据缓存器312和第二

×

4 dram芯片组342;第三主机侧数据总线303连接外部主机接口和第三高带宽数据缓存器313,第三存储侧数据总线323连接第三高带宽数据缓存器313和第三

×

4 dram芯片组343;第四主机侧数据总线304连接外部主机接口和第四高带宽数据缓存器314,第四存储侧数据总线324连接第四高带宽数据缓存器314和第四

×

4 dram芯片组344;第五主机侧数据总线305连接外部主机接口和第五高带宽数据缓存器315,第五存储侧数据总线325连接第五高带宽数据缓存器315和第五

×

4 dram芯片组345。

34.在

×

4 dimm中,64位数据总线和8位ecc被分为两个子通道,每个子通道的每个时钟边缘都有32位数据和4位ecc。在本发明实施例中,定义数据总线上的四个连续位为半字

节。在时钟上升沿,第一子通道300的外部主机接口有8个半字节数据(n0,n1,

…

,n7)和一个ecc半字节(ecc0);在时钟下降沿,第一子通道300的外部主机接口有8个数据半字节(n8,n9,...,n15)和一个ecc半字节(ecc1)。

35.以第一高带宽数据缓存器311为例,其以6400mt/s的速率,在时钟dck的上升沿从第一主机侧数据总线301获取数据半字节n0和n1,在时钟dck的下降沿从第一主机侧数据总线301获取数据半字节n8和n9,并在固定延迟时间tpdm后,以3200mt/s的速率通过第一存储侧数据总线321将n0、n1、n8和n9一起发送到第一

×

4 dram芯片组341内的4个

×

4 dram芯片,每个dram芯片接收一个数据半字节。在一些实施方式中,tpdm在1.1ns+tck/4和1.62ns+tck/4之间,其中,tck是时钟dck的周期。

36.类似地,第二高带宽数据缓存器312在时钟dck的上升沿获取半字节数据n2和n3,在时钟dck的下降沿获取半字节数据n10和n11,并在固定延迟时间tpdm后,将n2、n3、n10和n11一起发送到第二

×

4 dram芯片组342内的4个

×

4 dram芯片,每个dram芯片接收一个数据半字节。第三高带宽数据缓存器313在时钟dck的上升沿获取半字节数据n4和n5,在时钟dck的下降沿获取半字节数据n12和n13,并在固定延迟时间tpdm后,将n4、n5、n12和n13一起发送到第三

×

4 dram芯片组343内的4个

×

4 dram芯片,每个dram芯片接收一个数据半字节。第四高带宽数据缓存器314在时钟dck的上升沿获取半字节数据n6和n7,在时钟dck的下降沿获取半字节数据n14和n15,并在固定延迟时间tpdm后,将n6、n7、n14和n15一起发送到第四

×

4 dram芯片组344内的4个

×

4 dram芯片,每个dram芯片接收一个半字节数据。

37.在本发明实施例中,定义每个半字节为一个ecc符号,mc通过对16个连续的数据半字节在伽罗瓦场(galois field,gf)产生里德-所罗门(reed-solomon)码以支持chipkill校正算法,生成两个ecc半字节。具体地,对16个连续的半字节数据在gf(24)空间产生rs(18,16)码以支持chipkill校正算法,并生成两个ecc半字节ecc0和ecc1。

38.第五高带宽数据缓存器315以6400mt/s的速率,在时钟dck的上升沿从第五主机侧数据总线305获取半字节ecc0,在时钟dck的下降沿从第五主机侧数据总线305获取半字节ecc1,并在固定延迟时间tpdm后,以3200mt/s的速率通过第五存储侧数据总线325将ecc0和ecc1一起发送到第五

×

4 dram芯片组345内的2个

×

4 dram芯片,每个dram芯片接收一个半字节ecc。

39.在一些实施方式中,芯片组341-345内的18个

×

4 dram芯片为ddr4 dram芯片。在一些实施方式中dram芯片组341-345内的18个

×

4 dram芯片为ddr5 dram芯片。

40.在

×

4 dimm配置中,每个dram芯片的数据总线宽度为4位,每个通道的每次访问将激活18个dram芯片,由于每个通道有16个数据芯片以及2个芯片提供chipkill可靠性,因此,错误检测只会产生12.5%的存储开销。与现有技术相比,本发明错误检测产生的存储开销减少了12.5%,dram芯片的数量得以减少,且具有chipkill可靠性。

41.图5是mc将数据写入

×

8配置的图3所示的d5-hbdimm的子通道的示意图。如图5所示,第一子通道300包括5个

×

8 dram芯片组341-345,具体包括第一

×

8 dram芯片组341、第二

×

8 dram芯片组342、第三

×

8 dram芯片组343、第四

×

8 dram芯片组344和第五

×

8 dram芯片组345,第一至第五

×

8 dram芯片组341-345各自包含4个

×

8 dram芯片,

×

8 dram芯片组341-345共计包含20个

×

8 dram芯片。

42.在

×

8 dimm中,64位数据总线和16位ecc被分为两个子通道,每个子通道的每个时

钟边缘都有32位数据和8位ecc。在时钟上升沿,连接第一子通道300的外部主机接口有8个半字节数据(n0,n1,

…

,n7)和一个字节ecc(ecc0),在时钟下降沿,连接第一子通道300的外部主机接口有8个半字节数据(n8,n9,

…

,n15)和一个字节ecc(ecc1)。

43.以第一高带宽数据缓存器311为例,其以6400mt/s的速率,在时钟dck的上升沿从第一主机侧数据总线301获取半字节数据n0和n1,在时钟dck的下降沿从第一主机侧数据总线301获取半字节数据n8和n9,并在固定延迟时间tpdm后,以3200mt/s的速率通过第一存储侧数据总线321将n0和n1一起发送到第一

×

8 dram芯片组341内的一个

×

8 dram芯片,将n8和n9一起发送到第一

×

8 dram芯片组341内的另一个

×

8 dram芯片。

44.类似地,第二高带宽数据缓存器312在时钟dck的上升沿获取半字节数据n2和n3,在时钟dck的下降沿获取半字节数据n10和n11,并在固定延迟时间tpdm后,将n2和n3一起发送到第二

×

8 dram芯片组342内的一个

×

8 dram芯片,将n10和n11一起发送到第二

×

8 dram芯片组342内的另一个

×

8 dram芯片。第三高带宽数据缓存器313在时钟dck的上升沿获取半字节数据n4和n5,在时钟dck的下降沿获取半字节数据n12和n13,并在固定延迟时间tpdm后,将n4和n5一起发送到第三

×

8 dram芯片组343内的一个

×

8 dram芯片,将n12和n13一起发送到第三

×

8 dram芯片组343内的另一个

×

8 dram芯片。第四高带宽数据缓存器314在时钟dck的上升沿获取半字节数据n6和n7,在时钟dck的下降沿获取半字节数据n14和n15,并在固定延迟时间tpdm后,将n6和n7一起发送到第四

×

8 dram芯片组344内的一个

×

8 dram芯片,将n14和n15一起发送到第四

×

8 dram芯片组344内的另一个

×

8 dram芯片。

45.在本发明实施例中,定义每个字节为一个ecc符号,mc通过对8个连续的数据字节在gf空间产生reed-solomon码以支持chipkill校正算法,并生成两个ecc字节。具体地,对8个连续的数据字节在gf(28)空间产生rs(10,8)码以支持chipkill校正算法,并生成两个ecc字节ecc0和ecc1。

46.第五高带宽数据缓存器315以6400mt/s的速率,在时钟dck的上升沿从第五主机侧数据总线305获取一个字节ecc0,在时钟dck的下降沿从第五主机侧数据总线305获取一个字节ecc1,并在固定延迟时间tpdm后,以3200mt/s的速率通过第五存储侧数据总线325将ecc0和ecc1一起发送到第五

×

8 dram芯片组345内的2个

×

8 dram芯片,每个dram芯片接收一个字节ecc。

47.在一些实施方式中,

×

8 dram芯片组341-345为20个

×

8 ddr4 dram芯片。在一些实施方式中,

×

8 dram芯片组341-345为20个

×

8ddr5 dram芯片。

48.在

×

8 dimm配置中,每个dram芯片的数据总线宽度为8位,每个通道的每次访问仅需激活10个dram芯片,通过选择合适的ecc模块进行编码,并将两个ecc数据分别存储在两个

×

8 dram芯片中,能够实现chipkill功能。因此与现有技术相比,本发明具有chipkill可靠性和更低的功耗。

49.图6是里德-所罗门码的结构示意图,其包括:k个m位的原始数据符号和2t个m位的奇偶校验符号,n=k+2t表示代码符号的总数,t表示可以纠正的错误符号数。在

×

4 d5-hbdimm中,m=4,k=16,t=1,n=18。在

×

8 d5-hbdimm中,m=8,k=8,t=1,n=10。因此,本发明实施例的d5-hbdimm中的任何单个dram芯片故障都可以得到纠正,由此实现chipkill功能。

50.在一些实施方式中,在

×

4 d5-hbdimm中,两个半字节的ecc0和ecc1可以使用以下

编码方式,以生成2个4位奇偶校验符号:

51.ecc0=n0+n1+

…

+n15;

52.ecc1=α[1]*n0+α[2]*n1+

…

α[16]*n15。

[0053]

其中,α[]是gf(24)上对应的伽罗瓦场。

[0054]

在一些实施方式中,在

×

8 d5-hbdimm中,两个字节的ecc0和ecc1可以使用以下编码方式,以生成2个8位奇偶校验符号:

[0055]

ecc0={n1,n0}+{n3,n2}+

…

+{n15,n14};

[0056]

ecc1=alpha[1]*{n1,n0}+alpha[2]*{n3,n2}+

…

+alpha[8]*{n15,n14}。

[0057]

其中,alpha[]是gf(28)上对应的伽罗瓦场。

[0058]

图7是本发明实施例的在d5-hbdimm中实现chipkill的流程示意图。如图7所示,在d5-hbdimm中实现chipkill的方法具体包括如下步骤:

[0059]

步骤s1:初始化d5-hbdimm;

[0060]

步骤s2:读取d5-hbdimm的配置;

[0061]

步骤s3:根据读取的d5-hbdimm的配置,判断d5-hbdimm是否支持chipkill功能;

[0062]

步骤s4-1:在d5-hbdimm支持chipkill功能时,进一步判断d5-hbdimm是否为

×

4 dimm;

[0063]

步骤s4-2:在d5-hbdimm不支持chipkill功能时,使用汉明(hamming)ecc编码,存储器控制器准备好对dimm进行访问,进入步骤s6;

[0064]

步骤s5-1:在d5-hbdimm是

×

4 dimm时,将接收的4个连续的数据位组合成与dram的数据宽度相同的一个半字节数据,对16个连续的半字节数据在gf(24)空间产生rs(18,16)码以支持chipkill校正算法,生成两个半字节ecc,存储器控制器准备好对dimm进行访问,进入步骤s6;

[0065]

步骤s5-2:在d5-hbdimm不是

×

4 dimm时,将两个连续的数据半字节组合成与dram的数据宽度相同的一个字节数据,对8个连续的字节数据在gf(28)空间产生rs(10,8)码以支持chipkill校正算法,生成两个长度为一个字节的ecc,存储器控制器准备好对dimm进行访问,进入步骤s6;

[0066]

步骤s6:存储器控制器对d5-hbdimm进行访问。

[0067]

其中,在d5-hbdimm支持chipkill功能时,步骤s6进一步包括如下步骤:

[0068]

以第一速率将第一数据传输至d5-hbdimm的第一子通道,该第一子通道包括第一组数据缓存器和第一组dram芯片;

[0069]

以第一速率将第二数据传输至d5-hbdimm的第二子通道,该第二子通道包括第二组数据缓存器和第二组dram芯片;

[0070]

第一组数据缓存器和第二组数据缓存器分别接收第一数据和第二数据,并以第二速率将第一数据和第二数据分别存储至第一组dram芯片和第二组dram芯片;第一组dram芯片和第二组dram芯片各自包括多个dram芯片组。

[0071]

以第一速率将第一ecc码传输至d5-hbdimm的第一子通道;

[0072]

以第一速率将第二ecc码传输至d5-hbdimm的第二子通道;

[0073]

第一组数据缓存器和第二组数据缓存器分别接收第一ecc码和第二ecc码,并以第二速率将第一ecc码和第二ecc码分别存储至第一组dram芯片和第二组dram芯片。

[0074]

如前所述,第二子通道具有与第一子通道相同的结构,下面以第一子通道为例,对上述接收和存储数据的过程进行详细说明。第二子通道具有与第一子通道相同的过程,在此不再赘述。

[0075]

具体地,第一组数据缓存器以第一速率从多个主机侧数据总线获取第一数据和第一ecc码,以第二速率从多个存储侧数据总线将第一数据和第一ecc码存储至多个dram芯片组;其中,主机侧数据总线、数据缓存器、存储侧数据总线和dram芯片组一一对应。

[0076]

在一些实施方式中,第一数据包括第一部分和第二部分,第一ecc码包括第一ecc数据和第二ecc数据。第一子通道在时钟的上升沿从多个主机侧数据总线获取第一数据的第一部分和第一ecc数据,在时钟的下降沿从多个主机侧数据总线获取第一数据的第二部分和第二ecc数据。在一些实施方式中,第一子通道在获取第一数据和第一ecc码后,固定延迟时间tpdm,再以第二速率从多个存储侧数据总线将第一数据和第一ecc码存储至多个dram芯片组。在一些实施方式中,tpdm在1.1ns+tck/4和1.62ns+tck/4之间,其中,tck是时钟dck的周期。

[0077]

在一些实施方式中,第二速率是第一速率的一半,例如,第一速率为6400mt/s,第二速率为3200mt/s。

[0078]

在一些实施方式中,d5-hbdimm是

×

4 dimm,dram芯片为

×

4 dram芯片,第一组dram芯片包含的多个dram芯片组中,一个dram芯片组具有2个dram芯片,其他dram芯片组分别具有4个dram芯片。第一ecc码存储在2个dram芯片所在的组中。在一些实施方式中,第一数据包含多个半字节数据,第一ecc数据和第二ecc数据的长度分别为半字节,多个半字节数据、第一ecc数据和第二ecc数据分别存储在第一组dram芯片的dram芯片中。也就是说,半字节数据中的每一个、第一ecc数据和第二ecc数据各自占用一个dram芯片。在一些实施方式中,第一数据包含16个半字节数据,第一组dram芯片包含18个dram芯片,16个半字节数据、第一ecc数据和第二ecc数据分别存储在第一组dram芯片的18个dram芯片中,也就是说,每次访问子通道需要激活18个dram芯片。

[0079]

在一些实施方式中,d5-hbdimm是

×

8 dimm,dram芯片为

×

8 dram芯片,第一组dram芯片包含的多个dram芯片组分别具有4个dram芯片。第一ecc码存储在其中一组dram芯片中。在一些实施方式中,第一数据包含多个半字节数据,第一ecc数据和第二ecc数据的长度分别为一个字节,多个半字节数据中的每两个、第一ecc数据和第二ecc数据分别存储在第一组dram芯片的dram芯片中。也就是说,半字节数据中的每两个、第一ecc数据和第二ecc数据各自占用一个dram芯片。在一些实施方式中,第一数据包含16个半字节数据,第一组dram芯片包含20个dram芯片,16个半字节数据中的每两个、第一ecc数据和第二ecc数据分别存储在第一组dram芯片的10个dram芯片中。

[0080]

也就是说,与

×

4 dimm相比,

×

8 dimm的每个子通道增加了两个dram芯片,但每次访问子通道仅需要激活其中的10个dram芯片。通过生成合适的ecc码,并将ecc码的数据存储在两个

×

8 dram芯片中,能够实现chipkill错误检测,具有高的可靠性,同时,由于每次访问激活的芯片较少,能够显著降低功耗。

[0081]

上述方法能够根据计算机系统用户的需要执行chipkill算法,并进一步确定d5-hbdimm是否具有所需数量的ecc芯片以对dram芯片执行chipkill算法,且能够在chipkill算法和hamming ecc之间进行切换,适于更多应用场景。

[0082]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包括于本技术的至少一个实施例或示例中。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0083]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或隐含地包括至少一个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

[0084]

流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或多个(两个或两个以上)用于实现特定逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分。并且本技术的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能。

[0085]

在流程图中表示或在此以其他方式描述的逻辑和/或步骤,例如,可以被认为是用于实现逻辑功能的可执行指令的定序列表,可以具体实现在任何计算机可读介质中,以供指令执行系统、装置或设备(如基于计算机的系统、包括处理器的系统或其他可以从指令执行系统、装置或设备取指令并执行指令的系统)使用,或结合这些指令执行系统、装置或设备而使用。

[0086]

应理解的是,本技术的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。上述实施例方法的全部或部分步骤是可以通过程序来指令相关的硬件完成,该程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

[0087]

此外,在本技术各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。上述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读存储介质中。该存储介质可以是只读存储器,磁盘或光盘等。

[0088]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到其各种变化或替换,这些都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1