半导体装置的形成方法与流程

[0001]

本发明实施例涉及半导体技术,尤其涉及一种半导体装置中的纳米晶体高介电常数薄膜的形成方法。

背景技术:

[0002]

半导体装置被用于各种电子应用,例如个人电脑、行动电话、数字相机以及其他电子设备。通常通过依序地在半导体基底上沉积材料的绝缘层或介电层、导电层以及半导体层,并利用光刻工艺图案化各种材料层以形成电路组件及元件来制造半导体装置。

[0003]

半导体产业通过不断缩小最小特征尺寸(minimum feature size)来持续提升各种电子组件(例如:晶体管、二极管、电阻器、电容器等等)的积集度(integration density),其允许在一给定面积内整合更多的部件。然而,随着最小特征尺寸的缩小,应解决的额外问题也随之出现。

技术实现要素:

[0004]

本发明实施例的目的在于提供一种半导体装置的形成方法,以解决上述至少一个问题。

[0005]

本发明实施例提供一种半导体装置的形成方法,此方法包括:首先,沉积介电层于半导体装置的通道区中的鳍片上,之后对介电层执行第一次退火工艺以形成多个纳米晶体区,这些纳米晶体区悬浮在介电层的非晶体基质层内并被非晶形基质层分隔。之后,沉积一金属层于半导体装置中的通道区的介电层上。

[0006]

本发明实施例提供一种半导体装置的形成方法,此方法包括:首先,形成半导体装置中的鳍式场效晶体管中的栅极介电层,此栅极电介质层包括介电材料。接着,在栅极介电层的介电材料中形成多个自包含晶体区,多个自包含晶体区包括多个晶形/非晶形界面,并且其中多个自包含晶体区通过栅极介电层的非晶形基质层的介电材料来彼此分离。之后,在半导体装置的鳍式场效晶体管的栅极介电层上沉积金属栅极结构。

[0007]

本发明实施例提供一种半导体装置,此装置包括:场效晶体管的鳍片;沉积于鳍片上的栅极介电层,此栅极介电层包括多个自包含纳米晶体区,此纳米晶体区包含多个晶形/非晶形界面,其中自包含晶体区通过栅极介电层的非晶形基质介电材料来彼此分离;以及金属栅极电极,沉积于栅极介电层上。

附图说明

[0008]

配合所附附图来阅读以下详细叙述为理解本公开的各个方面的最佳方式。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制。事实上,为了清楚地进行讨论,可能任意地放大或缩小各种特征的尺寸。

[0009]

图1根据一些实施例示出形成鳍式场效晶体管装置的工艺中的步骤。

[0010]

图2为根据一些实施例示出源极/漏极区及层间电介质(ild)层的形成。

[0011]

图3a-图3c为根据一些实施例以三个相关视图示出第一介电层的形成。

[0012]

图4为根据一些实施例示出可选的第一退火工艺。

[0013]

图5为根据一些实施例示出盖层的形成。

[0014]

图6a-图6b为根据一些实施例以两个相关视图示出可选的第二退火工艺。

[0015]

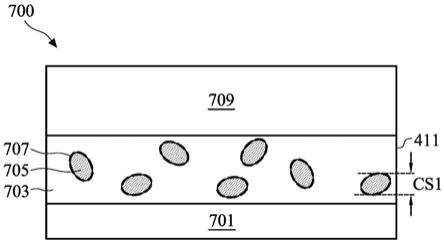

图7a-图7b为根据一些实施例示出纳米晶体高介电常数材料层的形成。

[0016]

图8a-图8b为根据一些实施例以两个相关视图示出栅极电极结构的形成。

[0017]

附图标记如下:

[0018]

100:半导体装置

[0019]

101:基板

[0020]

103:第一沟槽

[0021]

105:第一隔离区

[0022]

107:鳍片

[0023]

109:虚置栅极电介质

[0024]

111:虚置栅极电极

[0025]

113:第一间隔物

[0026]

115:虚置堆叠

[0027]

203:层间电介质层

[0028]

207:开口

[0029]

211:第一介电层

[0030]

401:沉积后退火工艺

[0031]

411:简易纳米晶体薄膜

[0032]

501,807:盖层

[0033]

601:顶盖后退火工艺

[0034]

611:化合物纳米晶体薄膜

[0035]

700,750:层状堆叠材料

[0036]

701:界面层

[0037]

703:非晶形基质层

[0038]

705,715:纳米晶体区

[0039]

707,717:整合界面

[0040]

709:盖层

[0041]

801:第一金属层

[0042]

803:第三金属材料

[0043]

805:栅极堆叠

[0044]

809:第一蚀刻停止层

[0045]

cs1,cs2:晶体尺寸

[0046]

a-a’,b-b’,c-c’:切割线

[0047]

t1,t2:厚度

[0048]

h1,h2:高度

[0049]

d1:距离

具体实施方式

[0050]

以下发明实施例提供了许多不同的实施例或范例,用于实施本发明的不同特征。各部件和其配置的具体范例描述如下,以简化本发明实施例的说明。当然,这些仅仅是范例,并非用以限制。举例而言,叙述中若提及第一部件形成在第二部件之上或上,可能包含所形成的第一和第二部件为直接接触的实施例,也可能包含额外的部件形成在第一和第二部件之间,使得它们不直接接触的实施例。此外,本发明实施例可能在不同的范例中重复参考数字及/或字母。如此重复是为了简明和清楚,而非用以表示所讨论的不同实施例及/或配置之间的关系。

[0051]

再者,其中可能用到与空间相对用词,例如“在

……

之下”、“下方”、“较低的”、“上方”、“较高的”等类似用词,是为了便于描述附图中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及附图中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

[0052]

参照图1,其示出半导体装置100(例如鳍式场效晶体管装置)的剖面视图。在一实施例中,鳍式场效晶体管装置100包括基板101和形成于其中的第一沟槽103。基板101可为硅基板,尽管也可使用其他基板,像是绝缘层上半导体(semiconductor-on-insulator(soi))、应变soi(strained soi)以及绝缘体上硅锗。基板101可为p型半导体,尽管在其他实施例中可为n型半导体。

[0053]

可以形成第一沟槽103以作为最终形成第一隔离区105的起始步骤。可通过掩膜层(在图1中并未单独示出)以及适合的蚀刻工艺来形成第一沟槽103。举例来说,掩膜层可为通过化学气相沉积(cvd)所形成的包括氮化硅的硬掩膜,尽管也可利用其他材料,像是氧化物、氮氧化物、碳化硅、上述的组合或类似者,以及其他工艺,像是等离子体辅助化学气相沉积(pecvd)、低压化学气相沉积(lpcvd)或者甚至是形成氧化硅之后接着进行氮化。一旦形成后,可通过适合的光刻工艺来图案化掩膜层以露出基板101中将会被移除以形成第一沟槽103的多个部分。

[0054]

然而,如本发明所属技术领域中技术人员所知,在为了形成第一沟槽103而露出基板101的其他部分时,上述形成掩膜层的工艺和材料并不是用来保护基板101的部分的唯一方法。可以通过任何适合的工艺(例如图案化且显影光刻胶)来露出基板101将被移除以形成第一沟槽103的部分。本实施例的范围完全意欲包括这类的所有方法。

[0055]

一旦形成且图案化掩膜层,即在基板101中形成第一沟槽103。可通过适合的工艺(例如反应离子蚀刻(reactive ion etching,rie))来移除露出的基板101以在基板101中形成第一沟槽103,尽管可利用任何适合的工艺。在一实施例中,第一沟槽103可以形成为具有距离基板101的表面小于大约5000埃的第一深度,例如大约2500埃。

[0056]

然而,本发明所属技术领域中技术人员可了解,上述形成第一沟槽103的工艺仅为可能的工艺,并且并非意味着是唯一的实施例,而是可利用用来形成第一沟层103的任何适合工艺,并且可以使用包括任何数量的掩膜和移除步骤的任何适合工艺。

[0057]

除了形成第一沟槽103,掩膜工艺以及蚀刻工艺另外由基板101中残留而未被移除的部分形成鳍片107。为了方便起见,附图中示出的鳍片107通过虚线及不同的图案与基板101分隔,尽管可能出现或未出现分隔的物理表示。如同以下的讨论,鳍片107可用来形成多

栅极鳍式场效晶体管的通道区。虽然图1只示出从基板101形成三个鳍片107,但可以使用任何数量的鳍片107。

[0058]

可形成鳍片107使得其在基板101表面的宽度介于约5纳米以及约80纳米之间,像是约30纳米。另外,鳍片107可以介于约10纳米以及约100纳米之间的距离彼此隔开,像是约50纳米。通过以这种方式使鳍片107彼此隔开,鳍片107可各自形成分隔的通道区域,同时仍足够靠近以共用共同栅极。

[0059]

一旦形成第一沟槽103与鳍片107,可用介电材料填充第一沟槽103,且第一沟槽中的介电材料可以被凹蚀以形成第一隔离区105。介电材料可为氧化材料、高密度等离子体(high-density plasma,hdp)氧化物或类似者。可在可选地清洗或内衬(lining)第一沟槽103之后,利用化学气相沉积(cvd)方法(例如:高纵横比工艺(high-aspect ratio process,harp))、高密度等离子体cvd方法或本发明所属技术领域中已知的其他适合的方法来形成介电材料。

[0060]

可通过以下方式填充第一沟槽103:用介电材料过量填充第一沟槽103和基板101,接着通过例如化学机械研磨(cmp)、蚀刻、上述的组合等适合的工艺来移除第一沟槽103和鳍片107外部的多余材料。在一实施例中,移除工艺也移除了在鳍片107上方的任何介电材料,因此将介电材料移除的步骤将露出鳍片107的表面以进行进一步的工艺步骤。

[0061]

一旦用介电材料填充第一沟槽103,介电材料可接着被凹蚀以远离鳍片107的表面。可执行凹蚀步骤以露出鳍片107中相邻于顶面的侧壁的至少一部分。可通过将鳍片107的顶面浸入例如hf的蚀刻剂中的湿式蚀刻来凹蚀电介质材料,尽管也可以使用其他蚀刻剂(例如h2)以及其他方法,例如反应离子蚀刻、使用像是nh3/nf3的蚀刻剂的干式蚀刻、化学氧化物去除或干式化学清洗(dry chemical clean)。可凹蚀介电材料以与鳍片107有介于约50埃以及约500埃之间的距离,例如约400埃。此外,也可通过凹蚀步骤来移除任何位于鳍片107上方的剩余的电介质材料,来确保鳍片107露出以进行进一步的工艺。

[0062]

然而,本发明所属技术领域中技术人员可了解,上述步骤仅为用于填充和凹蚀介电材料的整个工艺流程的一部分。举例来说,可利用内衬步骤、清洗步骤、退火步骤、间隙填充步骤、上述的组合以及类似者来形成第一沟槽103且以介电材料填充第一沟槽103。本实施例的范围完全意欲包括所有可能的工艺步骤。

[0063]

在形成第一隔离区105之后,虚置栅极电介质109、在虚置栅极电介质109上方的虚置栅极电极111以及第一间隔物113可形成于每个鳍片107上。在一实施例中,虚置栅极电介质109可通过热氧化、化学气相沉积、溅镀或本发明所属技术领域中已知的任何其他方法来形成栅极电介质。根据形成栅极电介质的技术,虚置栅极电介质109在鳍片107顶部上的厚度可与在鳍片107侧壁上的厚度不同。

[0064]

虚置栅极电介质109可包括例如二氧化硅或氮氧化硅的材料,其厚度在约3埃至约100埃的范围内,例如约10埃。虚置栅极电介质109可由高介电常数(高k值)材料(例如:相对介电常数大于约5)来形成,例如氧化镧(la2o3)、氧化铝(al2o3)、氧化铪(hfo2)、氧氮化铪(hfon)或氧化锆(zro2)或上述的组合,其等效氧化物厚度为约0.5埃至约100埃,例如约10埃或更小。此外,二氧化硅、氮氧化硅及/或高介电常数材料的任何组合也可用于虚置栅极电介质109。

[0065]

虚置栅极电极111可包括导电材料,且可选自由w、al、cu、alcu、ti、tialn、tac、

tacn、tasin、mn、zr、tin、ta、tan、co、ni、上述的组合或类似者所组成的群组。虚置栅极电极111可通过化学气相沉积(cvd)、溅镀沉积或本发明所属技术领域中已知且用于沉积导电材料的其他技术来沉积。虚置栅极电极111的厚度可介于约5埃至约200埃的范围内。虚置栅极电极111可具有非平坦的顶面,且可在图案化虚置栅极电极111之前或蚀刻栅极之前被平坦化。可在这时引入或不引入离子。可通过离子注入技术引入离子。

[0066]

一旦形成,虚置栅极电介质109与虚置栅极电极111可被图案化以在鳍片107上形成一系列的虚置堆叠115。虚置堆叠115定义靠近虚置栅极电介质109的鳍片107的每一侧上的多重通道区。可通过使用例如本发明所属技术领域中已知的沉积以及光刻技术来沉积且图案化虚置栅极电极111上的栅极掩膜(未在图1中单独示出)以形成虚置堆叠115。栅极掩膜可结合常用的掩膜和牺牲材料,例如(但不限于)氧化硅、氧氮化硅、sicon、sic、sioc及/或氮化硅,并且可以沉积到达介于约5埃及约200埃之间的厚度。可通过干式蚀刻工艺来蚀刻虚置栅极电极111及虚置栅极电介质109以形成图案化栅极堆叠115。

[0067]

一旦虚置堆叠115被图案化,即可形成第一间隔物113。第一间隔物113可形成于虚置堆叠115的相反侧上。第一间隔物113通常通过在先前形成的结构上毯覆沉积一间隔物层(未在图1中单独示出)来形成。间隔物层可包括sin、氮氧化物、sic、sion、siocn、sioc、氧化物以及类似者,且可通过用于形成此种膜层的方法来形成,例如化学气相沉积(cvd)、等离子体辅助cvd、溅击、以及本发明所属技术领域中已知的其他方法。间隔物层可包括具有不同蚀刻特性的不同材料,或者与第一隔离区105中的介电材料相同的材料。接着可图案化第一间隔物113,像是通过一道或多道蚀刻工艺来从结构的水平表面上移除间隔层来形成第一间隔物113。

[0068]

在一实施例中,第一间隔物113可被形成为具有介于约5埃以及约500埃的第一厚度t1,例如为50埃。另外,一旦形成第一间隔物113,相邻于一堆叠115的一第一间隔物113可与相邻于另一堆叠115的一第一间隔物以介于约5纳米与约200纳米之间的距离d1分离,例如约20纳米。然而,可使用任何适合的厚度以及距离。

[0069]

图2示出半导体装置100的源极/漏极区201。图2进一步示出移除栅极堆叠115以在第一间隔物113之间形成开口207,以及露出半导体装置100的通道区中的鳍片107以执行进一步工艺。

[0070]

根据一些实施例,移除如同图1中所示的未被虚置堆叠115保护且未被第一间隔物113保护的区域的鳍片107的部分。一旦移除鳍片107的这些区域,便再生长(regrown)源极/漏极区201。移除未被虚置堆叠115保护且未被第一间隔物113保护的区域的鳍片107的步骤可通过利用虚置堆叠115以及第一间隔物113作为硬掩膜的反应离子蚀刻(rie)来执行,或者通过任何适合的移除工艺来执行。移除工艺可持续直到鳍片107与第一间隔区105的表面齐平或者低于第一间隔区105的表面。

[0071]

一旦移除鳍片107的这些部分,便放置硬掩膜并将其图案化以覆盖虚置栅极电极111以防止其生长,并且可在与位于虚置堆叠115下方的通道区中的每个鳍片107接触的状态下再生长源极/漏极区201。在一实施例中,可再生长源极/漏极区201,且在一些实施例中,可再生长源极/漏极区201以形成对位于虚置堆叠115下方的鳍片107的通道区施加应力的应力源。在一实施例中,鳍片107包括硅且鳍式场效晶体管为p型装置。可通过选择性的外延工艺且使用像是硅的材料来再生长源极/漏极区201,或者使用像是具有与通道区不同的

晶格常数的材料,例如硅锗。在其他实施例中,源极/漏极区201的材料可包括例如gaas、gap、gan、inp、inas、insb、gaasp、algan、alinas、algaas、gainas、gainp、gainasp、上述的组合或类似者。外延生长工艺可使用例如硅烷、二氯硅烷、锗烷等的前驱物,并且可以持续介于约5分钟与约120分钟之间(例如约30分钟)。

[0072]

在一实施例中,源极/漏极区201可以形成为具有介于约5埃以及约1000埃之间的厚度,并且可以在第一隔离区105上具有介于约10埃以及约500埃之间的第一高度h1,例如约200埃。然而,可以使用任何合适的高度。

[0073]

一旦形成源极/漏极区201,可通过将适当的掺杂注入进入源极/漏极区201来补充位于虚置堆叠115下方的通道区中的鳍片107中的掺杂。举例来说,可注入像是硼、镓、铟或类似者的p型掺杂以形成pmos装置。替代地,可注入像是磷、砷、锑或类似者的n型掺杂以形成nmos装置。可利用虚置堆叠115以及第一间隔物113作为掩膜来注入这些掺杂。应注意的是,本发明所属技术领域中技术人员可了解,可利用许多其他的工艺、步骤或类似者来注入掺杂。举例来说,本发明所属技术领域中技术人员将了解,可以使用间隔物和内衬的各种组合来执行多个注入工艺,以形成具有适合特定目的的特定形状或特性的源极/漏极区域。这些工艺中的任何一种都可以用来注入掺杂,并且以上描述并非旨在将本发明限制于上述步骤。

[0074]

图2也示出位于虚置堆叠115上方且位于源极/漏极区201上方的层间电介质(ild)层203(在图2中以虚线示出以更清楚地示出下方的结构)的形成。层间电介质层203可包括像是硼磷硅酸盐玻璃(boron phosphorous silicate glass,bpsg)的材料,尽管可使用任何适合的电介质。层间电介质层203可通过像是pecvd的工艺来形成,尽管可替代地利用其他工艺,像是lpvcd。层间电介质层203可被形成为具有介于约100埃及约3000埃之间的厚度t2。一旦形成,层间电介质层203可通过像是化学机械研磨工艺的平坦化工艺来与虚置堆叠115以及第一间隔物113齐平,尽管可使用任何适合的工艺。

[0075]

在形成层间电介质层203之后,可移除虚置堆叠115的虚置栅极电极111以及虚置栅极电介质109以提供第一间隔物之间的开口207,且露出半导体装置100的通道区中的鳍片107。在一实施例中,可通过例如一道或多道干式蚀刻工艺来移除虚置栅极电极111以及虚置栅极电介质109,其中干式蚀刻工艺所使用的蚀刻剂对于虚置堆叠115的虚置栅极电极111以及虚置栅极电介质109的材料具有选择性。然而,可使用任何适合的移除工艺。一旦虚置堆叠115的虚置栅极电极111以及虚置栅极电介质109被移除,剩下的开口207可用来在其中形成金属栅极堆叠结构,以下将对其进行详细讨论。

[0076]

参照图3a,附图示出一旦移除了虚置堆叠115的虚置栅极电极111以及虚置栅极电介质109,便在半导体装置100上毯覆沉积第一介电层211。在一些实施例中,第一介电层211使用高介电常数材料(例如:相对介电常数大于约5)来沉积作为非晶形基质层,此材料包括氧化铪(hfo2)、氧化锆(zro2)、上述的组合或类似者。根据一些实施例,第一介电层211通过像是原子层沉积(ald)或类似者的工艺来沉积到达介于约1纳米以及约3纳米之间的厚度,例如约1.5纳米。尽管可以任何适合的材料、任何适合的沉积工艺以及任何适合的厚度来形成第一介电层211。

[0077]

在一实施例中,可通过利用一组循环的步骤来执行原子层沉积工艺,这些步骤可引入用于第一自限反应的第一前驱物、吹净第一前驱物、引入用于第二自限反应的第二前

驱物、并吹净第二前驱物以完成第一次循环。一旦完成第一次循环,可重复第一次循环来进行第二次循环,每个循环沉积所需材料的单层。举例来说,在第一介电层211为氧化铪的一实施例中,可引入像是氯化铪的第一前驱物并且接着吹净,并且引入像是氧或者臭氧的第二前驱物以形成氧化铪的单一单层。

[0078]

此外,在一些使用原子层沉积形成初期晶体而非完全的非晶形材料的实施例中,可通过高温原子层沉积在高于约300℃的温度下(例如约350℃),并且以介于约300秒至约1800秒之间的周期(例如约600秒)来沉积第一介电层211。如此一来,第一介电层211被沉积作为高介电常数材料的纳米晶体薄膜,此纳米晶体薄膜包括在非晶形基质层中悬浮的多个自包含纳米晶体(self-contained nano-crystallite)区。下文将对纳米晶体区与非晶形基质层进行更详细的讨论。

[0079]

图3b沿着线b-b’示出图3a的剖面视图。特别地,图3b示出第一介电层211的沉积,其中第一介电层211保形地沉积在经平坦化的第一间隔物113的上表面和侧壁上、在半导体装置的通道区中的鳍片107于形成于第一间隔物113之间的开口207的底部所露出的表面上以及在半导体装置100的源极/漏极区201中的层间电介质层203所露出的表面上。

[0080]

图3c沿着线c-c’示出图3a的剖面视图。特别地,图3c示出第一介电层211的沉积,其中第一介电层211保形地沉积在半导体装置的通道区中的鳍片107的露出的表面上,此露出的表面形成于第一间隔物113侧壁之间的开口207中。

[0081]

图4根据一些实施例示出可选的沉积后退火(post deposit anneal,pda)工艺(在图4中以标示为401的箭头来表示)。举例来说,在沉积工艺并未形成初期晶体或者提供最小量晶体的实施例中,一旦沉积第一介电层211,可执行可选的沉积后退火工艺以将第一介电层211退火,使得多个第一型纳米晶体区形成于非晶形基质层中及/或进一步地使任何形成于非晶形基质层中的第一型纳米晶体区结晶。如此一来,由第一介电层211形成了简易纳米晶体薄膜411,且设置于半导体装置100的通道区的鳍片107上。下文将对纳米晶体区与非晶形基质层进行更详细的讨论。

[0082]

在一实施例中,可在低于约700℃(例如约500℃)的温度下,并且以介于约5秒与约1800秒之间(例如约300秒)的周期来执行可选的沉积后退火(pda)工艺作为低温浸入式退火工艺(low-temperature soak anneal process)。在其他实施例中,可在高于约800℃(例如约1100℃)的温度下,并且以小于100毫秒(例如约3毫秒)的周期执行可选的沉积后退火(pda)工艺。在另外的实施例中,可在介于约700℃及约1000℃的温度下(例如约850℃),并且以大于0.5秒(例如约1.5秒)的周期来执行可选的沉积后退火(pda)工艺作为尖峰退火(spike anneal)工艺。然而,可使用任何适合的温度以及任何适合的周期来执行任何低温沉积后浸入式退火工艺、高温沉积后尖峰退火工艺以及沉积后尖峰退火工艺。

[0083]

图5示出盖层501在半导体装置100上的沉积工艺。在一些实施例中,盖层501可形成于图2中的第一介电层211上;且在一些实施例中,盖层501可形成于图4中的第一型纳米晶体薄膜411上。盖层501可使用一种或多种材料来沉积为单层或双层薄膜,其材料包括例如tin、tan或w;非晶形硅(例如a-si);高介电常数电介质,像是al2o3、zro2及tio2;上述的化合物或类似者。盖层501可通过像是原子层沉积(ald)或类似者的工艺来沉积到达介于约1纳米以及约50纳米之间的厚度,例如约2纳米。尽管可使用任何适合的材料、任何适合的沉积工艺以及任何适合的厚度来形成盖层501。

[0084]

图6a根据一些实施例示出可选的顶盖后退火(post capping anneal,pca)工艺(在图6中以标示为601的箭头来表示)。基于用来形成高介电常数介电材料211的材料组成及/或基于用来形成盖层501的材料组成,在一些实施例中,可单独执行可选的顶盖后退火(pca)工艺,且与后沉积退火(pda)分开执行。在其他实施例中,基于用来形成高介电常数介电材料211的材料组成及/或基于用来形成盖层501的材料组成,可结合后沉积退火(pda)来执行可选的顶盖后退火(pca)工艺。

[0085]

举例来说,根据一些实施例,在第一介电层211上沉积盖层之后,可在不执行pda工艺的情况下使用可选的顶盖后退火(pca)工艺来初步退火第一介电层211,并在高介电常数材料的非晶形基质层内初步形成第一型纳米晶体区。如此一来,由第一介电层211形成了简易纳米晶体薄膜411,且设置于通道区中的鳍片107上。

[0086]

在其他实施例中,在例如通过可选的后沉积退火(pda)工艺所形成的简易纳米晶体薄膜411上沉积盖层501之后,可使用可选的顶盖后退火(pca)工艺以进一步使先前在简易纳米晶体薄膜411的非晶形高介电常数材料中形成的任何第一型纳米晶体区结晶,及/或在非晶形高介电常数材料中初步形成第二型纳米晶体区。如此一来,由第一介电层211形成化合物纳米晶体薄膜611,且设置于通道区的鳍片107上。

[0087]

在一实施例中,可在介于约700℃及约1000℃的温度下(例如约850℃),并且以大于0.5秒(例如约1.5秒)的周期执行可选的后金属化退火(post metallization anneal,pma)及/或可选的顶盖后退火(pca)工艺作为尖峰退火工艺。然而,可使用任何适合的温度以及任何适合的周期来执行可选的后金属化退火(pma)工艺及/或可选的顶盖后退火(pca)工艺。

[0088]

尽管本文公开的实施例针对半导体装置100的鳍片107的通道区上的高介电常数材料薄膜的沉积和退火工艺,但高介电常数材料薄膜的沉积和退火工艺可在不背离本发明的精神的情况下用于其他应用中,并且被认为落在本文所公开的实施例的范围内。此外,本文所提供的例子针对具有小于约2.5纳米的厚度的高介电常数材料薄膜、且具有包括例如hfo2的材料的薄膜组成,可使用其他适合的区域、其他半导体装置、其他适合的厚度以及其他适合的材料,并且被认为落在本文所公开的实施例的范围内。如此一来,可以根据薄膜厚度以及薄膜组成来改变热预算(thermal budget),而不背离所公开的实施例的精神。

[0089]

图6b沿着线b-b’示出在沉积盖层501且在图6a中所示出的可选的顶盖后退火工艺之后的图3a的剖面视图。特别地,图6b示出盖层保形地设置501在半导体装置100的化合物纳米晶体薄膜611的表面上。如此一来,盖层501沿着化合物纳米晶体薄膜611保形地设置,此化合物纳米晶体薄膜611沿着经平坦化的第一间隔物113的上表面的侧面以及侧壁、沿着通道区中的鳍片107在开口207底部的表面并且沿着源极/漏极区201上的层间电介质层203的表面设置。

[0090]

图7a更详细地示出例如在简易的纳米晶体薄膜411中的多个纳米晶体区705的形成。图7a示出层状堆叠材料700的一部分,例如包括一部分材料的在半导体装置100的通道区中的鳍片107上方的简易纳米晶体薄膜411。在一些实施例中,层状堆叠材料700包括界面层701,此界面层701配置在半导体装置的通道区中的鳍片107的上表面与简易纳米晶体薄膜411之间。在其他实施例中,简易纳米晶体薄膜411可设置在鳍片107的上表面上方,且与鳍片107的上表面接触。在一些实施例中,层状堆叠材料700包括设置于简易纳米晶体薄膜

411上方的盖层709。

[0091]

在一实施例中,界面层701可为例如二氧化硅的材料,其通过例如原位蒸汽产生(in situ steam generation,issg)的工艺所形成。然而,可使用任何适合的材料或形成工艺。

[0092]

简易纳米晶体薄膜411可由第一介电层211形成,且通过上述关于图3a-图3c和图4的一道或多道沉积与退火工艺来退火。根据一些实施例,简易纳米晶体薄膜411可通过如同上文所详细讨论的一道或多道结晶工艺(例如:ht-ald、lt-pda、ht-pda及/或pda/pma)来形成。如此一来,简易纳米晶体薄膜411形成为具有多个纳米晶体区705悬浮在非晶形基质层703中的高介电常数介电层。

[0093]

图7a进一步示出纳米晶体区705形成为多个包括整合界面(coherence interface)707的自包含晶体材料,此整合界面707包括在纳米晶体区705的自包含晶体材料与非晶形基质层703的非晶形材料之间的多个晶形/非晶形界面。非晶形基质层703的非晶形材料有效地分离纳米晶体区705的晶界(grain boundaries)。如此一来,通过形成简易纳米晶体薄膜411,可完全避免漏电路径(leakage path)以及氧化剂路径(oxidant path)及/或将其最小化。因此,在制造半导体装置100时可将缺陷最小化及/或避免缺陷,导致半导体装置100的产量提升、效能提升且可靠性增加。

[0094]

简易纳米晶体薄膜411的结晶区域比被定义为多个纳米晶体区705的体积相对于简易纳米晶体薄膜411的总体积的百分比例。根据一些实施例,简易纳米晶体薄膜411的结晶区域比可介于约10体积百分比与约80体积百分比之间,例如介于约30体积百分比与约50体积百分比之间。可形成多个纳米晶体区705以具有介于约0.5纳米与约10纳米之间的晶体尺寸(crystallite size)(cs1)(例如:一或多个剖面直径),例如约3纳米。然而,可使用任何适合的结晶区域比以及任何适合的晶体尺寸。

[0095]

此外,简易纳米晶体薄膜411的介电材料可为掺杂或未掺杂的。在一些实施例中,可使用例如硅(si)、镧(la)、钇(y)、氮(n)、钪(sc)、钆(gd)、上述的组合或类似者来掺杂简易纳米晶体薄膜411的介电材料。然而,可使用任何其他适合的掺杂。基于所使用的掺杂及/或所使用的工艺控制(例如:厚度、热预算、退火的上升及下降速率),可修改纳米晶体区705的晶相(例如:四方晶(tetragonal)、立方晶(cubic)、斜方晶(orthorhombic)、菱面体(rhombohedral)等)。如此一来,可修改简易纳米晶体薄膜411的物理性质以提供与单独的非晶形基质层703相较之下更高的介电常数质及/或更强的铁电性质。此外,可通过控制一个或多个相边界(phase boundary)参数来维持简易纳米晶体薄膜411的经修改的物理性质,相边界参数包括:结晶区域比例、温度及/或由掺杂所引起的相分离以留在简易纳米晶体薄膜411的材料中各自晶相的准同型相界(morphotropic phase boundaries)。

[0096]

举例来说,相较于单独的非晶体基质层703,基于纳米晶体区705的四方晶相和立方晶相修改使得简易纳米晶体薄膜411具有增强的高介电常数值或介电常数。根据一些实施例,纳米晶体区705的四方晶相修改提供介于约25以及约70之间的介电常数(例如约40),且纳米晶体区705的立方晶相修改提供介于约20和约40之间(例如约30)的高介电常数值。

[0097]

如同其他的例子,基于纳米晶体区705的斜方晶相和菱面体相修改,与单独的非晶形基质层703相比,简易纳米晶体薄膜411具有增强的铁电性质,像是极化矫顽力(polarization coercivity)与极化保持性(polarization retentivity)。根据一些实施

例,对于纳米晶体区705的斜方晶相修改提供介于约0.1uc/cm2(微库仑/平方公分)及约15uc/cm2之间的残留极化(remnant polarization),例如约0.5uc/cm2,并且对于纳米晶体区705的菱面体相修改提供介于约0.1uc/cm2及约15uc/cm2之间的残留极化,例如约0.5uc/cm2。

[0098]

图7b更详细地示出例如在化合物纳米晶体薄膜611中包括整合界面717的多个纳米晶体区715。图7b示出层状堆叠材料750的一部分,此材料的部分包括例如在半导体装置100的通道区中的鳍片107上的化合物纳米晶体薄膜611。在一些实施例中,层状堆叠材料750包括设置于半导体装置的通道区中的鳍片107的上表面以及化合物纳米晶体薄膜611之间的界面层701。在其他实施例中,化合物纳米晶体薄膜611可设置于鳍片107的上表面上方,且与鳍片107的上表面接触。在一些实施例中,层状堆叠材料750包括设置于化合物纳米晶体薄膜611上方的盖层709。

[0099]

化合物纳米晶体薄膜611可被形成为非晶形高介电常数层211,且通过上述关于图3a-图3c、第4-5图以及图6a-图6b的一道或多道沉积与退火工艺来退火。根据一些实施例,化合物纳米晶体薄膜611由一种或多种介电材料形成,此介电材料包括hfo2、zro2、上述的合金及类似者,且可为掺杂或非掺杂。然而,可将任何适合的材料用于化合物纳米晶体薄膜611。在一些实施例中,化合物纳米晶体薄膜611的介电材料可使用一种或多种材料来掺杂,像是硅(si)、镧(la)、钇(y)、氮(n)、钪(sc)、钆(gd)、上述的组合或类似者。然而,可使用任何其他适合的掺杂。如此一来,化合物纳米晶体薄膜611包括非晶形基质层703中的多个化合物纳米晶体区715。

[0100]

根据一些实施例,化合物纳米晶体区715可包括图7a中已进行进一步工艺的多个纳米晶体区705。举例来说,可对图7a中的简易纳米晶体薄膜411进行第二退火工艺(例如:顶盖后退火工艺(pca))。如此一来,举例来说,化合物纳米晶体区715可更大程度地结晶以具有大于第一晶体尺寸(cs1)的第二晶体尺寸(cs2)(例如:一个或多个剖面直径)。根据一些实施例,第二晶体尺寸(cs2)介于约0.5纳米及约10纳米之间,例如约5纳米。然而,可使用任何适合的结晶区域比例以及任何适合的晶体尺寸。

[0101]

此外,在一些实施例中,注入掺杂的化合物纳米晶体区715可以具有与非晶形基质层703不同的组成。举例来说,在一实施例中,纳米晶体区715可具有介于约1原子百分比(atomic percentage)及约50原子百分比之间的掺杂浓度,例如约4原子百分比,而非晶形基质层703可具有较小的掺杂浓度,其介于约0.1原子百分比及约10原子百分比之间,例如约0.4原子百分比。然而,可使用任何适合的掺杂浓度。

[0102]

化合物纳米晶体薄膜611的结晶区域比例被定义为多个纳米晶体区715的体积相对于化合物纳米晶体薄膜611的总体积的百分比例。根据一些实施例,化合物纳米晶体薄膜611的结晶区域比可介于约10体积百分比与约80体积百分比之间,例如介于约30体积百分比与约50体积百分比之间。

[0103]

图8a与图8b根据一些实施例以两个视图示出金属栅极电极结构。一旦盖层501如同图6b所示地被沉积,可在盖层501上沉积一系列的金属层。根据一些实施例,可与盖层501相邻地形成第一金属层801,并且可由第一金属材料形成,例如ti、tialn、tac、tacn、tasin、mn、zr、tin、tan、ru、mo、wn、其他金属氧化物、金属氮化物、金属硅酸盐、过渡金属氧化物、过渡金属氮化物、过渡金属硅酸盐、金属氮氧化物,金属铝酸盐、硅酸锆、铝酸锆、上述的组合

或类似者。第一金属层801的第一金属材料可通过例如原子层沉积、化学气相沉积、溅镀或类似者的沉积工艺来沉积到达介于约5埃及约200埃的厚度,尽管可使用任何适合的沉积工艺或厚度。

[0104]

在一些实施例中,第一金属层801可为包括相邻于第一金属材料而形成的第二金属材料的化合物金属层,且在一特定实施例中,第二金属材料可相似于第一金属材料。举例来说,第二金属材料可由例如ti、tialn、tac、tacn、tasin、mn、zr、tin、tan、ru、mo、wn、其他金属氧化物、金属氮化物、金属硅酸盐、过渡金属氧化物、过渡金属氮化物、过渡金属硅酸盐、金属氮氧化物,金属铝酸盐、硅酸锆、铝酸锆、上述的组合或类似者的第二金属材料来形成。此外,第一金属层801的第二金属材料可通过例如原子层沉积、化学气相沉积、溅镀或类似者的沉积工艺来沉积到达介于约5埃及约200埃的厚度,尽管可使用任何适合的沉积工艺或厚度。

[0105]

第三金属材料803填充通过移除虚置栅极电极111而留下的开口207的剩余部分。在一实施例中,第三金属材料803可由例如w、al、alcu、ti、tialn、tac、tacn、tasin、mn、zr、tin、ta、tan、co、ni、上述的组合或类似者的第三金属材料来形成,且可通过例如原子层沉积、化学气相沉积、溅镀或类似者的沉积工艺来填充或过量填充通过移除虚置栅极电极111而留下的开口207。在一特定实施例中,第三金属材料803可沉积到达介于约5埃及约500埃的厚度,尽管可使用任何适合的材料、沉积工艺或厚度。

[0106]

一旦通过移除虚置栅极电极111而留下的开口207被填充,可由填充开口207的材料形成栅极堆叠805,其中通过对材料进行平坦化来移除任何在开口207外部的多余材料。在特定实施例中,可通过例如化学机械研磨(cmp)的平坦化工艺来执行移除工艺。然而,可使用任何合适的平坦化工艺及移除工艺。

[0107]

在形成且平坦化栅极堆叠805的材料之后,栅极堆叠805的材料可被凹蚀且以盖层807封盖。在一实施例中。栅极堆叠805的材料可通过例如湿式或干式蚀刻工艺来凹蚀,此工艺使用对栅极堆叠805的材料具有选择性的蚀刻剂。在一实施例中,栅极堆叠805的材料可被凹蚀介于约5纳米及约150纳米之间的距离,例如约120纳米。然而,可使用任何适合的工艺与距离。

[0108]

一旦栅极堆叠805的材料被凹蚀,可沉积盖层807并且使其与第一间隔物113齐平。在一实施例中,盖层807的材料为例如sin、sion、sicon、sic、sioc、上述的组合或类似者,通过例如原子层沉积、化学气相沉积、溅镀或类似者的沉积工艺来沉积。盖层807可沉积到达介于约5埃及约200埃之间的厚度,且接着通过像是化学机械研磨的平坦化工艺来平坦化,使得盖层807与第一间隔物113齐平。

[0109]

图8a与图8b另外示出第一蚀刻停止层809形成于栅极堆叠805上。在一实施例中,第一蚀刻停止层809可通过等离子体辅助化学气相沉积(pecvd)由氮化硅形成,尽管可使用其他材料,例如sion、sicon、sic、sioc、sic

x

n

y

、sio

x

、其他电介质、上述的组合或类似者,并且可替代地使用形成第一蚀刻停止层809的替代技术,像是低压cvd(lpcvd)、pvd或类似者。第一蚀刻停止层809可形成为介于约5埃及约200埃之间的厚度,或者介于约5埃及约50埃之间。

[0110]

图8b示出半导体装置100在沉积第一蚀刻停止层809之后的透视图。图8b更示出切割线b-b’,其中图8a通过此线示出剖面图。

[0111]

上述的高级的光刻工艺、方法以及材料可用于任何应用中,包括鳍式场效晶体管(finfet)。举例来说,可图案化鳍片以在部件之间产生相对紧密的间隔,其非常适合上述的发明实施例。此外,可根据以上发明实施例来对用于形成鳍式场效晶体管鳍片的间隔物进行处理。

[0112]

此外,鳍片可通过任何适合的方法图案化。例如,可利用包括双重图案化或多重图案化的一道或多道光刻工艺来图案化鳍片。一般来说,双重图案化或多重图案化工艺结合了光刻工艺及自我对准工艺,可创造具有例如比使用单一、指向性的光刻工艺能获得的节距还要更小的节距的图案。举例来说,在一实施例中,一牺牲层在基板上形成,并且以光刻工艺进行图案化。间隔物沿着图案化的牺牲层以自我对准工艺形成。接着移除牺牲层,剩下的间隔物可接着用来将鳍片图案化。

[0113]

根据本发明实施例,简易纳米晶体薄膜411以及化合物纳米晶体薄膜611可形成为纯hfo2、zro2以及其合金的介电层,此介电层包括悬浮在非晶形基质层703的非晶形材料中的多个自包含纳米晶体区705。可用si、la、y、n、sc、gd或类似者中的一种或多种来掺杂或不掺杂介电层,且可在沉积期间或者退火期间修改纳米晶体区705的晶相(例如四方晶、立方晶、斜方晶、菱面体以及类似者)。基于所使用的掺杂以及工艺控制,可提升高介电常数介电材料的介电常数及/或铁电性质(例如极化矫顽力与极化保持性)。此外,可通过控制工艺以将工艺保持在高介电常数介电材料的准同型相界(morphotropic phase boundary)中来维持这些修改。如此一来,可通过简易纳米晶体薄膜411以及化合物纳米晶体薄膜611来完全阻止及/或将漏电路径以及氧化剂路径最小化。因此,在制造半导体装置100时可将缺陷最小化及/或避免缺陷,提升半导体装置100的产量、效能并增加可靠性。

[0114]

在一实施例中,一种方法包括:沉积介电层于半导体装置的通道区中的鳍片上;对介电层执行第一次退火工艺以形成多个纳米晶体区,多个纳米晶体区悬浮在介电层的非晶体基质层内并被非晶形基质层分隔;以及沉积一金属层于半导体装置中的通道区的介电层上。在一实施例中,形成纳米晶体区的步骤包括以第一掺杂来掺杂介电层。在一实施例中,形成纳米晶体区的步骤还包括维持介电层的结晶区域比例大于或等于10体积百分比,且小于或等于80体积百分比。在一实施例中,形成纳米晶体区的步骤包括修改纳米晶体区的晶相。在一实施例中,此方法还包括形成一盖层于介电层上。在一实施例中,形成盖层之后执行对电介质层的退火工艺。在一实施例中,此方法还包括对介电层执行第二次退火工艺,其中在形成盖层之前对介电层执行第一次退火工艺,以及其中在形成盖层之后对介电层执行第二次退火工艺。

[0115]

在一实施例中,一种方法包括:形成半导体装置中的鳍式场效晶体管中的栅极介电层,此栅极电介质层包括介电材料;在栅极介电层的介电材料中形成多个自包含晶体区,其中多个自包含晶体区包括多个晶形/非晶形界面以及其中多个自包含晶体区通过栅极介电层的非晶形基质层的介电材料来彼此分离;以及在半导体装置的鳍式场效晶体管的栅极介电层上沉积金属栅极结构。在一实施例中,此方法还包括在介电材料中注入第一掺杂材料。在一实施例中,此方法还包括执行退火工艺以将经注入第一掺杂材料的介电材料结晶成多个第一自包含晶体区。在一实施例中,第一掺杂材料为钆。在一实施例中,此方法还包括:于介电材料上沉积盖层;以及在沉积盖层之后执行第二退火工艺,此第二退火工艺修改介电材料的晶体结构。在一实施例中,介电材料为氧化铪。在一实施例中,自包含晶体区具

有第一组成,且非晶形基质层具有与第一组成不同的第二组成。在一实施例中,栅极介电层具有不大于2.5nm的厚度。在一实施例中,此方法还包括:执行一退火工艺以使介电材料结晶;以及于介电材料上沉积盖层,其中在沉积盖层之前执行退火工艺。

[0116]

在一实施例中,一种半导体装置包括:场效晶体管的鳍片;沉积于鳍片上的栅极介电层,此栅极介电层包括多个自包含纳米晶体区,此纳米晶体区包含多个晶形/非晶形界面,其中自包含晶体区通过栅极介电层的非晶形基质介电材料来彼此分离;以及金属栅极电极,沉积于栅极介电层上。在一实施例中,栅极介电层的厚度小于2.5nm。在一实施例中,此半导体装置还包括在自包含晶体区中的多个掺杂。在一实施例中,栅极介电层的结晶区域比例大于或等于10体积百分比,且小于或等于80体积百分比。

[0117]

以上概述数个实施例的部件,以便在本公开所属技术领域中技术人员可更易理解本公开的观点。在本公开所属技术领域中技术人员应理解,他们能以本公开为基础,设计或修改其他工艺和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本公开所属技术领域中技术人员也应理解到,此类等效的工艺和结构并无悖离本公开的精神与范围,且他们能在不违背本公开的精神和范围之下,做各式各样的改变、取代和替换。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1