高电子迁移率晶体管的制作方法

1.本发明涉及半导体装置技术领域,具体涉及一种高电子迁移率晶体管。

背景技术:

2.在半导体技术中,iii-v族的半导体化合物可用于形成各种集成电路装置,例如:高功率场效应晶体管、高频晶体管或高电子迁移率晶体管(high electron mobility transistor,hemt)。hemt属于具有二维电子气(two dimensional electron gas,2-deg)的一种晶体管,其2-deg会邻近于能隙不同的两种材料之间的接合面(亦即,异质接合面)。由于hemt并非使用掺杂区域作为晶体管的载子通道,而是使用2-deg作为晶体管的载子通道,因此相较于公知的金氧半场效晶体管(mosfet),hemt具有多种吸引人的特性,例如:高电子迁移率及以高频率传输信号的能力。

3.为了使得hemt在导通状态(on-state)和截止状态(off-state)间被切换,通常会对hemt的栅极施予正电压或负电压。然而,对于现有的hemt而言,由于栅极延迟效应(gate-lag),导致阈值电压(threshold voltage,vt)通常会随着栅极电压的数值大小而有所变动。举例而言,在导通状态和截止状态所对应的阈值电压偏离度(δvt)通常会有所不同,此不利于hemt的快速切换,因而影响了半导体装置的效能。

技术实现要素:

4.有鉴于此,有必要提出一种改良的高电子迁移率晶体管,以改善现有的高电子迁移率晶体管所存在的缺陷。

5.根据本发明的一实施例,提供一种高电子迁移率晶体管,包括:一通道层,设置于一基底上;一阻障层,设置于所述通道层上;一第一化合物半导体层,设置于所述阻障层上;以及,一第二化合物半导体层,设置于所述阻障层和所述第一化合物半导体层之间,其中所述第一化合物半导体层与所述第二化合物半导体层包括一金属掺质的一浓度分布,该浓度分布于所述第一化合物半导体层具有一第一波峰,且该浓度分布于所述第二化合物半导体层具有一第二波峰。

6.根据本发明的实施例,由于第二化合物半导体层设置于第一化合物半导体层和阻障层之间,藉由在第二化合物半导体层中形成金属掺质的浓度波峰,可以增加第二化合物半导体层的最高价带和阻障层的最高价带(maximum ev)之间的能障。因此,来自于第一化合物半导体层的空穴便不易被注入至阻障层,因而避免在阻障层中产生捕捉电荷(trapped charge),进而降低了高电子迁移率晶体管的阈值电压偏离度,并避免了栅极延迟效应。

附图说明

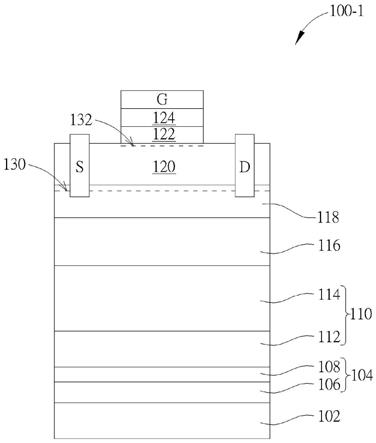

7.图1是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中该半导体堆栈层至少包括第二化合物半导体层;

8.图2是本发明半导体堆栈层中的掺质浓度和深度间的关系图;

9.图3是本发明实施例1、2和比较例1的阈值电压偏离值和栅极电压间的关系图;

10.图4是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中该半导体堆栈层至少包括硅盖层;

11.图5是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中该半导体堆栈层至少包括第二化合物半导体层和p型三五族盖层;

12.图6是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中该半导体堆栈层至少包括第二化合物半导体层和p型三五族阻障层;

13.图7是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中该半导体堆栈层至少包括第二化合物半导体层、p型三五族阻障层和p型三五族盖层。

14.附图标记说明:100-1、100-2、100-3、100-4、100-5 高电子迁移率晶体管102 基底104 氮化物层106 第一氮化物层108 第二氮化物层110 超晶格层112 第一超晶格层114 第二超晶格层116 高电阻层118 三五族通道层120 三五族阻障层122 第二化合物半导体层124 第一化合物半导体层126 结晶硅化合物半导体层128 p型三五族化合物半导体层130 二维电子气区域132 二维空穴气区域134 p型三五族阻障层210、212、220、222 曲线δv1 第一阈值电压偏离度δv2 第二阈值电压偏离度v

g1 第一栅极电压v

g2 第二栅极电压d 漏极g 栅极s 源极p 浓度波峰

具体实施方式

15.下面结合附图和具体的实施方式对本发明作进一步说明。

16.本发明提供了数个不同的实施例,可用于实现本发明的不同特征。为简化说明起见,本发明也同时描述了特定构件与布置的实施例。提供这些实施例的目的仅在于示意,而非予以任何限制。举例而言,下文中针对「第一特征形成在第二特征上或上方」的叙述,其可以是指「第一特征与第二特征直接接触」,也可以是指「第一特征与第二特征间另存在有其他特征」,致使第一特征与第二特征并不直接接触。

17.另外,针对本发明中所提及的空间相关的叙述词汇,例如:「在...之下」、「低」、「下」、「上方」、「之上」、「下」、「顶」、「底」等类似词汇,为便于叙述,其用法均在于描述附图中一个元件或特征与另一个(或多个)元件或特征的相对关系。除了附图中所显示的摆向外,这些空间相关词汇也用来描述半导体装置在使用中以及操作时的可能摆向。随着半导体装置的摆向的不同(旋转90度或其它方位),用以描述其摆向的空间相关叙述亦应通过类似的方式予以解释。

18.虽然本发明使用第一、第二、第三等用词,以叙述种种元件、部件、区域、层及/或区块(section),但应了解此等元件、部件、区域、层及/或区块不应被此等用词所限制。此等用词仅是用以区分某一元件、部件、区域、层及/或区块与另一个元件、部件、区域、层及/或区块,其本身并不代表该元件有任何之前的序数,也不代表某一元件与另一元件的排列顺序或是制造方法上的顺序。因此,在不背离本发明具体实施例的范畴下,下列所讨论的第一元件、部件、区域、层或区块亦可以第二元件、部件、区域、层、或区块之词称之。

19.本发明中所提及的「约」或「实质上」等类似用语通常表示在一给定值或范围的20%之内,较佳是10%之内,且更佳是5%之内,或3%之内,或2%之内,或1%之内,或0.5%之内。应注意的是,说明书中所提供的数量为大约的数量,亦即在没有特定说明「约」或「实质上」的情况下,仍可隐含「约」或「实质上」之含义。

20.在本发明中,「三五族半导体(group iii-v semiconductor)」系指包含至少一iii族元素与至少一v族元素的化合物半导体。其中,iii族元素可以是硼(b)、铝(al)、镓(ga)或铟(in),而v族元素可以是氮(n)、磷(p)、砷(as)或锑(sb)。进一步而言,「三五族半导体」可以包括:氮化镓(gan)、磷化铟(inp)、砷化铝(alas)、砷化镓(gaas)、氮化铝镓(algan)、氮化铟铝镓(inalgan)、氮化铟镓(ingan)、氮化铝(aln)、磷化镓铟(gainp)、砷化铝镓(algaas)、砷化铝铟(inalas)、砷化镓铟(ingaas)、氮化铝(aln)、磷化镓铟(gainp)、砷化铝镓(algaas)、砷化铝铟(inalas)、砷化镓铟(ingaas)、其类似物或上述化合物的组合,但不限于此。此外,端视需求,三五族半导体内亦可包括掺质,而为具有特定导电型的三五族半导体,例如n型或p型iii-v族半导体。

21.本发明系关于一种高压半导体装置或高电子迁移率晶体管(hemt),例如是可以作为电压转换器应用的功率切换晶体管或电信高功率应用,本发明并不以此为限。相较于硅功率晶体管,由于iii-v hemt具有较宽的能带间隙,因此具有低导通电阻(on-state resistance,r

on

)与低切换损失的特征。

22.图1是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中半导体堆栈层至少包括p型三五族中间层。如图1所示,高电子迁移率晶体管100-1,包括基底102、半导体堆栈层(例如至少包括三五族通道层118、三五族阻障层120、p型三五

族中间层122、第一化合物半导体层124)、源极s、漏极d以及栅极g。基底102和半导体堆栈层间可以选择性地另设置其他层,例如氮化物层104、超晶格层110及高电阻层116。

23.根据本发明的一实施例,基底102可以是如碳化硅(sic)、氧化铝(al2o3)、蓝宝石(sapphire)氮化铝等陶瓷基底。于一实施例中,基底102表面可设置接合层,其中接合层材料例如包括硅。根据本发明一实施例中,基底102更包含一核心层以及包覆住核心层的单一或多层的绝缘材料层以及/或其他合适的材料层,核心层可以是氮化铝或氧化铝,绝缘材料层可以是氧化物、氮化物、氮氧化物或其他合适的绝缘材料。

24.氮化物层104可以选择性地被设置于基底102上,其具有较少的晶格缺陷,因此可以增进设置于氮化物层104上的半导体堆栈层的磊晶质量。其中,氮化物层104可以包括一氮化物堆栈层,例如包括第一氮化物层106及第二氮化物层108。根据本发明一实施例,第一氮化物层106可例如是低温氮化铝层(lt-aln),此低温氮化铝层可以经由有机金属化学气相沉积(metal-organic cvd,mocvd),在800℃-1100℃的环境温度下而形成;第二氮化物层108可例如是高温氮化铝层(ht-aln),此高温氮化铝层可以经由有机金属化学气相沉积,在1100℃-1400℃的环境温度下而形成,但不限定于此。

25.超晶格层(superlattice layer,sl)110可以选择性地被设置于基底102上,例如被设置于氮化物层104上。超晶格层110可用以降低基底102和设置于超晶格层110上的半导体层之间的晶格不匹配(lattice mismatch)的程度,以及降低晶格不匹配所产生之应力。根据本发明一实施例,超晶格层110可以是一超晶格堆栈层,例如包括第一超晶格层112及第二超晶格层114。根据不同需求,第一超晶格层112或第二超晶格层114可以各自是由至少两种iii-v(三五族)化合物半导体所构成的周期性交替层结构,例如由aln薄层/gan薄层交替堆栈而成的结构,或是各自是组成比例渐变的iii-v化合物半导体,例如是铝组成比例由下至上渐减的氮化铝镓(al

x

ga

1-x

n,0.15≦x≦0.9),但不限定于此。

26.高电阻层116可以选择性地被设置于基底102上,例如是被设置于超晶格层110上。高电阻层116相较于其他的层具有较高的电阻率,因此可避免设置于高电阻层116上的半导体层和基底102间产生漏电流。根据本发明一实施例,高电阻层116可以是具有掺质的iii-v半导体层,例如碳掺杂氮化镓(c-gan),但不限定于此。

27.通道层(即以下内文所述三五族通道层)118可以被设置于基底102上,例如是被设置于高电阻层116上。三五族通道层118可包含一层或多层iii-v族半导体层,且iii-v族半导体层的成份可以是gan、algan、ingan或inalgan,但不限定于此。根据本发明的一实施例,三五族通道层118为未掺杂的iii-v族半导体,例如是未掺杂的gan(undoped-gan,u-gan)。根据本发明的其他实施例,三五族通道层118亦可以是被掺杂的一层或多层iii-v族半导体层,例如是p型的iii-v族半导体层。对p型的iii-v族半导体层而言,其掺质可以是cd、fe、mg或zn,但不限定于此。

28.阻障层(即以下内文所述三五族阻障层)120可被设置于三五族通道层118上。三五族阻障层120可包含一层或多层iii-v族半导体层,且其组成会不同于iii-v族主体层104的iii-v族半导体。举例来说,三五族阻障层120可包含aln、alyga

(1-y)

n(0<y<1)或其组合。根据一实施例,三五族阻障层120可以是n型iii-v族半导体,例如是本质上为n型的algan层,但不限定于此。

29.由于三五族通道层118和三五族阻障层120间具有不连续的能隙,藉由将iii-v族

通道层118和iii-v族阻障层120互相堆栈设置,电子会因压电效应(piezoelectric effect)而聚集于iii-v族通道层118中,且邻近于三五族通道层118和三五族阻障层120间的异质接面。此聚集的电子可构成具有高载子迁移率的薄层,亦即二维电子气(2-deg)区域130。

30.第一化合物半导体层124可被设置于三五族阻障层120上,以耗尽二维电子气(2-deg)区域130,达成半导体装置的常关(normally-off)状态。第一化合物半导体层124可以是p型iii-v族半导体,例如是p型的gan层,但不限定于此。此外,第一化合物半导体层124的能隙可小于三五族阻障层120的能隙,使得第一化合物半导体层124和三五族阻障层120间可具有不连续的能隙。

31.p型三五族中间层122可以被设置于三五族阻障层120和第一化合物半导体层124之间,且p型三五族中间层122的厚度同时薄于三五族阻障层120的厚度与第一化合物半导体层124的厚度。举例来说,p型三五族中间层122的厚度可以是20nm,而三五族阻障层120和第一化合物半导体层124的厚度可以分别是50nm和35nm,但不限定于此。根据本发明的一实施例,p型三五族中间层122是p型iii-v族半导体,例如是p型的gan层,且掺质可以是选自mg、cd或zn的金属掺质。根据本发明的一实施例,p型三五族中间层122的掺质波峰浓度范围为9e18cm-3

至2e19cm-3

,且低于第一化合物半导体层124的掺质波峰浓度范围(例如1e19cm-3

至1e20cm-3

)。

32.由于p型三五族中间层122和三五族阻障层120间具有不连续的能隙,藉由将p型三五族中间层122和iii-v族阻障层120互相堆栈设置,空穴会因压电效应而聚集于p型三五族中间层122中,且邻近于p型三五族中间层122和三五族阻障层120间的异质接面。此聚集的空穴可构成具有高载子迁移率的薄层,亦即二维空穴气(two dimensional hole gas,2-dhg)区域132。

33.源极s和漏极d可以分别电连接至三五族通道层118,而栅极g可以电连接至第一化合物半导体层124。其中,源极s和漏极d可以和三五族通道层118构成欧姆接触,而栅极g可以和第一化合物半导体层124构成肖特基接触,但不限定于此。

34.为了分析半导体堆栈层之中的浓度分布,可藉由二次离子质谱仪(secondary ion mass spectroscopy,sims)以分析图1所示的半导体堆栈层的金属成分浓度和深度间的关系,量测的结果显示于图2。图2是根据本发明一实施例半导体堆栈层中的掺质浓度和深度间的关系图。如图2所示,曲线210和曲线212分别是本发明一实施例的半导体堆栈层中的mg、al对应于不同深度的浓度分布,曲线220和曲线222分别是比较例1半导体堆栈层(不具有第二化合物半导体层122)中的mg、al对应于不同深度的浓度分布。其中,图2中深度0-70nm大致对应图1的第一化合物半导体层124、深度70-85nm大致对应图1的第二化合物半导体层122、深度85-120nm大致对应图1的三五族阻障层120、深度120-140nm大致对应图1的三五族通道层118。就曲线210而言,在深度70-85nm区间内(即对应第二化合物半导体层)具有浓度波峰p,此浓度波峰p的半高宽(full width halfmaximum,fwhm)大致为5nm至15nm,且最高浓度(或称波峰浓度)大致约为至1.5e19 cm-3

;而在深度0-70nm区间内(即对应第一化合物半导体层)的最高浓度大致为5e19 cm-3

(对应深度2-5nm区间),且最低浓度大致7e18 cm-3

(对应深度70nm)。相较之下,曲线220的mg浓度在深度40-100nm区间并不存在任何浓度波峰。需注意的是,图2所示的金属掺质的浓度分布较佳地采用二次离子质谱仪或分辨率更

高的侦测装置进行测量。若以分辨率较差的侦测装置进行测量,则可能无法量测到第二化合物半导体层的浓度波峰。

35.为了判别高电子迁移率晶体管中第二化合物半导体层对于栅极延迟效应的影响,可以进一步分析在不同栅极电压(gate stress voltage)下的阈值电压偏离度,量测的结果显示于图3。图3绘示了本发明实施例1、2和比较例1、2的阈值电压偏离值和栅极电压间的关系图。请同时参照图1、图3及图4。其中,图3中实施例1的结构类似图1所示的结构;图3中实施例2的结构类似图4所示的结构,图4所示的结构和图1的主要差异在于半导体堆栈层中不包括第二化合物半导体层122,但包括设置于第一化合物半导体层124上的结晶硅化合物半导体层126;图3中比较例1的结构则是半导体堆栈层中不包括任何第二化合物半导体层122。

36.如图3所示,当栅极电压分别为第一栅极电压v

g1

和第二栅极电压v

g2

时,例如分别对应至-6v和6v时,高电子迁移率晶体管可以分别对应至截止状态和导通状态。对于实施例1而言,当栅极电压分别为第一栅极电压v

g1

和第二栅极电压v

g2

时,其对应的阈值电压偏离值大致相等,而位于第一阈值电压偏离值δv1和第二阈值电压偏离值δv2之间,表示实施例1的高电子迁移率晶体管不具有明显的栅极延迟效应。对于实施例2而言,当栅极电压为第二栅极电压v

g2

时,其对应的阈值电压偏离值会略低于第一阈值电压偏离值δv1,而非位于第一阈值电压偏离值δv1和第二阈值电压偏离值δv2之间,表示实施例2的高电子迁移率晶体管在导通状态时具有栅极延迟效应。相较之下,对于比较例1而言,当栅极电压为第一栅极电压v

g1

时,其对应的阈值电压偏离值远大于第一阈值电压偏离值δv1。因此比较例1的栅极延迟效应较实施例1、2的栅极延迟效应显著。

37.本技术领域中具有通常知识者应可轻易了解,为能满足实际产品需求的前提下,本发明的高电子迁移率晶体管亦可能有其它态样,而不限于前述。下文将进一步针对高电子迁移率晶体管的其他实施例或变化型进行说明。且为简化说明,以下说明主要针对各实施例不同之处进行详述,而不再对相同之处作重复赘述。此外,本发明中的各种实施例可能使用重复的参考符号和/或标记。使用这些重复的参考符号与标记是为了使叙述更简洁和明确,而非用以指示不同的实施例及/或配置之间的关联性。

38.图4是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中半导体堆栈层至少包括硅化合物半导体层。如图4所示,图4所示的结构100-2类似图1所示的结构100-1,主要差异在于图4的三五族阻障层120和第一化合物半导体层124间不包括第二化合物半导体层122,但化合物半导体层被设置于第一化合物半导体层124上。根据本发明一实施例,化合物半导体层可以是结晶硅化合物半导体层126。由于结晶硅化合物半导体层126和第一化合物半导体层124间的能隙不连续,因此可以让空穴更容易自栅极传递至第一化合物半导体层124。

39.图5是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中半导体堆栈层至少包括第二化合物半导体层和p型三五族盖层。如图5所示,图5所示的结构100-3类似图1所示的结构100-1,主要差异在于图5的三五族阻障层120和第一化合物半导体层124间除了包括第二化合物半导体层122之外,还包括设置于第一化合物半导体层124上的p型iii-v族化合物半导体层128。根据本发明一实施例,p型三五族化合物半导体层128可以是高掺质浓度的p

+

型gan,其可用于促进空穴的注入。其中,p型三五族化合物

半导体层128和第一化合物半导体层124可包括相同的金属掺质,例如mg,且p型三五族化合物半导体层128的掺杂浓度高于第一化合物半导体层124的掺杂浓度。

40.图6是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中半导体堆栈层至少包括第二化合物半导体层和p型三五族阻障层。如图6所示,图6所示的结构100-4类似图1所示的结构100-1,主要差异在于图6的iii-v族阻障层120和第一化合物半导体层124间除了包括第二化合物半导体层122之外,还包括设置于三五族阻障层120和第二化合物半导体层122之间的p型三五族阻障层134。根据本发明一实施例,p型三五族阻障层134可以是低掺质浓度的p-型algan,其可以用于增加阈值电压(vth),降低电子被iii-v族阻障层120捕捉的程度。其中,p型三五族阻障层134和第二化合物半导体层122可包括相同的金属掺质,例如mg,且p型iii-v族阻障层134的掺杂浓度低于第二化合物半导体层122的掺杂浓度。

41.图7是根据本发明一实施例所绘示的高压半导体装置的半导体堆栈层的剖面示意图,其中半导体堆栈层至少包括第二化合物半导体层、p型三五族阻障层、和p型三五族盖层。如图7所示,图7所示的结构100-5类似图1所示的结构100-1,主要差异在于图7的三五族阻障层120和第一化合物半导体层124间除了包括p型三五族中间层122之外,还包括设置于第一化合物半导体层124上的p型三五族化合物半导体层128,以及包括设置于三五族阻障层120和第二化合物半导体层122之间的p型三五族阻障层134。

42.根据上述实施例,由于第二化合物半导体层会被设置于第一化合物半导体层和三五族阻障层之间,藉由在第二化合物半导体层中形成金属掺质的浓度波峰,可以增加第二化合物半导体层的最高价带和阻障层的最高价带之间的能障。因此,来自于第一化合物半导体层的空穴便不容易被注入至阻障层,因而避免在三五族阻障层中产生捕捉电荷(trapped charge),进而降低了高电子迁移率晶体管的阈值电压偏离度。因此,可避免栅极延迟效应,而有利于高电子迁移率晶体管的快速切换。

43.以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的技术人员来说,在不脱离本发明构思的前提下,还可以做出若干等同替代或明显变型,而且性能或用途相同,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1