用于减少继电器作动的延迟电路与方法与流程

on pulse)的一起始时间延后一特定时间,且该特定时间大于该电源转换装置的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。如此方式,当该电子装置操作在休眠模式时,继电器的作动便会被大幅减少或停止,从而使电子装置内的电源转换装置不会产生噪音,也同时延长了继电器的使用寿命。

7.为达成上述目的,本发明提出所述用于减少继电器作动的延迟电路的一实施例,其应用于具有一继电器的一电源转换装置之中,且包括:

8.一第一二极管,以其一阳极端耦接于向该继电器传送的一电源信号;

9.一第二二极管,以其一阴极端耦接该第一二极管的一阴极端;

10.一双极结型晶体管,以其一集极端与一射极端分别耦接该第二二极管的一阳极端和一参考地端;以及

11.一延迟单元,耦接于该双极结型晶体管的一基极端、该参考地端和该第一二极管的该阴极端与该第二二极管的该阳极端之间的一第一共接点;

12.其中,该第一共接点耦接至该继电器内的一线圈的一端,且该线圈的另一端耦接至该双极结型晶体管的该集极端与该第二二极管的该阳极端之间的一第二共接点;

13.当具有该电源转换装置的一电子装置操作在一休眠模式,该延迟单元将该电源信号所包含的一切换导通脉冲(switch-on pulse)的一起始时间延后一特定时间,且该特定时间大于该电源转换装置的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。

14.并且,为达成上述目的,本发明同时提出所述用于减少继电器作动的延迟方法的一实施例,其前述的延迟电路实现于具有一继电器的一电源转换装置之中,且包括以下步骤:

15.(1)接收向该继电器传送的一电源信号;

16.(2)在具有该电源转换装置的一电子装置操作在一休眠模式的情况下,将该电源信号所包含的一切换导通脉冲(switch-on pulse)的一起始时间延后一特定时间;

17.其中,该特定时间大于该电源转换装置的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。

18.在一实施例中,该开机脉冲(power-on pulse)的该脉冲宽度为1秒,且该特定时间大于或等于1秒。

19.在一实施例中,该双极结型晶体管为一npn型双极结型晶体管。

20.在一实施例中,该延迟单元包括一微控制器,其耦接于该双极结型晶体管的该基极端、该参考地端和该第一共接点之间。

21.在另一实施例中,该延迟单元包括:

22.一第三二极管,为一齐纳二极管,且以其一阳极端耦接该双极结型晶体管的该基极端;

23.一延时电阻,以其一第一端耦接该第三二极管的一阴极端,且以其一第二端耦接该第一共接点;

24.一第四二极管,以其一阳极端耦接该第一电阻的该第一端与该第三二极管的该阴极端之间的一第三共接点,且以其一阴极端耦接该第一电阻的该第二端;以及

25.一延时电容,耦接于该第三共接点与该参考地端之间;

26.其中,该延时电阻的一电阻值和该延时电容的一电容值组成一时间常数,且该时间常数大于该开机脉冲(power-on pulse)的该脉冲宽度。

附图说明

27.图1为现有的一种电源供应装置的简易方块图;

28.图2为电源开关信号以及电源信号(vcco)的工作时序图;

29.图3为本发明的一种用于减少继电器作动的延迟电路的电路架构图;

30.图4为电源开关信号、延迟处理前的电源信号(vcco)、以及延迟处理后的电源信号(vcco)的工作时序图;

31.图5为本发明的一种用于减少继电器作动的延迟电路的电路架构图;以及

32.图6为本发明的一种用于减少继电器作动的延迟方法的流程图。图中主要符号说明:

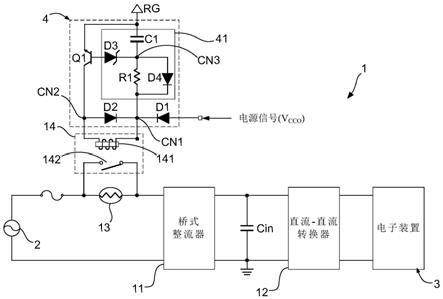

33.1:电源供应装置

34.11:桥式整流器

35.12:直流-直流转换器

36.13:热敏电阻

37.14:继电器

38.141:线圈

39.142:单刀双掷开关

40.cin:滤波电容

41.2:交流电源

42.3:电子装置

43.4:延迟电路

44.d1:第一二极管

45.d2:第二二极管

46.d3:第三二极管

47.d4:第四二极管

48.q1:双极结型晶体管

49.c1:延时电容

50.r1:延时电阻

51.41:延迟单元

52.rg:参考地端

53.cn1:第一共接点

54.cn2:第二共接点

55.cn3:第三共接点

56.s1-s2:步骤

[0057]1’

:电源供应装置

[0058]

11’:桥式整流器

[0059]

12’:直流-直流转换器

[0060]

13’:热敏电阻

[0061]

14’:继电器单元

[0062]

cin’:滤波电容

[0063]2’

:交流电源

[0064]3’

:电子装置

具体实施方式

[0065]

为了能够更清楚地描述本发明所提出的一种用于减少继电器作动的延迟电路与方法,以下将配合图式,详尽说明本发明的较佳实施例。

[0066]

第一实施例

[0067]

图3显示本发明的一种用于减少继电器作动的延迟电路的电路架构图。如图3所示,本发明提出一种用于减少继电器作动的延迟电路4(下文简称“延迟电路4”),其应用于一电源转换装置1之中。其中,该电源转换装置1用以向一电子装置3提供所需电源,且包括用以吸收涌浪电流的一热敏电阻13、一继电器14、一桥式整流器11、一输入滤波电容cin、以及一直流-直流转换器12。如图3所示,本发明的延迟电路4主要包括:一第一二极管d1、一第二二极管d2、一双极结型晶体管(bipolar junction transistor,bjt)q1、以及一延迟单元41。

[0068]

更详细地说明,该第一二极管d1以其一阳极端耦接于向该继电器14传送的一电源信号(vcco),且该第二二极管d2以其一阴极端耦接该第一二极管d1的一阴极端。另一方面,该双极结型晶体管q1以其一集极端与一射极端分别耦接该第二二极管d2的一阳极端和一参考地端rg,且该延迟单元41耦接于该双极结型晶体管q1的一基极端、该参考地端rg和该第一二极管d1的阴极端与该第二二极管d2的阳极端之间的一第一共接点cn1。值得注意的是,该第一共接点cn1耦接至该继电器14内的一线圈141的一端,且该线圈141的另一端耦接至该双极结型晶体管q1的该集极端与该第二二极管d2的该阳极端之间的一第二共接点cn2。

[0069]

如此设置,在该电子装置3操作在一休眠模式的情况下,该延迟单元41会对向该继电器14的该线圈141传送的电源信号(vcco)执行一延迟处理。更详细地说明,是将该电源信号(vcco)所包含的一切换导通脉冲(switch-on pulse)的一起始时间延后一特定时间,且该特定时间大于该电源转换装置1的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。图4显示电源开关信号、延迟处理前的电源信号(vcco)、以及延迟处理后的电源信号(vcco)的工作时序图。如图4所示,未进行延迟处理前,该电源信号(vcco)的切换导通脉冲(switch-on pulse)的起始时间几乎等于该电源开关信号的开机脉冲(power-on pulse)的起始时间,且所述切换导通脉冲与所述开机脉冲的脉冲宽度皆为1秒。然而,在将该电源信号(vcco)的切换导通脉冲(switch-on pulse)的起始时间延时大于或等于1秒之后,在其导通脉冲的上升缘尚未出现之前,该电源开关信号已经结束其开机脉冲的工作时序且进入关机时序。

[0070]

故而,如图4所示,在该电子装置3操作在休眠模式时,该电源信号(vcco)经由本发明的延迟电路4的延迟处理之后,其已不包含导通脉冲(switch-on pulse)。因此,将延迟处理后的电源信号(vcco)送入该继电器14内的线圈141之后,该线圈141不会衍生足够的磁力

以吸和该单刀双掷开关142。换句话说,当该电子装置3操作在休眠模式时,继电器14的作动便会被停止,从而使电子装置3内的电源转换装置1不会产生噪音,也同时延长了继电器14的使用寿命。

[0071]

在一实施例中,该双极结型晶体管q1为一npn型双极结型晶体管,且该延迟单元41为一模拟电路,其包括:一第三二极管d3、一延时电阻r1、一第四二极管d4、以及一延时电容c1。如图3所示,该第三二极管d3为一齐纳二极管,且以其一阳极端耦接该双极结型晶体管q1的该基极端。并且,该延时电阻r1以其一第一端耦接该第三二极管d3的一阴极端,且以其一第二端耦接该第一共接点cn1。另一方面,该第四二极管d4以其一阳极端耦接该第一电阻r1的该第一端与该第三二极管d3的该阴极端之间的一第三共接点cn3,且以其一阴极端耦接该延迟电阻r1的该第二端。再者,该延时电容c1耦接于该第三共接点cn3与该参考地端rg之间。依据本发明的设计,该延时电阻r1的一电阻值和该延时电容c1的一电容值组成一时间常数,且该时间常数大于该开机脉冲(power-on pulse)的该脉冲宽度。举例而言,延时电阻r1的电阻值为100kω,且延时电容c1的电容值为10μf,则时间常数为100

×

103

×

10

×

10-6=1秒。

[0072]

第二实施例

[0073]

图5显示本发明的一种用于减少继电器作动的延迟电路的电路架构图。如图5所示,在第二实施例中,本发明的延迟电路4同样包括:一第一二极管d1、一第二二极管d2、一双极结型晶体管q1、以及一延迟单元41。然而,与前述第一实施例不同的是,第二实施例所使用的延迟单元41为一微控制器,其耦接于该双极结型晶体管q1的基极端、该参考地端rg和该第一共接点cn1之间。应可理解,只要在该微控制器之中写入所述特定时间(即,延迟时间),该微控制器会对向该继电器14的该线圈141传送的电源信号(vcco)执行一延迟处理。更详细地说明,是将该电源信号(vcco)所包含的一切换导通脉冲(switch-on pulse)的一起始时间延后一特定时间,且该特定时间大于该电源转换装置1的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。

[0074]

故而,如图4所示,在该电子装置3操作在休眠模式时,该电源信号(vcco)经由本发明的延迟电路4的延迟处理之后,其已不包含导通脉冲(switch-on pulse)。因此,将延迟处理后的电源信号(vcco)送入该继电器14内的线圈141之后,该线圈141不会衍生足够的磁力以吸和该单刀双掷开关142。换句话说,当该电子装置3操作在休眠模式时,继电器14的作动便会被停止,从而使电子装置3内的电源转换装置1不会产生噪音,也同时延长了继电器14的使用寿命。

[0075]

本发明同时提出一种用于减少继电器作动的延迟方法。图6即显示本发明的一种用于减少继电器作动的延迟方法的流程图。如图6所示,本发明的用于减少继电器作动的延迟方法由一延迟电路4(如图3或图5所示)实现于具有一继电器14的一电源转换装置1之中,且包括以下步骤:

[0076]

步骤s1:接收向该继电器14传送的一电源信号(vcco);以及

[0077]

步骤s2:在具有该电源转换装置1的一电子装置3操作在一休眠模式的情况下,将该电源信号(vcco)所包含的一切换导通脉冲(switch-on pulse)的一起始时间延后一特定时间。其中,该特定时间大于或等于该电源转换装置1的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。

[0078]

如此,上述已完整且清楚地说明本发明所提出的一种用于减少继电器作动的延迟电路与方法。并且,经由上述,可以得知本发明具有下列的优点:

[0079]

(1)本发明提供一种用于减少继电器作动的延迟电路与方法,其中该延迟电路4应用于具有一继电器14的一电源转换装置1之中,且包括:一第一二极管d1、一第二二极管d2、一双极结型晶体管q1、以及一延迟单元4。依据本发明的设计,在具有该电源转换装置1的一电子装置3操作在一休眠模式的情况下,该延迟单元4会将向该继电器14传送的一电源信号(vcco)执行一延时处理。更详细地说明,是将该电源信号所包含的一切换导通脉冲(switch-on pulse)的一起始时间延后一特定时间,且该特定时间大于该电源转换装置1的一电源开关信号所包含的一开机脉冲(power-on pulse)的一脉冲宽度。如此方式,当该电子装置3操作在休眠模式时,继电器14的作动便会被大幅减少或停止,从而使电子装置3内的电源转换装置1不会产生噪音,也同时延长了继电器14的使用寿命。

[0080]

如此,上述已完整且清楚地说明本发明所提供的一种用于减少继电器作动的延迟电路与方法的所有实施例。必须加以强调的是,上述的详细说明是针对本发明可行实施例的具体说明,惟该实施例并非用以限制本发明的专利范围,凡未脱离本发明技艺精神所为的等效实施或变更,均应包含于本案的专利范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1