存储器材料及应用其的存储器装置的制作方法

1.本发明是有关于一种存储器材料及应用其的存储器装置。

背景技术:

2.集成电路中,有许多开关元件的应用,例如晶体管与二极管。其中一种开关元件被称为双向阈值开关(ovonic threshold switch,ots)。开关元件以双向材料为基础,其特征在于当进行阈值电压切换(switching threshold voltage)时电阻会大幅度下降,且当电压低于保持电压阈值值(holding threshold)时,将回复高电阻与闭锁状态。开关元件已被使用在,例如各种包含以交叉点架构(cross-point architecture)组织的高密度存储单元阵列的可写入电阻式存储器元件。此外,双向阈值开关的各种其他使用方式,包含所谓的神经拟态运算(neuromorphic computing)已经被提出。

3.特别在具有大量开关元件的集成电路中,开关元件的一个重要特征是漏电电流。漏电电流是开关元件在次临界状态中的电流流量。此外,所期望的开关元件应具高耐久性。因此,有需要提供具有低漏电电流、高切换速度与高耐久性的开关元件。

技术实现要素:

4.本发明是有关于一种存储器材料及应用其的存储器装置。

5.根据本发明的一方面,提出一种存储器材料,其为碳原子掺杂的硫族化物。硫族化物包含砷(as)原子、硒(se)原子、锗(ge)原子及硅(si)原子。

6.根据本发明的另一方面,提出一种存储器装置,其包括第一存取线、第二存取线及存储器材料。存储器材料电性连接在第一存取线与第二存取线之间。存储器材料为碳原子掺杂的硫族化物。硫族化物包含砷原子、硒原子、锗原子及硅原子。

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

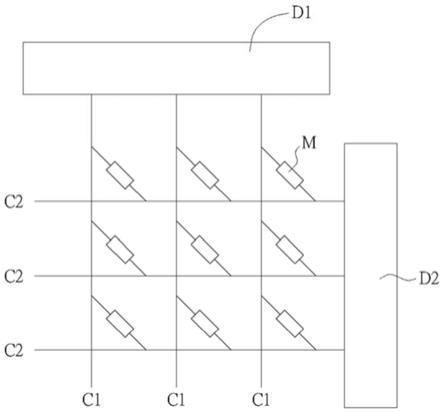

8.图1绘示一实施例的存储器装置的电路示意图。

9.图2绘示一实施例的存储器装置的立体图。

10.图3绘示另一实施例的存储器装置的剖面示意图。

11.图4绘示又另一实施例的存储器装置的剖面示意图。

12.图5绘示又再另一实施例的存储器装置的剖面示意图。

13.【符号说明】

14.102:柱状元件

15.104:第一导线层

16.106:第二导线层

17.410,412,414:绝缘层

18.b21,b22,b23,b31,b32,b33,b41:缓冲层

19.c1:第一存取线

20.c2:第二存取线

21.d1:第一存取线驱动器

22.d2:第二存取线驱动器

23.e11,e12,e21,e22,e31,e32,e33,e34,e41,e42:电极层

24.k:存储元件

25.m:存储单元

26.s:开关元件

具体实施方式

27.以下是以一些实施例做说明。须注意的是,本揭露并非显示出所有可能的实施例,未于本揭露提出的其他实施方式也可能可以应用。再者,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本揭露权利要求保护范围之用。另外,实施例中的叙述,例如局部结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本揭露欲保护的范围做限缩。实施例的步骤和结构各自细节可在不脱离本揭露的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

28.本揭露中,原子的含量单位「at%」表示原子百分比。所谓的「原子」亦可表示周期表中的「元素」。

29.实施例中,存储器材料为碳(c)原子掺杂的硫族化物。硫族化物包含砷(as)原子、硒(se)原子、锗(ge)原子及硅(si)原子。

30.实施例中,碳原子可占存储器材料的5at%至20at%。借此,实施例的存储器材料可具有较佳的热稳定性,应用至存储器装置(例如双向阈值开关(ovonic threshold switch,ots)选择器)可稳定或提升存储器装置的电性特征,例如具有稳定的阈值电压,或未被选择的存储单元具有较低漏电流(即关闭电流)。当存储器材料的碳原子少于(less than)5at%时,存储器材料的热稳定表现增加并不明显。当存储器材料的碳原子多于(more than)20at%时,存储器装置的电性特征不佳,例如关闭电流高。

31.硫族化物的砷原子占存储器材料的23at%至32at%。硫族化物的硒原子占存储器材料的40at%至46at%。硫族化物的锗原子占存储器材料的8at%至25at%。硫族化物的硅原子占存储器材料的5at%至20at%。一实施例中,硫族化物实质上由砷(as)原子、硒(se)原子、锗(ge)原子及硅(si)原子构成。或者,砷(as)原子、硒(se)原子、锗(ge)原子与硅(si)原子的总含量占硫族化物的100at%。

32.一实施例中,存储器材料实质上由碳原子、砷原子、硒原子、锗原子及硅原子构成。或者,碳原子、砷原子、硒原子、锗原子及硅原子的总含量占存储器材料的100at%。亦即,存储器材料为碳掺杂的砷硒锗硅(c-doped assegesi)。

33.相较于存储器材料使用非以碳掺杂的砷硒锗硅或未掺杂(un-doped assegesi)的砷硒锗硅的比较例,本案实施例中使用碳掺杂的砷硒锗硅(c-doped assegesi)的存储器材料可具有较佳的热稳定性。实验中,是通过对存储器材料从室温进行退火工艺了解其热稳

定性,其中升温速率为每秒1℃。实施例中碳掺杂的砷硒锗硅的膜在退火工艺之前与退火工艺之后颜色几乎没有差异,表示与固态结构相有关的表面粗糙度没有改变,可由此判断碳掺杂的砷硒锗硅的膜在退火工艺之后仍维持在退火工艺之前所具有的非结晶相,即使退火温度高达500℃亦然,因此存储器材料的耐受温度可高于500℃。而比较例的存储器材料的膜在经退火温度为375℃的退火工艺之后,膜颜色即明显不同于退火之前,表示其耐受温度低于375℃。一比较例中,硅掺杂的锗碲(si-doped gete6)其耐受温度低于300℃。具体而言,te在200℃以上时会先结晶化,然后在300℃时发生菱体(rhombohedral)gete结晶化,并发现显著的相分离。

34.请参照图1,其绘示一实施例的存储器装置的电路示意图。存储器装置可包括第一存取线c1、第二存取线c2与存储单元m。第一存取线c1可为位线与字线其中之一。第二存取线c2可为位线与字线其中之另一。存储单元m可配置在第一存取线c1与第二存取线c2的交错处。存储单元m电性连接在第一存取线c1与第二存取线c2之间。实施例中,存储单元m各包括上述含碳原子的存储器材料。第一存取线驱动器d1可响应于译码地址,并耦接至第一存取线c1(例如位线),而控制电路(未绘示)是耦接至第一存取线驱动器d1。第二存取线驱动器d2可响应于译码地址,并耦接至第二存取线c2(例如字线),而控制电路(未绘示)是耦接至第二存取线驱动器d2。

35.第一存取线c1与第二存取线c2可独立包括钨(w)、铝(al)、铜(cu)、氮化钛(tin)、氮化钽(tan)、氮化钨(wn)、掺杂多晶硅、硅化钻(cosi)、硅化钨(wsi)、钛氮化硅(tisin)、氮化铝钛(tialn)、氮化铝钽(taaln)、tin/w/tin或其它材料。

36.请参照图2,其绘示一实施例的存储器装置的立体图。电极层e11可在第一导线层104的上表面上。电极层e11与电极层e12可分别在开关元件s的下表面与上表面上。存储元件k可在电极层e12的上表面上。第二导线层106可在电极层e12的上表面上。一实施例中,存储单元m(图1)可包括电极层e11、开关元件s、电极层e12与存储元件k。电极层e11、开关元件s、电极层e12与存储元件k可具有柱形状。或者,柱状元件102可包括电极层e11、开关元件s、电极层e12与存储元件k。柱状元件102电性连接在第一导线层104与第二导线层106之间。如图1所示的第一存取线c1可包括第一导线层104。如图1所示的第二存取线c2可包括第二导线层106。

37.实施例中,开关元件s为双向阈值开关(ovonic threshold switch,ots)。开关元件s可包括上述含碳原子的存储器材料。

38.存储元件k可包括相变化材料。存储元件k的材料的实施例可包含基于硫族的材料及其它材料。硫族合金包含硫族以及其它材料例如过渡金属的化合物。硫族合金通常包含来自元素周期表iva族的一个或多个原子,例如锗(ge)和锡(sn)。通常,硫族合金包含锑(sb)、镓(ga)、铟(in)、银(ag)的一者或多者的化合物。许多基于相变化存储材料已在技艺文献中被说明,包含的合金有:ga/sb、in/sb、in/se、sb/te、ge/te、ge/sb/te、in/sb/te、ga/se/te、sn/sb/te、in/sb/ge、ag/in/sb/te、ge/sn/sb/te、ge/sb/se/te、及te/ge/sb/s。在ge/sb/te合金家族中,大范围的合金合成物是有作用的。合成物例如可以是ge2sb2te5、gesb2te4、及gesb4te7。更详细来说,过渡金属例如铬(cr)、铁(fe)、镍(ni)、铌(nb)、钯(pd)、铂(pt)及其混合物或合金,可与ge/sb/te或ga/sb/te合成,以形成具可编程电阻特性的相变化合金。存储元件k可包含一层硫族及其它具有添加物的相变化材料,以变更导电

性、转移温度、熔化温度、及其它特性。代表性的添加物可包含氮(n)、硅(si)、氧(o)、氧化硅(siox)、氮化硅(sin)、铜(cu)、银(ag)、金(au)、铝(al)、氧化铝(al2o3)、钽(ta)、氧化钽(taox)、氮化钽(tan)、钛(ti)、和氧化钛(tiox)。

39.电极层e11与电极层e12可独立包括钨(w)、铝(al)、铜(cu)、氮化钛(tin)、氮化钽(tan)、氮化钨(wn)、掺杂多晶硅、硅化钻(cosi)、硅化钨(wsi)、钛氮化硅(tisin)、氮化铝钛(tialn)、氮化铝钽(taaln)、tin/w/tin或其它材料。

40.请参照图3,其绘示另一实施例的存储器装置的剖面示意图。缓冲层b21在电极层e21的上表面上。缓冲层b21与缓冲层b22分别在开关元件s的下表面与上表面上。缓冲层b22与缓冲层b23分别在存储元件k的下表面与上表面上。电极层e22在缓冲层b23的上表面上。

41.一实施例中,存储单元m(图1)可包括电极层e21、缓冲层b21、开关元件s、缓冲层b22、存储元件k、缓冲层b23与电极层e22。存储单元m可具有柱形状。

42.另一实施例中,存储单元m(图1)可包括缓冲层b21、开关元件s、缓冲层b22、存储元件k与缓冲层b23。存储单元m可具有柱形状。第一存取线c1(图1)可包括电极层e21。第二存取线c2(图1)可包括电极层e22。

43.电极层e21与电极层e22可独立包括参照图2所说明电极层e11与电极层e12可使用的导电材料。

44.缓冲层b21、缓冲层b22与缓冲层b23可独立包括金属氮化物,例如氮化钛(tin)、氮化钽(tan)、氮化钨(wn)、氮化钼(mon)、氮化铌(nbn)、氮化钛(tisin)、氮化钛(tialn)、氮化硅锆(zrsin)、氮化硅钨(wsin)、氮化硼钨(wbn)、氮化铝锆(zrain)、氮化硅钼(mosin)、氮化铝钼(moaln)、氮化硅钽(tasin)、钽铝氮化物(taaln)。或者,缓冲层b21、缓冲层b22与缓冲层b23可独立包括掺杂多晶硅、钨(w)、铜(cu)、钛(ti)、钼(mo)、钽(ta)、硅化钛(tisi)、硅化钽(tasi)、钛钨(tiw)、氮氧化钛(tion)、钛铝氧氮化物(tialon)、氮氧化钨(won)、氧氮化钽(taon)、碳(carbon)、硅掺杂的碳(si doped carbon)。或可使用上述材料的组合。

45.请参照图4,其绘示又另一实施例的存储器装置的剖面示意图。

46.电极层e31与电极层e32分别在开关元件s的下表面与上表面上的缓冲层b31与缓冲层b32上。存储元件k在电极层e32的上表面上。电极层e33在存储元件k的上表面上。缓冲层b33在电极层e33的上表面上。电极层e34在缓冲层b33的上表面上。

47.一实施例中,存储单元m(图1)可包括电极层e31、缓冲层b31、开关元件s、缓冲层b32、电极层e32、存储元件k、电极层e33、缓冲层b33与电极层e34。存储单元m可具有柱形状。

48.另一实施例中,存储单元m(图1)可包括缓冲层b31、开关元件s、缓冲层b32、电极层e32、存储元件k、电极层e33与缓冲层b33。第一存取线c1(图1)可包括电极层e31。第二存取线c2(图1)可包括电极层e34。存储单元m可具有柱形状。

49.电极层e31、电极层e32、电极层e33与电极层e34可独立包括参照图2所说明电极层e11与电极层e12可使用的导电材料。缓冲层b31、缓冲层b32与缓冲层b33可独立包括参照图3所说明缓冲层b21、缓冲层b22与缓冲层b23可使用的缓冲材料。

50.请参照图5,其绘示又再另一实施例的存储器装置的剖面示意图。电极层e41与缓冲层b41分别在开关元件s的下表面与上表面上。电极层e42在缓冲层b41的上表面上。电极层e41可在绝缘层410中。开关元件s可在绝缘层410的上表面上。绝缘层412在绝缘层410的上表面上。开关元件s、缓冲层b41与电极层e42可在绝缘层412中。绝缘层414可在电极层e42

与绝缘层412的上表面上。一实施例中,存储单元m(图1)可包括电极层e41、开关元件s、缓冲层b41与电极层e42。

51.电极层e41与电极层e42可独立包括参照图2所说明电极层e11与电极层e12可使用的导电材料。缓冲层b41可包括参照图3所说明缓冲层b21、缓冲层b22与缓冲层b23可使用的缓冲材料。绝缘层410、绝缘层412与绝缘层414可独立包括氧化物例如氧化硅、氮化物例如氮化硅,或其它合适的介电材料。

52.实施例中,开关元件s使用具有热稳定性质的碳掺杂的砷硒锗硅,因此可兼容三维积体(3d integration)的后段工艺(back-end-of-line,beol),适用于三维交叉点(3d cross-point)技术。后段工艺可包含整合cmos工艺使用的高温工艺,例如温度高达400℃。实施例中,使用碳掺杂的砷硒锗硅的开关元件s可具有薄的厚度,例如13nm至45nm,例如可为20nm或更薄,为工艺与整合所期望的尺寸特征。

53.实施例中,开关元件s使用碳掺杂的砷硒锗硅的存储器装置可具有高的耐久性表现(high endurance performance),例如,类似图5所示的存储器装置(其中电极层e41与电极层e42使用w,电极层e42的厚度为约40nm,缓冲层b41使用碳且厚度为约15nm)的开关元件s(其使用碳掺杂的砷硒锗硅,且厚度为约20nm)其设定/重置循环(set/reset cycling)的耐久性约1e10次。此外,实施例中使用碳掺杂的砷硒锗硅的开关元件s可维持具有期望的开关性质。例如,实施例中使用碳掺杂的砷硒锗硅的开关元件s可具有稳定或优异的阈值电压(vth),例如约3.25v。且/或,实施例中使用碳掺杂的砷硒锗硅的开关元件s可具有低的漏电流,例如关闭电流(ioff)约1na/@2v。

54.表1列示实施例与比较例的开关元件s的存储器材料的原子含量(单位为at%),及阈值电压(vth)与关闭电流(ioff)结果。实施例的存储器材料使用碳(c)掺杂的砷硒锗硅。比较例的存储器材料含有氧原子,且未以碳掺杂。由表1可发现,相较于比较例的开关元件s,实施例的开关元件s具有更佳的阈值电压与关闭电流。

55.表1

[0056] assegesicovthioff比较例31.342.314.47.5-4.43.6v190pa@2v实施例24.145.28.56.915.3-3.25v1na@2v

[0057]

其它实验中,是对实施例与比较例的存储器装置进行1e9次的设定/重置循环(set/reset cycling)操作,并测试各存储器装置的所有66个存储单元m了解其是否失效(fail)。判断失效的规范为,当循环操作后的关闭电流为循环操作前的初始关闭电流的5倍时,判断存储单元为失效。实施例中,存储器装置的开关元件s使用碳掺杂的砷硒锗硅,且66个存储单元m皆通过1e9次的设定/重置循环(set/reset cycling)操作,没有失效。比较例中,存储器装置的开关元件使用非碳掺杂的砷硒锗硅或未掺杂的砷硒锗硅,且66个存储单元m的其中一个存储单元m在第1e9次的循环操作之前失效。

[0058]

综上所述,虽然本发明已以实施例揭露如上,然其并非用以限定本发明。本发明所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当以随附权利要求所界定的为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1