一种全碳化硅双面散热模块的封装结构及其封装方法

1.本发明属于功率半导体模块的封装集成技术领域,更具体地,涉及一种全碳化硅双面散热模块的封装结构及其封装方法。

背景技术:

2.电力电子系统的迅速迭代发展对电力电子器件的性能有了更高的要求,传统的si器件性能已经基本达到其物理极限,因此迫切需要发展新型半导体材料器件作为替代品。为了进一步提高其开关特性和导通特性,宽禁带半导体(wbg)逐渐进入人们的视野。在相同的条件下,宽禁带半导体材料器件拥有比传统si器件更高的击穿电压、更高的导通电流、更高的工作温度、更高的开关速度以及更低的开关损耗。

3.然而现有的碳化硅分立器件(to247封装)每个引脚的电感值约4nh,商业大功率碳化硅模块内部的换流回路电感值普遍在15nh以上。较大的寄生电感使得开关器件在开关过程承受较大的电压过冲,并且在暂态过程伴随着电压震荡。除此之外,现有的单个碳化硅芯片通流能力有限,因此在大功率场合一般会采用多芯片并联的方式扩流。然而各个并联芯片的驱动回路寄生电感值存在差异,这将导致在开通/关断过程中流经各个芯片电流分布不均,动态过程不平衡。随着回路电感值的增加,影响愈烈,这大大限制了碳化硅器件/模块在高频场合的应用。

4.此外,热性能是评估模块可靠性的重要指标,随着电力电子系统的发展,电力电子模块所需要处理的功率等级不断攀升,随之带来的是产生大量损耗。对于传统的引线键合模块,由于仅能实现单面冷却,散热功率不足,因此难以胜任大功率场合应用。

技术实现要素:

5.针对相关技术的缺陷,本发明的目的在于提供一种低寄生电感、低热阻且各并联功率器件回路寄生参数相对平衡的新型双面散热封装结构及其封装方法,旨在解决现有的碳化硅功率封装内寄生电感大、并联功率器件间寄生参数不平衡导致动态不均以及传统模块散热能力差的问题。

6.为实现上述目的,本发明的一个方面提供了一种全碳化硅双面散热的封装结构,包括底层dbc基板、碳化硅功率芯片、驱动电阻、垫片、顶层dbc基板、第一散热器和第二散热器;

7.所述碳化硅功率芯片和驱动电阻直接贴装于所述底层dbc基板,所述垫片直接焊接于所述顶层dbc基板;

8.所述碳化硅功率芯片、驱动电阻和垫片均位于所述顶层dbc基板和底层dbc基板之间;

9.所述第一散热器和第二散热器分别装配于所述顶层dbc基板和底层dbc基板的外侧。

10.进一步地,所述封装结构还包括:

11.连接端子;所述连接端子包括主功率输入端子、主功率输出ac端子和驱动回路端子。

12.进一步地,所述主功率输入端子包括两组功率出线端,且所述两组功率出线端关于所述碳化硅功率芯片对称地设置。

13.进一步地,所述两组功率出线端关于所述碳化硅功率芯片对称地设置包括:

14.当所述碳化硅功率芯片为并联的多个芯片时,所述主功率输入端子包括第一功率出线端和第二功率出线端;其中,所述第一功率出线端到每个芯片的距离之和等于所述第二功率出线端到每个芯片的距离之和。

15.进一步地,所述碳化硅功率芯片包括两组碳化硅mosfet芯片构成半桥电路,各组碳化硅mosfet芯片之间相互并联分别构成所述半桥电路的上桥臂和下桥臂;

16.所述驱动电阻包括上桥臂驱动电阻和下桥臂驱动电阻;

17.所述驱动回路端子包括上桥臂源极驱动端子、下桥臂源极驱动端子、上桥臂栅极驱动端子和下桥臂栅极驱动端子;

18.所述上桥臂的碳化硅mosfet芯片的源极通过上桥臂源极键合线引出到底层dbc的相应铜块上,并与所述上桥臂源极驱动端子相连;所述上桥臂的碳化硅mosfet芯片的栅极通过上桥臂栅极键合线连接到底层dbc的相应铜块上,并与所述上桥臂驱动电阻相连;

19.所述下桥臂的碳化硅mosfet芯片的源极通过下桥臂源极键合线引出到底层dbc的相应铜块上,并与所述下桥臂源极驱动端子相连;所述下桥臂的碳化硅mosfet芯片的栅极通过下桥臂栅极键合线连接到底层dbc的相应铜块上,并与所述下桥臂驱动电阻相连。

20.进一步地,所述顶层dbc基板和底层dbc基板均分为三层结构,上、下层均为金属铜,中间层为氮化铝陶瓷。

21.进一步地,所述顶层dbc基板和底层dbc基板均采用无氧铜材料,且表面进行镀镍处理。

22.本发明的另一方面还提供了一种如上述封装结构的封装方法,包括如下步骤:

23.根据所述封装结构制备所述顶层dbc基板和底层dbc基板,并刻蚀出相应的连接面结构;

24.在所述底层dbc基板对应的焊接位置均匀涂上焊料一,在所述焊料一上放置所述碳化硅功率芯片,使用夹具进行固定并采用真空回流焊的方法加热烧结;然后采用引线键合工艺将所述碳化硅功率芯片的电极与底层dbc基板的相应铜块进行电连接;

25.在所述顶层dbc基板对应的焊接位置均匀涂上焊料二,在所述焊料二上放置所述垫片,使用夹具进行固定并采用真空回流焊的方法加热烧结;

26.在所述碳化硅功率芯片的上表面均匀涂上焊料三,在所述焊料三上放置所述顶层dbc基板,再将所述垫片与碳化硅功率芯片的表面对齐,使用夹具固定并采用真空回流焊的方法加热烧结;

27.采用焊料四,将所述第一散热器和第二散热器分别焊接于顶层dbc基板、底层dbc基板的外侧,然后将绝缘凝胶注入外壳中,并冷凝至所述绝缘凝胶固化。

28.进一步地,所述焊料一、焊料二和焊料三是纳米银材料。

29.进一步地,所述焊料四采用sn63pb37材料。

30.通过本发明所构思的以上技术方案,与现有技术相比,能够取得以下有益效果:

31.(1)本发明提供的全碳化硅双面散热封装结构集成上下两层dbc,dbc的内侧金属用于实现功率回路及驱动回路连接,外侧金属用于连接散热器。实现双面散热,对比现在的单面散热模块热性能大大提升。

32.(2)本发明提供的全碳化硅双面散热封装结构中,功率端子dc+与dc-采用双端出线的方式,大大减小了多芯片并联时各开关管功率回路寄生参数不平衡引起的动态不均影响。

33.(3)本发明提供的全碳化硅双面散热封装结构中,各碳化硅mosfet芯片的驱动回路均采用kelvin连接,减小共源电感进而减小了功率回路对驱动回路的影响,提高了驱动信号的稳定性。

附图说明

34.图1是本发明实施例提供的全碳化硅双面散热模块的封装结构的外部结构示意图;

35.图2是本发明实施例提供的封装结构的内部结构示意图;

36.图3是本发明实施例提供的封装结构的内部平面示意图;

37.图4是本发明实施例提供的封装结构的底层dbc基板示意图;

38.图5是本发明实施例提供的封装结构的顶层dbc基板示意图;

39.图6是本发明实施例提供的封装结构对应的半桥电路示意图;

40.图7是本发明实施例提供的封装方法的流程示意图。

41.附图标记:1-上桥臂源极驱动端子、2-上桥臂栅极驱动端子、3-第一直流母线电压检测端子、4-主功率dc+端子、5-主功率dc-端子、6-第二直流母线电压检测端子、7-下桥臂栅极驱动端子、8-下桥臂源极驱动端子、9-底层dbc、10-主功率输出ac端子、11-顶层dbc、12-ac垫片、13-下桥臂开关管、14-下桥臂垫片、15-上桥臂垫片、16-上桥臂开关管、17-上桥臂栅极键合线、18-下桥臂栅极键合线、19-下桥臂驱动电阻、20-下桥臂源极键合线、21-上桥臂驱动电阻、22-上桥臂源极键合线、23-第一铜块、24-第二铜块、25-dc+铜块、26-ac2铜块、27-第五铜块、28-第六铜块、29-第四铜块、30-第三铜块、31-dc-铜块、32-ac1铜块。

具体实施方式

42.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以相互组合。

43.为实现上述目的,本发明实施例提供了一种全碳化硅双面散热的封装结构,包括底层dbc基板、碳化硅功率芯片、驱动电阻、垫片、顶层dbc基板、第一散热器和第二散热器;

44.所述碳化硅功率芯片和驱动电阻直接贴装于所述底层dbc基板,所述垫片直接焊接于所述顶层dbc基板;

45.所述碳化硅功率芯片、驱动电阻和垫片均位于所述顶层dbc基板和底层dbc基板之间;

46.所述第一散热器和第二散热器分别装配于所述顶层dbc基板和底层dbc基板的外

侧。

47.进一步地,所述封装结构还包括:

48.连接端子;所述连接端子包括主功率输入端子、主功率输出ac端子和驱动回路端子。

49.进一步地,所述主功率输入端子包括两组功率出线端,且所述两组功率出线端关于所述碳化硅功率芯片对称地设置。

50.进一步地,所述两组功率出线端关于所述碳化硅功率芯片对称地设置包括:

51.当所述碳化硅功率芯片为并联的多个芯片时,所述主功率输入端子包括第一功率出线端和第二功率出线端;其中,所述第一功率出线端到每个芯片的距离之和等于所述第二功率出线端到每个芯片的距离之和。

52.进一步地,所述碳化硅功率芯片包括两组碳化硅mosfet芯片构成半桥电路,各组碳化硅mosfet芯片之间相互并联分别构成所述半桥电路的上桥臂和下桥臂;

53.所述驱动电阻包括上桥臂驱动电阻和下桥臂驱动电阻;

54.所述驱动回路端子包括上桥臂源极驱动端子、下桥臂源极驱动端子、上桥臂栅极驱动端子和下桥臂栅极驱动端子;

55.所述上桥臂的碳化硅mosfet芯片的源极通过上桥臂源极键合线引出到底层dbc的相应铜块上,并与所述上桥臂源极驱动端子相连;所述上桥臂的碳化硅mosfet芯片的栅极通过上桥臂栅极键合线连接到底层dbc的相应铜块上,并与所述上桥臂驱动电阻相连;

56.所述下桥臂的碳化硅mosfet芯片的源极通过下桥臂源极键合线引出到底层dbc的相应铜块上,并与所述下桥臂源极驱动端子相连;所述下桥臂的碳化硅mosfet芯片的栅极通过下桥臂栅极键合线连接到底层dbc的相应铜块上,并与所述下桥臂驱动电阻相连。

57.进一步地,所述顶层dbc基板和底层dbc基板均分为三层结构,上、下层均为金属铜,中间层为氮化铝陶瓷。

58.进一步地,所述顶层dbc基板和底层dbc基板均采用无氧铜材料,且表面进行镀镍处理。

59.本发明实施例还提供了一种如上述封装结构的封装方法,包括如下步骤:

60.根据所述封装结构制备所述顶层dbc基板和底层dbc基板,并刻蚀出相应的连接面结构;

61.在所述底层dbc基板对应的焊接位置均匀涂上焊料一,在所述焊料一上放置所述碳化硅功率芯片,使用夹具进行固定并采用真空回流焊的方法加热烧结;然后采用引线键合工艺将所述碳化硅功率芯片的电极与底层dbc基板的相应铜块进行电连接;

62.在所述顶层dbc基板对应的焊接位置均匀涂上焊料二,在所述焊料二上放置所述垫片,使用夹具进行固定并采用真空回流焊的方法加热烧结;

63.在所述碳化硅功率芯片的上表面均匀涂上焊料三,在所述焊料三上放置所述顶层dbc基板,再将所述垫片与碳化硅功率芯片的表面对齐,使用夹具固定并采用真空回流焊的方法加热烧结;

64.采用焊料四,将所述第一散热器和第二散热器分别焊接于顶层dbc基板、底层dbc基板的外侧,然后将绝缘凝胶注入外壳中,并冷凝至所述绝缘凝胶固化。

65.进一步地,所述焊料一、焊料二和焊料三是纳米银材料。

66.进一步地,所述焊料四采用sn63pb37材料。

67.下面结合一个优选实施例,对上述实施例中涉及的内容进行说明。

68.本发明实施例提供了一种大功率全碳化硅功率模块的封装结构,该结构包括:底层直接覆铜陶瓷(dbc)基板、贴装在底层dbc基板上的碳化硅功率芯片、驱动电阻、垫片(spacer)、顶层dbc基板、连接端子。以下实施例中以碳化硅功率芯片具体为碳化硅mosfet芯片为例进行说明。

69.碳化硅mosfet芯片和驱动电阻都贴装在底层dbc基板上。六个碳化硅mosfet芯片三三并联并相连构成半桥电路结构。连接端子包括主功率输入端子(dc+端子和dc-端子)、主功率输出ac端子和驱动回路端子。

70.上桥臂的三颗碳化硅mosfet芯片的漏极通过纳米银烧结连接在底层dbc的dc+铜块上;下桥臂的三颗碳化硅mosfet芯片的漏极通过纳米银烧结连接在底层dbc的ac2铜块上。

71.上桥臂的三颗碳化硅mosfet芯片的源极通过纳米银烧结连接在各自的垫片(即上桥臂垫片)上,此三个垫片又通过纳米银烧结连接在顶层dbc的ac1铜块上;下桥臂的三颗碳化硅mosfet芯片的源极通过纳米银烧结连接在各自的垫片(即下桥臂垫片)上,此三个垫片又通过纳米银烧结连接在顶层dbc的dc-铜块上。顶层dbc的ac1铜块和底层dbc的ac2铜块也是通过银烧结与ac垫片相连接。

72.上桥臂的三颗碳化硅mosfet芯片的栅极通过键合线连接在底层dbc的第三铜块上并通过上桥臂驱动电阻与第二铜块相连,最后与上桥臂栅极驱动端连接;下桥臂的三颗碳化硅mosfet芯片的栅极通过键合线连接在底层dbc的第四铜块上并通过下桥臂驱动电阻与第五铜块相连,最后与下桥臂栅极驱动端连接。

73.除此之外,上桥臂三颗碳化硅mosfet芯片的源极又都通过键合线连接在底层dbc的第一铜块上并与上桥臂源极驱动端相连,构成上桥臂的三颗碳化硅mosfet芯片驱动的kelvin连接;下桥臂三颗碳化硅mosfet芯片的源极又都通过键合线连接在底层dbc的第六铜块上并与下桥臂源极驱动端相连,构成下桥臂的三颗碳化硅mosfet芯片驱动的kelvin连接。

74.dc+铜块连接三个dc+端子,两个构成双端功率出线,一个(即第一直流母线电压检测端子)与相应的dc-端子(即第二直流母线电压检测端子)构成检测电路;dc-铜块连接三个dc-端子,两个构成双端功率出线,一个(即第二直流母线电压检测端子)与相应的dc+端子(即第一直流母线电压检测端子)构成检测电路;ac2铜块连接ac端子。

75.本领域技术人员可以理解的是,上述双端出线指的是主功率输入端子包括两组功率出线端,且所述两组功率出线端关于所述碳化硅功率芯片对称地设置。

76.例如,当所述碳化硅功率芯片为并联的多个芯片时,所述主功率输入端子包括第一功率出线端和第二功率出线端;其中,所述第一功率出线端到每个芯片的距离之和等于所述第二功率出线端到每个芯片的距离之和。

77.而对于功率要求更高的场合,构成双端功率出线的不一定是两个端子,也可以是四个、六个甚至更多偶数个端子,端子的具体数量根据具体功率需求确定。只要功率出线端子数为偶数并且关于所述碳化硅功率芯片对称地设置,功率引线存在电流流向相反的结构,就能利用互感抵消一部分功率回路上的寄生电感,使得并联芯片换流回路寄生电感更

加均衡。

78.优选地,上述碳化硅功率器件的封装结构包含两层dbc结构,半桥结构上下桥臂的碳化硅功率器件都连接在底层dbc铜块上。

79.优选地,上述碳化硅功率器件的封装结构上下两面都直接焊接散热器,省去了底板,实现双面散热减小热阻。

80.优选地,上述碳化硅功率器件的封装结构功率引线采用双端出线,减小了多功率芯片并联导致的寄生参数不平衡带来的动态不均影响。

81.优选地,上述碳化硅功率器件的封装结构控制引线采用kelvin连接,降低驱动回路与功率回路之间的耦合作用,减小功率回路对驱动回路的干扰。

82.优选地,上述dc+与dc-均设置有信号出线,用于检测母线电压起到保护作用。

83.优选地,上述dbc基板分为三层结构,上、下层均为金属铜,中间层为氮化铝陶瓷。

84.上述非倒装结构(上、下桥臂的碳化硅功率器件在同一层)通过ac垫片连接构成半桥结构,上下桥臂均由三个碳化硅mosfet芯片构成。

85.上述底层dbc的铜层有八个铜块(连接面),分别是:第一铜块、第二铜块、第三铜块、dc+铜块、ac2铜块、第四铜块、第五铜块、第六铜块。

86.上述顶层dbc的铜层有两个连接面:ac1铜块、dc-铜块。

87.优选地,上述铜块之间的间距应不小于1mm,以保证绝缘。

88.本发明实施例还提供了一种全碳化硅双面散热模块的封装方法,包括如下步骤:

89.(1)根据拟封装的全碳化硅双面散热模块的结构,制备顶层与底层dbc基板,刻蚀出合适的dbc基板的连接面结构;

90.(2)采用焊料一,使用夹具对准将碳化硅mosfet芯片焊接到底层dbc基板的对应位置上;

91.(3)采用引线键合工艺将碳化硅mosfet芯片的栅极和源极与底层dbc基板的相应铜块进行电连接;

92.(4)采用焊料二,将垫片与顶层dbc基板连接;

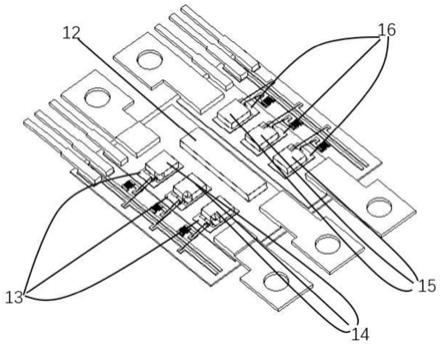

93.(5)采用焊料三,使用夹具对准将垫片与芯片连接;

94.(6)采用焊料四,将散热器与顶/底层dbc焊接在一起;将绝缘凝胶注入外壳中;冷凝使绝缘凝胶固化。

95.优选地,上述焊料一、焊料二、焊料三采用纳米银材料通过烧结实现连接。

96.优选地,上述焊料四采用sn63pb37材料,其熔点为183℃。

97.优选地,上述碳化硅mosfet芯片焊接至底层dbc基板、垫片焊接至顶层dbc基板均先在相应位置放置好焊料,使用夹具固定对齐放置芯片,最后采用真空回流焊的方法焊接。

98.下面对照附图对本发明实施例作进一步解释。图1所示是本发明实施例提供的全碳化硅双面散热模块的封装结构的外部结构示意图。主功率dc+端子4、主功率dc-端子5、主功率输出ac端子10、上桥臂源极驱动端子1、上桥臂栅极驱动端子2、第一直流母线电压检测端子3、第二直流母线电压检测端子6、下桥臂栅极驱动端子7和下桥臂源极驱动端子8均连接在顶层dbc 11与底层dbc 9内部相应的铜块上。

99.图2所示是本发明实施例提供的封装结构的内部结构示意图,图3所示,是本发明实施例提供的封装结构的内部平面示意图。上桥臂垫片15、下桥臂垫片14、ac垫片12上下表

面与顶/底层dbc的铜层之间均通过银烧结实现连接。上桥臂开关管16、下桥臂开关管13分别由三个碳化硅mosfet并联构成,其源极通过焊料连接在相应垫片上,并分别通过上桥臂源极键合线22和下桥臂源极键合线20引出到相应铜块上用于构成kelvin连接,其栅极分别通过上桥臂栅极键合线17和下桥臂栅极键合线18连接到相应铜块上并与各自的驱动电阻21、19相连;上桥臂开关管16的漏极与dc+铜块25通过银烧结连接,下桥臂开关管13的漏极与ac2铜块26通过银烧结连接。

100.图4所示为本发明实施例提供的封装结构的底层dbc基板示意图,其上表面铜层分成八个部分:第一铜块、第二铜块、第三铜块、dc+铜块、ac2铜块、第四铜块、第五铜块、第六铜块;

101.第一铜块23通过上桥臂源极键合线22与上桥臂开关管16的源极相连;第二铜块24与上桥臂驱动电阻21的一端相连,第三铜块30与上桥臂驱动电阻21的另一端相连,同时通过上桥臂栅极键合线17与上桥臂开关管16的栅极相连;dc+铜块25与上桥臂开关管16的漏极相连,同时与dc+端子4相连,还与第一直流母线电压检测端子3相连。ac2铜块26与下桥臂开关管13的漏极相连,同时与ac垫片12下表面相连,还与主功率输出ac端子10相连;第六铜块28通过下桥臂源极键合线20与下桥臂开关管13的源极相连;第五铜块27与下桥臂驱动电阻19的一端相连,第四铜块29与下桥臂驱动电阻19的另一端相连,同时通过下桥臂栅极键合线18与下桥臂开关管13的栅极相连。

102.图5所示为本发明实施例提供的封装结构的顶层dbc基板示意图,其下表面铜层分为两部分:dc-铜块31、ac1铜块32;

103.dc-铜块31与下桥臂垫片14上表面相连,还与dc-端子5相连,同时与第二直流母线电压检测端子6相连;ac1铜块32与ac垫片12的上表面相连。

104.上述顶/底层dbc基板采用无氧铜材料,表面进行镀镍处理,增强表面的抗氧化性和利于引线键合。

105.由图1、图2与图3可以看到,由于主功率dc+端子4与主功率dc-端子5均采用双端出线,功率引线存在电流流向相反的结构,利用互感抵消了一部分功率回路上的寄生电感,并联芯片换流回路寄生电感更加均衡。另一方面可以看到,上桥臂驱动回路端子(上桥臂栅极驱动端子2、上桥臂源极驱动端子1)和下桥臂驱动回路端子(下桥臂栅极驱动端子7、下桥臂源极驱动端子8)均采用kelvin连接方式极大地减小了驱动回路的寄生电感,而避免了传统连接方式(例如上桥臂源极驱动端子直接连接主功率输出ac端子10、下桥臂源极驱动端子直接连接主功率dc-端子5)中共源电感对驱动回路的干扰。

106.图6所示是本发明实施例提供的封装结构对应的半桥电路示意图;半桥电路结构,由主功率dc+端子4、主功率dc-端子5、主功率输出ac端子10、上桥臂栅极驱动端子2、上桥臂源极驱动端子3、下桥臂栅极驱动端子6、下桥臂源极驱动端子7、上桥臂开关管16、上桥臂驱动电阻21、下桥臂开关管13、下桥臂驱动电阻19以及它们之间的电气连接形成。

107.图7是本发明实施例提供的全碳化硅双面散热模块封装方法的流程示意图,具体包括以下步骤:

108.步骤s101,选择dbc基板,其中dbc基板绝缘层材料选择具有高热导率的氮化铝(aln)材料,顶层dbc与底层dbc均按图4、图5所示蚀刻出相应图案;

109.步骤s102,先在底层dbc对应的焊接位置上均匀涂好纳米银材料,在上边放置要焊

接的碳化硅mosfet芯片或端子,使用夹具进行固定,最后采用真空回流焊的方法加热烧结;

110.步骤s103,采用引线键合方法将碳化硅mosfet芯片的栅极以及源极与底层dbc基板的相应铜块连接;

111.步骤s104,先在顶层dbc对应的焊接位置上均匀涂好纳米银材料,放好垫片和dc-端子,使用夹具固定,最后采用真空回流焊的方法加热烧结;

112.步骤s105,先在芯片上表面均匀涂好纳米银材料,在其上放好顶层dbc,其中垫片与芯片表面对齐,使用夹具固定,最后采用真空回流焊的方法加热烧结;

113.步骤s106,将散热器焊接在顶层及底层dbc外侧上,将硅凝胶灌入其中,灌封后静置24小时直至硅凝胶固化。

114.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1