包括嵌入式焊接连接结构的半导体封装的制作方法

1.本公开总体上涉及一种半导体封装,更具体地,涉及一种包括嵌入式焊接连接结构(embedded solder connection structure)的半导体封装。

背景技术:

2.半导体行业已经朝着以低成本制造具有低重量、小尺寸、高速度、多功能、高性能和高可靠性的半导体产品的方向发展,并且实现这种产品的重要技术之一是半导体封装技术。半导体封装技术是通过晶片工艺(wafer process)来安装具有形成在封装基板上的电路部分的半导体芯片的技术,通过封装基板确保半导体芯片和外部电子装置之间的电连接的技术,以及保护半导体芯片免受外部环境影响的技术。

3.近来,响应于对更轻和更短封装产品的需求,持续进行对封装基板和层叠在封装基板上的半导体芯片的结构稳定性和电连接稳定性的研究。

技术实现要素:

4.根据本公开的一个方面的半导体封装可以包括:第一半导体芯片,其包括第一芯片主体部和设置在凹入第一芯片主体部的区域中的第一芯片后凸块;以及第二半导体芯片,其层叠在第一半导体芯片上,并且包括第二芯片主体部和从第二芯片主体部突出的第二芯片前凸块。第一芯片后凸块可以包括下金属层和设置在下金属层上的焊接层。第二芯片前凸块可以接合到焊接层。第二芯片前凸块可以被设置成在第二芯片前凸块和焊接层的接合表面上至少覆盖焊接层。

5.根据本公开的另一方面的半导体封装可以包括:基部构件;第一半导体芯片,其设置在基部构件上;以及第二半导体芯片,其设置在第一半导体芯片上。第一半导体芯片可以包括:第一芯片主体部,其包括前表面和后表面;以及第一芯片后凸块,其设置在从后表面凹入第一芯片主体部的区域中。第二半导体芯片可以包括:第二芯片主体部,其包括前表面和后表面;以及第二芯片前凸块,其从第二芯片主体部的前表面突出。第一芯片后凸块可以包括下金属层和设置在下金属层上的焊接层。第一半导体芯片的焊接层和第二半导体芯片的第二芯片前凸块可以彼此接合。第二芯片前凸块可以被设置成在第二芯片前凸块和焊接层的接合表面上至少覆盖焊接层。

6.公开了根据本公开的另一方面的制造半导体封装的方法。在该方法中,可以制备第一半导体芯片,其包括第一芯片主体部和设置在凹入第一芯片主体部的区域中的第一芯片后凸块,其中第一芯片后凸块可以包括下金属层和设置在下金属层上的焊接材料层。可以制备第二半导体芯片,其包括第二芯片主体部和从第二芯片主体部突出的第二芯片前凸块。可以接合第一半导体芯片的焊接材料层和第二半导体芯片的第二芯片前凸块以形成焊接层。在接合焊接材料层和第二芯片前凸块时,第二芯片前凸块和焊接层可以彼此接合,使得第二芯片前凸块在第二芯片前凸块和焊接层的接合表面上至少覆盖焊接层。

附图说明

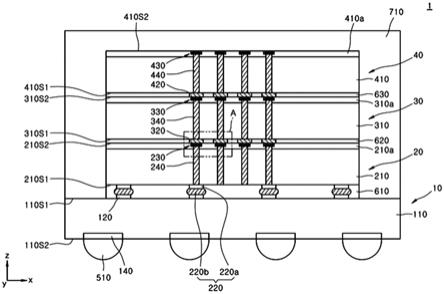

7.图1是示出根据本公开的一个实施方式的半导体封装的截面图。

8.图2是与图1的半导体封装中的半导体芯片之间的连接结构相关的区域“a”的放大图。

9.图3、图4a、图4b、图5、图6a、图6b、图6c、图7a、图7b和图8至图10是示出根据本公开的一个实施方式的制造半导体封装的方法的截面图。

具体实施方式

10.本文使用的术语可以对应于考虑到它们在实施方式中的功能而选择的词汇,并且根据实施方式所属领域的普通技术,这些术语的含义可以进行不同的解释。如果进行了详细定义,则术语可以根据定义进行解释。除非另有定义,否则本文使用的术语(包括技术和科学术语)与实施方式所属领域的普通技术人员所通常理解的含义相同。

11.在本公开的实施方式的描述中,诸如“第一”和“第二”、“上”和“下”以及“左”和“右”的描述用于区分构件,而不是用于限制构件本身或者表示特定的顺序。

12.在整个说明书中,相同的附图标记表示相同的元件。即使没有参照一幅附图提及或描述某一附图标记,也可以参照另一附图提及或描述该附图标记。此外,即使一幅附图中未示出某一附图标记,也可以参照另一附图来提及或描述该附图标记。

13.在附图中,为了图示清楚,可能放大元件(例如,层或区域)的尺寸(例如,宽度或厚度)。此外,可能简化元件以在附图中清楚地示出其操作、其状态以及其间的关系。在说明书中,对附图的描述基于观察者的视点。应当理解,当一个元件被称为位于另一元件“上”时,它可以直接位于另一元件“上”,或者也可以存在中间元件。在附图中,相同的附图标记始终表示相同的元件。还应注意,在本说明书中,“连接/联接”是指一个组件不仅直接联接另一组件,而且通过中间组件间接联接另一组件。此外,只要没有特别提及,单数形式可以包括复数形式,反之亦然。

14.图1是示出根据本公开的一个实施方式的半导体封装1的截面图。图2是与图1的半导体封装1中的半导体芯片之间的连接结构相关的区域“a”的放大图。

15.参照图1和图2,半导体封装1可以包括基部构件(base member)10、设置在基部构件10上的第一半导体芯片20以及设置在第一半导体芯片20上的第二半导体芯片30。此外,半导体封装1还可以包括设置在第二半导体芯片30上的第三半导体芯片40。在图1和图2中,一个半导体芯片层叠在第二半导体芯片30上,但并不必须限制于此。在一些实施方式中,两个或更多个半导体芯片可以层叠在第二半导体芯片30上。此外,半导体封装1还可以包括在基部构件10上围绕第一半导体芯片至第三半导体芯片20、30和40的模制层710。

16.基部构件10可以将第一半导体芯片至第三半导体芯片20、30和40电连接到外部系统。基部构件10例如可以是插入件(interposer)或印刷电路板(pcb)。

17.基部构件10可以包括基部主体110。在一个实施方式中,基部主体110可以包括半导体材料,例如硅(si)。在另一实施方式中,基部主体110可以包括陶瓷材料,例如氧化硅或玻璃。在另一实施方式中,基部主体110可以包括聚合物材料,例如树脂。

18.基部主体110可以包括第一表面110s1和第二表面110s2。第一表面110s1可以是面向第一半导体芯片20的表面。第二表面110s2可以是基于基部主体110与第一表面110s1相

反的表面。

19.用于电连接到第一半导体芯片20的芯片连接焊盘120可以设置在基部主体110的第一表面110s1上。芯片连接焊盘120可以连接到第一芯片前凸块220的焊接层220b,使得基部构件10和第一半导体芯片20可以彼此电连接。凸块焊盘140可以位于基部主体110的第二表面110s2。在一个实施方式中,除了凸块焊盘140的与第二表面110s2位于相同的平面上的下表面之外,凸块焊盘140可以嵌入到基部主体110中。在一些实施方式中,凸块焊盘140可以被设置成从第二表面110s2向外突出。

20.连接结构510可以设置在凸块焊盘140的下表面上。连接结构510例如可以是焊接凸块或焊球。连接结构510连接到另一印刷电路板或外部系统,使得印刷电路板或外部系统可以电连接到基部构件10。根据所执行的功能,连接结构510可以分类为电源引脚结构(power pin structure)、接地引脚结构或输入/输出引脚结构。多个连接结构510可以在第二表面110s2上彼此隔开。

21.尽管未示出,但是基部构件10可以包括内部布线。内部布线可以包括多个电路图案层和电连接所述多个电路图案层的通孔。内部布线可以将芯片连接焊盘120电连接到凸块焊盘140。因此,通过连接结构510从另一印刷电路板或外部系统输入到凸块焊盘140的电信号可以经由内部布线到达芯片连接焊盘120。

22.参照图1和图2,第一半导体芯片20可以设置在基部构件10上。第一半导体芯片20可以包括第一芯片主体部210。第一芯片主体部210可以由硅(si)制成。第一半导体芯片20可以是通过硅集成工艺制造(silicon integration process)的芯片。第一芯片主体部210可以包括前表面210s1和后表面210s2。这里,前表面210s1可以是与第一半导体芯片20内部的集成电路密集分布的区域相邻的表面。也就是说,诸如晶体管的有源元件和诸如电容器或电阻器的无源元件可以集成在第一芯片主体部210的邻近前表面210s1的内部区域中。此外,电连接到有源元件和无源元件的多个布线图案层可以设置在第一芯片主体部210的邻近前表面210s1的内部区域中。后表面210s2可以是前表面210s1基于第一芯片主体部210的相反表面。在第一芯片主体部210的邻近后表面210s2的内部区域中,与邻近前表面210s1的第一芯片主体部210相比,集成电路可以不存在或者可以以相对较低的密度分布。

23.第一芯片前凸块220可以设置在第一芯片主体部210的前表面210s1上。第一芯片前凸块220可以被设置成对应于基部构件10的芯片连接焊盘120。每一个第一芯片前凸块220可以包括凸块主体220a和焊接层220b。凸块主体220a例如可以包括铜(cu)或镍(ni)。焊接层220b可以包括包含锡(sn)和银(ag)的焊接材料(solder material)。通过将第一芯片前凸块220的焊接层220b接合到芯片连接焊盘120,基部构件10能够电连接到第一半导体芯片20。

24.第一芯片前凸块220可以通过通孔240电连接到第一芯片。参照图1,第一芯片前凸块220可以被设置成在z方向上接触第一芯片通孔240,或者可以被设置成在z方向上不接触第一芯片通孔240。当第一芯片前凸块220在z方向上不接触第一芯片通孔240时,第一芯片前凸块220可以通过设置在第一芯片主体部210中的重分布线(未示出)而电连接到第一芯片通孔240的端部。

25.此外,第一芯片后连接结构230可以设置在第一芯片主体部210的邻近后表面210s2的区域中。第一芯片后连接结构230可以接触第二半导体芯片30的前凸块320。由此,

第一半导体芯片20能够电连接到第二半导体芯片30。此外,第一芯片通孔240设置在第一芯片主体部210内部,以将第一芯片前凸块220电连接到第一芯片后连接结构230。通过第一芯片通孔240,从基部构件10输入到第一半导体芯片20的电信号能够朝向第二半导体芯片30传输。

26.在一些未示出的实施方式中,金(au)层可以附加地设置在每一个第一芯片前凸块220的凸块主体220a的表面上。焊接层220b可以设置在金(au)层上。金(au)层可以用作凸块主体220a的抗氧化层。此外,当焊接层220b接合凸块主体220a和芯片连接焊盘120时,金(au)层可以用于促进焊接层220b中的金属间化合物(intermetallic compound)的形成,或者可以直接与焊接层220b中的焊接材料结合以转化成金属间化合物。如下所述,当焊接材料包括锡(sn)时,金属间化合物可以包括金-锡(ausn4)。

27.第一芯片主体部210可以包括设置在邻近于后表面210s2的区域中的第一芯片钝化层210a。例如,第一芯片钝化层210a可以被设置成从第一芯片主体部210的后表面210s2在第一芯片主体部210的向内方向上具有预定厚度。第一芯片钝化层210a可以包括无机材料。例如,第一芯片钝化层210a可以包括氧化硅、氮化硅或氮氧化硅。本文中关于参数(例如,预定厚度、预定电压或预定间距)使用的词语“预定”表示在参数用于工艺或算法之前确定参数的值。对于一些实施方式,在工艺或算法开始之前确定参数的值。在其它实施方式中,在工艺或算法期间但是在参数用于工艺或算法之前确定参数的值。

28.参照图1和图2,第一芯片后连接结构230可以被设置成邻近第一芯片主体部210的后表面210s2。第一芯片后连接结构230可以设置在从第一芯片主体部210的后表面210s2凹入第一芯片主体部210的区域中。在一个实施方式中,参照图2,可以在凹入第一芯片主体部210的第一芯片钝化层210a的区域中形成沟槽图案212。第一芯片后连接结构230可以分别设置在各个沟槽图案212中。第一芯片后连接结构230可以通过通孔240电连接到第一芯片。同时,如图所示,第一芯片钝化层210a可以被设置成围绕每一个第一芯片后连接结构230的一部分和每一个第一芯片通孔240的一部分。

29.每一个第一芯片后连接结构230可以包括阻挡层231和第一芯片后凸块232。第一芯片后凸块232可以包括下金属层232a和设置在下金属层232a上的焊接层232b。

30.阻挡层231可以沿着沟槽图案212的内表面设置。阻挡层231可以被设置成围绕第一芯片后凸块232。阻挡层231能够将第一芯片后凸块232与第一芯片钝化层210a隔离。阻挡层231能够防止第一芯片后凸块232和第一芯片钝化层210a之间的材料扩散。此外,阻挡层231可以通过通孔240电连接到第一芯片。例如,阻挡层231可以包括钽(ta)。在一个实施方式中,阻挡层231可以是钽(ta)层。在另一实施方式中,阻挡层231可以形成为钽层和钴(co)层的两层结构。此时,钽(ta)层可以被设置成接触第一芯片钝化层210a和第一芯片通孔240,并且钴(co)层可以设置在钽(ta)层上。

31.下金属层232a可以以预定厚度设置在阻挡层231的与沟槽图案212底部相对应的部分上。下金属层232a可以提供构成在形成焊接层232b的工艺中在焊接层232b内部产生的金属间化合物的金属,这将在后面参照图7a和图7b进行描述。此外,下金属层232a可以用于防止构成第一芯片通孔240的铜(cu)扩散到焊接层232b中。例如,下金属层232a可以包括镍(镍)。

32.焊接层232b可以在垂直于沟槽图案212底部的方向上设置在下金属层232a上。焊

接层232b可以接合到第二半导体芯片30的第二芯片前凸块320。结果,第一芯片后凸块232可以电连接到第二芯片前凸块320。

33.焊接层232b可以包括焊接材料和金属间化合物。焊接材料可以包括锡(sn)或银(ag)等。如下所述,如图7a和图7b所示,当使用图4b所示的第一半导体芯片20的第一芯片后凸块232的焊接材料层232c将第一半导体芯片20的下金属层232a和第二半导体芯片30的第二芯片前凸块320接合时,焊接材料层232c可以转变成包括金属间化合物的焊接层232b。可以通过焊接材料层232c和下金属层232a之间的化学反应以及焊接材料层232c和第二芯片前凸块320之间的化学反应中的至少一者来形成金属间化合物。

34.在一个实施方式中,当下金属层232a和第二芯片前凸块320中的每一个包括镍(ni)时,金属间化合物例如可以包括镍-锡(ni3sn4)。在一些实施方式中,可以在第二芯片前凸块320的表面上附加地设置金(au)层,以防止第二芯片前凸块320的氧化。在这种情况下,例如,金属间化合物还可以包括金-锡(ausn4)。

35.每一个第一芯片后凸块232可以被设置成在横向(即,x方向)上与其它第一芯片后凸块具有预定间距pb。例如,间距pb可以是10μm或更小。

36.填充材料层610可以设置在基部构件10和第一半导体芯片20在z方向上交叠的区域中。填充材料层610可以包括有机材料。例如,填充材料层610可以包括底部填料(underfill)。在一些实施方式中,填充材料层610可以与模制层710包括相同的材料。也就是说,当形成模制层710时,可以用模制材料填充基部构件10和第一半导体芯片20在z方向上交叠的区域,而无需形成填充材料层610的单独工艺。

37.参照图1和图2,第二半导体芯片30可以设置在第一半导体芯片20上。第二半导体芯片30可以包括第二芯片主体部310。第二芯片主体部310可以由硅(si)形成。第二半导体芯片30可以是通过硅(si)集成工艺制造的芯片。第二芯片主体部310可以包括前表面310s1和后表面310s2。这里,前表面310s1可以是邻近第二半导体芯片30内部的集成电路密集分布的区域的表面。后表面310s2可以是基于第二芯片主体部310与前表面310s1相反的表面。在第二芯片主体部310的邻近后表面310s2的内部区域中,与邻近前表面310s1的第二芯片主体部310相比,集成电路可以不存在或者可以以相对较低的密度存在。

38.第二芯片前凸块320可以设置在第二芯片主体部310的前表面310s1上。第二芯片前凸块320可以被设置成从第二芯片主体部310突出。如图2所示,第二芯片前凸块320可以接合到第一芯片后凸块232的焊接层232b。第二芯片前凸块320例如可以包括镍(ni)。

39.第二芯片后连接结构330可以设置在第二芯片主体部310的后表面310s2上。第二芯片后连接结构330可以电连接到第三半导体芯片40的前凸块420。此外,电连接第二芯片前凸块320和第二芯片后连接结构330的第二芯片通孔340可以设置在第二芯片主体部310内部。

40.参照图2,第二芯片前凸块320可以被设置成对应于第一芯片主体部210的第一芯片后凸块232。在第二芯片前凸块320和第一芯片后凸块232中的焊接层232b的接合表面(即,后表面210s2)上,每一个第二芯片前凸块320可以被设置成与相邻的第二芯片前凸块具有预定间距pb。此时,第二芯片前凸块320之间的间距pb可以基本上与第一芯片后凸块232之间的间距pb相同。

41.第二芯片前凸块320可以被设置成在第二芯片前凸块320和焊接层232b的接合表

面处至少覆盖焊接层232b。也就是说,每一个第二芯片前凸块320可以被设置成覆盖焊接层232b的整体。此外,每一个第二芯片前凸块320可以被设置成在接合表面处额外地覆盖阻挡层231。

42.第二芯片前凸块320可以被第二芯片主体部310的前表面310s1上的第一聚合物粘合层620围绕。例如,第二芯片前凸块320的侧面可以被第一聚合物粘合层620掩埋。第一聚合物粘合层620可以包括例如聚合物材料。第一聚合物粘合层620例如可以包括非导电膜(ncf)。第一聚合物粘合层620可以接合到第一芯片主体部210的第一芯片钝化层210a。第一聚合物粘合层620和第一芯片钝化层210a的接合表面可以与第二芯片前凸块320和焊接层232b的接合表面是基本相同的平面。

43.在一个实施方式中,第二芯片前凸块320可以被设置成在第二芯片前凸块320和焊接层232b的接合表面处覆盖焊接层232b的整体。此外,焊接层232b可以通过阻挡层231与第一芯片钝化层210a分离。阻挡层231与第一聚合物粘合层620分离,并且第一芯片钝化层210a在两者之间,使得焊接层232b可以通过第二芯片前凸块320和阻挡层231与第一聚合物粘合层620隔离。也就是说,焊接层232b可以被配置为不接触第一聚合物粘合层620。

44.同时,再次参照图1,第二芯片主体部310可以包括设置在邻近后表面310s2的区域中的第二芯片钝化层310a。例如,第二芯片钝化层310a可以被设置成从第二芯片主体部310的后表面310s2在第二芯片主体部310的向内方向上具有预定厚度。第二芯片钝化层310a可以包括无机材料。例如,第二芯片钝化层310a可以包括氧化硅、氮化硅或氮氧化硅。

45.参照图1,第二芯片后连接结构330可以被设置成邻近第二芯片主体部310的后表面310s2。第二芯片后连接结构330可以设置在从第二芯片主体部310的后表面310s2凹入第二芯片主体部310的区域中。第二芯片后连接结构330的配置可以与第一半导体芯片20的第一芯片后连接结构230的配置基本相同。因此,省略了对第二芯片后连接结构300的配置的描述。尽管未示出,但是每一个第二芯片后连接结构330可以包括与第一芯片后连接结构230的阻挡层231、第一芯片后凸块232和第一焊接层232b相对应的阻挡层、第二芯片后凸块和第二焊接层。可以在形成在第二芯片钝化层310a中的沟槽图案内部形成第二芯片后连接结构330的阻挡层、第二芯片后凸块和第二焊接层。也就是说,第二芯片钝化层310a可以被设置成围绕第二芯片后连接结构330。此外,第二芯片钝化层310a可以被设置成还围绕第二芯片通孔340的一部分。

46.第二芯片后连接结构330可以接合到第三半导体芯片40的第三芯片前凸块420。第二芯片后连接结构330和第三芯片前凸块420之间的接合结构可以与上述第一芯片后连接结构230和第二芯片前凸块320的接合结构基本相同。

47.再次参照图1,第三半导体芯片40可以设置在第二半导体芯片30上。第三半导体芯片40可以包括第三芯片主体部410,其包括前表面410s1和后表面410s2。第三半导体芯片40可以包括设置在第三芯片主体部410的前表面410s1上的第三芯片前凸块420。此时,第三芯片主体部410的前表面410s1上的第三芯片前凸块420可以被第二聚合物粘合层630围绕。

48.第三半导体芯片40可以包括设置在邻近第三芯片主体部410的后表面410s2的区域中的第三芯片钝化层410a。此外,第三半导体芯片40可以包括被设置成邻近第三芯片主体部410的后表面410s2的第三芯片后连接结构430。第三半导体芯片40可以包括连接第三芯片前凸块420和第三芯片后连接结构430的第三芯片通孔440。

49.同时,第三半导体芯片40的配置可以与第二半导体芯片30的配置基本相同。例如,第三芯片主体部410、第三芯片钝化层410a、第三芯片前凸块420、第三芯片后连接结构430和第三芯片通孔440的配置可以与第二芯片主体部310、第二芯片钝化层310a、第二芯片前凸块320、第二芯片后连接结构330和第二芯片通孔340的配置基本相同。此外,第二聚合物粘合层630的配置可以与第一聚合物粘合层620的配置基本相同。

50.在一些实施方式中,当多个半导体芯片层叠在基部构件10上时,多个半导体芯片中的最上面的半导体芯片可以不包括芯片通孔和芯片后连接结构。也就是说,在图1中,当第一半导体芯片至第三半导体芯片20、30和40层叠在基部构件10上时,最上层的第三半导体芯片40可以不包括第三后连接结构430和第三芯片通孔440。

51.再次参照图1,围绕第一半导体芯片至第三半导体芯片20、30和40的模制层710可以设置在基部构件10上。模制层710可以包括例如环氧模塑料(emc)。模制层710可以用于物理地或化学地保护第一半导体芯片至第三半导体芯片20、30和40免受外部环境的影响。

52.如上所述,芯片通孔240、340和440可以分别在半导体芯片20、30和40中被用于在基部构件10和层叠在基部构件10上的半导体芯片20、30和40之间交换电信号。根据本公开的各种实施方式,电连接第一半导体芯片20和第二半导体芯片30的焊接层232b可以通过第二芯片前凸块320、阻挡层231和第一芯片钝化层210a而与第一聚合物粘合层620隔离。这种物理隔离能够防止由例如导电性阳极细丝物(conductive anodic filament)产生现象的电化学反应引起的缺陷。导电性阳极细丝物产生现象可以是这样的电化学反应:在阳极和阴极被设置成与聚合物层接触的结构中,当在阳极和阴极之间施加电场时,在聚合物层中产生由阳极材料制成的细丝物。当在高温和高湿度环境中聚合物层吸收水分并且聚合物层的绝缘性劣化的状态下在阳极和阴极之间施加高电场时,可能发生电化学反应。

53.更具体地,当在环境中施加高电场时,在阳极中的导电化学物质氧化之后,氧化的导电化学物质可以以离子的形式释放到聚合物层中。所释放的导电化学物质的离子可以沿着电场向阴极移动,并通过获得电子而被还原,从而在聚合物层内形成导电丝。当导电化学物质形成导电丝时,在阳极和阴极之间会出现诸如电短路的缺陷。

54.再次参照图2,可以通过第一电路径p1和第二电路径p2来执行第一半导体芯片20和第二半导体芯片30之间的信号交换。这里,第一电路径p1表示通过设置在图2左侧的第一芯片通孔240、第一芯片后连接结构230、第二芯片前凸块320和第二芯片通孔340的电信号流。第二电路径p2表示通过设置在图2右侧的第一芯片通孔240、第一芯片后连接结构230、第二芯片前凸块320和第二芯片通孔340的电信号流。这里,为了产生沿着第一电路径p1和第二电路径p2的电信号流,可以将预定电压分别施加到第一电路径p1和第二电路径p2。

55.如果与图2所示的本公开的当前实施方式不同,位于第一电路径p1中的焊接层232b(即,图2中左侧所示的焊接层232b)和位于第二电路径p2中的焊接层232b(即,图2中右侧所示的焊接层323b)分别直接接触第一聚合物粘合层620,则可能产生诸如上述导电性阳极细丝物的电缺陷。也就是说,在高温和高湿度的环境中,当施加到第一电路径p1的电压和施加到第二电路径p2的电压在第一聚合物粘合层620上产生电压差时,第一电路径p1和第二电路径p2中的焊接层232b中的一个可以用作阳极,而另一个用作阴极。因此,用作阳极的焊接层232b内的锡(sn)可以被氧化以产生锡(sn)离子,并且锡(sn)离子可以在第一聚合物粘合层620的内部朝向阴极移动。此外,锡(sn)离子可以在第一聚合物粘合层620的内部被

还原以形成锡(sn)的细丝物。锡(sn)的细丝物可能在阳极和阴极之间产生电短路。

56.同时,再次参照图2,根据本公开的一个实施方式,第二芯片前凸块320、阻挡层231和第一芯片钝化层210a可以允许焊接层232b和第一聚合物粘合层620彼此分离。因此,当分别沿着第一电路径p1和第二电路径p2施加预定电压时,可以防止由于上述电化学反应而导致焊接层323b内部的锡(sn)移动到第一聚合物粘合层620中的现象。结果,根据本公开的一个实施方式,焊接层232b在结构上稳定,从而能够确保第一半导体芯片和第二半导体芯片之间的焊接接合的电性可靠性。

57.同时,第二半导体芯片30和第三半导体芯片40之间的电连接结构可以与第一半导体芯片20和第二半导体芯片30之间的电连接结构基本相同。因此,能够以相同的方式确保位于第二半导体芯片30和第三半导体芯片40之间的焊接接合的电性可靠性。

58.图3、图4a、图4b、图5、图6a、图6b、图6c、图7a、图7b和图8至图10是示出根据本公开的一个实施方式的制造半导体封装的方法的截面图。这里,图4b是图4a的区域“b”的放大图。图6b是图6a的区域“c”的放大图,而图6c是图6a的区域“d”的放大图。图7b是图7a的区域“e”的放大图。

59.参照图3,可以设置基部构件10。基部构件10可以包括具有第一表面110s1和第二表面110s2的基部主体110。芯片连接焊盘120可以设置在基部主体110的第一表面110s1上。

60.凸块焊盘140可以暴露于基部主体110的第二表面110s2。在一个实施方式中,除了凸块焊盘140的与第二表面110s2位于相同的平面上的下表面之外,每一个凸块焊盘140可以埋入在基部主体110内部。在一些实施方式中,凸块焊盘140可以被设置成从第二表面110s2向外突出。

61.尽管未示出,但是基部构件10可以包括内部布线。内部布线可以包括多个电路图案层和电连接所述多个电路图案层的通孔。内部布线可以将芯片连接焊盘120电连接到凸块焊盘140。

62.参照图4a和图4b,可以设置第一半导体芯片20。第一半导体芯片20可以包括第一芯片主体部210。第一芯片主体部210可以由硅(si)制成。通过硅工艺制造的多个集成电路层和使多个集成电路层绝缘的多个绝缘层可以设置在第一芯片主体部210中。第一芯片主体部210可以包括前表面210s1和后表面210s2。

63.可以在第一芯片主体部210的前表面210s1上形成凸块主体220a。每一个凸块主体220a可以包括例如镍(ni)。可以在每一个凸块主体220a上形成焊接材料层220c。焊接材料层220c可以包括例如锡(sn)或银(ag)等。凸块主体220a和焊接材料层220c可以通过电镀工艺形成。

64.第一芯片主体部210可以包括第一芯片钝化层210a。第一芯片钝化层210a可以被形成为从第一芯片主体部210的后表面210s2在第一芯片主体部210的向内方向上具有预定厚度。第一芯片钝化层210a可以包括无机材料。例如,第一芯片钝化层210a可以包括氧化硅、氮化硅或氮氧化硅。可以通过诸如化学气相沉积或物理气相沉积的半导体薄膜沉积工艺在第一芯片主体部210中形成第一芯片钝化层210a。

65.第一芯片后连接结构230可以被形成为邻近第一芯片主体部210的后表面210s2。一起参照图4a和图4b,形成第一芯片后连接结构230的工艺可以如下执行。首先,可以从后表面210s2到第一芯片主体部210内部形成沟槽图案212。例如,可以在第一芯片主体部210

的第一芯片钝化层210a内部形成沟槽图案212。对于形成沟槽图案212的工艺,可以应用半导体光刻工艺和蚀刻工艺。

66.随后,可以沿着沟槽图案212的内表面形成阻挡层231。例如,每一个阻挡层231可以包括钽(ta)。在一个实施方式中,阻挡层231可以是钽(ta)层。在另一实施方式中,阻挡层231可以形成为钽(ta)层和钴(co)层的两层结构。在这种情况下,钽(ta)层可以被设置成接触第一芯片钝化层210a和第一芯片通孔240,并且钴(co)层可以设置在钽(ta)层上。例如,可以使用诸如溅射的半导体薄膜沉积工艺来执行形成阻挡层231的工艺。

67.随后,可以在阻挡层231的与沟槽图案212的底面相对应的部分上形成预定厚度的下金属层232a。例如,每一个下金属层232a可以包括镍(ni)。下金属层232a例如可以通过电镀方法形成。在一个实施方式中,可以在阻挡层231上形成电镀种子层(未示出),并且可以使用电镀种子层通过电解电镀方法形成下金属层232a。

68.随后,可以在下金属层232a上形成预定厚度的焊接材料层232c。焊接材料层232c例如可以使用电镀方法形成。焊接材料层232c例如可以包括诸如锡(sn)或银(ag)等焊接材料。这里,可以控制焊接材料层232c的上表面以使其与第一芯片主体部210的后表面210s2位于基本相同的水平。

69.在一个实施方式中,每一个沟槽图案212可以被形成为与相邻的沟槽图案具有预定间隔。因此,每一个形成在沟槽图案212的内部的第一芯片后连接结构230可以与在横向方向(即,x方向)上相邻的其它第一芯片后连接结构具有预定间距pb。间距pb例如可以是10μm或更小。

70.参照图4a,可以在第一芯片主体部210中形成将第一芯片前凸块220电连接到第一芯片后连接结构230的第一芯片通孔240。可以通过电镀工艺形成第一芯片通孔240。

71.参照图5,第一半导体芯片20可以层叠在基部构件10上。例如,凸块主体220a和芯片连接焊盘120可以使用图4a所示的形成在凸块主体220a上的焊接材料层220c而彼此接合。因此,基部构件10和第一半导体芯片20可以彼此电连接。

72.在接合工艺中,图4a所示的第一半导体芯片20的焊接材料层220c可以放置在图3所示的基部构件10的对应芯片连接焊盘120上,并且可以将热量施加到焊接材料层220c。焊接材料层220c的焊料(solder)通过热量而流动,使得芯片连接焊盘120和凸块主体220a能够彼此接合。此后,焊料可以被冷却,并且焊接材料层232c能够转变成图5所示的焊接层220b。

73.焊接层220b还可以包括通过源自于焊接材料层220c的焊料组分和化学反应所产生的金属间化合物。化学反应可以包括焊接材料层220c和凸块主体220a之间的化学反应以及焊接材料层220c和芯片连接焊盘120之间的化学反应中的至少一者。金属间化合物可以包括例如镍-锡(ni3sn4)或铜-锡(cu-sn)。

74.随后,可以在基部主体110和第一芯片主体部210在z方向上交叠的区域中形成填充材料层610。填充材料层610可以包括聚合物材料。例如,填充材料层610可以通过使用底部填料的底部填料工艺形成。在一些实施方式中,可以省略形成填充材料层610的工艺。相反,在将参照图9描述的形成模制层710的工艺中,可以一起执行利用模制材料填充基部主体110和第一芯片主体部210的交叠区域的工艺。

75.参照图6a至图6c,可以设置第二半导体芯片30。第二半导体芯片30可以包括第二

芯片主体部310。第二芯片主体部310可以包括前表面310s1和后表面310s2。

76.可以在第二芯片主体部310的前表面310s1上形成第二芯片前凸块320。可以在第二芯片主体部310的邻近后表面310s2的区域中形成第二芯片后连接结构330。此外,在第二芯片主体部310中,可以在邻近后表面310s2的内部区域中形成第二芯片钝化层310a。参照图6c,可以在形成在第二芯片钝化层310a内部的沟槽图案312中形成第二芯片后连接结构330。每一个第二芯片后连接结构330可以包括阻挡层331、下金属层332a和焊接材料层332c。此外,再次参照图6a,在第二芯片主体部310中,可以形成将第二芯片前凸块320电连接到第二芯片后连接结构330的第二芯片通孔340。

77.在一个实施方式中,除了第二芯片前凸块320之外,图6a至图6c中示出的第二半导体芯片30的配置可以与上面参照图4a和图4b描述的第一半导体芯片20的配置基本相同。也就是说,第二半导体芯片30的第二芯片主体部310、第二芯片钝化层310a、第二芯片后连接结构330和第二芯片通孔340的配置可以与第一半导体芯片20的第一芯片主体部210、第一芯片钝化层210a、第一芯片后连接结构230和第一芯片通孔240的配置基本相同。

78.参照图6a至图6c,位于第二半导体芯片30的前表面310s1上的每一个第二芯片前凸块320的面积可以大于图4b所示的位于第一半导体芯片20的后表面210s2上的每一个焊接材料层232c的面积。因此,如稍后结合图7a和图7b所述,当分别接合对应的第二芯片前凸块320和焊接材料层232c时,在接合界面处,每一个第二前凸块320能够覆盖每一个焊接材料层232c的整体。在这种情况下,接合界面可以与第一芯片主体部210的后表面210s2是基本相同的平面。

79.参照图6a和图6b,每一个第二芯片前凸块320可以在前表面310s1上与在横向方向(即,x方向)上相邻的第二芯片前凸块320具有第二间距尺寸的间距pb。第二芯片前凸块320的间距pb可以对应于图4a所示的第一半导体芯片20的第一芯片后凸块230的间距pb。同时,一起参照图6a和图6c,第二芯片后连接结构330可以与在横向方向(即,x方向)上相邻的其它第二后连接结构具有预定间距pb。

80.参照图6a和图6b,可以在第二芯片主体部310的前表面310s1上形成围绕第二芯片前凸块320的第一聚合物粘合层620。第一聚合物粘合层620例如可以包括聚合物材料,例如树脂。例如,第一聚合物粘合层620可以包括非导电膜(ncf)。

81.可以使用如下各种实施方式的方法来执行形成第一聚合物粘合层620的方法。在一个实施方式中,可以制备聚合物组分的粘合膜。能够通过在第二芯片主体部310的前表面310s1上施加压力来附着粘合膜。由此,粘合膜能够覆盖第二芯片前凸块320。此时,可以选择性地去除粘合膜,从而不将粘合膜施加在第二芯片前凸块320的一个表面320s上。在另一实施方式中,可以制备具有预定粘度(viscosity)的液体聚合物粘合剂。例如,通过应用涂覆方法(coating method),可以将聚合物粘合剂涂覆在第二芯片主体部310的前表面310s1上。然后,涂覆的聚合物粘合剂可以不完全固化,使得不完全固化的粘合剂可以覆盖第二芯片前凸块320。此时,可以选择性地去除没有完全固化的聚合物粘合剂,从而不将聚合物粘合剂施加在第二芯片前凸块320的一个表面320s上。在另一实施方式中,可以制备光敏聚合物粘合剂。可以将光敏聚合物粘合剂涂覆在第二芯片主体部310的前表面310s1上,使得光敏聚合物粘合剂可以覆盖第二芯片前凸块320。此后,可以选择性地对光敏聚合物粘合剂进行曝光和显影,以选择性地去除施加在每一个第二芯片前凸块320的一个表面320s上的聚

合物粘合剂。通过应用上述各种实施方式的方法,可以在前表面310s1上形成围绕第二芯片前凸块320的第一聚合物粘合层620。作为通过上述各种方法形成第一聚合物粘合层620的结果,如图6b所示,每一个第二芯片前凸块320的一个表面320s和第一聚合物粘合层620的一个表面620s可以设置在基本相同的平面上。

82.参照图7a和图7b,第二半导体芯片30可以层叠在第一半导体芯片20上。例如,通过施加热量和压力,图4b所示的第一芯片主体部210的第一芯片后连接结构230中的焊接材料层232c可以接合到图6a和图6b所示的第二芯片主体部310的第二芯片前凸块320。在接合工艺中,焊接材料层232c可以转变成焊接层232b。另外,在z方向上,第一芯片主体部210和第二芯片主体部310之间的空间可以由第一聚合物粘合层620填充。

83.如上文参照图6a和图6b所述,位于第二芯片主体部310的前表面310s1上的每一个第二芯片前凸块320的面积可以大于以上参照图4b所述的位于第一芯片主体部210的后表面210s2上的焊接材料层232c的面积。因此,作为接合彼此对应的第二芯片前凸块320和焊接材料层232c的结果,在接合界面处,每一个第二芯片前凸块320可以每一个覆盖焊接层232b的整体。接合界面与第一芯片主体部210的后表面210s2可以是基本相同的平面。

84.参照图8,第三半导体芯片40可以层叠在第二半导体芯片30上。第三半导体芯片40可以包括第三芯片主体部410。第三芯片主体部410可以包括前表面410s1和后表面410s2。

85.可以在第三芯片主体部410的前表面410s1上形成第三芯片前凸块420。可以在第三芯片主体部410的邻近后表面410s2的区域中形成第三芯片后连接结构430。此外,第三芯片主体部410可以包括形成在邻近后表面410s2的内部区域中的第三芯片钝化层410a。可以在第三芯片主体部410的内部形成将第三芯片前凸块420连接到第三芯片后连接结构430的第三芯片通孔440。

86.第三半导体芯片40的配置可以与第二半导体芯片30的配置基本相同。也就是说,第三芯片主体部410、第三芯片钝化层410a、第三芯片前凸块420、第三芯片后连接结构430和第三芯片通孔440的配置可以与第二芯片主体部310、第二芯片钝化层310a、第二芯片前凸块320、第二芯片后连接结构330和第二芯片通孔340的配置基本相同。

87.在一些实施方式中,顺序层叠在半导体封装的基部构件10上的多个半导体芯片中的最上面的半导体芯片可以不包括芯片通孔和芯片后连接结构。参照图8,与所示不同,被设置为基部构件10上的顶层的第三半导体芯片40可以不包括第三芯片后连接结构430和第三芯片通孔440。

88.同时,在第二半导体芯片30上层叠第三半导体芯片40的方法可以与以上参照图7a和图7b描述的在第一半导体芯片20上层叠第二半导体芯片30的方法基本相同。

89.参照图9,可以形成模制层710以覆盖基部构件10上的第一半导体芯片至第三半导体芯片20、30和40。在形成模制层710的方法中,例如,可以在基部构件10上设置环氧模塑料(emc),以掩埋第一半导体芯片至第三半导体芯片20、30和40。在一些实施方式中,在参照图5描述的基部构件10和第一半导体芯片20的接合工艺中,当省略在基部主体110和第一芯片主体部210在z方向上交叠的区域中形成填充材料层610的工艺时,可以在图9的模制层710的形成操作中执行在基部主体110和第一芯片主体部210在z方向上交叠的区域中填充环氧模制材料的工艺。

90.参照图10,可以在基部主体110的第二表面110s2上形成连接结构510。可以分别在

各个凸块焊盘140上形成连接结构510。每一个连接结构510可以是焊接凸块或焊球。

91.通过上述工艺,能够制造根据本公开的一个实施方式的半导体封装。

92.已经出于例示的目的公开了本公开的实施方式。本领域技术人员将会理解,在不脱离本公开和所附权利要求的范围和精神的情况下,可进行各种修改、添加和替换。

93.相关申请的交叉引用

94.本技术要求于2020年4月9日提交的韩国申请no.10-2020-0043654的优先权,其全部内容通过引用结合于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1