一种芯片信息校验的方法与流程

[0001]

本发明涉及半导体测试领域,特别是涉及一种芯片信息校验的方法。

背景技术:

[0002]

在集成电路晶圆的测试过程中,通常会保存所有被测芯片的测试数据与测试结果,并且需要将每片集成电路晶圆上的每个被测芯片的芯片信息与其具体测试数据和测试结果一一对应。因此,在测试时往往会先通过通用接口总线(general-purpose interface bus,gpib)从集成电路探针台(prober)读回光学字符(optical character recognition,ocr)所识别的所述被测芯片的批号、片号和位置坐标等信息,并将这些信息记录下来,然后保存这些被测芯片对应的详细测试数据及测试结果。

[0003]

但是,ocr识别有可能出现异常,导致被测芯片的批号错误;或者,gpib的通讯出现异常,导致被测芯片的位置坐标错误,这就导致被测芯片最终记录的信息错误,使得这些信息错误无法与实际测试数据一一对应,还使得这些信息错误无法与实际测试结果一一对应。而这些问题如果没有被及时发现,则会出现实际测试结果不合格的被测芯片流入到下一环节中去,使得这些被测芯片无法追溯。

技术实现要素:

[0004]

本发明的目的在于提供一种芯片信息校验的方法,以解决现有技术中将信息记录错误的被测芯片流入下一环节,或者较晚发现信息错误,导致重新测试的问题。

[0005]

为了解决上述问题,本发明提供了一种芯片信息校验的方法,包括以下步骤:

[0006]

步骤s1:提供一集成电路晶圆,所述集成电路晶圆包括多个被测芯片,所述被测芯片进行了多个测试项目,且每个所述被测芯片均包括后台芯片信息;

[0007]

步骤s2:获取每个所述被测芯片的识别芯片信息;

[0008]

步骤s3:比较同一个所述被测芯片的后台芯片信息和识别芯片信息,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配;

[0009]

步骤s4:若所述被测芯片的后台芯片信息和识别芯片信息不匹配,查找不匹配原因,在查找到原因后纠正所述不匹配原因,并返回步骤s2;或者,若所述被测芯片的后台芯片信息和识别芯片信息匹配,记录所述被测芯片的测试数据及测试结果。

[0010]

可选的,每个所述被测芯片的后台芯片信息为二进制数据。

[0011]

进一步的,每个所述被测芯片的批号、片号、位置坐标、流片厂代码、测试厂代码先经过ascii码转换,再经过二进制翻译得到所述后台芯片信息。

[0012]

可选的,步骤s2包括:

[0013]

通过通用接口总线从集成电路探针台读回光学字符识别每个所述被测芯片的识别芯片信息;

[0014]

记录所述识别芯片信息,并对应保存每个所述被测芯片的测试结果和测试数据。

[0015]

进一步的,所述识别芯片信息包括被测芯片的批号、片号以及位置坐标、流片厂代

码、测试厂代码等信息。

[0016]

进一步的,所述测试数据具体包括rawdata,stdf,txt等格式的测试数据。

[0017]

进一步的,所述测试数据包括至少一个筛分标识。

[0018]

进一步的,所述测试数据包括hardbin和softbin。

[0019]

可选的,所述被测芯片的后台芯片信息和识别芯片信息不匹配时,所述集成电路晶圆中被测芯片的芯片信息记录错误。

[0020]

进一步的,所述被测芯片的后台芯片信息和识别芯片信息不匹配时,所述被测芯片的批号错误;或者,所述通用接口总线接口的通讯错误;又或者,所述被测芯片的位置坐标设置错误。

[0021]

与现有技术相比存在以下有益效果:

[0022]

本发明提供一种芯片信息校验的方法,包括以下步骤:步骤s1:提供一集成电路晶圆,所述集成电路晶圆包括多个被测芯片,所述被测芯片进行了多个测试项目,且每个所述被测芯片均包括后台芯片信息;步骤s2:获取每个所述被测芯片的识别芯片信息;步骤s3:比较同一个所述被测芯片的后台芯片信息和识别芯片信息,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配;步骤s4:若所述被测芯片的后台芯片信息和识别芯片信息不匹配,查找不匹配原因,在查找到原因后纠正所述不匹配原因,并返回步骤s2;或者,若所述被测芯片的后台芯片信息和识别芯片信息匹配,记录所述被测芯片的测试数据及测试结果。本发明的方法在不影响测试效率的前提下,利用芯片信息实时比对校验,并在第一时间发现芯片信息错误并找出其错误的原因,避免由于被测芯片的芯片信息错误发现较晚造成的需要重新测试或者测试结果不合格的芯片直接流入下一环节,从而避免了造成无法弥补的损失;还在测试时间不变的前提下,实时校验记录了被测芯片的芯片信息是否正确,提高了被测芯片的芯片信息可追溯性。

附图说明

[0023]

图1a为一种位置坐标设置错误的测绘图的示意图;

[0024]

图1b为一种位置坐标设置正确的测绘图的示意图;

[0025]

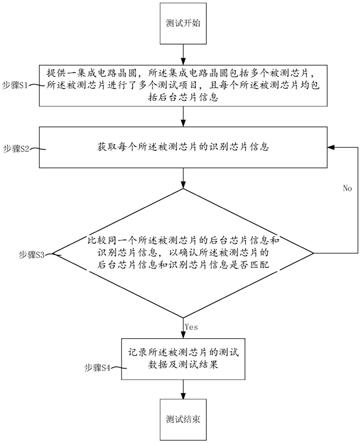

图2为本发明一实施例的一种芯片信息校验的方法的流程示意图;

[0026]

图3为本发明一实施例的集成电路晶圆的芯片测试map图。

[0027]

附图标记说明:

[0028]

1-集成电路晶圆;10-被测芯片。

具体实施方式

[0029]

如背景技术所述,被测芯片例如是通过多工位并行测试,那么在测试开始之前,需要按照要求,对应探针卡上位置进行排列,并设定好位置坐标,例如16个被测芯片的位置排列的测试设置方案包括2*8排列,8*2排列,4*4排列等。在设定位置坐标时出现设置错误,例如是将2*8排列设定为8*2排列,此时被测芯片的实际结果与被测芯片的测试结果无法一一对应。图1a为一种位置坐标设置错误的测绘图的示意图,图1b为一种位置坐标设置正确的测绘图的示意图。如图1a和图1b所示,正确的map图是在最外圈有比较均匀的一圈测试不合格的被测芯片(即集成电路晶圆的边缘位置处黑色的一圈被测芯片),而位置坐标设置错误

的map图整体发生了偏移,使得其左边边缘处多了一圈测试不合格的被测芯片(即集成电路晶圆的左边边缘处多了一圈黑色的被测芯片),这种由于位置坐标设置错误得到的map图错误一般不易被察觉,只有有经验的工程师在测试完成后查验map图时才会发现,在发现之后的解决办法也只有重新测试整片晶圆。而那些无法被发现的将会流入到下一环节中去,使得这些被测芯片无法追溯。

[0030]

而现有技术中,无法完全避免被测芯片的信息错误引起的种种问题,可能在发现后重新进行测试导致浪费测试时间,也可能直接导致本身测试结果不合格的被测芯片由于信息记录错位流入到下一环节,造成无法弥补的失误。

[0031]

本发明的核心思想在于提供一种芯片信息校验的方法,可以在集成电路晶圆的测试时间不变的前提下,实时校验记录被测芯片的芯片信息是否正确,从而提高芯片信息可追溯性。

[0032]

以下将对本发明的一种芯片信息校验的方法作进一步的详细描述。下面将参照附图对本发明进行更详细的描述,其中表示了本发明的优选实施例,应该理解本领域技术人员可以修改在此描述的本发明而仍然实现本发明的有利效果。因此,下列描述应当被理解为对于本领域技术人员的广泛知道,而并不作为对本发明的限制。

[0033]

为了清楚,不描述实际实施例的全部特征。在下列描述中,不详细描述公知的功能和结构,因为它们会使本发明由于不必要的细节而混乱。应当认为在任何实际实施例的开发中,必须做出大量实施细节以实现开发者的特定目标,例如按照有关系统或有关商业的限制,由一个实施例改变为另一个实施例。另外,应当认为这种开发工作可能是复杂和耗费时间的,但是对于本领域技术人员来说仅仅是常规工作。

[0034]

为使本发明的目的、特征更明显易懂,下面结合附图对本发明的具体实施方式作进一步的说明。需说明的是,附图均采用非常简化的形式且均使用非精准的比率,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0035]

图2为本实施例的一种芯片信息校验的方法的流程示意图。如图2所示,本实施例提供了一种芯片信息校验的方法,所述芯片信息校验的方法为集成电路晶圆在测试过程中的芯片信息校验的方法。

[0036]

所述方法包括以下步骤:

[0037]

步骤s1:提供一集成电路晶圆,所述集成电路晶圆包括多个被测芯片,所述被测芯片进行了多个测试项目,且每个所述被测芯片均包括后台芯片信息;

[0038]

步骤s2:获取每个所述被测芯片的识别芯片信息;

[0039]

步骤s3:比较同一个所述被测芯片的后台芯片信息和识别芯片信息,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配;

[0040]

步骤s4:若所述被测芯片的后台芯片信息和识别芯片信息不匹配,查找不匹配原因,在查找到原因后纠正所述不匹配原因,并返回步骤s2;或者,

[0041]

若所述被测芯片的后台芯片信息和识别芯片信息匹配,记录所述被测芯片的测试数据及测试结果。

[0042]

下面结合图2-3对本发明实施例所提供的一种芯片信息校验的方法进行详细介绍。

[0043]

首先执行步骤s1,提供一集成电路晶圆1,所述集成电路晶圆1包括多个被测芯片

10,所述被测芯片10进行了多个测试项目,且每个所述被测芯片10均包括后台芯片信息。

[0044]

其中,每个所述被测芯片10的批号、片号、位置坐标、流片厂代码、测试厂代码等信息,先将这些信息转换为ascii码,再翻译为二进制数据,并将所述二进制数据生成每个被测芯片10的后台芯片信息,从而生成集成电路晶圆1中所有被测芯片10的后台芯片信息数据库。多个所述测试项目例如是所述被测芯片10的所有测试项目。

[0045]

图3为本实施例的集成电路晶圆的芯片测试map图。如图3所示,在本实施例中,所述集成电路晶圆1共有615个被测芯片10,每个所述被测芯片10可以包括批号、片号、位置坐标、流片厂代码、测试厂代码等信息,作为示例,每个所述被测芯片10的批号为7eca23;所述片号为1#~25#;所述位置坐标包括x坐标位置和y坐标位置,所述x坐标位置的坐标范围为1~28,y坐标位置的坐标范围为1~25。所述被测芯片10通过双工位测试,两个工位为上下排布,且首个被测的被测芯片10坐标为(x=9,y=2),按照所述被测芯片10在测试时设计的最优走步方法,计算得到所述被测芯片10的测试坐标依次为(9,2)、(10,2)、(11,1)、(11,2)、(12,1)、(12,2)

……

(17,1)、(17,2)、(18,2)、(19,2)、(22,4)、(21,3)、(21,4)、(20,3)、(20,4)

……

。所述流片厂代码例如是sc,所述测试厂代码例如是tc。根据如上信息,编写程序,将所述批号、片号、位置坐标中的数字、字母以及符号等均转换为ascii码,再将其翻译为二进制数据,生成每个被测芯片10的后台芯片信息,从而生成集成电路晶圆1中所有被测芯片10的后台芯片信息数据库,所述后台芯片信息数据库包括所述集成电路晶圆1每个被测芯片10的芯片信息。

[0046]

如下表格所示,每行二进制数据代表一个被测芯片的后台芯片信息,且每行的前48位二进制数据表示被测芯片的批号,第48~56位二进制数据表示被测芯片的片号,第57~72位二进制数据表示被测芯片的位置坐标,第73~88位二进制数据表示被测芯片的流片厂代码,第89~104位二进制数据表示被测芯片的测试厂代码,该表格为本实施例的集成电路晶圆1中所有被测芯片的后台芯片信息数据库。

[0047][0048]

接着执行步骤s2,获取每个所述被测芯片的识别芯片信息。

[0049]

具体的,

[0050]

首先,通过通用接口总线(general-purpose interface bus,gpib)从集成电路探针台(prober)读回光学字符(optical character recognition,ocr)识别每个所述被测芯片的识别芯片信息。

[0051]

其中,所述识别芯片信息包括被测芯片的批号、片号以及位置坐标、流片厂代码、测试厂代码等信息。

[0052]

接着,记录所述识别芯片信息,并对应保存每个所述被测芯片的测试结果和测试数据,所述测试数据具体包括rawdata,stdf,txt等格式的测试数据。其中,所述测试数据包括至少一个筛分标识,例如是包括hardbin和softbin,所述hardbin用于标识被测芯片在其对应的测试项目合格是芯片的落入位置,所述softbin也是标识对被测芯片的筛选,其是hardbin分类后的再细分,且其只作为一个结构存储在表格里供客户查看,结果包括对该测试项目的相关表述。所述测试结果包括合格(pass)和不合格(fail)。

[0053]

如图3所示,所述集成电路晶圆中黑色的被测芯片10即为测试项目不合格的芯片,所述集成电路晶圆中白色未显示出的被测芯片10即为测试项目合格的芯片。

[0054]

接着执行步骤s3,比较同一个所述被测芯片10的后台芯片信息和识别芯片信息,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配。具体的,将每个所述被测芯片10的识别芯片信息与对应的所述后台芯片信息进行比较,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配。

[0055]

接着执行步骤s4:若所述被测芯片的后台芯片信息和识别芯片信息不匹配,查找不匹配原因,在查找到原因后纠正所述不匹配原因,并返回步骤s2;或者,若所述后台芯片信息和识别芯片信息匹配,记录所述被测芯片的测试数据及测试结果。

[0056]

具体的,

[0057]

当每个所述被测芯片10的识别芯片信息与对应的所述后台芯片信息相匹配(即每个所述被测芯片10识别芯片信息与对应的所述后台芯片信息一致),那么说明所述集成电路晶圆1中的每个被测芯片10的芯片信息记录正确,因此,芯片信息校验的测试结束。

[0058]

当每个所述被测芯片10的识别芯片信息与对应的所述后台芯片信息不匹配(每个所述被测芯片10识别芯片信息与对应的所述后台芯片信息不一致)时,那么说明所述被测芯片10的芯片信息记录错误(例如被测芯片10的批号错误,或者,gpib通讯错误,又或者位置坐标设置错误等),需要暂时停止测试,进行检查找到导致错误的原因,在查找到错误的原因之后,进行及时纠正,并在纠正错误之后返回步骤s2重新获取每个所述被测芯片的识别芯片信息,比较同一个所述被测芯片的后台芯片信息和识别芯片信息,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配,若所述后台芯片信息和识别芯片信息匹配,结束测试;若所述后台芯片信息和识别芯片信息不匹配,继续检查找到导致错误的原因,在查找处错误的原因之后,进行及时纠正,并在纠正错误之后返回步骤s2,直至所述后台芯片信息和识别芯片信息匹配,记录所述被测芯片的测试数据及测试结果,芯片信息校验的测试结束。本实施例的方法在不影响测试效率的前提下,利用芯片信息实时比对校验,并在第一时间发现芯片信息错误并找出其错误的原因,避免由于被测芯片的芯片信息错误发现较晚造成的需要重新测试或者测试结果不合格的芯片直接流入下一环节,从而避免了造成无法弥补的损失;还在测试时间不变的前提下,实时校验记录了被测芯片的芯片信息是否正确,提高了被测芯片的芯片信息可追溯性。

[0059]

综上所述,本发明提供一种芯片信息校验的方法,包括以下步骤:步骤s1:提供一集成电路晶圆,所述集成电路晶圆包括多个被测芯片,所述被测芯片进行了多个测试项目,且每个所述被测芯片均包括后台芯片信息;步骤s2:获取每个所述被测芯片的识别芯片信

息;步骤s3:比较同一个所述被测芯片的后台芯片信息和识别芯片信息,以确认所述被测芯片的后台芯片信息和识别芯片信息是否匹配;步骤s4:若所述被测芯片的后台芯片信息和识别芯片信息不匹配,查找不匹配原因,在查找到原因后纠正所述不匹配原因,并返回步骤s2;或者,若所述被测芯片的后台芯片信息和识别芯片信息匹配,记录所述被测芯片的测试数据及测试结果。本发明的方法在不影响测试效率的前提下,利用芯片信息实时比对校验,并在第一时间发现芯片信息错误并找出其错误的原因,避免由于被测芯片的芯片信息错误发现较晚造成的需要重新测试或者测试结果不合格的芯片直接流入下一环节,从而避免了造成无法弥补的损失;还在测试时间不变的前提下,实时校验记录了被测芯片的芯片信息是否正确,提高了被测芯片的芯片信息可追溯性。

[0060]

此外,需要说明的是,除非特别说明或者指出,否则说明书中的术语“第一”、“第二”的描述仅仅用于区分说明书中的各个组件、元素、步骤等,而不是用于表示各个组件、元素、步骤之间的逻辑关系或者顺序关系等。可以理解的是,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1