具有假晶高电子迁移率晶体管的单晶集成电路元件的制作方法

1.本发明是有关一种由一个以上的假晶高电子迁移率晶体管(pseudomorphic high electron mobility transistors,phemts)构成的单晶集成电路元件,特别是有关一种整片晶片中或不同晶片间本质上具有极高度均一性的夹止或临界电压的单晶积体栅极沉降假晶高电子迁移率晶体管。

背景技术:

2.栅极沉降或栅极埋入技术已广泛用于实现增强型(enhanchment

‑

mode/e

‑

mode)假晶高电子迁移率晶体管(以下简称为phemt),增强型phemt的夹止电压或临界电压(以下使用夹止电压)为正值,这是因为栅极至通道之间的距离缩短所致。当晶体管外延结构及工艺被适当地设计时,栅极沉降技术的运用应包括但不该仅限于增强型phemt。栅极沉降技术要求精细地控制热处理工艺的温度及时间,以确保第一沉积的栅极金属能均匀且全面性地扩散进入萧基能障层。因此,对整片晶片中或不同晶片间,栅极沉降phemt具有高度一致的夹止电压,是本领域中最主要的需求。

3.在某些应用中,例如数位及偏压电路,需要多个具有不同夹止电压的phemt。举例来说,将一恒关(normally

‑

off)(正夹止电压)phemt和一恒开(normally

‑

on)(负夹止电压)phemt外延集成于同一基板上。图1揭示了由一空乏型(depletion

‑

mode/d

‑

mode)phemt d1和一增强型(enhanchment

‑

mode/e

‑

mode)phemt e1构成的一现有单晶集成电路元件。所述现有单晶集成电路元件包括一化合物半导体基板100和一外延结构110。生长于化合物半导体基板100上的外延结构110从下到上依序包括一缓冲层111、一通道层112、一萧基层113、一萧基接触层114、一第一刻蚀终止层115、一第一导电层116、一第二刻蚀终止层117和一第二导电层118。空乏型/增强型phemt的源极电极101/103和漏极电极102/104形成于第二导电层118上。一凹槽底部由萧基接触层114定义的栅极凹槽108是位于空乏型phemt的源极电极101和漏极电极102之间。一凹槽底部由萧基层113定义的栅极凹槽109是位于增强型phemt的源极电极103和漏极电极104之间。空乏型phemt的栅极电极120是沉积于栅极凹槽108中的萧基接触层114上。增强型phemt的栅极电极130是沉积于栅极凹槽109中的萧基层113上。如图1所示,空乏型和增强型phemt的栅极电极是形成于不同的半导体层上。这表示对现有单晶集成电路元件中的空乏型和增强型phemt两者需要额外的光刻和刻蚀步骤。

4.图2揭示了由一空乏型phemt d1和一增强型phemt e1构成的另一个现有单晶集成电路元件。如图2所示,空乏型和增强型phemt两者皆以栅极沉降技术制作。所述单晶集成电路元件包括一化合物半导体基板200和一外延结构210。生长于化合物半导体基板200上的外延结构210从下到上依序包括一缓冲层211、一通道层212、一第一萧基能障层213、一第一刻蚀终止层214、一第二萧基能障层215、一第二刻蚀终止层216和一欧姆接触层217。空乏型/增强型phemt的源极电极201/203和漏极电极202/204形成于欧姆接触层217上。一凹槽底部由第二萧基能障层215定义的栅极凹槽208是位于空乏型phemt的源极电极201和漏极电极202之间。一凹槽底部由第一萧基能障层213定义的栅极凹槽209是位于增强型phemt的

源极电极203和漏极电极204之间。空乏型phemt的栅极电极220是沉积于栅极凹槽208中的第二萧基能障层215上。增强型phemt的栅极电极230是沉积于栅极凹槽209中的第一萧基能障层213上。一栅极沉降区域221/231是位于空乏型/增强型phemt的栅极电极220/230下方。在图2所示现有单晶集成电路元件中,空乏型phemt和增强型phemt个别的栅极电极是形成于不同的萧基层上。这表示需要额外的光刻和刻蚀步骤来形成空乏型和增强型phemt的栅极凹槽208、209,导致在phemt工艺中产生额外的成本及复杂性。最重要的是,第一、第二萧基能障层213、215经刻蚀的表面可能会造成缺陷和表面态,其可能劣化晶体管特性并使phemt夹止电压偏移目标值。

5.此外,图2的现有单晶集成电路元件在控制空乏型phemt和增强型phemt个别的夹止电压会遭遇严重的问题。实际上不可能将空乏型/增强型phemt栅极沉降区域221/231的底边界完美地控制在萧基能障层的一特定的狭窄区域内。这个事实可归因于整片晶片中或不同晶片间栅极电极的厚度不一致,以及热处理的温度和时间的不一致。这些不良效应使得整片晶片中晶体管的夹止电压产生高度差异。

6.因此,非常需要一个新的设计来达到整片晶片中或不同晶片间本质上具有极高度均一性的夹止电压的单晶积体栅极沉降phemt。

技术实现要素:

7.为了在具有一个以上栅极沉降phemt的单晶集成电路元件中达到预期的夹止电压均一性,本发明实施一种由半导体层堆叠的复合萧基层结构。藉由控制栅极金属的沉降深度至萧基层堆叠的半导体层中的一特定接面,可显著降低整片晶片中或不同晶片间夹止电压的差异。此外,在单晶集成电路元件中每个phemt的夹止电压可调整为任何(正或负)想要的值。因此,本发明提供一种由一低夹止电压phemt和一高夹止电压phemt所构成的多层结构的单晶集成电路元件,其中该多层结构包括一半导体基板,其上叠合该低夹止电压phemt和该高夹止电压phemt共用的多层外延半导体层,该多层外延半导体层包括一缓冲层,该缓冲层上叠合一通道层,该通道层上叠合一萧基层,而该萧基层上叠合一第一覆盖层。该萧基层从下到上包括至少三个半导体材料的层叠区域,其中两个相邻的层叠区域的每一者与另一者的材料不同,且两者之间设有一层叠区域接面,其中该层叠区域接面的任两者至该半导体基板的距离不同。该低夹止电压phemt和该高夹止电压phemt的源极接触和漏极接触耦合于该第一覆盖层。该低夹止电压phemt和该高夹止电压phemt的每一者包括一栅极接触、一第一栅极金属层、一栅极沉降区域和一栅极沉降底边界。该低夹止电压phemt和该高夹止电压phemt个别的栅极接触耦合于该萧基层,其中该低夹止电压phemt和该高夹止电压phemt个别的第一栅极金属层与该萧基层的最上层层叠区域接触。该低夹止电压phemt的栅极沉降区域和该高夹止电压phemt的栅极沉降区域分别位于该低夹止电压phemt和该高夹止电压phemt的第一栅极金属层下方。该低夹止电压phemt和该高夹止电压phemt个别的栅极沉降底边界是位于该萧基层内,其中该高夹止电压phemt的栅极沉降底边界比该低夹止电压phemt的栅极沉降底边界更接近该半导体基板,且该高夹止电压phemt的栅极沉降底边界是位于该萧基层的层叠区域接面的一者的上或下之内。

8.此外,本发明提供另一种在一多层结构中包括一低夹止电压phemt和一高夹止电压phemt的单晶集成电路元件,其中该多层结构包括一半导体基板,其上叠合该低夹止电压

phemt和该高夹止电压phemt共用的多层外延半导体层,该多层外延半导体层包括一缓冲层,该缓冲层上叠合一通道层,该通道层上叠合一萧基层,该萧基层上叠合一第一接触层,该第一接触层上叠合一第一覆盖层。该萧基层从下到上包括至少三个半导体材料的层叠区域,其中两个相邻的层叠区域的每一者与另一者的材料不同,且两者之间设有一层叠区域接面,其中该层叠区域接面的任两者至该半导体基板的距离不同。该第一接触层与该萧基层的最上层层叠区域的一上表面接触,且该第一接触层与该萧基层的最上层层叠区域之间设有一最上层接触接面。该低夹止电压phemt和该高夹止电压phemt的源极接触和漏极接触耦合于该第一覆盖层。该低夹止电压phemt和该高夹止电压phemt的每一者包括一栅极接触、一第一栅极金属层、一栅极沉降区域和一栅极沉降底边界。该低夹止电压phemt和该高夹止电压phemt个别的栅极接触耦合于该萧基层,且该低夹止电压phemt和该高夹止电压phemt个别的第一栅极金属层与该第一接触层接触。该低夹止电压phemt的栅极沉降区域和该高夹止电压phemt的栅极沉降区域分别位于该低夹止电压phemt和该高夹止电压phemt的第一栅极金属层下方。该低夹止电压phemt的栅极沉降底边界是位于该萧基层中或该最上层接触接面的上或下之内。该高夹止电压phemt的栅极沉降底边界是位于该萧基层的层叠区域接面的一者的上或下之内。且该高夹止电压phemt的栅极沉降底边界比该低夹止电压phemt的栅极沉降底边界更接近该半导体基板。

9.在一些实施例中,所述低夹止电压phemt的栅极沉降底边界是位于所述萧基层的层叠区域接面的一者的上或下之内。

10.在一些实施例中,所述高夹止电压phemt的栅极沉降底边界是位于所述萧基层的层叠区域接面的一者处。

11.在一些实施例中,所述低夹止电压phemt的栅极沉降底边界是位于所述萧基层的层叠区域接面的一者处或所述最上层接触接面处。

12.在一些实施例中,所述第一接触层包括gaas、algaas、algaasp、inalgaas、ingap、ingaasp和inalgap中的至少一者,且所述第一接触层与所述萧基层的最上层层叠区域的材料不同。

13.在一些实施例中,在所述萧基层的任两个相邻的层叠区域中,由algaas为基底的半导体材料构成的层叠区域与由ingap为基底的半导体材料构成的另一层叠区域交替层叠,其中所述algaas为基底的半导体材料包括algaas、algaasp和inalgaas中的至少一者,而所述ingap为基底的半导体材料包括ingap、ingapas和alingap中的至少一者。

14.在一些实施例中,所述低夹止电压phemt和高夹止电压phemt个别的第一栅极金属层包括钼(mo)、钨(w)、硅化钨(wsi)、钛(ti)、铱(ir)、钯(pd)、铂(pt)、镍(ni)、钴(co)、铬(cr)、钌(ru)、锇(os)、铑(rh)、钽(ta)、氮化钽(tan)、铝(al)和铼(re)中的至少一者。

15.在一些实施例中,所述低夹止电压phemt和高夹止电压phemt个别的第一栅极金属层是由不同的材料制成。

16.在一些实施例中,所述低夹止电压phemt和高夹止电压phemt个别的第一栅极金属层是由相同的材料制成。

17.在一些实施例中,所述高夹止电压phemt的第一栅极金属层的厚度大于所述低夹止电压phemt的第一栅极金属层的厚度。

18.在一些实施例中,所述多层外延半导体层更包括一刻蚀终止层和一第二覆盖层,

该刻蚀终止层是形成于所述第一覆盖层上,该第二覆盖层是形成于该刻蚀终止层上,而所述低夹止电压phemt和高夹止电压phemt个别的的源极接触和漏极接触是形成于该第二覆盖层上。

19.在一些实施例中,所述刻蚀终止层包括ingap、ingaasp、inalgap和alas中的至少一者,且所述第二覆盖层包括gaas。

20.在一些实施例中,所述第一覆盖层包括gaas,所述通道层包括gaas和ingaas中的至少一者,所述缓冲层包括gaas和algaas中的至少一者,且所述化合物半导体基板包括gaas。

21.为对于本发明的特点与作用能有更深入的了解,兹藉实施例配合图式详述于后。

附图说明

22.图1为一单晶集成电路元件的一现有技术实施例的截面示意图。

23.图2为另一具有栅极沉降phemt的单晶集成电路元件的一现有技术实施例的截面示意图。

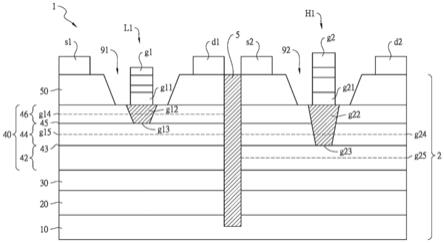

24.图3a至图3g为本发明的具有栅极沉降phemt的单晶集成电路元件的一实施例的侧视截面示意图。

25.图4a至图4c为本发明的具有栅极沉降phemt的单晶集成电路元件的一实施例的侧视截面示意图。

26.图5至图7为本发明的具有栅极沉降phemt的单晶集成电路元件的一实施例的侧视截面示意图。

27.【符号说明】

[0028]1ꢀꢀꢀꢀꢀꢀꢀ

单晶集成电路元件;

[0029]2ꢀꢀꢀꢀꢀꢀꢀ

多层结构;

[0030]5ꢀꢀꢀꢀꢀꢀꢀ

绝缘区域;

[0031]

10

ꢀꢀꢀꢀꢀꢀ

半导体基板;

[0032]

20

ꢀꢀꢀꢀꢀꢀ

缓冲层;

[0033]

30

ꢀꢀꢀꢀꢀꢀ

通道层;

[0034]

35

ꢀꢀꢀꢀꢀꢀ

载子供应层;

[0035]

40

ꢀꢀꢀꢀꢀꢀ

萧基层;

[0036]

42

ꢀꢀꢀꢀꢀꢀ

层叠区域;

[0037]

43

ꢀꢀꢀꢀꢀꢀ

层叠区域接面;

[0038]

44

ꢀꢀꢀꢀꢀꢀ

层叠区域;

[0039]

45

ꢀꢀꢀꢀꢀꢀ

层叠区域接面;

[0040]

46

ꢀꢀꢀꢀꢀꢀ

层叠区域;

[0041]

47

ꢀꢀꢀꢀꢀꢀ

层叠区域接面;

[0042]

48

ꢀꢀꢀꢀꢀꢀ

层叠区域;

[0043]

49

ꢀꢀꢀꢀꢀꢀ

最上层接触接面;

[0044]

50

ꢀꢀꢀꢀꢀꢀ

第一覆盖层;

[0045]

52

ꢀꢀꢀꢀꢀꢀ

第二覆盖层;

[0046]

60

ꢀꢀꢀꢀꢀꢀ

第一接触层;

[0047]

70

ꢀꢀꢀꢀꢀꢀ

刻蚀终止层;

[0048]

91

ꢀꢀꢀꢀꢀꢀ

栅极凹槽;

[0049]

92

ꢀꢀꢀꢀꢀꢀ

栅极凹槽;

[0050]

100

ꢀꢀꢀꢀꢀ

化合物半导体基板;

[0051]

101

ꢀꢀꢀꢀꢀ

源极电极;

[0052]

102

ꢀꢀꢀꢀꢀ

漏极电极;

[0053]

103

ꢀꢀꢀꢀꢀ

源极电极;

[0054]

104

ꢀꢀꢀꢀꢀ

漏极电极;

[0055]

108

ꢀꢀꢀꢀꢀ

栅极凹槽;

[0056]

109

ꢀꢀꢀꢀꢀ

栅极凹槽;

[0057]

110

ꢀꢀ

外延结构;

[0058]

111

ꢀꢀ

缓冲层;

[0059]

112

ꢀꢀ

通道层;

[0060]

113

ꢀꢀ

萧基层;

[0061]

114

ꢀꢀ

萧基接触层;

[0062]

115

ꢀꢀ

第一刻蚀终止层;

[0063]

116

ꢀꢀ

第一导电层;

[0064]

117

ꢀꢀ

第二刻蚀终止层;

[0065]

118

ꢀꢀ

第二导电层;

[0066]

120

ꢀꢀꢀꢀꢀ

栅极电极;

[0067]

130

ꢀꢀꢀꢀꢀ

栅极电极;

[0068]

200

ꢀꢀꢀꢀꢀ

化合物半导体基板;

[0069]

201

ꢀꢀꢀꢀꢀ

源极电极;

[0070]

202

ꢀꢀꢀꢀꢀ

漏极电极;

[0071]

203

ꢀꢀꢀꢀꢀ

源极电极;

[0072]

204

ꢀꢀꢀꢀꢀ

漏极电极;

[0073]

208

ꢀꢀꢀꢀꢀ

栅极凹槽;

[0074]

209

ꢀꢀꢀꢀꢀ

栅极凹槽;

[0075]

210

ꢀꢀꢀꢀꢀ

外延结构;

[0076]

211 缓冲层;

[0077]

212

ꢀꢀꢀꢀꢀ

通道层;

[0078]

213

ꢀꢀꢀꢀꢀ

第一萧基能障层;

[0079]

214

ꢀꢀꢀꢀꢀ

第一刻蚀终止层;

[0080]

215

ꢀꢀꢀꢀꢀ

第二萧基能障层;

[0081]

216

ꢀꢀꢀꢀꢀ

第二刻蚀终止层;

[0082]

217

ꢀꢀꢀꢀꢀ

欧姆接触层;

[0083]

220

ꢀꢀꢀꢀꢀ

栅极电极;

[0084]

221

ꢀꢀꢀꢀꢀ

栅极沉降区域;

[0085]

230

ꢀꢀꢀꢀꢀ

栅极电极;

[0086]

231

ꢀꢀꢀꢀꢀ

栅极沉降区域;

[0087]

d1

ꢀꢀꢀ

空乏型phemt;

[0088]

e1

ꢀꢀꢀ

增强型phemt;

[0089]

h1

ꢀꢀꢀ

高夹止电压phemt;

[0090]

l1

ꢀꢀꢀꢀ

低夹止电压phemt;

[0091]

d1

ꢀꢀꢀꢀ

漏极接触;

[0092]

d2

ꢀꢀꢀꢀ

漏极接触;

[0093]

g1

ꢀꢀꢀꢀ

栅极接触;

[0094]

g11

ꢀꢀꢀ

第一栅极金属层;

[0095]

g12

ꢀꢀꢀꢀꢀ

栅极沉降区域;

[0096]

g13

ꢀꢀꢀꢀꢀ

栅极沉降底边界;

[0097]

g14

ꢀꢀꢀꢀꢀ

上限;

[0098]

g15

ꢀꢀꢀꢀꢀ

下限;

[0099]

g2

ꢀꢀꢀꢀ

栅极接触;

[0100]

g21

ꢀꢀꢀꢀꢀ

第一栅极金属层;

[0101]

g22

ꢀꢀꢀꢀꢀ

栅极沉降区域;

[0102]

g23

ꢀꢀꢀꢀꢀ

栅极沉降底边界;

[0103]

g24

ꢀꢀꢀꢀꢀ

上限;

[0104]

g25

ꢀꢀꢀꢀꢀ

下限;

[0105]

s1

ꢀꢀꢀꢀ

源极接触;

[0106]

s2

ꢀꢀꢀꢀ

源极接触。

具体实施方式

[0107]

图3a为本发明一种具有栅极沉降phemt的单晶集成电路元件的一实施例的侧视截面示意图。该具有栅极沉降phemt的单晶集成电路元件1包括在一多层结构2中的一低夹止电压phemt l1和一高夹止电压phemt h1。多层结构2包括一半导体基板10,其上叠合该低夹止电压和高夹止电压phemt共用的多层外延半导体层。该多层外延半导体层包括一缓冲层20,缓冲层20上叠合一通道层30,通道层30上叠合一萧基层40,而萧基层40上叠合一第一覆盖层50。萧基层40从下到上包括三个半导体材料的层叠区域42、44、46,其中两个相邻的层叠区域的每一者与另一者的材料不同。相邻的层叠区域42、44之间设有一层叠区域接面43,而相邻的层叠区域44、46之间设有一层叠区域接面45。层叠区域接面43和45至半导体基板10的距离不同。该多层外延半导体层包括位于低夹止电压phemt l1和高夹止电压phemt h1之间的一绝缘区域5。低夹止电压phemt l1和高夹止电压phemt h1的每一者以绝缘区域5隔绝。低夹止电压phemt l1的源极接触s1和漏极接触d1耦合于第一覆盖层50。高夹止电压phemt h1的源极接触s2和漏极接触d2耦合于第一覆盖层50。低夹止电压phemt l1包括一栅极接触g1。栅极接触g1包括一第一栅极金属层g11。栅极接触g1可更包括一沉积于第一栅极金属层g11上的第二栅极金属层。一栅极沉降区域g12位于第一栅极金属层g11下方。栅极沉降区域g12具有一栅极沉降底边界g13。高夹止电压phemt h1包括一栅极接触g2。栅极接触

g2包括一第一栅极金属层g21。栅极接触g2可更包括一沉积于第一栅极金属层g21上的第二栅极金属层。一栅极沉降区域g22位于第一栅极金属层g21下方。栅极沉降区域g22具有一栅极沉降底边界g23。低夹止电压phemt l1的一栅极凹槽91位于源极电极s1和漏极电极d1之间。高夹止电压phemt h1的一栅极凹槽92位于源极电极s2和漏极电极d2之间。低夹止电压phemt l1的栅极接触g1位于栅极凹槽91之内。栅极接触g1耦合于萧基层40。高夹止电压phemt h1的栅极接触g2位于栅极凹槽92之内。栅极接触g2耦合于萧基层40。低夹止电压phemt l1和高夹止电压phemt h1个别的第一栅极金属层g11和g21与萧基层40的最上层层叠区域46接触。低夹止电压phemt的栅极沉降区域g12位于低夹止电压phemt的第一栅极金属层g11下方。高夹止电压phemt的栅极沉降区域g22位于高夹止电压phemt的第一栅极金属层g21下方。

[0108]

栅极沉降底边界g13和g23是位于萧基层40之内。高夹止电压phemt h1的栅极沉降底边界g23比低夹止电压phemt l1的栅极沉降底边界g13更接近该半导体基板10。高夹止电压phemt h1的栅极沉降底边界g23位于一上限g24和一下限g25之间。上限g24在萧基层40的层叠区域接面的一者上方处,下限g25在同一层叠区域接面下方处。在一些实施例中,高夹止电压phemt h1的栅极沉降底边界g23可位于萧基层40的层叠区域接面的一者处。在一些实施例中,低夹止电压phemt l1的栅极沉降底边界g13位于一上限g14和一下限g15之间。上限g14在萧基层40的层叠区域接面的一者上方处,下限g15在同一层叠区域接面下方处。在一些实施例中,低夹止电压phemt l1的栅极沉降底边界g13可位于萧基层40的层叠区域接面的一者处。在图3a所示的实施例中,低夹止电压phemt l1的栅极沉降底边界g13位于萧基层40的层叠区域接面45处,而高夹止电压phemt h1的栅极沉降底边界g23位于萧基层40的层叠区域接面43处。图3b至图3e显示本发明的具有栅极沉降phemt的单晶集成电路元件的其他实施例。在图3b至图3e中,上限g14和下限g15分别位于层叠区域接面45的上方和下方处,上限g24和下限g25分别位于层叠区域接面43的上方和下方处。在图3b中,低夹止电压phemt l1的栅极沉降底边界g13位于萧基层40的层叠区域接面45处,而高夹止电压phemt h1的栅极沉降底边界g23位于上限g24和萧基层40的层叠区域接面43之间。在图3c中,低夹止电压phemt l1的栅极沉降底边界g13位于萧基层40的层叠区域接面45处,而高夹止电压phemt h1的栅极沉降底边界g23位于下限g25和萧基层40的层叠区域接面43之间。在图3d中,低夹止电压phemt l1的栅极沉降底边界g13位于下限g15和萧基层40的层叠区域接面45之间,而高夹止电压phemt h1的栅极沉降底边界g23位于下限g25和萧基层40的层叠区域接面43之间。在图3e中,低夹止电压phemt l1的栅极沉降底边界g13位于上限g14和萧基层40的层叠区域接面45之间,而高夹止电压phemt h1的栅极沉降底边界g23位于下限g25和萧基层40的层叠区域接面43之间。

[0109]

在一些实施例中,萧基层40的任两个相邻的层叠区域中,由algaas为基底的半导体材料构成的层叠区域与由ingap为基底的半导体材料构成的另一层叠区域交替层叠,其中所述algaas为基底的半导体材料包括algaas、algaasp和inalgaas中的至少一者,而所述ingap为基底的半导体材料包括ingap、ingapas和alingap中的至少一者。

[0110]

在本发明中,萧基层可包括三个以上半导体材料的层叠区域,其中两个相邻的层叠区域的每一者与另一者的材料不同,且两者之间设有一层叠区域接面,该层叠区域接面

的任两者至该半导体基板的距离不同。图3f和图3g显示本发明的具有栅极沉降phemt的单晶集成电路元件的其他实施例,其中萧基层40从下到上包括四个半导体材料的层叠区域42、44、46、48。层叠区域接面43、45、47分别设于层叠区域之间。如图3f所示,低夹止电压phemt l1的栅极沉降底边界g13位于萧基层40的层叠区域接面47处,而高夹止电压phemt h1的栅极沉降底边界g23位于萧基层40的层叠区域接面43处。在图3g中,上限g14和下限g15分别位于层叠区域接面45的上方和下方处。上限g24和下限g25分别位于层叠区域接面43的上方和下方处。低夹止电压phemt l1的栅极沉降底边界g13位于下限g15和萧基层40的层叠区域接面45之间,而高夹止电压phemt h1的栅极沉降底边界g23位于下限g25和萧基层40的层叠区域接面43之间。

[0111]

图4a至图4c显示本发明的具有栅极沉降phemt的单晶集成电路元件的其他实施例。在图4a和图4b中,萧基层40从下到上包括三个半导体材料的层叠区域42、44、46,且层叠区域接面43、45分别设于层叠区域之间。如前所述,萧基层可包括三个以上半导体材料的层叠区域。在图4c中,萧基层40从下到上包括四个半导体材料的层叠区域42、44、46、48。层叠区域接面43、45、47分别设于层叠区域之间。在图4a至图4c中,多层外延半导体层更包括一第一接触层60,其与萧基层的最上层层叠区域的一上表面接触。第一接触层60与萧基层40的该最上层层叠区域之间设有一最上层接触接面49。第一覆盖层50是形成于第一接触层60上。低夹止电压phemt l1和该高夹止电压phemt h1个别的第一栅极金属g11和g21层与第一接触层60接触。低夹止电压phemt l1的栅极沉降底边界g13位于一上限g14和一下限g15之间。上限g14在最上层接触接面49上方处或在萧基层40的层叠区域接面的一者上方处,下限g15在同一接面(最上层接触接面或层叠区域接面)下方处。高夹止电压phemt h1的栅极沉降底边界g23位于一上限g24和一下限g25之间。上限g24在萧基层40的层叠区域接面的一者上方处,下限g25在同一层叠区域接面下方处。如图4a所示,低夹止电压phemt l1的栅极沉降底边界g13位于萧基层40的层叠区域接面45处,而高夹止电压phemt h1的栅极沉降底边界g23位于萧基层40的层叠区域接面43处。在图4b中,低夹止电压phemt l1的栅极沉降底边界g13位于最上层接触接面49处,而高夹止电压phemt h1的栅极沉降底边界g23位于萧基层40的层叠区域接面43处。在图4c中,低夹止电压phemt l1的栅极沉降底边界g13位于最上层接触接面49处,而高夹止电压phemt h1的栅极沉降底边界g23位于萧基层40的层叠区域接面43处。

[0112]

在一些实施例中,第一接触层60包括gaas、algaas、algaasp、inalgaas、ingap、ingaasp和inalgap中的至少一者,且第一接触层60与萧基层40的该最上层层叠区域的材料不同。

[0113]

在一些实施例中,低夹止电压phemt和该高夹止电压phemt个别的第一栅极金属层包括钼(mo)、钨(w)、硅化钨(wsi)、钛(ti)、铱(ir)、钯(pd)、铂(pt)、镍(ni)、钴(co)、铬(cr)、钌(ru)、锇(os)、铑(rh)、钽(ta)、氮化钽(tan)、铝(al)和铼(re)中的至少一者。在一些实施例中,低夹止电压phemt和高夹止电压phemt个别的第一栅极金属层是由不同的材料制成。在一些实施例中,低夹止电压phemt和高夹止电压phemt个别的第一栅极金属层是由相同的材料制成。在一些实施例中,高夹止电压phemt的第一栅极金属层的厚度大于低夹止电压phemt的第一栅极金属层的厚度。

[0114]

图5显示本发明的具有栅极沉降phemt的单晶集成电路元件的另一个实施例。在此实施例中,多层外延半导体层更包括一刻蚀终止层70和一第二覆盖层52。刻蚀终止层70是形成于第一覆盖层50上,第二覆盖层52是形成于刻蚀终止层70上。低夹止电压phemt l1和高夹止电压phemt h1个别的源极接触s1、s2和漏极接触d1、d2耦合于第二覆盖层52。

[0115]

在一些实施例中,刻蚀终止层70包括ingap、ingaasp、inalgap和alas中的至少一者,且第二覆盖层52包括gaas。在一些实施例中,第一覆盖层50包括gaas。在一些实施例中,通道层30包括gaas和ingaas中的至少一者。在一些实施例中,缓冲层20包括gaas和algaas中的至少一者。在一些实施例中,化合物半导体基板10包括gaas。

[0116]

图6显示本发明的具有栅极沉降phemt的单晶集成电路元件的另一个实施例。在此实施例中,多层外延半导体层更包括一载子供应层35。载子供应层35是形成于通道层30上,且萧基层40是形成于载子供应层35上。载子供应层35包括algaas、algaasp和inalgaas中的至少一者。

[0117]

图7显示本发明的具有栅极沉降phemt的单晶集成电路元件的另一个实施例。在此实施例中,萧基层40从下到上包括四个半导体材料的层叠区域42、44、46、48,层叠区域接面43、45、47分别设于层叠区域之间。低夹止电压phemt l1和高夹止电压phemt h1共用一对源极接触s1和漏极接触d1。低夹止电压phemt l1包括一栅极接触g1。栅极接触g1包括一第一栅极金属层g11、一栅极沉降区域g12和一栅极沉降底边界g13。高夹止电压phemt h1包括一栅极接触g2。栅极接触g2包括一第一栅极金属层g21、一栅极沉降区域g22和一栅极沉降底边界g23。低夹止电压phemt l1和高夹止电压phemt h1个别的栅极凹槽91和92位于源极电极s1和漏极电极d1之间。耦合于萧基层40的低夹止电压phemt l1的栅极接触g1位于栅极凹槽91之内。耦合于萧基层40的高夹止电压phemt h1的栅极接触g2位于栅极凹槽92之内。低夹止电压phemt l1和高夹止电压phemt h1个别的第一栅极金属层g11和g21与萧基层40的最上层层叠区域48接触。低夹止电压phemt的栅极沉降区域g12位于低夹止电压phemt的第一栅极金属层g11下方。高夹止电压phemt的栅极沉降区域g22位于高夹止电压phemt的第一栅极金属层g21下方。在图7中,上限g14和下限g15分别位于层叠区域接面47的上方和下方处,上限g24和下限g25分别位于层叠区域接面43的上方和下方处。低夹止电压phemt l1的栅极沉降底边界g13位于萧基层40的层叠区域接面47处,而高夹止电压phemt h1的栅极沉降底边界g23位于萧基层40的层叠区域接面43处。

[0118]

因此,单晶集成电路元件中每个phemt的夹止电压和栅极

‑

通道间距离的均一性能被显著地提升。再者,单晶集成电路元件中每个phemt的夹止电压可设计为任何(正或负)想要的值。此外并能简化工艺以及提升经济效益。

[0119]

虽然本发明的实施例已经详细描述,本领域的技术人员可从上述教示做出更多修改及变更。因此,应理解为等同于本发明的精神的任何修改及变更应视为落入所附权利要求所定义的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1