一种摄像头芯片的SiP封装设计方法与流程

一种摄像头芯片的sip封装设计方法

技术领域

1.本发明涉及半导体封装技术领域,特别涉及一种摄像头芯片的sip封装设计方法。

背景技术:

2.集成电路在应用角度上可分为专用集成电路和通用集成电路,即专用芯片和通用芯片。专用芯片具有可靠性高、性能好和功能利用率高等特点,通用芯片具有通用性强、移植性高和扩展性好等特点。

3.随着电子工程的发展,从最开始单一组件的开发,逐渐进入到了集结多个组件开发成为一个系统的阶段。在产品高效能及外观轻薄的要求下,不同功能的芯片开始迈向整合的阶段。在此期间,封装技术的不断发展和突破,成为推动整合的力量之一,sip的概念随即被提出。sip作为一种封装技术是指通过将多芯片die集中于一个单一封装内,从而使芯片获得系统功能。

4.目前市场上摄像头产品内部电子器件主要包括图像传感器芯片,主控芯片,内存芯片,存储芯片,网络传输芯片等。其中图像传感器芯片主要是作为视频图像采集功能,主控芯片主要承担图像和视频的压缩处理功能,内存芯片是作为系统软件运行的载体,存储芯片保存系统运行的代码程序,网络传输芯片是将主控压缩后的视频图像传输到后端服务器或者云端。

5.随着sip封装技术的发展,目前摄像头主芯片普遍已经将主控芯片die和内存芯片die合封在一个封装体内,但随着产品轻薄化,外扩功能多样化等发展需要,产品单板pcb肯定会更复杂化,设计及生产成本势必跟着增长。因此,提供一种sip封装设计方案,将图像传感器die,主控芯片die以及内存芯片die sip在一个封装体内形成一个芯片,势必更加简化摄像头产品的设计,降低生产成本,使得在市场推广中有更高性价比,更有竞争力。

6.现有技术中的常用技术术语包括:

7.sip封装(system in a package系统级封装)是将多种功能晶圆,包括处理器、存储器等功能晶圆根据应用场景、封装基板层数等因素,集成在一个封装内,从而实现一个基本完整功能的封装方案。

8.die(晶粒),裸片;是硅片中一个很小的单位,包括了设计完整的单个芯片以及芯片邻近水平和垂直方向上的部分划片槽区域。wafer上的一个小块,就是一个晶片晶圆体,学名die,封装后就成为一个颗粒。晶粒是组成多晶体的外形不规则的小晶体,而每个晶粒有时又有若干个位向稍有差异的亚晶粒所组成。晶粒的平均直径通常在0.015~0.25mm范围内,而亚晶粒的平均直径通常为0.001mm数量级。

9.cis(cmos image sensor),即cmos(compound metal oxided semiconductor)工艺图像传感器,中文名复合金属氧化物半导体工艺图像传感器。

10.键合线:半导体封装用的核心材料,是连接引脚和硅片、传达电信号的零件,半导体生产中不可或缺的核心材料。只有1/4忽米直径的超丝线,生产键合线需要高强度超精密和耐高温的技术能力。

11.打线,也叫wire bonding(压焊,也称为绑定,键合,丝焊),是指使用金属丝(金线、铝线等),利用热压或超声能源,完成微电子器件中固态电路内部互连接线的连接,即芯片与电路或引线框架之间的连接。常见于表面封装工艺,如cob工艺。

12.mipi(移动产业处理器接口)是mipi联盟发起的为移动应用处理器制定的开放标准和一个规范。mipi是差分串口传输,速度快,抗干扰。dvp(digital video port)是传统的sensor输出接口,采用并行输出方式,d数据位宽有8bit、10bit、12bit、16bit,是cmos电平信号(重点是非差分信号),pclk最大速率为96mhz;dvp是并口传输,速度较慢,传输的带宽低。

13.电源地,主要是针对电源回路电流所走的路径而言的,一般来说电源地流过的电流较大,而信号地主要是针对两块芯片或者模块之间的通信信号的回流所流过的路径,一般来说信号地流过的电流很小。

技术实现要素:

14.为了解决上述问题,本方法目的在于:充分将图像传感器die,主控芯片die,内存芯片die合封在一个封装体内形成一个芯片,简化后续摄像头产品的单板设计,降低产品生产成本。

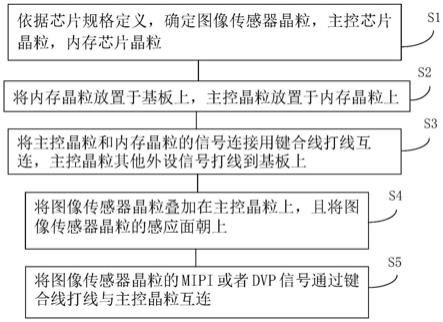

15.具体地,本发明提供一种摄像头芯片sip封装设计方法,所述方法包括以下步骤:

16.s1,依据芯片规格定义,确定图像传感器晶粒,主控芯片晶粒,内存芯片晶粒;

17.s2,将内存晶粒放置于基板上,主控晶粒放置于内存晶粒上;

18.s3,将主控晶粒和内存晶粒的信号连接用键合线打线互连,主控晶粒其他外设信号打线到基板上;

19.s4,将图像传感器晶粒叠加在主控晶粒上,且将图像传感器晶粒的感应面朝上;

20.s5,将图像传感器晶粒的mipi或者dvp信号通过键合线打线与主控晶粒互连。

21.所述封装基板可用框架代替,所述封装基板或框架是sip封装里面各晶圆晶粒的载体。

22.所述主控晶粒、内存晶粒以及图像传感器晶粒相关其他信号通过键合线打线到封装基板上,再连接到焊球或焊脚上,形成芯片封装。

23.所述的主控芯片晶粒承担图像和视频的压缩处理功能。

24.所述内存芯片晶粒是作为系统软件运行的载体,与主控之间通过ddr总线协议交互信息;所述键合线是sip封装内各个晶粒相互连接以及各晶粒到基板的物理实体导线。

25.所述步骤s3中,所述主控晶粒和内存晶粒通过键合线打线的信号,有ddr总线,包括数据,地址,命令信号。

26.所述步骤s5中,所述图像传感器晶粒和主控晶粒需要通过键合线打线的信号,为mipi-csi或者dvp信号,时钟信号,i2c信号及控制信号;所述的图像传感器芯片晶粒承担视频图像采集功能与主控连接,接口包括mipi-csi和dvp两种。

27.所述步骤s3中主控晶粒的电源地及其他外设信号焊点通过键合线直接打线到基板上。

28.其他外设信号包括存储器信号,网络传输信号。

29.所述的图像传感器晶粒工作所需的电源地焊点,通过键合线直接打线到基板或者

csi或者dvp信号,时钟信号,i2c信号及相关控制信号;

49.进一步,主控die 2的电源地及其他外设信号焊点(如存储器信号,网络传输信号等)通过键合线直接打线到基板5上,具体打线实现方式不是本发明所要体现的关键信息,不详细赘述;

50.进一步,图像传感器die 1工作所需的电源地等焊点,通过键合线直接打线到基板或者框架5上,具体打线实现方式不是本发明所要体现的关键信息,不详细赘述;

51.进一步,内存die 4工作所需的电源地等焊点,通过键合线直接打线到基板或者框架5上,具体打线实现方式不是本发明所要体现的关键信息,不详细赘述;

52.进一步,图像传感器die 1的感应面7堆叠在主控die 2时要朝上堆叠,以便工厂塑封时留出感应窗口,这样应用时才能通过感应面采集到图像信息,如图2所示。

53.通过上述本发明的sip方案,经封装工厂加工后,就可以得到一颗包含图像传感器,内存芯片和主控芯片三合一的高度集成的sip芯片,如图3所示。

54.如图4所示,首先,从确定cis规格和内存规格;其次,选定cis die和内存die;再次,内存die放置基板上;第四,主控die叠加放置于内存die上;最后,cis die感应面朝上叠加放置于主控die上。

55.对于后端摄像头产品来说,采用本发明sip封装方案的芯片,将更加简化产品设计复杂度,免去再贴合传感器芯片,从而降低了产品的生产成本。

56.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明实施例可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1