电子封装件及其线路结构的制作方法

1.本发明有关一种半导体封装制程,尤指一种可提升可靠度的电子封装件及其线路结构。

背景技术:

2.随着电子产业的蓬勃发展,电子产品也逐渐迈向多功能、高性能的趋势。为了满足半导体封装件微型化(miniaturization)的封装需求,发展出晶圆级封装(wafer level packaging,简称wlp)的技术。

3.图1a至图1d为现有晶圆级半导体封装件1的制法的剖面示意图。

4.如图1a所示,形成一热化离型胶层(thermal release tape)11于一承载件10上。

5.接着,置放多个半导体元件12于该热化离型胶层11上,该些半导体元件12具有相对的作用面12a与非作用面12b,各该作用面12a上均具有多个电极垫120,且各该作用面12a粘着于该热化离型胶层11上。

6.如图1b所示,形成一封装胶体13于该热化离型胶层11上,以包覆该半导体元件12。

7.如图1c所示,进行烘烤制程以硬化该封装胶体13,而同时该热化离型胶层11因受热后会失去粘性,故可一并移除该热化离型胶层11与该承载件10,以外露该半导体元件12的作用面12a。

8.如图1d所示,进行线路重布层(redistribution layer,简称rdl)制程,以形成一包含有介电层140及线路层141的线路重布结构14于该封装胶体13与该半导体元件12的作用面12a上,且令该线路重布结构14电性连接该半导体元件12的电极垫120,其中,为了提升散热功效,该线路重布结构14的表面上布设有大面积的图案化金属层141’,且该图案化金属层141’也可供该半导体芯片21作接地或传递电源之用。接着,形成一绝缘保护层15于该线路重布结构14上,且该绝缘保护层15外露该线路重布结构14的部分表面,以供结合如焊球的导电元件16。最后进行切单制程。

9.然而,现有半导体封装件1中,该金属层141’所占面积比例过多,且该线路重布结构14的线路层141的结构强度太弱,致使该线路重布结构14的应力分布容易不均,造成该线路重布结构14的各层介电层140平整度不一致,故该半导体封装件1容易发生翘曲,导致该线路层141无法有效电性连接该些半导体元件12的电极垫120,致使电性不良,进而造成良率过低及产品可靠度不佳等问题。

10.因此,如何克服上述现有技术的种种问题,实已成目前亟欲解决的课题。

技术实现要素:

11.鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件及其线路结构,以减少应力集中,避免该电子封装件发生翘曲。

12.本发明的线路结构包括:多个介电层;多个线路层,其设于该多个介电层上;至少一第一金属层,其设于该多个介电层的其中一者上且具有多个第一开口;以及至少一第二

金属层,其设于该多个介电层的其它至少一者上且具有多个第二开口,以令该第一金属层及第二金属层位于不同的介电层上,其中,该第一开口的位置未对齐该第二开口的位置。

13.前述的线路结构中,该第一开口及/或第二开口为矩形。

14.前述的线路结构中,该第一金属层及第二金属层为虚铜片。

15.前述的线路结构中,该第一金属层及第二金属层为线路层。

16.前述的线路结构中,第二金属层具有多个个,并设于该多个介电层的未设有第一金属层的全部,且令位于不同介电层上的二该第二金属层的第二开口的位置为未相互对齐。

17.本发明还提供一种电子封装件,包括:包覆层,其具有相对的第一侧与第二侧;至少一电子元件,其嵌埋于该包覆层中;以及如前述的线路结构,其设于该包覆层的第一侧上,且该线路层电性连接该电子元件。

18.前述的电子封装件中,该电子元件外露于该包覆层的第二侧。

19.前述的电子封装件中,该第一金属层及/或第二金属层未电性连接该电子元件。

20.前述的电子封装件中,该第一金属层及/或第二金属层电性连接该电子元件。

21.前述的电子封装件中,还包括埋设于该包覆层中且电性连接该线路层的多个导电柱。

22.前述的电子封装件中,还包括形成于该线路结构上且电性连接该线路层的多个导电元件。

23.由上可知,本发明的电子封装件及其线路结构中,主要经由于该介电层上形成具有开口的金属层,以降低该金属层所占该介电层的面积比例,因而能分散应力的分布,故相比于现有技术,本发明能避免该线路结构发生翘曲,也就是避免该电子封装件翘曲,令该线路层能有效电性连接该电子元件,进而提升产品良率及产品可靠度。

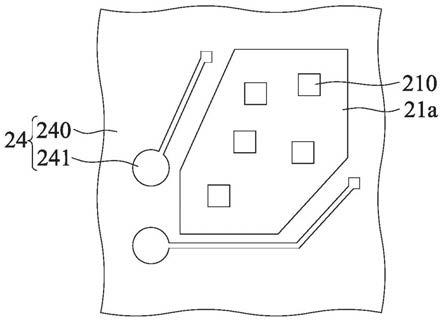

24.此外,经由各金属层的开口位置并未对齐,以避免该线路结构发生应力集中的问题,因而能增加该介电层的平整性,故相比于现有技术,本发明更能避免该电子封装件或该线路结构发生翘曲。

附图说明

25.图1a至图1d为现有半导体封装件的制法的剖面示意图。

26.图2a至图2d为本发明的电子封装件的制法的剖面示意图。

27.图2b’为图2b的局部上视图。

28.图2e为图2d的后续制程的剖面示意图。

29.图3a、图3b、图3c及图3d为图2d的不同态样的局部上视示意图。

30.附图标记说明

31.1:半导体封装件

32.10,9:承载件

33.11:热化离型胶层

34.12:半导体元件

35.12a,20a:作用面

36.12b,20b:非作用面

37.120,200:电极垫

38.13:封装胶体

39.14:线路重布结构

40.140,240,250:介电层

41.141,241,251,251’:线路层

42.141’:金属层

43.15,253:绝缘保护层

44.16,26:导电元件

45.2:电子封装件

46.2a:线路结构

47.20:电子元件

48.21a:第一金属层

49.21b,21c:第二金属层

50.210:第一开口

51.210’,210”:第二开口

52.22:导电柱

53.23:包覆层

54.23a:第一侧

55.23b:第二侧

56.24:线路部

57.25:增层部

58.252:导电盲孔

59.26:导电元件

60.260:凸块底下金属层

61.3:电子装置

62.90:离形层

63.91:结合层

64.s:切割路径。

具体实施方式

65.以下经由特定的具体实施例说明本发明的实施方式,本领域技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。

66.须知,本说明书附图所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供本领域技术人员的了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本发明可实施的范畴。

67.图2a至图2d为本发明的电子封装件2的制法的剖面示意图。

68.如图2a所示,提供一具有相对的第一侧23a与第二侧23b的包覆层23,且该包覆层23中嵌埋有至少一电子元件20及多个导电柱22。

69.于本实施例中,形成该包覆层23的材料为绝缘材,如模封材(molding compound)、干膜(dry film)、聚对二唑苯(poly-p-polybenzoxazole,简称pbo)、聚酰亚胺(polyimide,简称pi)、预浸材(prepreg,简称pp)、ajinomoto build-up film(abf)、环氧树脂(epoxy)或光阻材。

70.此外,该电子元件20为主动元件、被动元件或其组合者,其中,该主动元件为半导体芯片,而该被动元件为电阻、电容及电感。例如,该电子元件20为半导体芯片,如电源管理芯片、动态随机存取存储器、应用处理器等,其具有相对的作用面20a与非作用面20b,该作用面20a具有多个电极垫200,且该电子元件20的非作用面20b齐平该包覆层23的第二侧23b。可理解地,于其它实施例中,该包覆层23的第二侧23b可覆盖该电子元件20的非作用面20b。

71.另外,该包覆层23与该电子元件20的制作方式繁多,例如,该包覆层23以铸模成型(molding)或压合(laminate)方式形成者,但并不限于此方式。具体地,可先将该电子元件20与该些导电柱22设于支撑件(图略)上,再形成用以包覆该电子元件20与该些导电柱22的包覆层23,之后将该包覆层23的第二侧23b结合于一承载件9上,才移除该支撑件。或者,先将该些导电柱22与该电子元件20以其非作用面20b设于该承载件9上,再形成用以包覆该电子元件20与该些导电柱22的包覆层23。

72.另外,形成该导电柱22的材料为如铜的金属材或焊锡材,且该承载件9上可依序形成有一离形层90与一结合层91,使该包覆层23的第二侧23b与该电子元件20的非作用面20b结合于该结合层91上。具体地,该离形层90例如为热化离型胶(thermal release tape)、光感离形膜或机械离形构造,且该结合层91如粘着材。

73.如图2b所示,进行线路重布层(redistribution layer,简称rdl)制程,以形成一线路部24于该包覆层23的第一侧23a上,且该线路部24电性连接该电子元件20与该些导电柱22,并形成一第一金属层21a于该线路部24上。

74.于本实施例中,该线路部24包含至少一介电层240及设于该介电层240的线路区上的线路层241,且该线路层241电性连接该电子元件20的电极垫200与该些导电柱22。

75.此外,该第一金属层21a设于该介电层240的非线路区上,且该第一金属层21a与该线路层241可一同制作;或者,该第一金属层21a与该线路层241可采用不同制程制作。因此,该第一金属层21a的材料与该线路层241的材料可相同(如铜材)或不相同。

76.另外,该第一金属层21a为网状体(mesh),其具有多个第一开口210,如图2b’所示。应可理解地,该第一开口210的轮廓与数量不限于图中所示的矩形(如正方形或如图3b所示的长方形),也可为其它数量或其它形状的轮廓。

77.如图2c所示,进行另一线路重布层(rdl)制程,以形成一增层部25于该线路部24与该第一金属层21a上,以令该增层部25与该线路部24作为线路结构2a,且形成至少一第二金属层21b,21c于该增层部25上。之后,形成多个导电元件26于该增层部25上。

78.于本实施例中,该增层部25具有至少一结合该第二金属层21b,21c的介电层250、形成于该些介电层250上的线路层251,251’、及设于该些介电层250中的多个导电盲孔252,

且经由该些导电盲孔252电性连接该些线路层241,251,而该增层部25的最外侧介电层250与线路层251’形成有一绝缘保护层253,以令该最外侧的部分线路层251’外露于该绝缘保护层253,以供结合该些导电元件26于该线路层251’上。

79.此外,该第二金属层21b,21c设于该介电层250的非线路区上,且该第二金属层21b,21c与该线路层251,251’可一同制作;或者,该第二金属层21b,21c与该线路层251,251’可采用不同制程制作。因此,该第二金属层21b,21c的材料与该线路层251的材料可相同(如铜材)或不相同。

80.请同时配合参阅图3a至图3d,该第二金属层21b,21c为网状体(mesh),其具有多个第二开口210’,210”,以令该线路层251沿该第二金属层21b,21c的边缘间隔布设。应可理解地,该第二开口210’,210”的轮廓与数量不限于图中所示的矩形(如正方形或长方形),也可为其它数量或其它形状的轮廓。较佳者,相邻两层(即上下两层)的金属层的开口位置并未对齐,如图3a、图3b、图3c及图3d所示的相互错位。

81.另外,该导电元件26为焊球、金属凸块或金属针等,且于形成该导电元件26前,可先于该线路层251’上形成凸块底下金属层(under bump metallurgy,简称ubm)260,以利于结合该导电元件26。

82.如图2d所示,移除该承载板9、离形层90及该结合层91,使该电子元件20的非作用面20b外露于该包覆层23的第二侧23b。之后,沿如图2c所示的切割路径s进行切单制程,以完成该电子封装件2的制作。

83.于本实施例中,该第一金属层21a及第二金属层21b,21c作为虚铜片(dummy cu),其未电性连接该电子元件20;或者,该第一金属层21a及第二金属层21b,21c可依需求作为线路层,其电性连接该电子元件20的部分电极垫210,以供该电子元件20作散热、接地及/或传递电源之用。

84.此外,于后续制程中,该电子封装件2可经由该些导电元件26结合至一如电路板的电子装置3上,如图2e所示。

85.本发明的电子封装件2的线路结构2a主要经由该第一金属层21a及第二金属层21b,21c具有多个第一开口210及第二开口

86.210’,210”,以降低其所占该介电层240,250的面积比例,因而能减少应力集中,故相比于现有技术,本发明能避免该线路结构2a发生翘曲,也就是避免该电子封装件2翘曲,令该线路层241能有效电性连接该电子元件20,进而提升产品良率及产品的可靠度。

87.此外,经由任两层或相邻两层(即上下两层)的金属层的开口位置并未对齐,如图3a、图3b、图3c及图3d所示的相互错位,以减少该线路结构2a发生应力集中的问题,因而能增加该介电层240,250的平整性,避免该电子封装件2或该线路结构2a发生翘曲。

88.本发明提供一种线路结构2a,包括:多个介电层240,250、设于该多个介电层240,250上的多个线路层241,251,251’、至少一第一金属层21a以及至少一第二金属层21b,21c。

89.所述的第一金属层21a设于该多个介电层240的其中一者上且具有多个第一开口210。

90.所述的第二金属层21b,21c设于该多个介电层250的其它至少一者上且具有多个第二开口210’,210”(该第一金属层21a及第二金属层21b,21c位于不同层),其中,该第一开口210的位置未对齐该第二开口210’,210”的位置。

91.于一实施例中,该第一开口210及/或第二开口210’,210”为矩形。

92.于一实施例中,该第一金属层21a及第二金属层21b,21c为虚铜片。

93.于一实施例中,该第一金属层21a及第二金属层21b,21c为线路层。

94.于一实施例中,多个第二金属层21b,21c设于未设有第一金属层21a的该多个介电层250的全部,且令位于不同介电层250上的二该第二金属层21b,21c的该第二开口210’,210”的位置未相互对齐。

95.本发明还提供一种电子封装件2,包括:一包覆层23、至少一电子元件20以及该线路结构2a。

96.所述的包覆层23具有相对的第一侧23a与第二侧23b。

97.所述的电子元件20嵌埋于该包覆层23中。

98.所述的线路结构2a设于该包覆层23的第一侧23a上,且该线路层241电性连接该电子元件20。

99.于一实施例中,该电子元件20外露于该包覆层23的第二侧23b。

100.于一实施例中,该第一金属层21a及/或第二金属层21b,21c未电性连接该电子元件20。

101.于一实施例中,该第一金属层21a及/或第二金属层21b,21c电性连接该电子元件20。

102.于一实施例中,该电子封装件2还包括埋设于该包覆层23中且电性连接该线路层241的多个导电柱22。

103.于一实施例中,该电子封装件2还包括形成于该线路结构2a上且电性连接该线路层251’的多个导电元件26。

104.综上所述,本发明的电子封装件及其线路结构,主要经由网状体金属层的设计,以降低其所占该介电层的面积比例,因而能减少应力集中,故本发明能避免该线路结构发生翘曲,也就是避免该电子封装件翘曲,令该线路层能有效电性连接该电子元件,进而提升产品良率及产品的可靠度。

105.此外,经由各金属层的开口位置并未对齐,以减少该线路结构发生应力集中的问题,增加该介电层的平整性,避免该电子封装件或该线路结构发生翘曲。

106.上述实施例仅用以例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修改。因此本发明的权利保护范围,应如权利要求书所列。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1