动态随机存取存储器电容器及其制备方法与流程

1.本发明属于半导体元件领域,具体涉及一种动态随机存取存储器电容器及其制备方法。

背景技术:

2.随着电子工业向多功能化发展,电子器件的集成化、小型化和高性能化已经成为一种趋势。对于dram电容器来说,其中的介电材料层也越来越薄,不仅工艺制程越来越难达到,还会导致介电损耗也越来越高。

3.提供一种具有高介电常数和低介电损耗的dram电容器介电层成为亟待解决的问题。

技术实现要素:

4.为了解决上述问题,本发明提供一种dram电容器及其制备方法。

5.本发明一方面提供一种动态随机存取存储器电容器,包括介电层,所述介电层包括:高介电材料层;和低介电损耗材料层,设置在所述高介电材料层两侧表面。

6.根据本发明的一实施方式,所述介电层包括一层以上的所述高介电材料层。

7.根据本发明的另一实施方式,所述高介电材料层与所述低介电损耗材料层的厚度比为200-100:1,所述低介电损耗材料层的厚度为0.34nm-10nm。

8.根据本发明的另一实施方式,所述高介电材料层包括掺杂的介电陶瓷材料,所述掺杂的介电陶瓷材料为ag、in、sb、bi、ta、la、nd、ce中一种或多种金属掺杂的hfo2、tio2、zro2、ceo2中一种或多种介电陶瓷材料。

9.根据本发明的另一实施方式,以所述掺杂的介电陶瓷材料的总重量计,所述ag、in、sb、bi、ta、la、nd、ce中一种或多种金属掺杂的掺杂重量含量为1.5%-3.5%。

10.根据本发明的另一实施方式,所述低介电损耗材料层包括聚酰亚胺、聚偏氟乙烯、环氧树脂、聚苯乙烯、氧化石墨烯中的一种或多种。

11.本发明另一方面提供一种动态随机存取存储器电容器的制备方法,包括:s1,形成低介电损耗材料层;s2,在所述低介电损耗材料层上形成高介电材料层;s3,在所述高介电材料层上形成低介电损耗材料层。

12.根据本发明的一实施方式,依次重复所述s2、s3步骤至少一次。

13.根据本发明的另一实施方式,所述高介电材料层包括掺杂的介电陶瓷材料,通过原子层沉积所述掺杂的介电陶瓷材料形成所述高介电材料层。

14.根据本发明的另一实施方式,所述掺杂的介电陶瓷材料为ag、in、sb、bi、ta、la、nd、ce中一种或多种金属掺杂的hfo2、tio2、zro2、ceo2中一种或多种介电陶瓷材料。

15.本发明的dram电容器的介电层包括高介电材料层和设置在高介电材料层两侧表面的低介电损耗材料层,高介电材料层可以提高介电层的介电常数,使其具有更好的介电性能;两侧表面设置的低介电损耗材料层可以有效解决高介电材料层的介电损耗,从而实

现介电层的高介电常数和低介电损耗的目的。本发明的dram电容器制程简单,便于工业化生产。

附图说明

16.通过参照附图详细描述其示例实施方式,本发明的上述和其它特征及优点将变得更加明显。

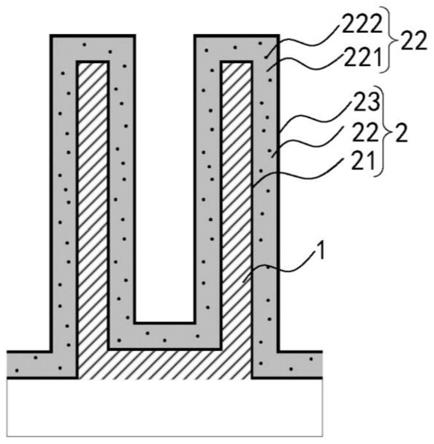

17.图1a是本发明一实施方式的dram电容器的局部剖面示意图。

18.图1b是图1a中dram电容器的介电层的局部放大示意图。

19.图2a本发明另一实施方式的dram电容器的局部剖面示意图。

20.图2b是图2a中dram电容器的介电层的局部放大示意图。

21.其中,附图标记说明如下:

22.1:第一电容器电极

23.2:介电层

24.21,21a,21b:第一低介电损耗材料层

25.22:掺杂的介电陶瓷材料层

26.221,221a,221b:介电陶瓷材料粒子

27.222,222a,222b:掺杂粒子

28.23:第二低介电损耗材料层

具体实施方式

29.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式;相反,提供这些实施方式使得本发明将全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。在图中,为了清晰,夸大了区域和层的厚度。在图中相同的附图标记表示相同或类似的结构,因而将省略它们的详细描述。

30.本文中术语“高介电常数材料是指介电常数高于4的材料;术语“低介电损耗材料”是指介电损耗低于0.2的材料。

31.本发明的动态随机存取存储器电容器,包括介电层,其中介电层包括高介电材料层和设置在高介电材料层两侧表面的低介电损耗材料层。高介电材料可以提高介电层的介电常数,使其具有更好的介电性能。两侧表面设置的低介电损耗材料层可以有效解决高介电材料层的介电损耗,从而实现介电层的高介电常数和低介电损耗的目的。

32.在可选的实施方式中,如图1a所示,介电层2包括一层高介电材料层22和设置在内侧的、与dram电容器的第一电容器电极1表面的第一低介电损耗材料层21和设置在外侧的第二低介电损耗材料层23。

33.在可选的实施方式中,如图2a所示,介电层2包括两层高介电材料层22,即高介电材料层22a和22b。也就是说,高介电材料层22a、22b与低介电损耗材料层21a、21b、23交替排列。

34.以上两种方式仅是列举,介电层还可以是更多层的堆叠,例如包含3层高介电材料层和4层低介电损耗材料层的堆叠、或者包含4层高介电材料层和5层低介电损耗材料层的

堆叠等等。

35.在可选的实施方式中,高介电材料层与低介电损耗材料层的厚度比为200-100:1。根据电容串联的相关公式,可知高介电材料层的厚度与低介电损耗材料层的厚度比越大,介电层的介电常数越接近高介电材料层的介电常数,因此为了发挥高介电材料层的高介电常数性能,趋向于选择更大的厚度比。但同时考虑工艺可行性和介电层的总体厚度,优选高介电材料层与低介电损耗材料层的厚度比为200-100:1。本领域技术人员可以根据具体的需要选择其中的任何数值,例如190:1、180:1、170:1、160:1、150:1、140:1、130:1、120:1、110:1等等。低介电损耗材料层的厚度可以是0.34nm-10nm。当低介电损耗材料层为氧化石墨烯层时,可以采用单层氧化石墨烯作为低介电损耗材料层,单层氧化石墨烯层的厚度为0.34nm。综合考虑电容器的性能、工艺可行性、材料的种类和成本等因素,选择适当的低介电损耗材料层的厚度,例如但不限于为1nm、2nm、3nm、4nm、5nm、6nm、7nm、8nm、9nm、10nm等等。

36.在可选的实施方式中,高介电材料层可以但不限于,由掺杂的介电陶瓷材料形成。掺杂的介电陶瓷材料可以是ag、in、sb、bi、ta、la、nd、ce中一种或多种金属掺杂的hfo2、tio2、zro2、ceo2中一种或多种介电陶瓷材料。以掺杂的介电陶瓷材料层的总重量计,掺杂量在1.5%-3.5%之间时,介电常数可以达到最大。因此,本领域技术人员可以根据实际的需要,在1.5%-3.5%之间选择适当的数值,例如但不限于1.8%、2%、2.3%、2.5%、2.8%、3%等等。

37.低介电损耗材料层可以是由低介电损耗绝缘材料形成,例如聚合物、氧化石墨烯等。聚合物可以选自聚酰亚胺、聚偏氟乙烯、环氧树脂、聚苯乙烯中的一种或多种形成。

38.以下结合附图,以掺杂的介电陶瓷材料为高介电材料层为例解释本发明的发明构思。但本领域技术人员应当理解,高介电材料不并意在仅限定为掺杂的介电陶瓷材料。

39.参照图1b,高介电材料层22由于介电陶瓷材料221中包含掺杂粒子222,由于掺杂元素取代介电陶瓷材料中的金属,从而产生更多的感应偶极矩以及掺杂离子进入晶体内部后会使晶格畸变有利于极化,所以拥有更高的介电常数。但是,由于掺杂粒子会产生电子位移,从而导致较高的介电损耗。设置在高介电材料层22两侧的第一低介电损耗材料层21和第二低介电损耗材料层22,通过包覆在高介电材料层22外表面,可以有效解决因离子掺杂导致的介电损耗,实现低损耗的目的。同时掺杂后可以增加介电陶瓷材料的粘结与低介电损耗材料层之间的粘结强度。第一低介电损耗材料层21和第二低介电损耗材料层22可以是聚合物层或氧化石墨烯层。

40.参照图2b,当介电层包含两层高介电材料层时,两层高介电材料层22a和22b的两侧分别层叠有第一低介电损耗材料层21a和21b和第二低介电损耗材料层23。高介电材料层22a和22b分别包括介电陶瓷材料221a,221b和掺杂粒子222a,222b。基于前述实施方式相同的原理,高介电材料层22a和22b可以提高材料的介电常数,包覆在介电陶瓷材料层22a和22b两侧的第一低介电损耗材料层21a和21b和第二低介电损耗材料层23实现低损耗的目的。

41.本发明的动态随机存取存储器电容器可以通过如下方法制备。s1,形成高介电材料层;s2,在高介电材料层上形成低介电损耗材料层;s3,在高介电材料层上形成低介电损耗材料层。其中步骤s1、s2和s3仅表示步骤地前后关系,并不意在限定各步骤之间紧密连

接,而是各步骤之间还可以包含其它辅助步骤,例如清洗、干燥等步骤。当制备包含多层掺杂的介电陶瓷材料层时,重复s2、s3步骤至少一次即可实现。优选,s2步骤中通过原子层沉积形成掺杂的介电陶瓷材料层。

42.以下通过具体实例进一步描述本发明。不过这些实例仅仅是范例性的,并不对本发明的保护范围构成任何限制。

43.在下述实施例和对比例中,所使用到的试剂、材料以及仪器如没有特殊的说明,均可商购获得。

44.实施例1

45.采用hummers法制备单层氧化石墨烯(go)。即将石墨粉/nano3/kmno4以质量比10:5:12混合少量浓硫酸/h2o2作为反应前驱体,在冰浴条件充分进行氧化还原反应(控制反应温度不超过10℃)。用h2so4/h2o2/hcl去除衍生物,得到氧化石墨烯。通过超声或者机械剥离,得到单层氧化石墨烯。将单层氧化石墨烯通过原位旋涂法,旋涂在第一电容器电极(tin)表面,形成氧化石墨烯层。

46.采用四二乙基氨基铪(tdeah)、sb(ch)和水作为反应前驱体,采用99.99的高纯氮气作为载体和冲洗气体,前驱体温度为100度,反应腔室温度300℃,沉积得到sb掺杂的hfo2层。

47.在sb掺杂的hfo2表面再旋涂一层go,使go能够包覆sb掺杂的hfo2层。

48.在外侧的氧化石墨烯层表面形成第二电容器电极(tin),从而完成dram电容器的制备。

49.通过上海爱义电子设备有限公司as2855高频介电常数介质损耗测试系统对电容器进行介电常数和介电损耗测试as2855高频介电常数介质损耗测试系统由s916测试装置(夹具)、qbg-3e/qbg-3f/as2853a型高频q表、数据采集和tanδ自动测量控件(装入qbg-3e/qbg-3f或as2853a的软件模块)、及lki-1型电感器组成。使用qbg-3e/3f或as2853a数字q表具有自动计算介电常数(ε)和介质损耗(tanδ)。电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

50.实施例2

51.采用环四二甲氨基钛、ch3cooag和水作为反应前驱体,采用99.99的高纯ar作为载体和冲洗气体。前驱体温度100度,反应腔室温度300度,沉积得到ag掺杂的tio2层。

52.其它各层的形成方式及测试方法与实施例1相同。

53.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

54.实施例3

55.采用环四二甲氨基钛、insb和水作为反应前驱体,采用99.99的高纯ar作为载体和冲洗气体。前驱体温度100度,反应腔室温度300度,沉积得到in和sb掺杂的tio2层。

56.选择一定质量的聚酰亚胺固体颗粒与万能溶剂n,n-二甲基甲酰胺配出浓度百分比为25%的聚酰亚胺前驱液,然后采用高速旋涂的方法在tin上面旋涂前驱液(转速5000),然后放进炉管用200度退火,得到2nm的聚酰亚胺膜层。

57.其它各层的形成方式及测试方法与实施例1相同。

58.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

59.实施例4

60.采用四二甲氨基锆、c6h9bio6和水作为反应前驱体,采用99.99的高纯ar作为载体和冲洗气体。前驱体温度100度,反应腔室温度300度,沉积得到bi掺杂的zro2层。

61.其它各层的形成方式及测试方法与实施例3相同。

62.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

63.实施例5

64.采用四二甲氨基锆、tah和水作为反应前驱体,采用99.99的高纯ar作为载体和冲洗气体。前驱体温度100度,反应腔室温度300度,沉积得到ta掺杂的zro2层。

65.将聚偏氟乙烯、n,n-二甲基甲酰胺、丙酮配出浓度百分比为25%的前驱液,加热溶解,采用静电纺丝法,在10kv的高压下,使前驱液形成tyler锥并成拉丝状沉积在tin电极上,然后200度退火得到2nm的聚偏氟乙烯纤维膜层。

66.其它各层的形成方式及测试方法与实施例1相同。

67.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

68.实施例6

69.采用四二乙基氨基铪(tdeah)、lah和水作为反应前驱体,采用99.99的高纯氮气作为载体和冲洗气体,前驱体温度为100度,反应腔室温度300℃,沉积得到la掺杂的hfo2层。

70.其它各层的形成方式及测试方法与实施例5相同。

71.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

72.实施例7

73.采用四二乙基氨基铪(tdeah)、ce(ac)3和水作为反应前驱体,采用99.99的高纯氮气作为载体和冲洗气体,前驱体温度为100度,反应腔室温度300℃,沉积得到ce掺杂的hfo2层。

74.其它各层的形成方式及测试方法与实施例1相同。

75.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

76.实施例8

77.以实施例1相同的方式制备3层结构后,再重复形成sb掺杂的hfo2层和go层各一次,最后形成第二电容器电极,从而完成dram电容器的制备。对电容器进行介电常数和介电损耗测试,方法与实施例1相同。

78.该实施例制备的电容器的测试结果及介电层中各层的组成、厚度参数如表1所示。

79.对比例1

80.采用四二乙基氨基铪(tdeah)水作为反应前驱体,采用99.99的高纯氮气作为载体和冲洗气体,前驱体温度为100度,反应腔室温度300℃,沉积得到hfo2层。其它各层的形成方式及测试方法与实施例1相同。

81.该对比例制备的电容器的测试结果及介电层的组成、厚度参数如表1所示。

82.对比例2

83.采用四二乙基氨基铪(tdeah)、sbcl3/sb(ch)和水作为反应前驱体,采用99.99的高纯氮气作为载体和冲洗气体,前驱体温度为100度,反应腔室温度300℃,沉积得到sb掺杂的hfo2层。

84.该对比例制备的电容器的测试结果及介电层的组成、厚度参数如表1所示。

85.表1

[0086][0087][0088]

如表1所示,结合实施例1-8和对比例1-2的数据可以看出,本发明的介电层确实可以实现兼顾电容器的高介电常数和低介电损耗的目的。

[0089]

以上公开的本发明优选实施例只是用于帮助阐述本发明。优选实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施方式。显然,根据本说明书的内容,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地理解和利用本发明。本发明仅受权利要求书及其全部范围和等效物的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1