一种低钳位电压ESD防护结构及其制备方法与流程

一种低钳位电压esd防护结构及其制备方法

技术领域

1.本发明涉及电子科学与技术领域,主要用于静电泄放(electro static discharge,简称为esd)防护技术,具体涉及一种低钳位电压esd防护结构及其制备方法。

背景技术:

2.esd即静电泄放,是自然界普遍存在的现象。esd存在于人们日常生活的各个角落。而就是这样习以为常的电学现象对于精密的集成电路来讲却是致命的威胁。

3.随着集成电路制造工艺的提高,其最小线宽已经下降到亚微米甚至纳米的级别,在带来芯片性能提高的同时,其抗esd打击能力也大幅度降低,因此静电损害更严重。设计者需要同时满足esd设计窗口及防护等级的要求,器件闩锁及钳位过高的矛盾贯穿着设计的始终。

4.npn晶体管由于其具有一定的电流放大能力,因此在esd应力下易产生回扫,即snapback现象。其snapback强弱与npn晶体管的电流放大能力有很大关系。当电流放大能力减弱时,其回扫效应会减弱,因此为了提高器件维持电压,一般用于esd的npn管通常具有低的电流放大倍数。

技术实现要素:

5.本发明为解决背景技术中存在的上述技术问题,而提供一种低钳位电压esd防护结构及其制备方法,利用npn晶体管发射区重掺杂引起的高俄歇复合几率,从而大大降低npn晶体管的放大系数,实现更高的维持特性。

6.本发明的技术解决方案是:本发明为一种低钳位电压esd防护结构,其特殊之处在于:所述防护结构包括p型衬底、n型外延层、pwell区、第一n+接触区、n+齐纳接触区、第一p+接触区和第二n+接触区,p型衬底上方为n型外延层,pwell区和第二n+接触区位于n型外延层内部上方,第二n+接触区位于pwell区右方,第一n+接触区、n+齐纳接触区,第一p+接触区位于pwell区内部上方;n+齐纳接触区包围第一n+接触区,第一p+接触区位于n+齐纳接触区右方。

7.一种制备权利上述的低钳位电压esd防护结构的方法,其特殊之处在于:所述方法包括以下步骤:

8.1)在p型衬底中,外延形成n型外延层;

9.2)在n型外延层中,离子注入p型杂质

10.3)热扩散形成p型阱区;

11.4)通过离子注入形成n+接触区、p+接触区,作为npn晶体管的发射极、基极、集电极;

12.5)在发射结所处的n+接触区范围内,利用齐纳注入n型杂质,快速热退火激活后形成npn晶体管新发射极。

13.本发明还提供一种低钳位电压esd防护结构,其特殊之处在于:所述防护结构包括

n型衬底、p型外延层、nwell区、第一p+接触区、齐纳p+接触区、第二n+接触区和第二p+接触区,n型衬底上方为p型外延层,nwell区和第二p+接触区位于p型外延层内部上方,第二p+接触区位于nwell区右方,第一p+接触区、齐纳p+接触区,第二n+接触区位于nwell区内部上方;齐纳p+接触区包围第一p+接触区,第二n+接触区位于齐纳p+接触区右方。

14.一种制备上述的低钳位电压esd防护结构的方法,其特殊之处在于:所述方法包括以下步骤:

15.1)在n型衬底中,外延形成p型外延层;

16.2)在p型外延层中,离子注入n型杂质

17.3)热扩散形成n型阱区;

18.4)通过离子注入形成n+接触区、p+接触区,作为pnp晶体管的发射极、基极、集电极;

19.5)在发射结所处的p+接触区范围内,利用齐纳注入p型杂质,快速退火激活形成npn晶体管新发射极。

20.本发明的低钳位电压esd防护结构及其制备方法,提出的利用齐纳注入的方式用于增加npn晶体管发射结俄歇复合几率,对发射结进行重掺杂从而降低npn注入效率,从而大大降低其发射极注入效率,以此来抑制npn晶体管的电流放大能力,以提高esd脉冲下的维持电压值。根据理论,该方法能够对具有寄生npn或pnp结构的其他结构产生相同的作用以提高维持电压(如可控硅整流器scr结构)。

附图说明

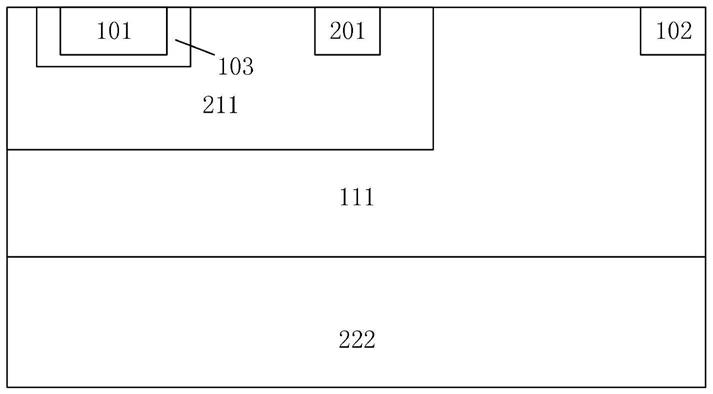

21.图1为本发明实施例一的结构示意图;

22.图2为本发明实施例而的结构示意图。

23.附图标号说明如下:

24.222、p型衬底;111、n型外延层;211、pwell区;101、第一n+接触区;103、n+齐纳接触区;201、第一p+接触区;102、第二n+接触区;122、n型衬底;223、p型外延层;112、nwell区;202、第一p+接触区;205、p+齐纳接触区;203、第二p+接触区;105、第二n+接触区。

具体实施方式

25.下面结合附图和具体实施例对本发明的技术方案做进一步详细描述。

26.实施例1

27.参见图1,本发明具体实施例一的结构包括:p型衬底222、n型外延层111、pwell区211、第一n+接触区101、n+齐纳接触区103、第一p+接触区201和第二n+接触区102,p型衬底222上方为n型外延层111,pwell区211和第二n+接触区102位于n型外延层111内部上方,第二n+接触区102位于pwell区211右方,第一n+接触区101、n+齐纳接触区103,第一p+接触区201位于pwell区211内部上方;n+齐纳接触区103包围第一n+接触区101,第一p+接触区201位于n+齐纳接触区103右方。

28.本发明实施例一结构的制备方法包括以下步骤:

29.1)在p型衬底中,外延形成n型外延层;

30.2)在n型外延层中,离子注入p型杂质

31.3)热扩散形成p型阱区;

32.4)通过离子注入形成n+接触区、p+接触区,作为npn晶体管的发射极、基极、集电极;

33.5)在发射结所处的n+接触区范围内,利用齐纳注入n型杂质,快速热退火激活后形成npn晶体管新发射极。

34.本实施例的工作原理为:

35.本实施例通过npn晶体管发射区加入齐纳注入区,使得发射区掺杂浓度变高。当发射区掺杂浓度高到一定量级时,俄歇复合影响会变的很大,再继续增大其注入浓度时,晶体管的注入效率会大大降低,从而npn晶体管的放大系数会降低,此时防护器件的维持电压会有所升高以应对可能的闩锁风险。

36.实施例2

37.参见图2,本发明具体实施例二的结构包括:n型衬底122、p型外延层223、nwell区112、第一p+接触区202、齐纳p+接触区205、第二n+接触区105和第二p+接触区203,n型衬底122上方为p型外延层223,nwell区112和第二p+接触区203位于p型外延223层内部上方,第二p+接触区203位于nwell区112右方,第一p+接触区202、齐纳p+接触区205,第二n+接触区105位于nwell区112内部上方;齐纳p+接触区205包围第一p+接触区202,第二n+接触区105位于齐纳p+接触区205右方。

38.本发明实施例二结构的制备方法包括以下步骤:

39.1)在n型衬底中,外延形成p型外延层;

40.2)在p型外延层中,离子注入n型杂质

41.3)热扩散形成n型阱区;

42.4)通过离子注入形成n+接触区、p+接触区,作为pnp晶体管的发射极、基极、集电极;

43.5)在发射结所处的p+接触区范围内,利用齐纳注入p型杂质,快速退火激活形成npn晶体管新发射极。

44.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细地说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1