提高芯片内器件性能均匀性的方法、装置及电子设备与流程

1.本申请涉及芯片设计及制作领域,具体而言,涉及一种提高芯片内器件性能均匀性的方法、装置及电子设备。

背景技术:

2.随着半导体制作工艺向更先进的节点(28nm

→

14nm

→

7nm)演进,集成电路中,芯片内部不同位置同种器件的性能差异,往往更容易导致均匀性相关的良率损失。尤其是新产品从导入、试生产,到量产的转换阶段,需要快速提升良率,因此,如何提高芯片内器件性能的均匀性至关重要。

3.现有技术中,针对某个目标芯片,往往是通过线宽扫描电子显微镜对其各关键功能模块中具有的关键尺寸量测结构进行尺寸大小的在线测量,此后,直接根据目标芯片内各关键功能模块对应的关键尺寸量测结构,在线测量的物理尺寸大小来做表征,获得使各关键功能模块对应的多个目标位置上,关键器件沟道长度尺寸大小一致所需的能量补偿值,再针对多个目标位置中的每个目标位置,通过与该目标位置对应的能量补偿值,对该目标位置进行曝光能量补偿,以提高目标芯片内各关键功能模块中,关键器件的沟道长度尺寸大小均匀性,从而提高目标芯片内处于不同位置的各关键器件性能的均匀性。

4.上述过程中,一方面,通过线宽扫描电子显微镜对目标芯片内各关键功能模块中具有的关键尺寸量测结构进行尺寸大小的在线测量需要耗费大量人力和机时,因此,降低了提高目标芯片内关键器件性能均匀性方法的实施效率,另一方面,由于其仅仅考虑了目标芯片内各关键功能模块中关键器件的沟道长度尺寸大小对目标芯片内关键器件均匀性的影响,而未考虑对目标芯片进行曝光生产后,其他制程的影响因素,例如,离子注入、快速退火等,因此,具有一定局限性,也就影响了目标芯片内关键器件的性能均匀性提高的效果。

技术实现要素:

5.本申请的目的在于,提供一种提高芯片内器件性能均匀性的方法、装置及电子设备,以解决上述问题。

6.第一方面,本申请提供的提高芯片内器件性能均匀性的方法,包括:

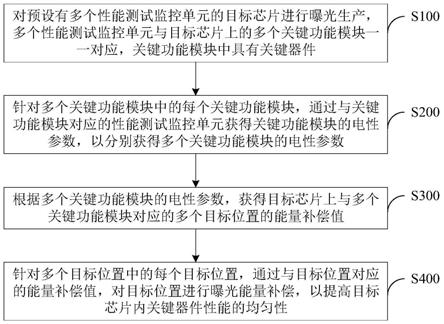

7.对预设有多个性能测试监控单元的目标芯片进行曝光生产,多个性能测试监控单元与目标芯片上的多个关键功能模块一一对应,关键功能模块中具有关键器件;

8.针对多个关键功能模块中的每个关键功能模块,通过与关键功能模块对应的性能测试监控单元获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数;

9.根据多个关键功能模块的电性参数,获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值;

10.针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿,以提高目标芯片内关键器件性能的均匀性。

11.结合第一方面,本申请实施例还提供了第一方面的第一种可选的实施方式,对预设有多个性能测试监控单元的目标芯片进行曝光生产之前,提高芯片内器件性能均匀性的方法还包括:

12.确定出目标芯片上与多个关键功能模块对应的多个目标位置;

13.分别在多个目标位置设置多个性能测试监控单元,以使多个性能测试监控单元与多个目标位置一一对应,且针对多个性能测试监控单元中的每个性能测试监控单元,性能测试监控单元能够应用联合测试行为组织协议,通过晶圆良率测试方法监测自身的电性指标,以表征对应功能关键功能模块的电性参数。

14.结合第一方面,本申请实施例还提供了第一方面的第二种可选的实施方式,对预设有多个性能测试监控单元的目标芯片进行曝光生产,包括:

15.获取目标芯片的原始曝光能量值;

16.分别通过原始曝光能量值,对目标芯片上与多个关键功能模块对应的多个目标位置进行曝光,以实现对目标芯片的曝光生产。

17.结合第一方面,本申请实施例还提供了第一方面的第三种可选的实施方式,根据多个关键功能模块的电性参数,获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值,包括:

18.获得目标电性值;

19.针对多个关键功能模块中的每个关键功能模块,获取关键功能模块的电性参数与目标电性值之间的电性差异值,以获得与多个关键功能模块一一对应的多个电性差异值;

20.针对多个关键功能模块中的每个关键功能模块,根据与关键功能模块对应的电性差异值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值,以获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值。

21.结合第一方面的第三种可选的实施方式,本申请实施例还提供了第一方面的第四种可选的实施方式,获取目标电性值,包括:

22.根据目标芯片所在待处理晶圆上的所有芯片上,多个关键功能模块的电性参数获得目标电性值。

23.结合第一方面的第四种可选的实施方式,本申请实施例还提供了第一方面的第五种可选的实施方式,根据目标芯片所在待处理晶圆上的所有芯片上,多个关键功能模块的电性参数获得目标电性值,包括:

24.计算出目标芯片所在待处理晶圆上的所有目标芯片上,位于同一目标位置的所有关键功能模块的电性参数的均值;

25.根据与多个关键功能模块一一对应的多个均值,获得目标电性值。

26.结合第一方面的第五种可选的实施方式,本申请实施例还提供了第一方面的第六种可选的实施方式,根据与多个关键功能模块一一对应的多个均值,获得目标电性值,包括:

27.从与多个关键功能模块一一对应的多个均值中,获取中位数,作为目标电性值;

28.或计算出与多个关键功能模块一一对应的多个均值的平均值,作为目标电性值。

29.结合第一方面的第三种可选的实施方式,本申请实施例还提供了第一方面的第七种可选的实施方式,获取目标电性值,包括:

30.获取预设固定值,以将预设固定值作为目标电性值。

31.结合第一方面的第三种可选的实施方式,本申请实施例还提供了第一方面的第八种可选的实施方式,根据与关键功能模块对应的电性差异值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值,包括:

32.获取关键器件的性能与关键器件的沟道长度尺寸大小之间的敏感度,作为第一敏感度;

33.根据与关键功能模块对应的电性差异值和第一敏感度,获取与关键功能模块对应的关键器件沟道长度尺寸调整值;

34.根据关键器件沟道长度尺寸调整值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值。

35.结合第一方面的第八种可选的实施方式,本申请实施例还提供了第一方面的第九种可选的实施方式,根据关键器件沟道长度尺寸调整值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值,包括:

36.获取曝光能量与关键器件的沟道长度尺寸大小之间的敏感度,作为第二敏感度;

37.根据关键器件沟道长度尺寸调整值和第二敏感度,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值。

38.第二方面,本申请实施例还提供了一种提高芯片内器件性能均匀性的装置,包括:

39.曝光生产模块,用于对预设有多个性能测试监控单元的目标芯片进行曝光生产,多个性能测试监控单元与目标芯片上的多个关键功能模块一一对应;

40.电性参数获取模块,用于针对多个关键功能模块中的每个关键功能模块,通过与关键功能模块对应的性能测试监控单元获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数;

41.能量补偿值获取模块,用于根据多个关键功能模块的电性参数,获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值;

42.曝光能量补偿模块,用于针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿,以提高目标芯片内器件性能均匀性。

43.第三方面,本申请实施例还提供了一种电子设备,包括控制器和存储器,存储器上存储有计算机程序,控制器用于执行计算机程序,以实现上述第一方面,或第一方面的任意一种可选的实施方式所提供的提高芯片内器件性能均匀性的方法。

44.第四方面,本申请实施例还提供了一种计算机可读存储介质,计算机可读存储介质上存储有计算机程序,计算机程序被执行时,实现上述第一方面,或第一方面的任意一种可选的实施方式所提供的提高芯片内器件性能均匀性的方法。

45.在本申请提供的提高芯片内器件性能均匀性的方法的实施过程中,由于目标芯片预设有多个性能测试监控单元,且针对多个关键功能模块中的每个关键功能模块,能够通过与关键功能模块对应的性能测试监控单元自动获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数,相对于现有技术中,通过线宽扫描电子显微镜对目标芯片内各关键功能模块中具有的关键器件进行沟道长度尺寸大小表征结构的在线测量的方案而言,无需耗费大量人力和机时,因此,在本申请提供的提高芯片内关键器件性能均匀性方法的实施效率相对于现有技术而言,有较大的提升,此外,由于目标芯片上与多个关键功

能模块对应的多个目标位置的能量补偿值,是根据多个关键功能模块最终的电性参数获得的,因此,能够综合考虑后续其他制程对目标芯片内关键器件电性的影响,而不局限于对目标芯片进行曝光生产过程中,栅极的光刻和蚀刻制程,从而保证针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿之后,目标芯片内关键器件性能的均匀性提高的效果。

46.本申请实施例提供的提高芯片内器件性能均匀性的装置、电子设备及计算机可读存储介质,具有与上述提高芯片内器件性能均匀性的方法相同的有益效果,本申请实施例对此不作赘述。

附图说明

47.为了更清楚地说明本申请实施例的技术方案,下面将对本申请实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本申请的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

48.图1为现有技术中,提高芯片内器件性能均匀性的方法的步骤流程图。

49.图2为本申请实施例提供的一种电子设备的示意性结构框图。

50.图3为本申请实施例提供的一种提高芯片内器件性能均匀性的方法的步骤流程图。

51.图4为本申请实施例提供的一种提高芯片内器件性能均匀性的方法的辅助性说明图。

52.图5为本申请实施例提供的提高芯片内器件性能均匀性的方法的一种具体实施方式的步骤流程图。

53.图6为本申请实施例提供的一种提高芯片内器件性能均匀性的装置的示意性结构框图。

54.附图标记:100

‑

电子设备;110

‑

处理器;120

‑

存储器;200

‑

提高芯片内器件性能均匀性的装置;210

‑

曝光生产模块;220

‑

电性参数获取模块;230

‑

能量补偿值获取模块;240

‑

曝光能量补偿模块。

具体实施方式

55.为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行描述。此外,应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

56.随着半导体制作工艺向更先进的节点(28nm

→

14nm

→

7nm)演进,集成电路中,芯片内部不同位置同种器件的性能差异,往往更容易导致均匀性相关的良率损失,例如,存储器内建自测试(memory build

‑

in self test,mbist)的读干扰失效(read disturb failure)等。尤其是新产品从导入(tape

‑

out)、试生产(engineer lot phase),到量产(mass production)的转换阶段,需要快速提升良率,因此,如何提高芯片内器件性能的均匀性至关重要。

57.如背景技术,现有技术中,针对某个目标芯片,往往是通过线宽扫描电子显微镜(critical dimension scanning electron microscope,cdsem)对其各关键功能模块中具有的关键尺寸量测结构进行尺寸大小的在线(inline)测量,此后,直接根据目标芯片内各关键功能模块对应的关键尺寸量测结构,在线(inline)测量的物理尺寸大小来做表征,获得使各关键功能模块对应的多个目标位置上,关键器件沟道长度(channel length)尺寸大小一致所需的能量补偿值,再针对多个目标位置中的每个目标位置,通过与该目标位置对应的能量补偿值,对该目标位置进行曝光能量补偿,以提高目标芯片内各关键功能模块中,关键器件的沟道长度(channel length)尺寸大小的均匀性,从而提高目标芯片内处于不同位置的各关键器件性能的均匀性。

58.请参阅图1,总结来说,现有技术中,提高芯片内器件性能均匀性的方法具体可以包括以下步骤:

59.分别在目标芯片上预先确定出的多个目标位置设置关键尺寸(critical dimension)量测结构,例如,互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)器件或关键尺寸大小的条状平行线组结构(critical dimension bar),多个目标位置与目标芯片上的多个关键功能模块一一对应;

60.分别通过原始曝光能量值,对目标芯片上的多个目标位置进行曝光,以实现对目标芯片的曝光生产;

61.通过cdsem对其表征各关键功能模块中具有的关键器件沟道长度(channel length)尺寸大小的关键尺寸(critical dimension)量测结构进行在线(inline)测量;

62.计算出cdsem在线(inline)测量获得的各沟道长度(channel length)尺寸大小的差异值;

63.根据各沟道长度(channel length)尺寸大小的差异值,以及曝光能量与关键器件的沟道长度尺寸大小之间的敏感度,获得使各关键功能模块对应的多个目标位置上,关键器件沟道长度(channel length)尺寸大小一致所需的能量补偿值;

64.将使各关键功能模块对应的多个目标位置上,关键器件沟道长度(channel length)尺寸大小一致所需的能量补偿值反馈给曝光系统,补偿多个目标位置的曝光能量,以提高目标芯片内各关键功能模块中,关键器件的沟道长度(channel length)尺寸大小均匀性,从而提高目标芯片内处于多个目标位置的各关键器件性能的均匀性。

65.现有技术中存在的缺陷:

66.(1)通过cdsem对目标芯片内各关键功能模块中具有的关键尺寸量测结构进行尺寸大小的在线(inline)测量,例如:若摆放的是cmos器件,则量测的是cmos器件的沟道长度(channel length),若摆放的是关键尺寸大小的条状平行线组结构(critical dimension bar),则量测的是条状图案线宽。虽然这些结构的测量都可以表征对应关键功能模块中关键器件的沟道长度(channel length)的尺寸大小,但是,这种在线(inline)测试需要耗费大量人力和机时,因此,降低了提高目标芯片内关键器件性能均匀性方法的实施效率。

67.(2)由于现有技术中,仅仅考虑了目标芯片内各关键功能模块中关键器件的沟道长度(channel length)尺寸大小对目标芯片内关键器件性能均匀性的影响,也即,仅仅是根据目标芯片内各关键功能模块中对应的关键尺寸量测结构,在线(inline)测量的物理尺寸大小来做表征,获得使各关键功能模块对应的多个目标位置上,关键器件沟道长度

(channel length)尺寸大小一致所需的能量补偿值,而未考虑对目标芯片进行曝光生产,也即,栅极(gate)的光刻/蚀刻(litho/etch)后,其他制程的影响因素,因此,具有一定局限性,也就影响了目标芯片内关键器件的性能均匀性提高效果。其他制程的影响因素可以是离子注入、快速退火等,以快速退火为例,图形密度(pattern density)或图形分布(pattern distribution)的局部差异,会导致芯片上的不同位置出现吸热差,而影响器件的电性性能。

68.此外,现有技术中,由于通过cdsem对目标芯片内各关键功能模块对应的关键尺寸量测结构的物理尺寸大小的在线(inline)测量需要耗费大量人力和机时,因此,通常只有在“新产品导入并量产”或者“量产期间,测试机台或制作工艺有重大更新的情况”时,才会通过cdsem对目标芯片内各关键功能模块对应的关键尺寸量测结构的物理尺寸大小进行在线(inline)测量,而获得使各关键功能模块对应的多个目标位置上,关键器件沟道长度(channel length)尺寸大小一致所需的能量补偿值,制程机台生产性维护(productive maintenance,pm)后或异常情况处理过程中,不会去特别获取目标芯片上与多个关键功能模块对应的目标位置的能量补偿值,因此,现有技术中,提高芯片内器件性能均匀性的方法也具有及时性较差的缺陷。

69.请参阅图2,为解决上述问题,本申请实施例提供了一种电子设备100。本申请实施例中,电子设备100可以是用于执行本申请实施例提供的提高芯片内器件均匀性的方法的测试机台。

70.在结构上,电子设备100可以包括处理器110和存储器120。

71.处理器110和存储器120直接或间接地电性连接,以实现数据的传输或交互,例如,这些元件相互之间可通过一条或多条通讯总线或信号线实现电性连接。提高芯片内器件性能均匀性的装置包括至少一个可以软件或固件(firmware)的形式存储在存储器120中的软件模块。处理器110用于执行存储器120中存储的可执行模块,例如,提高芯片内器件性能均匀性的装置所包括的软件功能模块及计算机程序等,以实现提高芯片内器件性能均匀性的方法。

72.处理器110可以在接收到执行指令后,执行计算机程序。其中,处理器110可以是一种集成电路芯片,具有信号处理能力。处理器110也可以是通用处理器,例如,可以是数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、分立门或晶体管逻辑器件、分立硬件组件,可以实现或者执行本申请实施例中的公开的各方法、步骤及逻辑框图,此外,通用处理器可以是微处理器或者任何常规处理器等。

73.存储器120可以是,但不限于,随机存取存储器(random access memory,ram)、只读存储器(read only memory,rom)、可编程只读存储器(programmable read

‑

only memory,prom)、可擦可编程序只读存储器(erasable programmable read

‑

only memory,eprom),以及电可擦编程只读存储器(electric erasable programmable read

‑

only memory,eeprom)。存储器120用于存储程序,处理器110在接收到执行指令后,执行该程序。

74.应当理解,图2所示的结构仅为示意,本申请实施例提供的电子设备100还可以具有比图2更少或更多的组件,或是具有与图2所示不同的配置。此外,图2所示的各组件可以通过软件、硬件或其组合实现。

75.请参阅图3,为本申请实施例提供的提高芯片内器件性能均匀性的方法的流程示意图,该方法应用于图2所示的电子设备100。需要说明的是,本申请实施例提供的提高芯片内器件性能均匀性的方法不以图3及以下所示的顺序为限制,以下结合图3对提高芯片内器件性能均匀性的方法的具体流程及步骤进行描述。

76.步骤s100,对预设有多个性能测试监控单元的目标芯片进行曝光生产,多个性能测试监控单元与目标芯片上的多个关键功能模块一一对应,关键功能模块中具有关键器件。

77.本申请实施例中,性能测试监控单元为一种低阈值电压器件(low vt device,lvt)结构,在芯片设计及制作技术领域中,也称之为“testkey”,性能测试监控单元的物理尺寸大小为半导体制作工艺的某个节点中,最小允许的器件尺寸,例如,某芯片设计制作商的7nm制作工艺中,最小允许的器件尺寸可以为width/length=0.038/0.008um,或某个芯片的设计过程中,用到最多且最普遍的一级器件尺寸,再例如,某芯片设计制作商的7nm制作工艺中,用到最多且最普遍的一级器件尺寸可以为width/length=0.038/0.011um。

78.此外,需要说明的是,本申请实施例中,性能测试监控单元用于采集关键功能模块的电性参数,例如,饱和漏电流(idsat)或临界电压(vtsat)。基于此,在步骤s100之前,本申请实施例提供的提高芯片内器件性能均匀性的方法还可以包括步骤s001和步骤s002。

79.步骤s001,确定出目标芯片上与多个关键功能模块对应的多个目标位置。

80.步骤s002,分别在多个目标位置设置多个性能测试监控单元,以使多个性能测试监控单元与多个目标位置一一对应,且针对多个性能测试监控单元中的每个性能测试监控单元,该性能测试监控单元能够应用联合测试行为组织协议,通过晶圆良率测试方法监测自身的电性指标,以表征对应功能关键功能模块的电性参数。

81.本申请实施例中,联合测试行为组织协议(joint test action group,jtag)为一种测试选择标准协议,它可以通过目标芯片内部预设的寄存器,在不同的测试步骤,选择不同的测试结构进行相应测试。例如,某个测试步骤选中某个性能测试监控单元,则可以在施加不同的测试条件(电压、电流等)之后,直接获得对应的功能关键功能模块的电性参数,而测试条件可以根据实际需求设定,本申请实施例对此不作具体限制。

82.此外,对于步骤s100,其可以包括步骤s110和步骤s120。

83.步骤s110,获取目标芯片的原始曝光能量值。

84.步骤s120,分别通过原始曝光能量值,对目标芯片上与多个关键功能模块对应的多个目标位置进行曝光,以实现对目标芯片的曝光生产。

85.本申请实施例中,在获取到目标芯片的原始曝光能量值之后,可以利用曝光系统,控制光刻设备通过原始曝光能量值,对目标芯片上与多个关键功能模块对应的多个目标位置进行曝光,以实现对目标芯片的曝光生产。其中,原始曝光能量值可以在通过试验确定初始条件(inline pi

‑

run),且通过cdsem测量确定切割道上摆放的关键尺寸大小的条状平行线组结构(critical dimension bar)达到目标值(on

‑

target)时获得。

86.步骤s200,针对多个关键功能模块中的每个关键功能模块,通过与关键功能模块对应的性能测试监控单元获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数。

87.如前所述,本申请实施例中,电性参数可以包括饱和漏电流(idsat)或临界电压

(vtsat)等。

88.此外,由于本申请实施例提供的提高芯片内器件性能均匀性的方法还可以包括步骤s001和步骤s002,因此,可以理解的是,本申请实施例中,针对多个关键功能模块中的每个关键功能模块,可以通过与该关键功能模块对应的性能测试监控单元应用jtag,通过晶圆良率测试(chip probing)方法监测自身的电性指标,以表征对应功能关键功能模块的电性参数。

89.步骤s300,根据多个关键功能模块的电性参数,获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值。

90.对于步骤s300,本申请实施例中,作为一种可选的实施方式,其可以包括步骤s310、步骤s320和步骤s330。

91.步骤s310,获得目标电性值。

92.对于目标电性值,本申请实施例中,其可以直接获取预设固定值,以将预设固定值作为目标电性值,而预设固定值可以是设计者出于设计仿真考虑,或良率考虑而设定的某一定值,此外,目标电性值也可以是综合目标芯片所在待处理晶圆上的所有芯片上,多个关键功能模块的电性参数之后,获得的目标电性值。基于此,本申请实施例中,步骤s310可以包括步骤s311。

93.步骤s311,根据目标芯片所在待处理晶圆上的所有芯片上,多个关键功能模块的电性参数获得目标电性值。

94.实际实施时,可以计算出目标芯片所在待处理晶圆上的所有目标芯片上,位于同一目标位置的所有关键功能模块的电性参数的均值,再根据与多个关键功能模块一一对应的多个均值,获得目标电性值,例如,从与多个关键功能模块一一对应的多个均值中,获取中位数,作为目标电性值,或计算出与多个关键功能模块一一对应的多个均值的平均值,作为目标电性值。

95.请结合图4,以待处理晶圆上包括目标芯片1、目标芯片2和目标芯片3,且每个目标芯片上包括3个关键功能模块为例,假设,目标芯片1上包括位于第一目标位置的关键功能模块11、位于第二目标位置的关键功能模块12,以及位于第三目标位置的关键功能模块13,目标芯片2上包括位于第一目标位置的关键功能模块21、位于第二目标位置的关键功能模块22,以及位于第三目标位置的关键功能模块23,目标芯片3上包括位于第一目标位置的关键功能模块31、位于第二目标位置的关键功能模块32,以及位于第三目标位置的关键功能模块33,那么,可以通过以下步骤获得目标电性值。

96.(1)计算出待处理晶圆上的所有目标芯片上,位于同一目标位置的所有关键功能模块的电性参数的均值:

97.对于第一目标位置,计算出关键功能模块11、关键功能模块21和关键功能模块31的电性参数的均值,记作均值x1;

98.对于第二目标位置,计算出关键功能模块12、关键功能模块22和关键功能模块32的电性参数的均值,记作均值x2;

99.对于第三目标位置,计算出关键功能模块13、关键功能模块23和关键功能模块33的电性参数的均值,记作均值x3。

100.(2)根据与多个关键功能模块一一对应的多个均值,获得目标电性值。

101.第一种方式,从与多个关键功能模块一一对应的多个均值中,获取中位数,作为目标电性值:

102.将均值x1、均值x2和均值x3按照数值大小进行排序,以获取均值x1、均值x2和均值x3的中位数,作为目标电性值。

103.第二种方式,计算出与多个关键功能模块一一对应的多个均值的平均值,作为目标电性值:

104.获取均值x1、均值x2和均值x3的平均值,作为目标电性值。

105.步骤s320,针对多个关键功能模块中的每个关键功能模块,获取关键功能模块的电性参数与目标电性值之间的电性差异值,以获得与多个关键功能模块一一对应的多个电性差异值。

106.步骤s330,针对多个关键功能模块中的每个关键功能模块,根据与关键功能模块对应的电性差异值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值,以获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值。

107.对于步骤s330,本申请实施例中,作为一种可选的实施方式,其可以包括步骤s331、步骤s332和步骤s333。

108.步骤s331,获取关键器件的性能与关键器件的沟道长度尺寸大小之间的敏感度,作为第一敏感度。

109.步骤s332,根据与关键功能模块对应的电性差异值和第一敏感度,获取与关键功能模块对应的关键器件沟道长度尺寸调整值。

110.本申请实施例中,针对多个关键功能模块中的某个关键功能模块,可以将与该关键功能模块对应的电性差异值作为目标差异值,计算出目标差异值的绝对值与第一敏感度的商,作为与该关键功能模块对应的关键器件沟道长度(device channel length)尺寸调整值。

111.同样,以目标芯片1上包括位于第一目标位置的关键功能模块11,核心电性参数为饱和漏电流(idsat)为例,若关键功能模块11的电性参数与目标电性值之间的电性差异值为

‑

40ua/um,且第一敏感度为关键器件的尺寸大小每增加1nm,电性参数便会减少20ua,也即,第一敏感度为20ua/nm,那么,与关键功能模块11对应的关键器件沟道长度(device channel length)尺寸调整值为:40/20=2nm,具体表征需要减少2nm的沟道长度(channel length)。减少2nm的沟道长度(channel length),饱和漏电流(idsat)增加40um/um,便可以使其与目标电性值的电性差异值

‑

40ua/um获得补偿,从而使关键功能模块的电性参数达到与目标电性值相同的水平。

112.需要说明的是,本申请实施例中,核心电性参数可以是电性参数中,对于当前制程而言,对关键器件的沟道长度尺寸大小影响最大的参数。

113.步骤s333,根据关键器件沟道长度尺寸调整值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值。

114.实际实施时,可以获取曝光能量与关键器件的沟道长度(channel length)尺寸大小之间的敏感度,作为第二敏感度,再根据关键器件沟道长度(device channel length)尺寸调整值和第二敏感度,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值。

115.继续以目标芯片1上包括位于第一目标位置的关键功能模块11,核心电性参数为

饱和漏电流(idsat),与关键功能模块11对应的关键器件沟道长度(device channel length)尺寸调整值为2nm,也即,需要减少2nm的沟道长度(channel length)为例,若第二敏感度为每增加0.2mj/cm2,关键器件的沟道长度(channel length)尺寸大小将减少1nm,也即,第二敏感度为0.2mj/cm2/nm,那么,第一目标位置的能量补偿值为:2*0.2=0.4mj/cm2,具体表征需要增加能量补偿值为0.4mj/cm2对第一目标位置进行曝光能量补偿。

116.步骤s400,针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿,以提高目标芯片内关键器件性能的均匀性。

117.本申请实施例中,针对多个目标位置中的每个目标位置,可以利用曝光系统控制光刻设备,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿,以提高目标芯片内关键器件性能的均匀性。

118.以下,将结合图5,对本申请实施例提供的一种提高芯片内器件性能均匀性的方法的一种具体实施方式进行总结描述:

119.分别在多个目标位置设置多个性能测试监控单元,以使多个性能测试监控单元与多个目标位置一一对应,且针对多个性能测试监控单元中的每个性能测试监控单元,该性能测试监控单元能够应用jtag,通过晶圆良率测试(chip probing)方法监测自身的电性指标,以表征对应功能关键功能模块的电性参数;

120.分别通过原始曝光能量值,对目标芯片上与多个关键功能模块对应的多个目标位置进行曝光,以实现对目标芯片的曝光生产;

121.针对多个关键功能模块中的每个关键功能模块,通过与该关键功能模块对应的性能测试监控单元应用jtag,通过晶圆良率测试(chip probing)方法监测自身的电性指标,以表征对应功能关键功能模块的电性参数;

122.针对多个关键功能模块中的每个关键功能模块,获取关键功能模块的电性参数与目标电性值之间的电性差异值,以获得与多个关键功能模块一一对应的多个电性差异值;

123.获取关键器件的性能与关键器件的沟道长度(channel length)尺寸大小之间的敏感度,作为第一敏感度,并根据与关键功能模块对应的电性差异值和第一敏感度,获取与关键功能模块对应的关键器件沟道长度(device channel length)尺寸调整值;

124.获取曝光能量与关键器件的沟道长度(channel length)尺寸大小之间的敏感度,作为第二敏感度,再根据关键器件沟道长度(device channel length)尺寸调整值和第二敏感度,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值;

125.针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿,以提高目标芯片内关键器件性能的均匀性。

126.总结来说,在本申请实施例提供的提供芯片内器件性能均匀性的方法的实施过程中,由于目标芯片预设有多个性能测试监控单元,且针对多个关键功能模块中的每个关键功能模块,能够通过与关键功能模块对应的性能测试监控单元自动获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数,相对于现有技术中,通过线宽扫描电子显微镜对目标芯片内各关键功能模块中具有的关键器件进行沟道长度尺寸大小表征结构的在线测量的方案而言,无需耗费大量人力和机时,因此,在本申请提供的提高芯片内关键器件性能均匀性方法的实施效率相对于现有技术而言,有较大的提升,此外,由于目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值,是根据多个关键功能模块最终

的电性参数获得的,因此,能够综合考虑后续其他制程对目标芯片内关键器件电性的影响,而不局限于对目标芯片进行曝光生产过程中,栅极的光刻和蚀刻制程,从而保证针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿之后,目标芯片内关键器件性能的均匀性提高效果。

127.基于与上述提高芯片内器件性能均匀性的方法同样的发明构思,本申请实施例还提供了一种提高芯片内器件性能均匀性的装置200。请参阅图6,本申请实施例提供的提高芯片内器件性能均匀性的装置200,包括曝光生产模块210、电性参数获取模块220、能量补偿值获取模块230和曝光能量补偿模块240。

128.曝光生产模块210,用于对预设有多个性能测试监控单元的目标芯片进行曝光生产,多个性能测试监控单元与目标芯片上的多个关键功能模块一一对应。

129.电性参数获取模块220,用于针对多个关键功能模块中的每个关键功能模块,通过与关键功能模块对应的性能测试监控单元获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数。

130.能量补偿值获取模块230,用于根据多个关键功能模块的电性参数,获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值。

131.曝光能量补偿模块240,用于针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿,以提高目标芯片内器件性能均匀性。

132.本申请实施例提供的提高芯片内器件性能均匀性的装置200还可以包括目标位置确定模块和关键功能模块设置模块。

133.目标位置确定模块,用于确定出目标芯片上与多个关键功能模块对应的多个目标位置。

134.关键功能模块设置模块,用于分别在多个目标位置设置多个性能测试监控单元,以使多个性能测试监控单元与多个目标位置一一对应,且针对多个性能测试监控单元中的每个性能测试监控单元,性能测试监控单元能够应用联合测试行为组织协议,通过晶圆良率测试方法监测自身的电性指标,以表征对应功能关键功能模块的电性参数。

135.本申请实施例中,曝光生产模块210可以包括原始曝光能量值获取单元和曝光生产单元。

136.原始曝光能量值获取单元,用于获取目标芯片的原始曝光能量值。

137.曝光生产单元,用于分别通过原始曝光能量值,对目标芯片上与多个关键功能模块对应的多个目标位置进行曝光,以实现对目标芯片的曝光生产。

138.本申请实施例中,能量补偿值获取模块230可以包括目标电性值获取单元、电性差异值获取单元和能量补偿值获取单元。

139.目标电性值获取单元,用于获得目标电性值。

140.电性差异值获取单元,用于针对多个关键功能模块中的每个关键功能模块,获取关键功能模块的电性参数与目标电性值之间的电性差异值,以获得与多个关键功能模块一一对应的多个电性差异值。

141.能量补偿值获取单元,用于针对多个关键功能模块中的每个关键功能模块,根据与关键功能模块对应的电性差异值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值,以获得目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值。

142.本申请实施例中,目标电性值获取单元可以包括第一目标电性值获取子单元。

143.第一目标电性值获取子单元,用于根据目标芯片所在待处理晶圆上的所有芯片上,多个关键功能模块的电性参数获得目标电性值。

144.本申请实施例中,第一目标电性值获取子单元可以包括第一计算单元和第二计算单元。

145.第一计算单元,用于计算出目标芯片所在待处理晶圆上的所有目标芯片上,位于同一目标位置的所有关键功能模块的电性参数的均值。

146.第二计算单元,用于根据与多个关键功能模块一一对应的多个均值,获得目标电性值。

147.本申请实施例中,第二计算单元可以包括第一计算子单元或第二计算子单元。

148.第一计算子单元,用于从与多个关键功能模块一一对应的多个均值中,获取中位数,作为目标电性值。

149.第二计算子单元,用于计算出与多个关键功能模块一一对应的多个均值的平均值,作为目标电性值。

150.本申请实施例中,目标电性值获取单元可以包括第二目标电性值获取子单元。

151.第二目标电性值获取子单元,用于获取预设固定值,以将预设固定值作为目标电性值。

152.本申请实施例中,能量补偿值获取单元可以包括第一敏感度获取单元和关键尺寸调整值获取单元。

153.第一敏感度获取单元,用于获取关键器件的沟道长度性能与关键器件的尺寸大小之间的敏感度,作为第一敏感度。

154.关键尺寸调整值获取单元,用于根据与关键功能模块对应的电性差异值和第一敏感度,获取与关键功能模块对应的关键器件沟道长度尺寸调整值。

155.实际补偿值获取单元,根据关键器件沟道长度尺寸调整值,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值。

156.本申请实施例中,实际补偿值获取单元可以包括第二敏感度获取单元和最终补偿值获取单元。

157.第二敏感度获取单元,用于获取曝光能量与关键器件的沟道长度尺寸大小之间的敏感度,作为第二敏感度。

158.最终补偿值获取单元,用于根据关键器件沟道长度尺寸调整值和第二敏感度,获得目标芯片上与关键功能模块对应的目标位置的能量补偿值。

159.由于本申请实施例提供的提高芯片内器件性能均匀性的装置200是基于与上述提高芯片内器件性能均匀性的方法同样的发明构思实现的,因此,提高芯片内器件性能均匀性的装置200中,每个软件模块的具体描述,均可参见上述提高芯片内器件性能均匀性的方法实施例中对应步骤的相关描述,此处不作赘述。

160.此外,本申请实施例还提供了一种计算机可读存储介质,计算机可读存储介质上存储有计算机程序,计算机程序被执行时,实现上述方法实施例所提供的提高芯片内器件性能均匀性的方法,具体可参见上述方法实施例,本申请实施例中对此不作赘述。

161.综上所述,在本申请提供的提高芯片内器件性能均匀性的方法的实施过程中,由

于目标芯片预设有多个性能测试监控单元,且针对多个关键功能模块中的每个关键功能模块,能够通过与关键功能模块对应的性能测试监控单元自动获得关键功能模块的电性参数,以分别获得多个关键功能模块的电性参数,相对于现有技术中,通过线宽扫描电子显微镜对目标芯片内各关键功能模块中具有的关键器件进行沟道长度尺寸大小表征结构的在线测量的方案而言,无需耗费大量人力和机时,因此,在本申请提供的提高芯片内关键器件性能均匀性方法的实施效率相对于现有技术而言,有较大的提升,此外,由于目标芯片上与多个关键功能模块对应的多个目标位置的能量补偿值,是根据多个关键功能模块最终的电性参数获得的,因此,能够综合考虑后续其他制程对目标芯片内关键器件电性的影响,而不局限于对目标芯片进行曝光生产过程中,栅极的光刻和蚀刻制程,从而保证针对多个目标位置中的每个目标位置,通过与目标位置对应的能量补偿值,对目标位置进行曝光能量补偿之后,目标芯片内关键器件性能的均匀性提高效果。

162.进一步地,本申请实施例提供的提高芯片内器件性能均匀性的装置、电子设备及计算机可读存储介质,具有与上述提高芯片内器件性能均匀性的方法相同的有益效果,本申请实施例对此不作赘述。

163.在本申请实施例所提供的几个实施方式中,应该理解到,所揭露的方法和装置,也可以通过其它的方式实现。以上所描述的装置实施例仅仅是示意性的,例如,附图中的流程图和框图显示了根据本申请的多个实施例的装置、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或代码的一部分,所述模块、程序段或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现方式中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个连续的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。此外,在本申请每个实施例中的各功能模块可以集成在一起形成一个独立的部分,也可以是每个模块单独存在,也可以两个或两个以上模块集成形成一个独立的部分。

164.此外,所述功能如果以软件功能模块的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本申请的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本申请每个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

165.还需要说明的是,在本申请文件中,诸如“第一”、“第二”、“第三”等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1