半导体装置及集成电路的制作方法

1.本发明涉及具有mosfet(metal oxide semiconductor field effect transistor)的半导体装置。

背景技术:

2.主要用于对电力用半导体装置的栅极进行驱动的用途的电力控制用ic(integrated circuit:集成电路)通常具有:低电位侧电路,其以接地(gnd)电位作为基准电位而进行动作;高电位侧电路,其以例如浮置电位等与gnd电位不同的电位作为基准电位而进行动作;以及

3.电平移位电路,其进行低电位侧电路与高电位侧电路之间的信号传输。

4.已知通过降低表面电场(resurf:reduced surface field)区域而将低电位侧电路区域与高电位侧电路区域分离,在该降低表面电场区域内形成构成电平移位电路的mosfet的技术(例如下述的专利文献1)。该mosfet需要保持与降低表面电场区域相同的耐压。另外,已知作为能够在耐压保持时降低表面电场区域完全耗尽而维持高耐压的条件,降低表面电场区域的垂直方向的深度(厚度)t[cm]与杂质浓度n[cm

‑3]之间的乘积的值受到限制(例如下述的专利文献2以及非专利文献1),根据非专利文献1,需要满足n

×

t<6.9

×

10

11

cm

‑2这一条件(以下,将该条件称为“降低表面电场条件”)。

[0005]

另外,具有低电位侧电路和高电位侧电路的ic需要用于对低电位侧电路以及高电位侧电路各自进行驱动的电源,但已知在ic内作为高电位侧电路的电源而设置自举电路的方式。已知作为该自举电路内的高耐压元件,使用在降低表面电场区域形成的mosfet的技术(例如下述的专利文献3)。

[0006]

专利文献1:日本专利3917211号公报

[0007]

专利文献2:美国专利第4292642号说明书

[0008]

专利文献3:日本专利5488256号公报

[0009]

非专利文献1:philips journal of research vol.35no.1 1980

[0010]

如上所述,就具有降低表面电场区域的半导体装置而言,需要在耐压保持时使降低表面电场区域完全耗尽而维持高耐压,所以降低表面电场区域的杂质浓度受到限制。这会妨碍在降低表面电场区域形成的mosfet的接通电阻的降低。另外,如果增加形成mosfet的降低表面电场区域的长度,则能够提高mosfet的耐压性能,但如果这样做,则mofet的接通电阻上升。即,在形成于降低表面电场区域的mosfet中,耐压性能的提高与接通电阻的降低存在折衷的关系。

技术实现要素:

[0011]

本发明就是为了解决这样的课题而提出的,其目的在于,改善在降低表面电场区域形成的mosfet的耐压性能的提高与接通电阻的降低之间的折衷关系。

[0012]

本发明涉及的半导体装置具有:半导体衬底,其形成有第1导电型的第1区域;第2

导电型的降低表面电场区域即第2区域,其形成于所述第1区域的表层部,将高电位侧电路与低电位侧电路分离;第2导电型的第3区域,其至少形成于所述第2区域的所述高电位侧电路侧的底部,与所述第2区域相比杂质的峰值浓度高;以及mosfet,其将所述第2区域作为漂移层,所述mosfet具有:第2导电型的漏极区域即第4区域,其形成于所述第2区域的表层部,与所述第2区域相比杂质的峰值浓度高;第2导电型的源极区域即第6区域,其在与所述第4区域相比更靠所述低电位侧电路侧,形成于在所述第2区域内设置的第1导电型的第5区域的表层部,或者形成于所述第1区域的表层部;第1热氧化膜,其在所述第4区域与所述第6区域之间,形成于所述第2区域的表面;以及第2导电型的第7区域,其形成于所述第1热氧化膜之下的所述第2区域的表层部,与所述第2区域相比杂质的峰值浓度高,所述第7区域的所述低电位侧电路侧的端部的位置与所述第3区域的所述低电位侧电路侧的端部的位置相比更靠近所述低电位侧电路。

[0013]

发明的效果

[0014]

就本发明涉及的半导体装置而言,由于第7区域,mosfet的接通电阻降低,另外,电场集中的部位被分散于第3区域和第7区域,由此耐压性能提高。因此,能够改善在降低表面电场区域形成的mosfet的耐压性能的提高与接通电阻的降低之间的折衷关系。

附图说明

[0015]

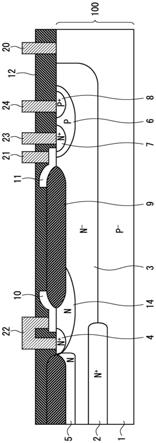

图1是在实施方式1涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。

[0016]

图2是表示以往的mosfet的结构的剖面图。

[0017]

图3是表示向以往的mosfet追加了第3区域(n型填埋扩散层2)的结构的图。

[0018]

图4是表示向以往的mosfet追加了第7区域(n型扩散层14)的结构的图。

[0019]

图5是表示针对实施方式1的mosfet以及以往的mosfet,对耐压保持时的半导体衬底的表面附近的水平方向的电位分布进行模拟的结果的图。

[0020]

图6是表示针对实施方式1的mosfet以及以往的mosfet,对耐压保持时的半导体衬底的表面附近的水平方向的电场分布进行模拟的结果的图。

[0021]

图7是表示针对实施方式1的mosfet以及以往的mosfet,对实施方式1的mosfet的第3区域(n型填埋扩散层2)附近的电场成为最大的部分的深度处的水平方向的电场分布进行模拟的结果的图。

[0022]

图8是表示针对实施方式1的mosfet以及图4的mosfet,对第7区域(n型扩散层14)的横向的长度与耐压性能之间的关系进行模拟的结果的图。

[0023]

图9是针对实施方式1的mosfet以及以往的mosfet,示出接通动作时的电流值以及耐压的测定结果的图。

[0024]

图10是在实施方式2涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。

[0025]

图11是表示n型扩散层15的结构例的图。

[0026]

图12是表示n型扩散层15的结构例的图。

[0027]

图13是在实施方式3涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。

[0028]

图14是表示对第7区域(n型扩散层14)的深度方向的杂质浓度分布进行模拟的结果的图。

[0029]

图15是在实施方式4涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。

[0030]

图16是表示对第1多晶硅层(多晶硅层10)向低电位侧电路侧延伸的长度与mosfet的耐压之间的关系进行模拟的结果的图。

[0031]

图17是在实施方式5涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。

[0032]

图18是表示高电位侧电路的例子的图。

[0033]

图19是表示实施方式6的半导体装置和周边的高电位侧电路区域的俯视图。

[0034]

图20是表示实施方式6的半导体装置、周边的高电位侧电路区域和横向型高耐压mosfet的俯视图。

[0035]

图21是表示实施方式7涉及的驱动ic的结构的图。

[0036]

图22是表示电平移位电路的结构的图。

[0037]

图23是表示实施方式7涉及的驱动ic的变形例的图。

[0038]

图24是表示实施方式8涉及的驱动ic的结构的图。

[0039]

图25是在实施方式9涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。

[0040]

标号的说明

[0041]

1 p型扩散层(第1区域),2 n型填埋扩散层(第3区域),3 n型扩散层(第2区域),4 n型扩散层(第4区域),5 n型扩散层(第8区域),6 p型扩散层(第5区域),7 n型扩散层(第6区域),8 p型扩散层,9热氧化膜,10多晶硅层(第1多晶硅层),11多晶硅层(第2多晶硅层),12绝缘膜,14 n型扩散层(第7区域),15 n型扩散层(第9区域),16 n型扩散层(第3区域),20基准电位电极,21栅极电极,22漏极电极,23源极电极,24背栅电极,100半导体衬底,201半导体衬底,202 n型扩散层(第2区域),203 n型填埋扩散层(第3区域),204低电位侧电路的电极,205高电位侧电路的电极,206、207 mosfet,301高电位侧电路,302低电位侧电路,303电平移位电路,304a 高电位侧电路的电源,304b 低电位侧电路的电源,305a 上侧开关元件,305b 下侧开关元件,306电源,307限制电阻,308自举二极管,309自举电容器,310、401 mosfet,402、403电阻元件。

具体实施方式

[0042]

<实施方式1>

[0043]

图1是在实施方式1涉及的半导体装置的降低表面电场区域形成的横向型高耐压n沟道mosfet的剖面图。以下,除非另有说明,“mosfet”是指在降低表面电场区域形成的横向型mosfet。另外,将图1中的左侧的方向定义为半导体装置的内侧,将右侧的方向定义为半导体装置的外侧。另外,以下,将第1导电型设为p型、将第2导电型设为n型而进行说明。但是,也可以与此相反地,将第1导电型设为n型、将第2导电型设为p型。

[0044]

实施方式1涉及的半导体装置是使用形成有作为第1区域的p型扩散层1的p型半导体衬底100而形成的。在半导体衬底100形成有后述的各区域,在以下的说明中,是指未形成

这些区域而残留下来的半导体衬底100的p型的区域,称为“p型扩散层1”。这里,将半导体衬底100的材料设为硅(si),但也可以是碳化硅(sic)或氮化镓(gan)等宽带隙半导体。使用了宽带隙半导体的半导体装置与使用了硅的以往的半导体装置相比,高电压、大电流、高温下的动作表现优秀。

[0045]

在半导体衬底100的表层部作为第2区域而形成有n型扩散层3。在图1中虽未图示,但在n型扩散层3的内侧形成有高电位侧电路,在n型扩散层3的外侧形成有低电位侧电路,n型扩散层3作为将高电位侧电路与低电位侧电路分离的降低表面电场区域而起作用。即,如果将n型扩散层3的杂质浓度设为n[cm

‑3]、将深度设为t[cm],则满足n

×

t<6.9

×

10

11

cm

‑2这一条件,即降低表面电场条件。

[0046]

在n型扩散层3的至少内侧(高电位侧电路侧)的底部,作为第3区域而形成有与n型扩散层3相比杂质的峰值浓度高的n型填埋扩散层2。n型填埋扩散层2具有下述效果,即,抑制高电位侧电路内的元件的纵向的寄生动作、以及防止在耐压保持时n型扩散层3内的耗尽层向高电位侧电路内延伸而对高电位侧电路内的元件的动作带来不良影响。

[0047]

实施方式1涉及的半导体装置具有将n型扩散层3作为漂移层的横向型高耐压n沟道mosfet。以下,对该mosfet的结构进行说明。

[0048]

在n型扩散层3的表层部形成有作为第4区域的n型扩散层4和作为第5区域的p型扩散层6。n型扩散层4与n型扩散层3相比杂质的峰值浓度高,成为mosfet的漏极区域。在p型扩散层6的表层部形成有作为第6区域的n型扩散层7和与p型扩散层6相比杂质的峰值浓度高的p型扩散层8。n型扩散层7成为mosfet的源极区域。p型扩散层6成为mosfet的背栅,p型扩散层8成为用于将p型扩散层6与后述的背栅电极24电连接的接触区域。

[0049]

在n型扩散层4与p型扩散层6之间(即n型扩散层4与n型扩散层7之间)的n型扩散层3的表面、以及比n型扩散层4更靠内侧的n型扩散层3的表面形成有热氧化膜9。n型扩散层4与p型扩散层6之间的热氧化膜9是第1热氧化膜,比n型扩散层4更靠内侧的热氧化膜9是第2热氧化膜。

[0050]

在n型扩散层4与p型扩散层6之间的热氧化膜9之下的n型扩散层3的表层部作为第7区域而形成有与n型扩散层3相比杂质的峰值浓度高的n型扩散层14。n型扩散层14不满足降低表面电场条件。即,如果将n型扩散层14的杂质浓度设为n[cm

‑3]、将深度设为t[cm],则满足n

×

t>6.9

×

10

11

cm

‑2的关系。另外,n型扩散层14的外侧的端部的位置与n型填埋扩散层2的外侧的端部的位置相比更靠近低电位侧电路。即,n型扩散层14延伸至与n型填埋扩散层2相比更靠外侧。n型扩散层14也可以与n型填埋扩散层2接触,但这里使n型扩散层14落在n型扩散层3内,使n型扩散层14与n型填埋扩散层2分离。另外,在图1中,n型扩散层14与n型扩散层4重叠地形成,但也可以使它们不重叠。

[0051]

在比n型扩散层4更靠内侧的热氧化膜9之下,为了防止场反转,形成有n型扩散层5作为第8区域。也可以省略该n型扩散层5。

[0052]

另外,n型扩散层4与p型扩散层6之间的热氧化膜9的内侧的端部之上被作为第1多晶硅层的多晶硅层10覆盖,该热氧化膜9的外侧的端部之上被作为第2多晶硅层的多晶硅层11覆盖。多晶硅层11从n型扩散层4与p型扩散层6之间的热氧化膜9的端部延伸至n型扩散层7之上,在该热氧化膜9与n型扩散层7之间将n型扩散层3以及p型扩散层6的表面覆盖。

[0053]

在半导体衬底100的表面之上形成有绝缘膜12。另外,用于将p型扩散层1的电位固

定为基准电位的基准电位电极20、mosfet的栅极电极21、源极电极23、漏极电极22以及背栅电极24以各自的一部分被绝缘膜12掩埋的方式而形成在绝缘膜12之上。基准电位电极20与p型扩散层1连接。栅极电极21设置于多晶硅层11之上,与n型扩散层7和n型扩散层3之间的p型扩散层8的表面相对。在mosfet的接通动作时,在栅极电极21之下的p型扩散层8的部分形成沟道。源极电极23与mosfet的源极区域即n型扩散层7连接。漏极电极22与mosfet的漏极区域即n型扩散层4连接,并且漏极电极22的一部分到达多晶硅层10的上表面。背栅电极24与p型扩散层8连接,通过p型扩散层8而与背栅即p型扩散层6电连接。

[0054]

实施方式1涉及的半导体装置具有以下特征,即,具有n型填埋扩散层2以及n型扩散层14,n型扩散层14的外侧(低电位侧电路侧)的端部的位置与n型填埋扩散层2的外侧的端部的位置相比更靠近低电位侧电路。以下,对通过该特征得到的效果进行说明。

[0055]

以往的半导体装置如图2所示,是不具有n型填埋扩散层2以及n型扩散层14的结构。就图2的半导体装置而言,在漏极电极22成为高电位的耐压保持时,耗尽层从n型扩散层3与p型扩散层1之间的pn结部起开始延伸。此时,由于降低表面电场效应,n型扩散层3完全耗尽,由此实现mosfet的高耐压化。

[0056]

例如,如图3所示,当在图2的半导体装置设置了第3区域即n型填埋扩散层2的情况下,如上所述,得到抑制高电位侧电路的元件的纵向的寄生动作的效果,以及防止在耐压保持时耗尽层给高电位侧电路的元件的动作带来不良影响的效果。但是,在耐压保持时n型填埋扩散层2没有完全耗尽,电场集中于n型填埋扩散层2的部分,因此mosfet的耐压性能下降。

[0057]

另外,例如,如图4所示,当在图2的半导体装置设置了第7区域即n型扩散层14的情况下,使n型扩散层14的纵向(与n型扩散层3的表面垂直的方向)的深度以及横向(从高电位侧电路朝向低电位侧方向的方向)的长度变得越大,则越能够减小mosfet的接通电阻。但是,在耐压保持时,电场集中于n型扩散层14的端部,因此如果增大n型扩散层的深度以及长度,则耐压性能恶化。即,在由n型扩散层14实现的mosfet的接通电阻的降低效果与mosfet的耐压性能之间存在折衷的关系。

[0058]

另一方面,就实施方式1涉及的半导体装置而言,在n型扩散层3内形成有n型填埋扩散层2和n型扩散层14这两者。在这种情况下,由于n型扩散层14,mosfet的接通电阻降低,并且在n型填埋扩散层2以及n型扩散层14这两者处产生电场集中,产生电场集中的部位被分散开,由此mosfet的耐压性能提高。因此,与图2~图4的半导体装置相比较,耐压性能与接通电阻之间的折衷关系得到改善。

[0059]

但是,在n型扩散层14的长度短的情况下,电场基本不集中于n型扩散层14,电场不向n型填埋扩散层2和n型扩散层14分散,在n型填埋扩散层2产生的电场变强,因此不能充分地得到上述的效果。因此,就实施方式1的半导体装置而言,以电场也集中于n型扩散层14的方式,增大n型扩散层14的长度,使n型扩散层14的外侧的端部位于与n型填埋扩散层2的外侧的端部相比更靠外侧处。此外,在实施方式1中,最能提高耐压性能的条件是在耐压保持时n型填埋扩散层2的最大电场强度与n型扩散层14的最大电场强度相等。

[0060]

图5是针对实施方式1的mosfet以及以往的mosfet,对耐压保持时的半导体衬底100的表面附近的水平方向的电位分布进行模拟的结果。在图5中,实线的曲线是实施方式1的mosfet的电位分布,虚线的曲线是以往的mosfet的电位分布。实线的曲线中的左端的平

坦区域对应于n型扩散层14的部分。如图5所示,就实施方式1的mosfet而言,n型扩散层14的部分的杂质浓度高,因此该部分的电位比以往的mosfet高。所以,可知就实施方式1的mosfet而言,在耐压保持时,电场不仅集中于n型填埋扩散层2的部分,也集中于n型扩散层14的部分。

[0061]

图6是针对实施方式1的mosfet以及以往的mosfet,对耐压保持时的半导体衬底100的表面附近的水平方向的电场分布进行模拟的结果。另外,图7是针对实施方式1的mosfet以及以往的mosfet,对实施方式1的mosfet的n型填埋扩散层2附近的电场成为最大的部分的深度处的水平方向的电场分布进行模拟的结果。在图6以及图7中,实线的曲线是实施方式1的mosfet的电场分布,虚线的曲线是以往的mosfet的电场分布。此外,在图5~图7的各模拟中,耐压保持时的偏置电位设定为全部相同。

[0062]

在图6中,在实施方式1的mosfet的曲线中出现电场强度的峰值的部分对应于n型扩散层14的外侧的端部。这样,在n型扩散层14的外侧的端部产生电场集中,由此,如图7所示,实施方式1的mosfet的电场的最大值比以往的mosfet低。因此,在实施方式1的mosfet中,得到比以往的mosfet高的耐压性能。

[0063]

图8是针对在实施方式1的mosfet以及以往的mosfet设置了n型扩散层14的结构(图4),对n型扩散层14的横向的长度与耐压性能之间的关系进行模拟的结果。在图8中,实线的曲线是实施方式1的mosfet的耐压特性,虚线的曲线是图4的mosfet的耐压特性。在具有n型填埋扩散层2和n型扩散层14这两者的实施方式1的mosfet中,与仅具有n型扩散层14的图4的mosfet相比较,耐压性能与接通电阻之间的折衷关系得到改善。

[0064]

图9是针对实施方式1的mosfet以及以往的mosfet,示出接通动作时的电流值以及耐压的测定结果的图。在图9中,黑点是实施方式1的mosfet的测定结果,白点是以往的mosfet的测定结果。此外,图9的曲线的纵轴以及横轴通过以往的mosfet的测定值而进行了标准化。实施方式1的mosfet与以往的mosfet相比较,耐压性能提高,并且接通电阻降低,确认了与上述的模拟结果相同的倾向。

[0065]

如上所述,根据实施方式1涉及的半导体装置,在降低表面电场区域即n型扩散层3内具有与降低表面电场区域相比杂质的峰值浓度更高的n型填埋扩散层2(第2区域)以及n型扩散层14(第7区域)这两者,由此能够改善将n型扩散层3作为漂移层的mosfet中的接通电阻的降低与耐压性能的提高之间的折衷关系。

[0066]

<实施方式2>

[0067]

图10是在实施方式2涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。图10的结构相比于图1的结构,在第7区域即n型扩散层14的外侧(低电位侧电路侧)作为第9区域而设置了杂质的峰值浓度比n型扩散层14低、比n型扩散层3高的n型扩散层15。

[0068]

实施方式2的mosfet具有n型扩散层15,由此与实施方式1的mosfet相比,漂移层的杂质浓度局部地变高。因此,在实施方式2的mosfet中,与实施方式1相比,接通电阻降低。

[0069]

另外,n型扩散层15与n型扩散层14相比杂质浓度低、容易耗尽。因此,能够通过配置n型扩散层15而抑制耐压保持时的电场的集中。因此,与实施方式1相比,能够提高耐压性能。

[0070]

如上述所示,根据实施方式2,与实施方式1相比,得到mosfet的接通电阻的降低以及耐压性能的提高的效果。因此,与实施方式1相比,能够进一步改善mosfet中的接通电阻

的降低与耐压性能的提高之间的折衷关系。

[0071]

此外,n型扩散层15内的杂质浓度的分布也可以不是恒定的,例如也可以与内侧的部分相比使外端的部分为低浓度。另外,在这种情况下,n型扩散层15也可以与n型扩散层14重叠地形成,例如,n型扩散层15也可以是以与整个n型扩散层14重叠的方式制作的。换言之,也可以将n型扩散层14内的杂质浓度的分布设为:与内侧的部分相比,外端的部分为低浓度。

[0072]

另外,在图10中,将n型扩散层15设为1个一体的区域,但n型扩散层15也可以由离散地形成的多个区域构成。例如,也可以如图11的斜视图所示,将n型扩散层15设为多个线状的区域,也可以如图12的斜视图所示,将n型扩散层15设为多个点状的区域。在这种情况下,构成n型扩散层15的多个区域各自的杂质浓度能够通过其图案形状(线或点的尺寸、间隔)而进行调整(参照后述的图14)。因此,在使n型扩散层15由离散的多个区域构成的情况下,能够使n型扩散层14和n型扩散层15在相同的杂质注入工序中一起形成。另外,在这种情况下,构成n型扩散层15的多个区域各自的杂质浓度与n型扩散层14相等或者比n型扩散层14低。

[0073]

<实施方式3>

[0074]

图13是在实施方式3涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。在实施方式3中,在n型扩散层4与p型扩散层6之间的热氧化膜9之下设置的第7区域即n型扩散层14和在与n型扩散层4相比更靠内侧的热氧化膜9之下设置的第8区域即n型扩散层5是在相同的杂质注入工序中制作的。在图13中,n型扩散层14与n型扩散层5相连,但它们也可以分离。

[0075]

在本实施方式中,n型扩散层14和n型扩散层5是在相同的杂质注入工序中制作的,因此n型扩散层5的杂质浓度与n型扩散层14的杂质浓度基本上相等。但是,也可以与实施方式2的n型扩散层15同样地,通过使n型扩散层14或者n型扩散层5由离散的多个区域构成,从而n型扩散层14的杂质浓度与n型扩散层5的杂质浓度彼此不同。优选如果将n型扩散层5的杂质浓度设为n1,将n型扩散层14的杂质浓度设为n2,则满足0.1

×

n1<n2<2

×

n1的关系。

[0076]

图14是对n型扩散层14的深度方向的杂质浓度分布进行模拟的结果。实线的曲线是使在形成n型扩散层14的杂质注入工序中使用的注入掩模的开口足够大的情况下的分布,虚线的曲线是将该注入掩模的开口的尺寸设为0.5μm的情况下的分布。图14的曲线的横轴是从热氧化膜9的表面算起的向垂直方向的距离,纵轴是n型扩散层14的杂质浓度的相对值(通过实线的曲线的峰值而标准化后的值)。如果将注入掩模的开口的尺寸设为0.5μm,则能够将杂质浓度降低为注入掩模的开口足够大的情况下的1/5倍左右。这样,n型扩散层14以及n型扩散层5的杂质浓度能够通过调整注入掩模的开口的尺寸,即杂质注入区域的尺寸而进行控制。

[0077]

如实施方式3所示,n型扩散层14以及n型扩散层5能够在相同的杂质注入工序中形成,由此能够减少杂质注入工序数,能够实现半导体装置的制造工序的简化。此外,实施方式3也可以与实施方式2进行组合。

[0078]

<实施方式4>

[0079]

图15是在实施方式4涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。就实施方式4的mosfet而言,将n型扩散层4与p型扩散层6之间的热氧化膜9的内侧的端

部覆盖的第1多晶硅层即多晶硅层10的外侧(低电位侧电路侧)的端部与在该热氧化膜9之下形成的n型扩散层14的外侧的端部相比,位于更靠近低电位侧电路处。即,多晶硅层10与n型扩散层14相比,延伸至外端。

[0080]

n型扩散层14与降低表面电场区域即n型扩散层3相比杂质浓度高,因此如图5所示,在对漏极电极22施加高电压的耐压保持时,n型扩散层14处的电压降小,n型扩散层14与其周围的n型扩散层3相比成为高电位。如果在该影响下,热氧化膜9的电位与n型扩散层3的电位的差异变大,则n型扩散层14的外侧的端部的电场变大,mosfet的耐压性能下降。在实施方式4中,如图15所示,与n型扩散层14相比,使多晶硅层10向更外侧较长地延伸,由此,抑制n型扩散层14与热氧化膜9之间的电位的差异。因此,根据实施方式4,能够提高mosfet的耐压。

[0081]

图16是对第1多晶硅层即多晶硅层10向低电位侧电路侧延伸的长度与mosfet的耐压之间的关系进行模拟的结果。图16的横轴是以n型填埋扩散层2的外侧的端部为基准的n型扩散层14的长度,与图16所描绘的纵轴平行的实线表示n型扩散层14的外侧的端部的位置。根据图16也可知,在与n型扩散层14相比而使多晶硅层10向更外侧较长地延伸时,mosfet的耐压提高。此外,实施方式4也可以与实施方式2、3进行组合。

[0082]

<实施方式5>

[0083]

图17是在实施方式5涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。在实施方式1(图1)中,mosfet的源极区域即n型扩散层7形成于在n型扩散层3内设置的p型扩散层6内。与此相对,在实施方式5中,如图17所示,省略p型扩散层6,将n型扩散层7形成于n型扩散层3的外侧的p型扩散层1内。在图17的结构中,在多晶硅层11之上设置的栅极电极21与n型扩散层7和n型扩散层3之间的p型扩散层1的表面相对,在mosfet的接通动作时,在栅极电极21之下的p型扩散层1的部分形成沟道。

[0084]

实施方式1的结构包含由p型扩散层6、n型扩散层3以及p型扩散层1形成的寄生pnp晶体管,担忧由于流过该寄生pnp晶体管的电流(寄生电流)而使耗费电力变大。与此相对,在实施方式5的结构中,不形成这样的寄生pnp晶体管,不流过寄生电流,因此能够实现耗费电力的降低。

[0085]

另外,在实施方式1的结构中,为了将p型扩散层1与p型扩散层6分离,需要充分地确保它们之间的距离,存在mosfet的尺寸变大的问题。与此相对,在实施方式5的结构中,不需要这样的分离,因此还得到能够减小mosfet的尺寸这一效果。此外,实施方式5也可以与实施方式2、3、4进行组合。

[0086]

<实施方式6>

[0087]

图18是表示以往的半导体装置的高电位侧电路区域的俯视图。如图18所示,就以往的半导体装置而言,在p型的半导体衬底201内形成有第2区域(降低表面电场区域)即n型扩散层202,在n型扩散层202内形成有第3区域即n型填埋扩散层203。在n型扩散层202的外侧形成有被供给低电位侧电路的基准电位(gnd电位)的电极204,在n型扩散层202内形成有被供给与gnd电位不同的高电位侧电路的基准电位的电极205。在电极205的电位上升时,n型扩散层202完全耗尽,由此gnd电位与高电位侧电路的基准电位分离。

[0088]

图19是表示实施方式6的半导体装置的高电位侧电路区域的俯视图。与图18同样地,在p型的半导体衬底201内形成有降低表面电场区域即n型扩散层202,在n型扩散层202

内形成有n型填埋扩散层203,在n型扩散层202的外侧形成有被供给低电位侧电路的基准电位(gnd电位)的电极204。在实施方式6的半导体装置,在作为将高电位侧电路包围的降低表面电场区域的n型扩散层202的部分(图19中的阴影部)形成有实施方式1涉及的mosfet 206。即,例如图19所示的沿a

‑

b线的剖面成为图1所示的结构。

[0089]

通过设为图19这样的布局,从而不新设置用于形成mosfet的区域就能够搭载mosfet。另外,能够通过在实施方式1中所说明的效果而提高高电位侧电路与gnd电位间的耐压。

[0090]

在将高电位侧电路包围的n型扩散层202的部分(图19中的阴影部)形成的mosfet也可以是实施方式2、3、4、5的mosfet。另外,也可以如图20所示,在高电位侧电路与低电位侧电路之间的部分形成mosfet 206和与其电分离的另外的mosfet 207。

[0091]

<实施方式7>

[0092]

图21是表示实施方式7涉及的驱动ic的结构的图。该驱动ic对构成半桥电路的开关元件进行驱动,具有:高电位侧电路301,其对上侧开关元件305a进行驱动;低电位侧电路302,其对下侧开关元件305b进行驱动;以及电平移位电路303,其在高电位侧电路301与低电位侧电路302之间对信号进行传输。向高电位侧电路301从电源304a供给驱动用电源,向低电位侧电路302从电源304a供给驱动用电源。另外,从电源306对上侧开关元件305a以及下侧开关元件305b供给电位。

[0093]

图22是电平移位电路303的电路图。电平移位电路303由在高电位侧电路301与gnd电位(低电位侧电路302的基准电位)之间串联连接的电阻元件402、mosfet 401以及电阻元件403构成。从低电位侧电路302输出的信号对mosfet 401的接通、断开进行切换,在电阻元件402产生的电压信号被输入至高电位侧电路301。由此,电平移位电路303能够将高电位侧电路301的基准电位与低电位侧电路302的基准电位分离,并且从低电位侧电路302向高电位侧电路301传输信号。

[0094]

在实施方式7中,作为电平移位电路303的mosfet 401而使用实施方式1的mosfet。实施方式1的mosfet的耐压性能高、接通电阻低,因此能够使电平移位电路303在更广范围的电位下进行动作,并且能够减小耗费电力。此外,作为电平移位电路303的mosfet 401,也可以使用实施方式2、3、4、5的mosfet。另外,高电位侧电路301、低电位侧电路302以及电平移位电路303可以形成于相同的芯片内,也可以各自分离至单独的芯片。

[0095]

在图21中,也可以取代高电位侧电路301的电源304a而使用自举电路。图23是使用自举电路作为高电位侧电路301的电源的例子。

[0096]

自举电路由限制电阻307、自举二极管308和自举电容器309构成。限制电阻307以及自举二极管308在低电位侧电路302的电源304b与高电位侧电路301的电源输入端子之间串联连接。自举电容器309连接在上侧开关元件305a和下侧开关元件305b之间的连接节点与高电位侧电路301的电源输入端子之间。

[0097]

上侧开关元件305a与下侧开关元件305b之间的连接节点的电位即vs电位伴随上侧开关元件305a以及下侧开关元件305b的接通、断开而在电源306的电位与gnd电位之间迁移。在vs电位变为gnd电位时,来自电源304b的电荷通过自举二极管308而被供给至自举电容器309,自举电容器309被充电。然后,如果vs电位变化为电源306的电位,则从自举电容器309向高电位侧电路301的电源输入端子供给电荷,因此自举电容器309作为高电位侧电路

301的电源而起作用。此时,自举二极管308用于防止向电源304b流入电流。限制电阻307是用于将对自举电容器309进行充电的电流限制为所期望的值的电阻。

[0098]

<实施方式8>

[0099]

图24是实施方式8涉及的驱动ic的结构图。实施方式8的驱动ic的结构是将图23的限制电阻307以及自举二极管308置换为实施方式1的mosfet 310,将该mosfet 310用作自举二极管。

[0100]

mosfet 310如实施方式5所示,形成于将高电位侧电路301与低电位侧电路302分离的降低表面电场区域。由此,就具有高电位侧电路301以及低电位侧电路302的驱动ic而言,无需使用其它高耐压元件就能够构成作为高电位侧电路301的电源而起作用的自举电路。其结果,能够促进包含半桥电路的驱动ic的驱动装置的小型化。此外,图24的mosfet 310也可以是实施方式2、3、4、5的mosfet。另外,高电位侧电路301、低电位侧电路302以及电平移位电路303可以形成于相同的芯片内,也可以各自分离至单独的芯片。

[0101]

<实施方式9>

[0102]

图25是在实施方式9涉及的半导体装置的降低表面电场区域形成的mosfet的剖面图。图25的结构相比于图1的结构,作为第3区域,取代n型填埋扩散层2而形成与n型扩散层3相比杂质的峰值浓度高的n型扩散层16。n型填埋扩散层2被填埋于半导体衬底100的内部(n型扩散层3的底部附近),但n型扩散层16是从半导体衬底100的表层部直至n型扩散层3的底部形成的。n型扩散层16的深度也可以比n型扩散层14深。

[0103]

另外,n型扩散层16不满足降低表面电场条件。即,如果将n型扩散层16的杂质浓度设为n[cm

‑3]、将深度设为t[cm],则满足n

×

t>6.9

×

10

11

cm

‑2的关系。因此,在实施方式9中,在耐压保持时n型扩散层16没有完全耗尽,电场集中于其外侧的端部。因此,电场集中于n型扩散层14和n型扩散层16这两者,因此得到与实施方式1相同的作用、效果。在本实施方式中,同样地也可以省略n型扩散层5。

[0104]

在实施方式9中,不需要形成呈被填埋于半导体衬底100的内部的构造的扩散层。因此,能够通过通常的杂质扩散工序而形成具有与实施方式1相同的作用、效果的半导体装置。此外,针对实施方式2、3、4、5、6、7、8的半导体装置,同样地也可以应用实施方式9,将n型填埋扩散层2置换为n型扩散层16。

[0105]

此外,能够对各实施方式自由地进行组合,或者对各实施方式适当地进行变形、省略。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1