具备静电保护能力的屏蔽栅沟槽MOSFET器件及制造方法与流程

具备静电保护能力的屏蔽栅沟槽mosfet器件及制造方法

技术领域

1.本发明涉及mosfet器件及其制造方法,具体涉及一种具备静电保护能力的屏蔽栅沟槽mosfet器件及制造方法。

背景技术:

2.mosfet的栅极和源极之间存在一层薄薄的栅氧化层,其在器件封装、运输、装配及使用过程中容易受到外来的意外高电压冲击,在栅极产生一个高电场,使得栅介质在高电场下发生绝缘击穿,从而使器件失效。因此在一些实际应用中,对mosfet的栅极提供静电放电(esd)的保护是必要的。通常的做法是,在mosfet的栅极和源极之间并联二极管保护单元,当静电放电(esd)产生的电压高于所述二极管的击穿电压时(所述二极管的击穿电压低于mosfet的栅氧化层的击穿电压值),二极管发生雪崩击穿,静电能量从二极管释放掉,从而避免了栅极和源极之间的栅氧化层受到破坏。为了降低电路板的尺寸及物料成本,通常将提供esd保护功能的二极管集成于mosfet器件中。

3.在申请号201910722915.6,名称为集成esd保护的屏蔽栅沟槽mosfet及制造方法的专利文献中,其mosfet屏蔽栅的多晶硅,和形成mosfet的esd保护二极管的多晶硅,是同一层多晶硅(第一层多晶硅),而形成mosfet的栅极的多晶硅,是第二层多晶硅。但是,这篇专利文献所公开的方法具有很大缺陷,主要在于:

4.1.图1为现有技术中淀积氧化层的示意图。图2为氧化层刻蚀的示意图。图3为屏蔽栅与控制栅间氧化层形成的示意图。如图2所示,在氧化层刻蚀的时候,此时esd保护区域的侧壁易形成氧化层残留。如果在回刻时加大刻蚀力度,可能导致屏蔽栅层间氧化层h1过小,而层间氧化层起到了对控制栅电极和屏蔽栅电极的隔离作用,若厚度不足或出现空洞,将对器件igss(栅源短路电流)产生不良影响。

5.2.如果为了解决上述的可能导致导致屏蔽栅层间氧化层h1过小的问题,可以考虑增加栅间氧化层厚度,这样会有两个结果a、trench深度h2不变,则栅极多晶硅h3减小,屏蔽效果差;b、栅极多晶硅h3保持不变,trench深度h2增加,则会影响器件bv(漏源击穿电压)/idss(饱和漏源电流)性能。

6.3.另一方面,采用第一层多晶硅制作屏蔽栅电极和esd保护区域,总会在硅平台区域边缘由于刻蚀不净导致多晶硅残留,在版图上,则体现为条状,图4为多晶硅残留示意图。如图4所示,这样的残留在后续的工艺中易脱落,导致栅源短路,影响良率。

技术实现要素:

7.针对现有技术的不足,本发明公开了一种具备静电保护能力的屏蔽栅沟槽mosfet器件及制造方法。

8.本发明所采用的技术方案如下:

9.一种具备静电保护能力的屏蔽栅沟槽mosfet器件的制作方法,包括;

10.步骤s1.提供衬底,于衬底上表面形成外延层;在外延层上刻蚀得到第一沟槽和第

二沟槽;

11.步骤s2.于第一沟槽和第二沟槽之内形成第一介质层和第一多晶硅层;且在第一沟槽和第二沟槽之内,第一多晶硅层的高度均低于第一沟槽和第二沟槽的顶端;第一介质层在外延层和第一多晶硅层之间;

12.步骤s3.回刻第二沟槽中的上部区域的第一介质层和第一多晶硅层,并在第二沟槽的下部区域的上表面生成顶部介质层,使得在下部区域的第一多晶硅层区块三被围住;之后生成第二多晶硅层,第二多晶硅层包括填充于第二沟槽的上部区域的第二多晶硅层区块二和位于第一沟槽侧边的第二多晶硅层区块四;

13.步骤s4.在第二沟槽旁侧形成体区;在体区的表层形成源区,同步的,在第二多晶硅层区块四上形成多个npn结构的esd保护二极管;

14.步骤s5.形成第二介质层;在第二介质层之上形成源极金属和栅极金属;在衬底下表面形成漏极金属。

15.其进一步的技术方案为,所述步骤s2包括:

16.步骤s21.于第一沟槽的内表面、第二沟槽的内表面及外延层的上表面形成第一介质层,在第一介质层之上沉积第一多晶硅层;去除位于外延层的上表面的第一介质层及位于外延层的上表面的第一多晶硅层,保留第一沟槽和第二沟槽之内的第一介质层和第一多晶硅层;

17.步骤s22.刻蚀除去位于第二沟槽内的上部区域的第一介质层和第一多晶硅层,留下第二沟槽内的下部区域的第一介质层区块三及第一多晶硅层区块三;在第二沟槽内沉积顶部介质层,顶部介质层和第一介质层区块三将第一多晶硅层区块三封闭包围。

18.其进一步的技术方案为,所述步骤s3包括:

19.步骤s31.在外延层的上表面以及第二沟槽的侧壁通过热氧化工艺形成氧化层;之后于外延层之上的氧化层的表面以及第二沟槽之内的氧化层之间形成第二多晶硅层;

20.步骤s32.使用掩膜层在第一沟槽旁侧的第二多晶硅层中保留第二多晶硅层区块一;在第二多晶硅层区块一以外的其他区域去除位于外延层的上表面的氧化层和位于外延层上方的第二多晶硅层;保留位于第二沟槽的侧壁的氧化层作为栅氧化层,对第二多晶硅层区块一的进行p型轻掺杂形成p型轻掺杂的第二多晶硅层区块四。

21.其进一步的技术方案为,在所述步骤s4中,在第二沟槽旁侧形成p型轻掺杂的体区;在体区的表层形成n型重掺杂的源区,同步的,在第二多晶硅层区块四中进行n型重掺杂形成多个npn结构的esd保护二极管。一种根据如上任一项所述的制作方法所制作的mosfet器件,mosfet器件包括衬底;衬底为n型;衬底之上形成n型的外延层;在外延层上具有第一沟槽和第二沟槽;

22.在第一沟槽的内壁有第一介质层区块一;在第一介质层区块一之间填充有第一多晶硅层区块一;且第一介质层区块一的上表面低于第一沟槽的顶面,第一介质层区块一位于第一多晶硅层区块一和外延层之间;第一多晶硅层区块一作为mosfet器件的一个屏蔽栅;

23.在第二沟槽的下部区域有被第一介质层区块三及顶部介质层包围的第一多晶硅层区块三;在顶部介质层之上的上部区域的侧壁覆盖有栅氧化层,在栅氧化层之间填充有n型重掺杂的第二多晶硅层区块三;第二多晶硅层区块三作为mosfet器件的控制栅极;

24.在第二沟槽的侧部设置有p型轻掺杂的体区;体区的表层之中形成n型重掺杂的源区;源区作为mosfet器件的源极;

25.在第一沟槽的侧部有esd保护二极管;esd保护二极管的两端并联于mosfet器件的一个屏蔽栅和源极;

26.在外延层以及形成于外延层中的各个结构的上表面覆盖有第二介质层;在第二介质层之上覆盖有源极金属和栅极金属;在衬底的下表面覆盖漏极金属。

27.其进一步的技术方案为,源极金属有三个端头,源极金属的第一端头和源极金属的第二端头穿过第二介质层连接至源区,源极金属的第三端头穿过第二介质层连接至esd保护二极管的一端;栅极金属有两个端头;栅极金属的第一端头穿过第二介质层连接至第一多晶硅层区块一,栅极金属的第二端头连接至esd保护二极管的另一端。

28.其进一步的技术方案为,esd保护二极管为由p型轻掺杂的第二多晶硅层区块四和在第二多晶硅层区块四之上间隔进行n型重掺杂所形成的第二多晶硅层区块五组成多个二极管串联而成。

29.本发明的有益效果如下:

30.本发明提供了一种具备静电保护能力的屏蔽栅沟槽mosfet,其以两层多晶硅、更低成本的方法制程实现,在本发明中,形成mosfet屏蔽栅的多晶硅,是第一层多晶硅(第一多晶硅层),而形成mosfet的栅极的多晶硅和形成mosfet的esd保护二极管的多晶硅,是第二层多晶硅(第二多晶硅层);整个制造流程中只需要两层多晶硅方法,即可实现集成esd保护的屏蔽栅沟槽mosfet之器件结构,比传统方法减少了一层多晶硅方法,实现方法更简单,降低了制造复杂度和方法成本。

31.更重要的,减少了由于第一次注入多晶硅形成esd调制区域导致的台阶以及由于窗口面积小导致的填充空隙,减少了栅极与漏极之间的漏电风险,增加了器件的可靠性,也即本发明避免了现有技术中第一次多晶硅淀积进而形成台阶对形貌及器件可靠性的影响,对于现有技术具有重大进步。

附图说明

32.图1为现有技术中淀积氧化层的示意图。

33.图2为氧化层刻蚀的示意图。

34.图3为屏蔽栅与控制栅间氧化层形成的示意图。

35.图4为多晶硅残留示意图。

36.图5为步骤s1的示意图。

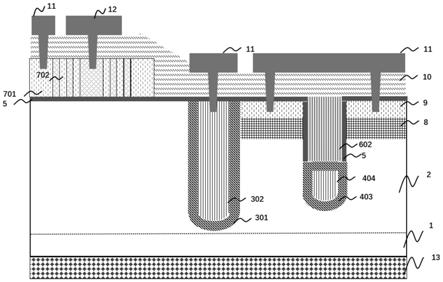

37.图6为步骤s21的示意图。

38.图7为步骤s22的示意图。

39.图8为步骤s31的示意图。

40.图9为步骤s32的去除步骤的示意图。

41.图10为步骤s32中的掺杂步骤的示意图。

42.图11为步骤s4的示意图。

43.图12为步骤s5的示意图。

44.图中:1、衬底;2、外延层;3、第一沟槽;301、第一介质层区块一;302、第一多晶硅层

区块一;4、第二沟槽;401、第一介质层区块二;402、第一多晶硅层区块二;403、第一介质层区块三;404、第一多晶硅层区块三;405、顶部介质层;5、栅氧化层;501、氧化层;6、第二多晶硅层;601、第二多晶硅层区块二;602、第二多晶硅层区块三;7、第二多晶硅层区块一;701、第二多晶硅层区块四;702、第二多晶硅层区块五;8、体区;9、源区;10、第二介质层;11、源极金属;12、栅极金属;13、漏极金属。

具体实施方式

45.下面结合附图,说明本发明的具体实施方式。

46.本发明公开了一种具备静电保护能力的屏蔽栅沟槽mosfet器件及其制作方法。图5~图12示出了制作方法的一个实施例的步骤。具体的:

47.图5为步骤s1的示意图。如图5所示,在步骤s1中,提供n型衬底1,于衬底1上形成n型外延层2。n型外延层2位于n型衬底1之上。在外延层2上形成图形化掩膜层,采用干法刻蚀工艺对外延层2的上表面进行刻蚀得到第一沟槽3和第二沟槽4。

48.步骤s2为第一多晶硅层沉积以形成屏蔽栅的步骤。步骤s2见图6、图7所示。

49.图6为步骤s21的示意图。如图6所示,步骤s21,于第一沟槽3的内表面、第二沟槽4的内表面及外延层2的上表面,通过热氧化工艺形成第一介质层,在第一介质层之上淀积形成第一多晶硅层。采用化学机械研磨工艺去除位于外延层2的上表面的第一介质层及第一多晶硅层,保留第一沟槽3之内的第一介质层区块一301和第一多晶硅层区块一302,以及第二沟槽4之内的第一介质层区块二401和第一多晶硅层区块二402。且使得第一多晶硅层区块一302的上表面低于第一沟槽3的顶面,第一介质层区块一301位于第一多晶硅层区块一302和外延层2之间;第一多晶硅层区块二402的上表面低于第二沟槽4的顶面,第一介质层区块二401位于第一多晶硅层区块二402与外延层2之间。第一多晶硅层区块一302用作连接mosfet器件源极的屏蔽栅。

50.图7为步骤s22的示意图,如图7所示,步骤s22,采用刻蚀工艺回刻去除位于第二沟槽4内的上部区域的第一介质层区块二401及位于第二沟槽4内的上部区域的第一多晶硅层区块二402,剩余第二沟槽4内下部区域的第一介质层区块三403及第一多晶硅层区块三404。之后再在第二沟槽4之内,第一介质层区块三403及第一多晶硅层区块三404的顶部沉积一层顶部介质层405,顶部介质层405和第一介质层区块三403将第一多晶硅层区块三404封闭包围。第一多晶硅层区块三404作为屏蔽栅结构。

51.步骤s3为沉积第二多晶硅层以形成mosfet的栅极和esd调制区域的过程。步骤s3见图8、图9、图10所示。

52.图8为步骤s31的示意图。如图6所示,在外延层2的上表面以及第二沟槽4的上部区域之内的侧壁通过热氧化工艺形成氧化层5,之后采用物理气相沉积工艺或者化学气相沉积工艺于外延层2的上表面的氧化层5的表面以及第二沟槽4之内形成第二多晶硅层6。

53.图9为步骤s32的去除步骤的示意图。如图7所示,步骤s32中,采用图形化掩膜层在第一沟槽3旁侧的第二多晶硅层6中保留第二多晶硅层区块一7,在第二多晶硅层区块一7以外的其他区域通过刻蚀工艺或化学机械研磨工艺去除位于外延层2的上表面的氧化层5和位于外延层2上方的第二多晶硅层6,保留位于第二沟槽4的侧壁的氧化层5作为栅氧化层501,留下填充于第二沟槽4中的上部区域的第二多晶硅层区块二601。

54.图10为步骤s32中的掺杂步骤的示意图。如图8所示,采用光刻、离子注入的方法在第二多晶硅层区块二601进行n型重掺杂并形成n型重掺杂的第二多晶硅层区块三602,掺杂物为磷原子、砷原子或者锑原子,掺杂浓度为每平方厘米1e15至2e16个。第二多晶硅层区块三602作为mosfet器件的控制栅极。

55.之后采用离子注入的方法对第二多晶硅层区块一7的进行p型轻掺杂,形成p型轻掺杂的第二多晶硅层区块四701,掺杂物为硼原子,掺杂浓度为每平方厘米1e14至1e15个。

56.图11为步骤s4的示意图。在步骤s4中,采用离子注入、退火的方法在n型外延层2的表层之中第二沟槽4的旁侧区域形成p型轻掺杂的体区8。采用光刻、离子注入、退火的方法在体区8的表层之中形成n型重掺杂的源区9,即mosfet的源极,与此同步的,对p型轻掺杂的第二多晶硅层区块四701的部分区域进行n型重掺杂,形成n型重掺杂的第二多晶硅层区块五702。

57.p型轻掺杂的第二多晶硅层区块四701和n型重掺杂的第二多晶硅层区块五702,构成了多个npn结构的esd保护二极管,esd保护二极管至少包含两个pn结,也可以是更多个pn结的串联,比如npnpnpn结构,如图11所示。

58.图12为步骤s5的示意图,如图12所示,步骤s5中,采用气相淀积、光刻、刻蚀、物理气相沉积(pvd)等方法形成第二介质层10(ild)、接触孔、金属层等结构,具体方法流程与现有技术中形成介质层、介质层接触孔、金属层的方法相同,而且这些方法步骤也都属于半导体器件制造领域常规的制程,具体细节不再赘述。

59.在步骤s5中,源极金属11有四个端头,源极金属11的第一端头和源极金属11的第二端头穿过第二介质层10连接至源区9,源极金属11的第三端头穿过第二介质层10连接至第一多晶硅层区块一302,源极金属11的第四端头穿过第二介质层10连接至esd保护二极管的一端;栅极金属12有一个端头;栅极金属12的第一端头连接至esd保护二极管的另一端。

60.第一多晶硅层区块一302和第一多晶硅层区块三404在芯片内部是互通的,也即短接的。

61.在栅氧化层5之间与顶部介质层405表面所形成的第二多晶硅层区块三602是mosfet器件的控制栅极,与被顶部介质层405和第一介质层区块三403围住的第一多晶硅层区块三404之间形成了上下结构的屏蔽栅极沟槽,降低了栅极导通电阻(rdson)和栅漏电容(cgd),在降低了系统的导通损耗和开关损耗的同时,提高了系统的使用效率。

62.根据以上的制作流程,如图12所示,本发明公开了一种具备静电保护能力的屏蔽栅沟槽mosfet器件,包括:

63.衬底1,衬底1内设置有至少两个沟槽。在图12示出的实施例中,衬底1为n型,衬底1之上具有n型的外延层2。外延层2上具有第一沟槽3和第二沟槽4。

64.在第一沟槽3之内有第一介质层区块一301和第一多晶硅层区块一302,第一多晶硅层区块一302的上表面低于第一沟槽3的顶面,第一介质层区块一301位于第一多晶硅层区块一302和外延层2之间。

65.第二沟槽4分为下部的第一区域和上部的第二区域。在第二沟槽4的第一区域有第一多晶硅层区块三404,第一多晶硅层区块三404被第一介质层区块三403及顶部介质层405包围。第二沟槽4的第二区域的侧壁有栅氧化层501,在第二区域之中还填充有n型重掺杂的第二多晶硅层区块三602;在第二沟槽4的侧部有p型轻掺杂的体区8。体区8的表层之中形成

n型重掺杂的源区9。

66.在第一沟槽3的侧部还设置有esd保护二极管。

67.第二介质层10,位于外延层2以及外延层2所形成的各个部件之上;

68.还包括金属层,金属层包括源极金属11,栅极金属12和漏极金属13。

69.源极金属11有四个端头,源极金属11的第一端头和源极金属11的第二端头穿过第二介质层10连接至源区9,源极金属11的第三端头穿过第二介质层10连接至第一多晶硅层区块一302,源极金属11的第四端头穿过第二介质层10连接至esd保护二极管的一端;栅极金属12有一个端头,栅极金属12的第一端头连接至esd保护二极管的另一端。

70.漏极金属13位于衬底1的下方。

71.以上描述是对本发明的解释,不是对发明的限定,本发明所限定的范围参见权利要求,在不违背本发明的基本结构的情况下,本发明可以作任何形式的修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1