半导体装置的制作方法

1.本发明涉及一种半导体装置。

背景技术:

2.半导体装置包括功率器件,并被用作电力转换装置。功率器件包括例如igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)、功率mosfet(metal oxide semiconductor field effect transistor,金属氧化物半导体场效应晶体管)的半导体芯片。这样的半导体装置至少包括半导体芯片、布线端子以及陶瓷电路基板。陶瓷电路基板配置有半导体芯片和布线端子。陶瓷电路基板包括绝缘板以及设置在该绝缘板上的导电板。在导电板上通过焊料接合有半导体芯片和布线端子。

3.在如此地将半导体芯片和布线端子接合于导电板时,会导致熔融的焊料扩散。如果在这样的焊料配置半导体芯片和布线端子,则有时会导致半导体芯片和布线端子从预定的接合区域错位。因此,在导电板上沿该接合区域的周围形成有狭缝。通过这样的狭缝,能够在利用焊料接合半导体芯片和布线端子时控制熔融的焊料的扩散。另外,狭缝也用作将半导体芯片和布线端子配置于导电板时的对位。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2003-100983号公报

技术实现要素:

7.技术问题

8.然而,有可能因形成于导电板的狭缝而导致导电板的电流路径中的电感变化。因此,导致半导体装置的电气特性受影响而使可靠性降低。

9.本发明是鉴于这一点而完成的,其目的在于提供一种能够在控制熔融的焊料的扩散的同时防止电感的变化的半导体装置。

10.技术方案

11.根据本发明的一个观点,提供一种半导体装置,所述半导体装置具有:基板,其包括绝缘板和设置于所述绝缘板的正面的导电板;第一半导体芯片,其设置于所述导电板的正面的第一芯片区;第二半导体芯片,其设置于所述导电板的正面的第二芯片区;以及布线端子,其设置于所述导电板的正面的端子区,所述导电板具备:第一狭缝,其形成于所述第一芯片区与所述第二芯片区之间的间隙;第二狭缝,其形成于所述第一芯片区与所述端子区之间的间隙;以及第三狭缝,其形成于所述第一芯片区与所述端子区之间的间隙,所述第一狭缝是贯穿了所述导电板的连续线,所述第二狭缝和所述第三狭缝是所述导电板的非贯穿的连续线或局部地贯穿了所述导电板的点线中的任一者。

12.发明效果

13.根据公开的技术,能够提供能够在控制熔融的焊料的扩散的同时防止电感的变

化,并抑制可靠性的降低的半导体装置。

14.本发明的上述及其他目的、特征以及优点通过表示作为本发明的例子而优选的实施方式的附图和关联的以下说明而变得清楚。

附图说明

15.图1为第一实施方式的半导体装置的侧视图。

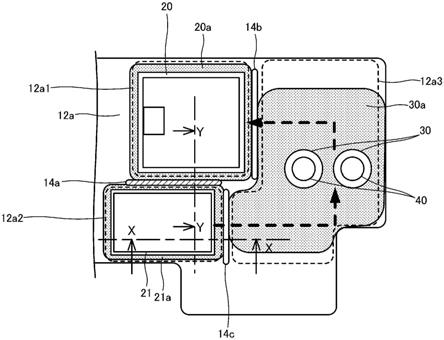

16.图2为第一实施方式的半导体装置的俯视图。

17.图3为第一实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。

18.图4为第一实施方式的半导体装置所包括的陶瓷电路基板的主要部分的截面图(其一)。

19.图5为第一实施方式的半导体装置所包括的陶瓷电路基板的主要部分的截面图(其二)。

20.图6为第二实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。

21.图7为第三实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。

22.图8为第四实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。

23.图9为第四实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的截面图。

24.符号说明

25.10:陶瓷电路基板

26.11:绝缘板

27.12、12a:导电板

28.12a1、12a4:第一芯片区

29.12a2:第二芯片区

30.12a3:端子区

31.13:金属板

32.14a:第一狭缝

33.14b、14b1、14d:第二狭缝

34.14c、14c1:第三狭缝

35.15:键合线

36.20、23:第一半导体芯片

37.21:第二半导体芯片

38.20a、21a、23a、30a、40a:焊料

39.24:电子部件

40.30:触点部件

41.40:外部连接引脚

42.41:引线框架

43.45:密封部件

44.50:半导体装置

具体实施方式

45.以下,参照附图对实施方式进行说明。应予说明,在以下的说明中,“正面”和“上表面”在图1的半导体装置50表示朝向上侧的面。同样地,“上”在图1的半导体装置50表示上侧的方向。“背面”和“下表面”在图1的半导体装置50表示朝向下侧的面。同样地,“下”在图1的半导体装置50表示下侧的方向。根据需要,在其他附图中也表示同样的方向性。“正面”、“上表面”、“上”、“背面”、“下表面”、“下”、“侧面”仅是确定相对的位置关系的方便的表述,并不限定本发明的技术思想。例如,“上”和“下”不一定表示相对于地面的铅直方向。即,“上”和“下”的方向不限于重力方向。

46.[第一实施方式]

[0047]

使用图1和图2对第一实施方式的半导体装置进行说明。图1为第一实施方式的半导体装置的侧视图,图2为第一实施方式的半导体装置的俯视图。应予说明,图1用虚线表示密封部件45。在图2中,省略了密封部件45的图示。另外,半导体装置50省略了壳体的记载。应予说明,壳体收纳陶瓷电路基板10、第一半导体芯片20、第二半导体芯片21等。另外,在第一实施方式中,针对多个导电板12、第一半导体芯片20、第二半导体芯片21、多个触点部件30、多个键合线15、以及多个外部连接引脚40,不分别区分而标注相同的符号进行说明。应予说明,对于这些以外的构成,也不对存在多个的构成分别区分而标注相同的符号并利用相同的符号进行说明。

[0048]

如图1和图2所示,半导体装置50具有陶瓷电路基板10(基板)、以及与陶瓷电路基板10的正面接合的第一半导体芯片20、第二半导体芯片21。半导体装置50具有与陶瓷电路基板10的正面接合的触点部件30(布线端子)。第一半导体芯片20、第二半导体芯片21以及触点部件30经由接合材料(省略图示)与陶瓷电路基板10的正面接合。接合材料是例如焊料。关于焊料的详细情况将在后面进行描述。另外,半导体装置50具有将陶瓷电路基板10的正面与第一半导体芯片20、第二半导体芯片21的主电极电连接的键合线15。另外,在触点部件30压入而安装有外部连接引脚40。此外,半导体装置50以使安装于触点部件30的外部连接引脚40的前端部突出的方式,与陶瓷电路基板10的正面的第一半导体芯片20、第二半导体芯片21一起被密封部件45密封。

[0049]

陶瓷电路基板10为基板的一例。这样的陶瓷电路基板10在俯视时为矩形形状。陶瓷电路基板10包括绝缘板11、设置于绝缘板11的背面的金属板13、以及设置于绝缘板11的正面的多个导电板12(包括导电板12a。以下相同)。绝缘板11和金属板13在俯视时为矩形形状。另外,角部可以倒角为r形或c形。金属板13的尺寸在俯视时比绝缘板11的尺寸小,并形成于绝缘板11的内侧。绝缘板11由导热性良好的陶瓷构成。这样的陶瓷为例如氧化铝、氮化铝、氮化硅。另外,绝缘板11的厚度为0.5mm以上且2.0mm以下。金属板13由导热性优异的金属构成。这样的金属为例如铝、铁、银、铜、或者至少包含它们中的一种的合金。另外,金属板13的厚度为0.1mm以上且2.0mm以下。为了提高耐腐蚀性,可以对金属板13的表面进行镀覆处理。此时,使用的镀覆材料为例如镍、镍-磷合金、镍-硼合金。

[0050]

多个导电板12由导电性优异的金属构成。这样的金属为例如银、铜、镍、或者至少包含它们中的一种的合金。另外,多个导电板12的厚度为0.5mm以上且1.5mm以下。为了提高耐腐蚀性,可以对多个导电板12的表面进行镀覆处理。此时,使用的镀覆材料为例如镍、镍-磷合金、镍-硼合金。针对绝缘板11,在绝缘板11的正面形成金属层,并对该金属层进行蚀刻等处理而得到多个导电板12。或者,也可以使预先从金属层切出的多个导电板12压接于绝缘板11的正面。应予说明,图1和图2所示的多个导电板12为一例。能够根据需要而适当选择导电板12的个数、形状、大小等。另外,在导电板12a的图2中虚线区域内形成有多个狭缝。这些狭缝的详细情况将在后面进行描述。

[0051]

作为这样的陶瓷电路基板10,能够使用例如dcb(direct copper bonding,直接铜键合)基板、amb(active metal brazed,活性金属钎焊)基板。应予说明,作为基板的另一例,能够使用例如金属基底基板。金属基底基板包括由树脂构成的绝缘层、设置于绝缘层的背面的金属板13、以及设置于绝缘板11的正面的多个导电板12。另外,被密封部件45密封而构成的半导体装置50露出陶瓷电路基板10的金属板13的背面。

[0052]

第一半导体芯片20是由硅或碳化硅构成的开关元件。开关元件为例如igbt、功率mosfet。在第一半导体芯片20为igbt的情况下,在背面具备集电极作为主电极,在正面具备栅电极作为控制电极以及发射极作为主电极。在第一半导体芯片20为功率mosfet的情况下,在背面具备漏极作为主电极,在正面具备栅电极作为控制电极以及源极作为主电极。另外,第二半导体芯片21是由硅或碳化硅构成的二极管元件。二极管元件为例如sbd(schottky barrier diode,肖特基势垒二极管)、pin(p-intrinsic-n,p-本征-n)二极管等fwd(free wheeling diode,续流二极管)。这样的第二半导体芯片21在背面具备阴极作为主电极,在正面具备阳极作为主电极。第一半导体芯片20、第二半导体芯片21的背面侧通过接合材料(省略图示)而接合在预定的导电板12上。接合材料为例如焊料。关于接合材料的详细情况将在后面进行描述。此外,第一半导体芯片20、第二半导体芯片21的厚度为例如180μm以上且220μm以下,平均为200μm左右。应予说明,在导电板12也能够配置电子部件24。电子部件24是例如热敏电阻、电流传感器。

[0053]

键合线15适当地电连接在第一半导体芯片20、第二半导体芯片21与导电板12之间,或者适当地电连接在多个第一半导体芯片20、第二半导体芯片21之间。这样的键合线15由导电性优异的材质构成。作为该材质,由例如金、银、铜、铝、或者至少包含它们中的一种的合金构成。另外,键合线15的直径为例如100μm以上且500μm以下。

[0054]

触点部件30为布线端子的一例。这样的触点部件30具备主体部和凸缘。主体部在内部形成有圆筒状的贯通孔。凸缘设置于主体部的开口端部。在触点部件30的主体部的贯通孔压入有外部连接引脚40。外部连接引脚40具有棒状的主体部、以及分别形成于主体部的两端部的锥状的前端部。主体部呈棱柱状。外部连接引脚40的截面的对角线的长度比触点部件30的主体部的直径长百分之几。触点部件30和外部连接引脚40由导电性优异的金属构成。这样的金属为例如银、铜、镍、或者至少包含它们中的一种的合金。为了提高耐腐蚀性,可以对触点部件30和/或外部连接引脚40的表面进行镀覆处理。此时,使用的镀覆材料为例如镍、镍-磷合金、镍-硼合金。

[0055]

布线端子只要至少一端经由接合部件与导电板12接合即可。作为布线端子的另一例,有引线框架、汇流条以及外部连接端子。引线框架将第一半导体芯片20、第二半导体芯

片21与导电板12之间电连接。汇流条将多个导电板12之间电连接。外部连接端子将导电板12与外部设备电连接。这样的引线框架、汇流条以及外部连接端子由导电性优异的金属构成。这样的金属为例如银、铜、镍、或者至少包含它们中的一种的合金。为了提高耐腐蚀性,可以对触点部件30和/或外部连接引脚40的表面进行镀覆处理。此时,使用的镀覆材料为例如镍、镍-磷合金、镍-硼合金。

[0056]

密封部件45包含热固性树脂、以及作为填料而包含于热固性树脂的填充剂。热固性树脂为例如环氧树脂、酚醛树脂、马来酰亚胺树脂。填充剂为例如二氧化硅、氧化铝、氮化硼或氮化铝。

[0057]

接下来,使用图3~图5对陶瓷电路基板10的导电板12a的图2中的虚线区域的详细情况进行说明。图3为第一实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。图4和图5为第一实施方式的半导体装置所包括的陶瓷电路基板的主要部分的截面图。应予说明,图4表示图3的单点划线y-y处的截面图,图5表示图3的单点划线x-x处的截面图。

[0058]

根据图3,第一半导体芯片20经由焊料20a设置于导电板12a的正面的第一芯片区12a1。第二半导体芯片21经由焊料21a设置于导电板12a的正面的第二芯片区12a2。触点部件30经由焊料30a设置于导电板12a的正面的端子区12a3。此外,外部连接引脚40被压入触点部件30。焊料20a、21a、30a以无铅焊料为基体而构成。无铅焊料以例如由锡和银构成的合金、由锡和锑构成的合金、由锡和锌构成的合金、以及由锡和铜构成的合金中的至少任一合金为主要成分。另外,在焊料20a、21a、30a可以包含有添加物。添加物为例如铜、铋、铟、镍、锗、钴或硅。另外,接合第一半导体芯片20、第二半导体芯片21的焊料20a、21a与接合触点部件30的焊料30a的焊料组成不同。接合第一半导体芯片20、第二半导体芯片21的焊料20a、21a难以产生空隙,并具有耐高温性。例如,焊料20a、21a是以锡和锑为主要成分的合金。接合触点部件30等布线端子的焊料30a具有比焊料20a、21a低的弹性率。焊料30a是例如以锡和银为主要成分的合金。应予说明,在图3中,示出了熔融的焊料20a、21a、30a扩散而固化的状态。另外,接合第一半导体芯片20、第二半导体芯片21的焊料20a、21a可以比接合触点部件30的焊料30a薄。焊料20a、21a的厚度为0.05mm以上且0.25mm以下。焊料30a的厚度为0.10mm以上且0.50mm以下。由于焊料30a的弹性率比焊料20a、21a的弹性率低,所以能够使焊料30a的厚度比焊料20a、21a的厚度厚。因此,能够较好地对半导体装置10工作时的半导体芯片20、21的发热进行散热。此外,能够抑止焊料30a中的裂纹以及剥离等的产生,并能够防止半导体装置10的破损。

[0059]

另外,相对于导电板12a,第一芯片区12a1和第二芯片区12a2被设定为至少彼此的侧部的一部分对置并相邻。另外,相对于导电板12a,端子区12a3被设定为与第一芯片区12a1的侧部和第二芯片区12a2的侧部对置并相邻。此外,相对于导电板12a,端子区12a3被设定为相对于第一芯片区12a1和第二芯片区12a2的排列方向(图3中的上下方向)而沿垂直方向(图3中的左右方向)邻接。触点部件30只要配置于该端子区12a3内的任一处即可,图3的配置位置为一例。

[0060]

在导电板12a分别形成有第一狭缝14a、第二狭缝14b、第三狭缝14c。第一狭缝14a形成于第一芯片区12a1与第二芯片区12a2之间的间隙。如图3、图4所示,第一狭缝14a是贯穿了导电板12a的连续线。此时的第一狭缝14a的宽度可以大于焊料20a、21a的厚度,且可以

为第一芯片区12a1与第二芯片区12a2之间的间隙的宽度以下。应予说明,对于第一半导体芯片20、第二半导体芯片21而言,它们的从导电板12a的正面起的高度大致相等。另外,优选第一狭缝14a的长度至少为与第一芯片区12a1和第二芯片区12a2对置并重叠的侧部对应的长度以上。另外,第一狭缝14a的长度优选为与第一芯片区12a1和第二芯片区12a2的对置的任一侧部对应的长度以下。由此,熔融的焊料20a、21a的端部与第一狭缝14a的对置的各个端边接触,从而被分离。因此,能够防止熔融的焊料20a、21a在第一芯片区12a1、第二芯片区12a2之间移动,并且能够防止第一半导体芯片20、第二半导体芯片21从预定的接合区域错位。

[0061]

第二狭缝14b形成于第一芯片区12a1与端子区12a3之间的间隙。第三狭缝14c形成于第二芯片区12a2与端子区12a3之间的间隙。如图3、图5所示,第三狭缝14c是导电板12a的非贯穿的连续线。应予说明,虽然省略了第二狭缝14b的截面图,但与图5所示的第三狭缝14c同样地,该第二狭缝14b是导电板12a的非贯穿的连续线。即,第二狭缝14b、第三狭缝14c的深度小于导电板12a的厚度。另外,焊料30a的厚度比焊料21a(以及焊料20a)的厚度厚。此时的第二狭缝14b、第三狭缝14c的宽度可以大于焊料20a、21a的厚度,且可以为第一芯片区12a1与端子区12a3之间的间隙的宽度、以及第二芯片区12a2与端子区12a3之间的间隙的宽度以下。优选第二狭缝14b、第三狭缝14c的长度至少为与端子区12a3和第一芯片区12a1、第二芯片区12a2对置并重叠的侧部对应的长度以上。另外,优选与第一芯片区12a1的靠端子区12a3一侧的侧部以及第二芯片区12a2的靠端子区12a3一侧的侧部对应的长度以下。另外,在图3中,第二狭缝14b、第三狭缝14c分别形成于第一芯片区12a1、第二芯片区12a2的侧部。第二狭缝14b、第三狭缝14c也可以是芯片区的内部被连接而连续的狭缝。这样的第一狭缝14a、第二狭缝14b、第三狭缝14c通过例如蚀刻、激光加工并根据形成位置而形成为预定的深度。由此,熔融的焊料20a、30a被第二狭缝14b的对置的端边拦截,从而被分离。因此,能够防止熔融的焊料20a、30a在第一芯片区12a1与端子区12a3之间移动,并且能够防止第一半导体芯片20和触点部件30从预定的接合区域错位。另外,由于抑制了焊料20a的流出,所以第一半导体芯片20的焊料厚度被维持。因此,也能够防止产生焊料20a中的焊料裂纹和/或散热不良。

[0062]

此外,根据上述,第二芯片区12a2具有隔着第一狭缝14a与第一芯片区12a1对置的第一侧端部、以及与第一侧端部垂直的第二侧端部。并且,该第二侧端部隔着第三狭缝14c与端子区12a3对置。另外,第一芯片区12a1具有与第二芯片区12a2对置的第三侧端部、以及与该第三侧端部垂直的第四侧端部。并且,该第四侧端部隔着第二狭缝14b与端子区12a3对置。此时,第一半导体芯片20、第二半导体芯片21之间的间隔可以比第一半导体芯片20与触点部件30之间的间隔、以及第二半导体芯片21与触点部件30之间的间隔短。另外,第一狭缝14a的宽度可以比第二狭缝14b、第三狭缝14c的宽度窄。

[0063]

上述的半导体装置50具有:陶瓷电路基板10,其包括绝缘板11和设置于绝缘板11的正面的导电板12a;第一半导体芯片20,其设置于导电板12a的正面的第一芯片区12a1;第二半导体芯片21,其设置于导电板12a的正面的第二芯片区12a2;以及触点部件30,其设置于导电板12a的正面的端子区12a3。导电板12a具备:第一狭缝14a,其形成于第一芯片区12a1与第二芯片区12a2之间的间隙;第二狭缝14b,其形成于第一芯片区12a1与端子区12a3之间的间隙;以及第三狭缝14c,其形成于第二芯片区12a2与端子区12a3之间的间隙。并且,

第一狭缝14a是贯穿了导电板12a的连续线,第二狭缝14b、第三狭缝14c是导电板12a的非贯穿的连续线。

[0064]

通过该第一狭缝14a、第二狭缝14b、第三狭缝14c,能够限制熔融的焊料20a、21a、30a的扩散。因此,能够防止种类不同的焊料20a、21a、30a混合。另外,第一狭缝14a以贯穿的连续线的方式形成于导电板12a。因此,防止第一半导体芯片20、第二半导体芯片21的错位,而能够使上述半导体芯片接近地配置。此外,第二狭缝14b、第三狭缝14c以不贯穿导电板12a的(非贯穿的)连续线的方式形成于导电板12a。因此,能够使来自触点部件30的电流沿着图3中的虚线箭头可靠地流向第一半导体芯片20的背面的主电极。另外,能够使从第二半导体芯片21的背面输出的电流沿着图3和图5中的虚线箭头可靠地流向触点部件30。如此,能够利用贯穿的连续线的第一狭缝14a而使第一半导体芯片20、第二半导体芯片21接近。此外,第一半导体芯片20、第二半导体芯片21相对于触点部件30的电流路径不会被非贯穿的连续线的第二狭缝14b、第三狭缝14c妨碍,从而能够在实现低电感的布线的同时,限制焊料20a、21a、30a的扩散。由此,能够在提高半导体装置50的电气特性的同时,防止可靠性的降低。

[0065]

[第二实施方式]

[0066]

在第二实施方式中,使用图6对第一芯片区12a1、第二芯片区12a2以及端子区12a3的配置位置、形状与第一实施方式不同的情况进行说明。图6为第二实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。应予说明,在第二实施方式中,对与第一实施方式相同的构成标注相同的符号,并简化或省略关于它们的说明。

[0067]

在图6所示的导电板12a,第一芯片区12a1相对于第二芯片区12a2,在比第二芯片区12a2更向图6中下方偏移的位置与第二芯片区12a2邻接而设定。此外,第一芯片区12a1的图6中下方的侧部与导电板12a的端部接近。第一狭缝14a形成于第一芯片区12a1与第二芯片区12a2之间的间隙。第一狭缝14a与第二芯片区12a2的与第一芯片区12a1对置的侧部的长度对应而形成。在第一芯片区12a1、第二芯片区12a2分别设置有第一半导体芯片20、第二半导体芯片21。应予说明,在图6中,第一芯片区12a1、第二芯片区12a2的位置也可以相反。

[0068]

端子区12a3设定在导电板12a被第一芯片区12a1的从第二芯片区12a2错位的侧部与第二芯片区12a2的图6中下方的侧部包围的区域。在该端子区12a3形成有作为布线端子的引线框架41。引线框架41经由焊料40a与导电板12a接合。应予说明,焊料40a与第一实施方式的焊料30a同样地构成。并且,沿着与端子区12a3对置的第二芯片区12a2、第一芯片区12a1的侧部而分别形成有第二狭缝14b、第三狭缝14c。第一狭缝14a是贯穿了导电板12a的连续线,第二狭缝14b、第三狭缝14c是导电板12a的非贯穿的连续线。

[0069]

第二芯片区12a2具有隔着第一狭缝14a与第一芯片区12a1对置的第一侧端部、以及与第一侧端部垂直的第二侧端部。并且,该第二侧端部隔着第三狭缝14c与端子区12a3对置。另外,第一芯片区12a1具有隔着第一狭缝14a与第二芯片区12a2对置,并隔着第二狭缝14b与端子区12a3对置的第三侧端部。此时,第一半导体芯片20、第二半导体芯片21之间的间隔可以比第一半导体芯片20与触点部件30之间的间隔和第二半导体芯片21与触点部件30之间的间隔短。另外,第一狭缝14a的宽度可以比第二狭缝14b、第三狭缝14c的宽度窄。

[0070]

由于在这样的导电板12a也形成有第一狭缝14a、第二狭缝14b、第三狭缝14c,所以能够限制熔融的焊料20a、21a、40a的扩散。因此,能够防止种类不同的焊料20a、21a、40a混

合。另外,第一狭缝14a以贯穿的连续线的方式形成于导电板12a。因此,防止在第一半导体芯片20、第二半导体芯片21之间的错位,而能够使上述半导体芯片接近地配置。此外,第二狭缝14b、第三狭缝14c以不贯穿导电板12a的(非贯穿的)连续线的方式形成于导电板12a。因此,能够使来自引线框架41的电流沿着图6中的虚线箭头可靠地流向第一半导体芯片20的背面的主电极。另外,能够使从第二半导体芯片21的背面输出的电流沿着图6的虚线箭头可靠地流向引线框架41。如此,能够利用贯穿的连续线的第一狭缝14a而使第一半导体芯片20、第二半导体芯片21接近。此外,第一半导体芯片20、第二半导体芯片21相对于引线框架41的电流路径不会被非贯穿的连续线的第二狭缝14b、第三狭缝14c妨碍,从而能够在实现低电感的布线的同时,限制焊料20a、21a、40a的扩散。由此,能够在提高半导体装置50的电气特性的同时,防止可靠性的降低。

[0071]

[第三实施方式]

[0072]

在第三实施方式中,使用图7对第一芯片区12a1、12a4以及端子区12a3的配置位置、形状与第一实施方式、第二实施方式不同的情况进行说明。图7为第三实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。

[0073]

在图7所示的导电板12a,第一芯片区12a1、12a4被设定为隔开间隔地相邻。应予说明,在第一芯片区12a4也经由焊料23a设置有第一半导体芯片23。第一半导体芯片23是与第一半导体芯片20同样的开关元件。焊料23a形成与焊料20a相同的组成。另外,在第一芯片区12a1、12a4之间的间隙形成有第一狭缝14a。第一狭缝14a的长度与第一半导体芯片20、23的宽度对应。

[0074]

相对于导电板12a,端子区12a3被设定为与第一芯片区12a1、12a4的图7中下方的侧部对置。在该端子区12a3也接合有引线框架41。引线框架41经由焊料40a与导电板12a接合。并且,沿着与端子区12a3对置的第一芯片区12a1、12a4的侧部而分别形成有第二狭缝14b、14d。应予说明,与第二狭缝14b同样地,第二狭缝14d相对于导电板12a以非贯穿的方式连续地形成。另外,第二狭缝14b、14d分别形成于第一芯片区12a1、12a4的侧部与端子区12a3重叠的间隙。第一狭缝14a是贯穿了导电板12a的连续线,第二狭缝14b、第三狭缝14c是导电板12a的非贯穿的连续线。

[0075]

两个第一芯片区12a1、12a4隔着第一狭缝14a对置。并且,两个第一芯片区12a1、12a4的与对置的侧端部垂直的侧端部分别隔着第二狭缝14b、14d与端子区12a3对置。第二狭缝14b、14d可以连续地形成。此时,两个第一半导体芯片20、23之间的间隔可以分别短于第一半导体芯片20与触点部件30之间的间隔、以及第一半导体芯片23与触点部件30之间的间隔。另外,第一狭缝14a的宽度可以比第二狭缝14b、14d的宽度窄。

[0076]

由于在这样的导电板12a也形成有第一狭缝14a和第二狭缝14b、14d,所以能够限制熔融的焊料20a、23a、40a的扩散。因此,能够防止种类不同的焊料20a、23a、40a混合。另外,第一狭缝14a以贯穿的连续线的方式形成于导电板12a。因此,防止在第一半导体芯片20、23之间的错位,而能够使上述半导体芯片接近地配置。此外,第二狭缝14b、14d以不贯穿导电板12a的(非贯穿的)连续线的方式形成于导电板12a。因此,能够使来自引线框架41的电流沿着图7中的虚线箭头可靠地流向第一半导体芯片20、23的背面的主电极。如此,能够利用贯穿的连续线的第一狭缝14a而使第一半导体芯片20、23接近。此外,第一半导体芯片20、23相对于引线框架41的电流路径不会被非贯穿的连续线的第二狭缝14b、14d妨碍,从而

能够在实现低电感的布线的同时,限制焊料20a、23a、40a的扩散。由此,能够在提高半导体装置50的电气特性的同时,防止可靠性的降低。

[0077]

[第四实施方式]

[0078]

在第四实施方式中,使用图8和图9对在第一实施方式的导电板12a第二狭缝14b、第三狭缝14c形成点线而构成的情况进行说明。图8为第四实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的俯视图。图9为第四实施方式的半导体装置所包括的陶瓷电路基板的导电板的主要部分的截面图。应予说明,图9表示图8的单点划线y-y处的截面图。

[0079]

在图8所示的导电板12a分别形成有第二狭缝14b1、第三狭缝14c1来代替连续地形成于图3的导电板12a的第二狭缝14b、第三狭缝14c,该第二狭缝14b1、第三狭缝14c1形成为点线状。如图8所示,该第二狭缝14b1局部地贯穿导电板12a的第一芯片区12a1与端子区12a3之间的间隙而形成为点线状。因此,第一芯片区12a1和端子区12a3未被第二狭缝14b1完全地分割断开。由于第二狭缝14b1包括贯穿的部分,所以能够限制熔融的焊料20a、30a的扩散。此外,能够使来自触点部件30的电流沿着图8中的虚线箭头,通过第二狭缝14b1的导电板12a的未被贯穿的部分而流向第一半导体芯片20的背面的主电极。另外,与第二狭缝14b1同样地,第三狭缝14c1也局部地贯穿导电板12a的第二芯片区12a2与端子区12a3之间的间隙而形成为点线状。因此,第二芯片区12a2和端子区12a3未被第三狭缝14c1完全地分割断开。由于第三狭缝14c1也包括贯穿的部分,所以能够限制熔融的焊料21a、30a的扩散。此外,能够使来自第二半导体芯片21的背面的电流沿着图8中的虚线箭头,通过第三狭缝14c1的导电板12a的未被贯穿的部分而流向触点部件30。

[0080]

由于在这样的导电板12a也形成有第一狭缝14a、第二狭缝14b1、第三狭缝14c1,所以能够限制熔融的焊料20a、21a、30a的扩散。因此,能够防止种类不同的焊料20a、21a、30a混合。另外,第一狭缝14a以贯穿的连续线的方式形成于导电板12a。因此,防止在第一半导体芯片20、第二半导体芯片21之间的错位,而能够使上述半导体芯片接近地配置。此外,第二狭缝14b1、第三狭缝14c1在导电板12a局部地贯穿而形成为点线状。因此,能够使来自触点部件30的电流沿着图8中的虚线箭头可靠地流向第一半导体芯片20的背面的主电极。另外,能够使从第二半导体芯片21的背面输出的电流沿着图8的虚线箭头可靠地流向触点部件30。如此,能够利用贯穿的连续线的第一狭缝14a而使第一半导体芯片20、第二半导体芯片21接近。此外,第一半导体芯片20、第二半导体芯片21相对于触点部件30的电流路径不会被非贯穿的连续线的第二狭缝14b1、第三狭缝14c1妨碍,从而能够在实现低电感的布线的同时,限制焊料20a、21a、30a的扩散。由此,能够在提高半导体装置50的电气特性的同时,防止可靠性的降低。

[0081]

以上仅示出了本发明的原理。此外,本领域技术人员能够进行多种变形、变更,本发明并不限于上述所示、所说明的正确的构成以及应用例,对应的所有变形例和等同物被视为基于所添附的权利要求及其等同物的本发明的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1