使用了基于半导体封装件以及开孔中介层的浸渍冷却方式的三维层叠集成电路的制作方法

1.本发明涉及具备基于制冷剂的冷却功能的三维层叠集成电路以及三维层叠集成电路的冷却方法。

背景技术:

2.存在有三维层叠的半导体的安装技术。例如,申请人公开了一种三维层叠集成电路,其在三维层叠集成电路各自的集成电路间以及最下面的集成电路之下分别具备中介层,在多个所述中介层各自设置制冷剂的移动路径,设于所述多个中介层的多个所述制冷剂的移动路径相互连接(参照专利文献1)。

3.现有技术文献

4.专利文献

5.专利文献1:国际公开第2019/146724号

技术实现要素:

6.发明所要解决的技术问题

7.原本,散热板即使插入层叠半导体之间也无法有效地发挥功能。使金属板向横向伸出而散热会导致热阻过大。虽说是金属,但是热阻(ψjt)与金属的导热距离成比例,tj=ψjt

×

p+tcl(tj是结温,ψjt是热阻,p是消耗电力,td是环境温度),当ψjt变大时不施加消耗电力。

8.图15是表示在发热的半导体芯片之上设置散热板后热如何传播的剖视图。半导体芯片的整体成为发热体,但是为了说明朝向散热板的热的传递方式而将发热部分作为发热点a、b、c的点热源。热从点热源相对于散热板呈半球状(由于图15是剖视图,因此用半圆表示)扩散。

9.热从中央的发热点b呈同心圆状地传播,但是由于存在有来自位于左右的发热点a或者发热点b的热,因此在左右方向上热阻较大而几乎不传播。另一方面,由于上方向的热阻较低,因此散热片b及其周边的散热片有效地发挥作用。

10.另一方面,在发热点a,因来自中央的发热点b的热而使得右方向的热阻较大,因此热向上方和左方传播。同样地,在发热点c,因来自中央的发热点b的热而使得左方向的热阻较大,因此热向上方和右方传播。

11.由于散热板以比发热体大的表面积向外部放出热,因此与半导体芯片相比足够大。因此,在发热点a的左侧和发热点c的右侧没有热源,热阻较小,因此通过散热板本身的表面积的散热能够进行充分的散热,存在有散热片a或者散热片c等的外缘部分的散热片未有效地发挥作用的可能性。

12.另外,为了使如散热片b那样位于作为发热体的半导体芯片的正上方的散热片最大限度地发挥有效性,只要如图16那样使散热板的厚度变薄,使发热点与散热片接近即可,

但是若使散热板的厚度变薄,则散热板的热阻变大,难以引起从发热点朝向正上部以外的散热板的导热,因此是本末倒置的。

13.因而,无论散热板较厚还是较薄,特别是在未将半导体芯片收容于bga封装件等而以三维浸渍为前提的情况下,即使在半导体芯片之间夹着散热板,其有效性也存在疑问。

14.不进行上述tsv中的三维化的、在封装件了半导体的基础上进行了浸渍的、以基于在表面具有电极焊盘的fc-bga封装件的、浸渍为前提的三维半导体(cpu、gpu等高发热运算电路的三维安装)的高效的方法中,由于不安装散热片而直接进行浸渍,将半导体基底部(半导体的电路安装部的相反侧,以尽量薄的方式切削而成的部分)直接进行浸渍(该情况下,用底部填料密封fc部),或者涂布复合物,用导热率良好的较薄的封装件金属覆盖而进行浸渍,w=j/s,因此对制冷剂进行压送而获得m2/s(由于半导体的表面积为1cm2/s左右,因此例如若以沸腾散热为前提,则一平方厘米的有效表面积不足10倍,则以10cm2/s的流量流动即可),仅设定必要的有效表面积的表面积流量即可。

15.例如,在制冷剂为氟化物液体的情况下,为大致0.5w/cm2℃的导热率,但是若对上述式子进行变形,则p=(tj-tcl)x1/ψjt,因此若tj为85℃,则在氟化物液体的沸点为56℃的情况下,tj-tcl得到29℃的温度差,但是在p成为58w,例如为200w的1cm2的cpu的情况下,对大致4cm/s的流量进行压送而使其流动即可。

16.在半导体为1kw的1cm2的gpgpu的情况下,使大致20cm/s左右的流量流动并进行沸腾冷却就足够了。这当然是划时代的说法,在重叠10层1kw的gpgpu而形成超级计算机的情况下,进行浸渍而从横向对全部层施加20cm/s左右的流量也就足够了。这在激光振荡器等中普遍实用化,并不是特别的。

17.根据本发明,在层叠在表面具有电极焊盘的fc-bga封装件时,通过插入开孔中介层基板,能够在表面具有电极焊盘的fc-bga封装件的半导体的背面(孔的部分)确保收容层叠陶瓷电容器的空间,且能够确保稳定地保证上述所需的流量的空间。

18.现有技术将三维半导体看作一块,着眼于在其内部用于冷却半导体的制冷剂的流路,但是并没有考虑为了使也被称为处理器(prossesser)的cpu(central processing unit中央处理器)、gpgpu(general-purpose computing on graphics processing unit通用图形处理器)、bbu(base band unit基带处理单元)、超级计算机的核等消耗大电流的半导体芯片动作而将陶瓷电容器配置在何处。虽然考虑在三维半导体的最上面或者底面配置陶瓷电容器,但是对于中央层的半导体芯片而言,从陶瓷电容器至半导体芯片的贯穿各层的电力供给路径变长,从而阻抗增大,无法对半导体芯片进行大电流供电。

19.本发明就是用于消除参考文献wo2019/146724的不良情况的提案,在该参考文献wo2019/146724中,去除从搭载有处理器的半导体封装件基板(也称为fc-bga(flip chip-ball grid array倒装芯片球栅格阵列)基板)的各层至陶瓷电容器的电路的bga(ball grid array球栅阵列)端子,在半导体封装件基盘的各层安装陶瓷电容器,从而降低电路的阻抗而能够进行大电流供电,且进行浸渍而实现三维冷却。

20.一般公开

21.在参考文献wo2019/146724中,通过重叠在表面具有电极焊盘的fc-bga封装件,封装件下部的陶瓷电容器与封装件上部的散热器的间隔变窄,即使进行浸渍,也存在有无法期待流量的隐患。

22.在本次的发明中,提出了一种装置和方法,该装置和方法用于通过以犹如在没有铁锅澡盆的盖时穿木屐进入这样的感觉插入未搭载半导体芯片的在上下带有焊盘和bga的电极的、使开设有四边形孔的bga电极上下电贯通散热器部分的带焊盘和bga的基板(以下称为“开孔中介层基板”),确保陶瓷电容器与散热器的间隔,从而确保浸渍的fluorinert液的流量和将陶瓷电容器配置于bga封装件的下部的空间,在不大幅改变现有的fc-bga封装件的存在方式的情况下构筑浸渍三维运算装置。

23.(1)一种三维层叠集成电路,其以将具备半导体芯片的封装件和在搭载半导体芯片的位置具备开口部的中介层基板通过各自的电极端子和电极焊盘交替地层叠的浸渍为前提,其中,

24.所述封装件和所述中介层基板为通过下表面的电极端子而在层叠方向与所述电极端子彼此之间产生空隙的形状,

25.在所述封装件和所述中介层基板的上表面设有用于连结所述电极端子的几何学形状的电极焊盘,

26.所述封装件和所述中介层基板的所述电极端子和所述电极焊盘沿上下以1:1电连接,

27.在所述封装件和所述中介层基板设有用于在层叠时进行准确的定位和保持连结的引导孔,

28.通过所述封装件与所述中介层基板的连结,由所述电极端子和电极焊盘形成层间通信路径,

29.通过使冷却液在所述封装件和所述中介层基板的所述电极端子彼此之间产生的空隙中流动来进行浸渍冷却。

30.(2)根据上述(1)所述的三维层叠集成电路,插入到所述封装件间的所述中介层基板被连续地插入有多片。

31.(3)根据上述(1)或(2)所述的三维层叠集成电路,搭载于所述封装件之中的半导体芯片为两层以上的层叠三维半导体(hbm即high bandwidth memory即高带宽存储器或者wide i/o dram等)。

32.(4)根据上述(1)至(3)中任一项所述的三维层叠集成电路,所述封装件为交叉连接而成的numa(non-uniform memory access即非一致性内存访问)结构,所述封装件的相互连接成为总线连接。

33.(5)根据上述(1)至(4)中任一项所述的三维层叠集成电路,所述引导孔兼具作为用于朝向搭载于所述封装件的半导体芯片供电的阳极和阴极的电极的功能,进而为了降低阻抗以便能够向搭载于所述封装件的陶瓷电容器直接供电,所述引导孔相邻地各具备两个。

34.(6)根据上述(1)至(5)中任一项所述的三维层叠集成电路,以相邻的两个所述电极端子为对,将由所述电极端子和电极焊盘形成的所述层间通信路径的数据传输方式设为lvd(low voltage differential即低电压差动)。

35.(7)根据上述(1)至(5)中任一项所述的三维层叠集成电路,以相邻的两个所述电极端子为对,将由所述电极端子和电极焊盘形成的所述层间通信路径的数据传输方式设为pci express(外部组件互联高速)。

36.(8)根据(7)所述的三维层叠集成电路,使用加频(clock up)后的pci express。

37.(9)根据上述(1)至(8)中任一项所述的三维层叠集成电路,为了降低在所述层间通信路径中流动的高频信号的反射的不良影响,与所述封装件的所述电极端子相邻地搭载有双向三态栅极驱动器。

38.(10)根据上述(1)至(9)中任一项所述的三维层叠集成电路,为了防止浸渍冷却中的基于间歇性沸腾的气蚀,与搭载于所述封装件的半导体芯片密合的散热器为烧结金属或者氧化金属。

39.(11)一种三维层叠集成电路,其中,

40.上述(1)至(10)所述的所述三维层叠集成电路的最下层的集成电路由总线驱动器开关或者以页为单位带地址总线窥探且带缓冲器的dma的总线驱动器缓冲开关构成。

41.发明效果

42.根据本发明,由于能够在搭载有处理器的半导体封装件基板的各层的背面确保隔离而确保安装陶瓷电容器的间隙的基础上进行浸渍冷却,因此能够降低电路的阻抗而进行大电流供电。

附图说明

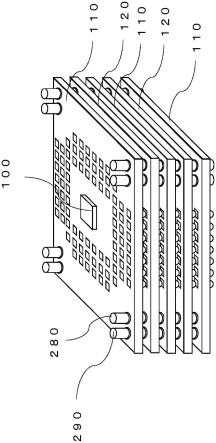

43.图1是在作为本实施方式的一个例子的三维层叠集成电路中层叠三层并结合的立体图。

44.图2是表示在作为本实施方式的一个例子的三维层叠集成电路中,在层叠三层时的表面具有电极焊盘的fc-bga封装件与开孔中介层基板的重叠的立体图。

45.图3是作为本实施方式的一个例子的在表面具有电极焊盘的fc-bga封装件的表面的立体图。

46.图4是作为本实施方式的一个例子的在表面具有电极焊盘的fc-bga封装件的背面的立体图。

47.图5是作为本实施方式的一个例子的在表面具有电极焊盘的fc-bga封装件的双向三态栅极驱动器和电路的概略图。

48.图6是双向三态栅极驱动器内部以及外部的电路的概略图。

49.图7是双向三态栅极驱动电路的示意图。

50.图8是表示作为本实施方式的一个例子的在表面具有电极焊盘的fc-bga封装件中,用散热器覆盖半导体芯片的结构的立体图。

51.图9是表示作为本实施方式的一个例子的在表面具有电极焊盘的fc-bga封装件中,用散热器覆盖半导体芯片的结构的剖视图。

52.图10是作为本实施方式的一个例子的开孔中介层基板的表面的立体图。

53.图11是作为本实施方式的一个例子的开孔中介层基板的背面的立体图。

54.图12是作为本实施方式的一个例子的三维层叠集成电路中的层间通信路径的示意图。

55.图13是作为本实施方式的一个例子的三维层叠集成电路的双向三态栅极驱动器所具备的层间通信路径的示意图。

56.图14是在作为本实施方式的一个例子的三维层叠集成电路中安装了具有厚度的

半导体芯片的图。

57.图15是半导体芯片的热向散热板传播的示意图。

58.图16是半导体芯片的热向较薄的散热板传播的示意图。

59.图17是在作为本实施方式的一个例子的三维层叠集成电路中,用层叠了两层的侧视图表示双向三态栅极驱动器的搭载位置的图。

60.图18是表示总线连接方式中的通信路径的名称的图。

具体实施方式

61.以下,参照附图对本发明的优选实施方式进行说明。通过发明的实施方式对本发明进行说明,但是以下的实施方式并不限定权利要求书所涉及的发明。另外,在实施方式中说明的特征的全部组合不一定是发明的解决手段所必须的。

62.在图中所示的本实施方式的三维层叠集成电路中,将在表面具有电极焊盘的fc-bga封装件和其上的一片或者多片开孔中介层基板集中设为一层,将在最上部的表面具有电极焊盘的fc-bga封装件单独设为一层。此外,fc-bga封装件是具有在与下层的基板连结的状态下在层叠方向和电极端子彼此之间产生空隙的形状的端子的封装件的一个例子,电极焊盘是几何学形状的焊盘的一个例子。另外,bga电极等是在层叠方向和电极端子彼此之间产生空隙的形状的电极端子的一个例子。此外,在各图中,标注了相同的附图标记的部分具有相同或者同样的结构。

63.参照图1以及图2,对本实施方式进行说明。图1是本实施方式的立体图。图2是表示本实施方式的层叠结构的立体图。

64.(bga、垫片、层间通信路径、浸渍冷却)

65.在参考文献wo2019/146724中,通过重叠在表面具有电极焊盘的fc-bga封装件,封装件下部的陶瓷电容器与封装件上部的散热器的间隔变窄,即使进行浸渍,也存在有无法期待流量的隐患。或者,也存在有发生干扰而无法重叠的隐患。

66.在本次的发明中提出了一种装置和方法,该装置和方法用于通过以犹如铁锅澡盆的木屐这样的感觉插入未搭载半导体芯片的在上下带有焊盘和bga的电极的、使开设有四边形孔的bga电极上下电贯通原本搭载ic和散热器部分的带焊盘和bga的基板(以下称为“开孔中介层基板”),确保陶瓷电容器与散热器的间隔,从而确保浸渍的fluorinert液的流量和将陶瓷电容器配置于bga封装件的下部的空间,在不大幅改变现有的fc-bga封装件的存在方式的情况下构筑浸渍三维运算装置。

67.在本实施方式中,如图1所示,通过层叠搭载有半导体芯片100的在表面具有电极焊盘的fc-bga封装件110和开孔中介层基板120而构成。

68.(可以连续多张垫片)。

69.开孔中介层基板120是用于调节制冷剂的流量和上下层的隔离的基板,也可以不是一个而是连续地层叠多个。

70.(具有电极兼引导孔)

71.在表面具有电极焊盘的fc-bga封装件110和开孔中介层基板120为了在阻抗较低的状态下对陶瓷电容器350进行电力供给,如图3和图10所示,相邻地具备用于立起引导销的通孔的阳极的供电电极240和用于立起引导销的通孔的阴极的供电电极250。

72.(层间通信为lvd)

73.如图11所示,本实施方式中的三维层叠集成电路通过将电极焊盘140与电极端子340接合而形成层间通信路径。其中,将跨越多层而连接的通信路径设为本地总线420。通过成对地使用相邻的两个电极端子并以lvd(low voltage differential:低电压差动)驱动本地总线420的通信方式来缓和信号反射的问题。

74.(层间通信是pci express)

75.在所述本地总线420的通信方式中,也可以成对地使用相邻的两个电极端子而采用pci express标准。

76.(层间通信加频后的pci express)

77.在所述本地总线420的通信方式中也可以采用成对地使用相邻的两个电极端子而加频后的pci express标准。在该情况下,由于层间通信在本系统中是关闭的,因此可以与下述列表无关地自由地进行时钟调谐。

78.此外,作为参考,以下表示pciexpress的修订、每一个链路宽度/单向的物理层传输频带(单位是千兆传输每秒(gt/sec))。

79.gen1 2.5gt/sec

80.gen2 5gt/sec

81.gen3 8gt/sec

82.gen4 16gt/sec

83.gen5 32gt/sec

84.gen6 64gt/sec

85.(在通过bga球进行层间耦合的本地总线的旁边附加双向三态栅极驱动器)

86.在上述本地总线420中,为了防止基于形成为梳状的各层内的引线的反射所引起的不良影响,如图17所示,在各层的电极端子340或者与电极焊盘140相邻且在电极端子340彼此的间隔内具备双向三态栅极驱动器130。通过双向三态栅极驱动器而使层间通信信号的反射停留在纵向由中介层构成bga球的互连范围内。因此,能够期待更进一步的时钟调谐。

87.(为了沸腾冷却而在散热器使用烧结金属或者氧化金属)

88.如图8和图9所示,半导体芯片100被散热器260覆盖,利用导热率较高的复合物等使其密合。一般的vlsi在散热器之上具有散热片,但是由于上次的发明以及本次的发明进行直接浸渍,因此需要考虑在散热器表面不产生间歇性的沸腾。散热器260的特征在于,为了防止由间歇性的沸腾引起的气蚀,表面为氧化金属或者烧结金属。

89.(在最下层的总线驱动器开关)

90.本实施方式的最下层也可以不是单纯地对本地总线420和外部周边设备等进行中继,而是总线驱动器开关或者以页为单位成为带地址总线窥探且带缓冲器的dma的总线驱动器缓冲器开关。

91.(开孔中介层基板的特征)

92.图10所示的开孔中介层基板120具备:位于中央的开口部270;几何学形状的电极焊盘140,用于接合层叠于上表面的在表面具有电极焊盘的fc-bga封装件110或者开孔中介层基板120的电极端子340;以及如图11所示的背面的电极端子340。表面的电极焊盘140与

背面的电极端子340以1:1电连接。进而,具备用于立起引导销的通孔的阳极的供电电极240和用于立起引导销的通孔的阴极的供电电极250。

93.(在半导体芯片旁边带有双向三态栅极驱动器)

94.图5是简略地表示在表面具有电极焊盘的fc-bga封装件110的一部分的内部电路的图。为了说明电路部分,与在图1至图3的表面具有电极焊盘的fc-bga封装件110相比,省略了一部分表现,但是示出了相同的结构。如图5所示,在表面具有电极焊盘的fc-bga封装件110在电极焊盘140或者电极端子340附近具备双向三态栅极驱动器130。

95.在表面具有电极焊盘的fc-bga封装件110除了半导体100以外还具备双向三态栅极驱动器130、电极焊盘141至145、栅极控制信号线600、数据信号线610至611。此外,在图5中,本实施方式以七个电极端子以及一个栅极控制信号线和两个数据控制信号线为例进行了表示,但是并不限定于此,电极端子为1以上即可,另外,栅极控制信号线也为1以上即可,数据信号线也为2以上即可。

96.双向三态栅极驱动器130根据来自半导体芯片100的栅极控制信号线600的信号,控制在数据信号线610和数据信号线611中流动的信号的方向。

97.图6是说明双向三态栅极驱动器130的电路的概略图。双向三态栅极驱动器130由三态缓冲器构成。双向三态栅极驱动器成为图7所示的电路结构。当栅极控制信号线710为“1”时,三态缓冲器731使数据信号线720的信号向数据信号线721的方向流动。此时,在三态缓冲器732中通过not电路730传递“0”,因此成为高阻抗。由此,数据信号从左向右流动。相反地,当栅极控制信号线710为“0”时,三态缓冲器731成为高阻抗,在三态缓冲器732中通过not电路730传递“1”,因此数据信号从数据信号线721向数据信号线720的方向(从右向左)流动。

98.(在表面具有电极焊盘的fc-bga封装件的特征:具有电极兼引导孔)

99.如图3所示,在表面具有电极焊盘的fc-bga封装件110具备:半导体芯片100;几何学形状的电极焊盘140,用于将层叠于上表面的在表面具有电极焊盘的fc-bga封装件110或者开孔中介层基板120的电极端子340接合;用于立起引导销的通孔的阳极的供电电极240;以及用于立起引导销的通孔的阴极的供电电极250。

100.在表面具有电极焊盘的fc-bga封装件110如图4所示,通过将本次的发明所示的开孔中介层基盘插入其间而能够如以往那样在于表面具有电极焊盘的fc-bga封装件110的背面具备陶瓷电容器350。

101.(冷却方式以浸渍的沸腾冷却进行)

102.在本实施方式中,通过进行使用了fluorinert等的浸液的沸腾冷却,也能够应对100w级的半导体的冷却。

103.(本实施方式的效果:利用引导销使层叠时的对准精致化)

104.如图1所示,在本实施方式中,需要将所层叠的在表面具有电极焊盘的fc-bga封装件110或者开孔中介层基板120的电极端子340和电极焊盘140准确地定位并结合。因此,通过向在表面具有电极焊盘的fc-bga封装件110或者开孔中介层基板120所具备的、用于立起引导销的通孔即阳极的供电电极240和用于立起引导销的通孔即阴极的供电电极250中插入引导销即阳极的供电电极280和引导销即阴极的供电电极290,在层叠时,能够准确地定位电极焊盘140和电极端子340。

105.(本实施方式的效果:通过在各层具备陶瓷电容器,能够对半导体芯片进行大电流供电。

106.如图4所示,在表面具有电极焊盘的fc-bga封装件110能够在于表面具有电极焊盘的fc-bga封装件110的半导体的背面具备陶瓷电容器350。由此,通过以各层为单位具备使cpu、gpgpu、bbu、超级计算机的核等消耗大电流的半导体芯片动作时所需的陶瓷电容器,能够使电力供给路径不使用电极端子340而成为最短,能够抑制阻抗而进行大电流供电。

107.(本实施方式的效果:通过开孔中介层基板的开口部和多层层叠能够确保足够的制冷剂)

108.如图10所示,本实施方式中的开孔中介层基板120具备开口部270,通过装配电极端子340并将其层叠在于表面具有电极焊盘的fc-bga封装件110之上,能够确保半导体芯片100的上方乃至周边的空间。由此,从电极端子340彼此的间隙流入的制冷剂能够确保冷却半导体芯片100所需的容量。

109.在开孔中介层基板120为一张时半导体芯片110周边的冷却容量不足的情况下,通过对开孔中介层基板120进行两张三张这样的多层层叠,能够更多地确保半导体芯片100的上方乃至周边的空间。

110.(层内的两层化)

111.放入到具有电极焊盘的fc-bga封装件110之中的半导体芯片100也可以不是单层,而是两层以上。本实施方式的三维层叠集成电路的各封装件内也可以是交叉连接而成的numa(non-uniform memory access)结构。层间的相互连接因销数的制约而成为总线连接。

112.(为了说明本实施方式的效果,说明两种层间通信路径)

113.本实施方式中的三维层叠集成电路通过使图2所示的电极焊盘140与电极端子340接合,如图12所示,形成用于与层叠有某一层的其它层进行通信的层间通信路径。层间通信路径具备从某一层至其相邻的层为止以1:1连接的通信路径(以下,称为“跳层连接”)、以及如图13所示那样从某一层呈梳状分支并连接至各层的通信路径(以下,称为“本地总线”)这两种。

114.(在1:1的跳层连接中没有问题)

115.图12所示的跳层连接430(将相邻的两层的cpu、gpgpu与等级2、或者等级3高速缓存、或者本地存储器连结的本地连接)由在水平方向上在图5所示的表面具有电极焊盘的fc-bga封装件110内的数据信号线640、和在垂直方向上图2所示的电极焊盘140与电极端子340的耦合构成。跳层连接430的路径为p2p(point to point点对点),不存在分支,起点和终点为1:1,因此发生反射,但是不会产生反射波稍微地重叠等特别的信号反射上的问题。

116.(在本地总线中存在信号的反射问题)

117.另一方面,关于图12以及图13所示的本地总线420,为了将多层间并联地耦合,在水平方向上由图5所示的在表面具有电极焊盘的fc-bga封装件110内的数据信号线610和双向三态栅极驱动器130构成,在垂直方向上由图2所示的电极焊盘140和电极端子340构成。此时,由于通信路径不仅通过电极端子与电极焊盘140在垂直方向上耦合,在半导体芯片110内也存在有在水平方向上连接的各fc-bga封装件内的信号线,因此形成梳状的电路而产生复杂的信号的反射图案而成为问题。

118.(反射的不良影响降低的理由)

119.图18为通常的总线电路概略图。梳状的总线电路中的成为中心的主总线在本实施方式的图13中是由电极端子和电极焊盘构成的垂直方向上的通信路径。然后,从主总线到沿水平方向延伸并接收信号的元件(在本实施方式中为双向三态栅极驱动器130)为止的通信路径被称为短截线(stub)。在没有双向三态栅极驱动器130的情况下,在图13所示的主总线中流动的高频信号具有在各个通信路径的端点进行反射的特性,但是导致在短截线内进行了反射的信号返回主总线,与本来的信号混合。短截线越多,反射的次数越多,在来自多个短截线的反射波不良地重叠的情况下,信号波过大,存在有产生误动作隐患。因此,通过使双向三态栅极驱动器130与电极端子相邻而极力缩短短截线,通过接近一条通信路径而不是梳状来抑制由反射的影响引起的问题。

120.(本实施方式的效果:通过双向三态栅极驱动器进行驱动而解决梳状漫反射的问题)

121.为此,如图5所示,设置双向三态栅极驱动器130而仅在垂直方向上抑制信号的反射,不对水平方向的通信路径造成影响,且使用如电极焊盘141和电极焊盘142那样相邻的两个端子的对,以lvd(low voltage differential)进行驱动,进行以对为单位的非同步传输,从而减轻信号反射的问题。由此,利用了本实施方式的系统仅通过使层间通信路径的线长一致就能够不发生严重的误动作地进行高速动作。另外,也可以在层间通信中采用pci express标准。在通信速度不足的情况下,也可以采用加频后的pci express标准。

122.(本实施方式的效果:层间通信路径的汇总:能够进行高速通信)

123.由此,层间通信路径中的信号反射的影响最小化,能够高速且稳定地实现本地总线连接。详细而言,灵活运用通常的处理器间公共总线技术。

124.(半导体除了cpu以外还包括hbm)。

125.搭载于具有电极焊盘的fc-bga封装件110的半导体100不仅可以是cpu、gpgpu等运算装置,也可以是将存储器元件垂直堆叠的hbm(high bandwidth memory)、wide i/o dram。

126.在hbm内部纵向堆积,但是如图14所示,能够进一步在本发明中进行低延迟耦合而搭载于纵向具有电极焊盘的fc-bga封装件110并纵向堆积。这不仅可以是最下层,也可以是任意的层。通过使用经由跳层连接的hbm、wide i/o dram作为本地存储器而成为numa结构。以上所写的跳层连接的本地存储器在三维集成电路的内部总线中经由集成电路(cpu、gpgpu)与本地总线进行numa连接。通过将成为numa结构的本地存储器用作使高速缓冲存储器退避的衰落区而使吞吐量提高。在高速缓存故障时用作工作组。用作二次缓存。作为跳层的用途是基于hbm的高速缓存区域的退避区域。作为numa结构。在多处理器中页面缓冲器充满时,若将该缓冲器放置于numa存储器中,则吞吐量极大地提高。

127.(本实施方式的效果:通过将最下层设为外部总线驱动器开关,能够进行高速化动作)

128.本实施方式的最下层也可以不是单纯地对本地总线420和外部周边设备等进行中继,而是以页为单位成为带有地址总线窥探且带缓冲器的dma。

129.在构建采用了本实施方式的系统的情况下,需要在外部与主存储装置、周边设备等进行外部总线连接,但是若在本实施方式的最下层将在表面具有电极焊盘的fc-bga封装件110设为外部总线驱动器开关,则能够将外部总线电切断。通过将外部总线驱动器开关设

为高阻抗,若将与本实施方式相连的外部总线切断,则信号传播距离变得极短,因此能够进行本实施方式的高速的时钟动作。另外,由于信号是非终端连接,因此与pci总线同样地成为考虑了信号反射的动作方式。

130.(本实施方式的效果:通过将半导体芯片的表面设为氧化金属或者烧结金属来提高冷却效率)

131.沸腾冷却是通过制冷剂从液体相变为气体来进行冷却的。在沸腾冷却中,尽可能多地产生在制冷剂之中产生的气体(气泡),激烈地扩散周围的制冷剂有助于冷却效率的提高。虽然难以预测气泡在哪个部位产生,但是由于从热源表面的微细的伤痕产生的概率较大,因此优选用多孔质的烧结金属、氧化金属覆盖。因此,如图8和图9所示,通过将覆盖半导体芯片100的散热器260的表面设为氧化金属或者烧结金属来提高冷却效率。

132.以上说明的实施方式用于使本发明容易理解,并不用于对本发明进行限定解释。实施方式所具备的各要素及其配置、材料、条件、形状以及尺寸等并不限定于示例的内容,能够适当变更。另外,能够将在不同的实施方式中示出的结构彼此局部地置换或者组合。

133.应当注意的是,权利要求书、说明书以及附图中所示的装置、系统、程序以及方法中的动作、顺序、步骤以及阶段等各处理的执行顺序只要没有特别明示“之前”、“先行”等,或者只要不是在后面的处理中使用前面的处理的输出,就能够以任意的顺序实现。关于权利要求书、说明书以及附图中的动作流程,即使为了方便而使用“首先”、“接着”等进行了说明,也不意味着必须按照该顺序来实施。

134.附图标记说明

135.100、半导体芯片;101、hbm、wide i/o dram等层叠半导体芯片;110、在表面具有电极焊盘的fc-bga封装件;120、开孔中介层基板;130、双向三态栅极驱动器;131、双向三态栅极驱动器;132、双向三态栅极驱动器;133、双向三态栅极驱动器;140、电极焊盘;141、电极焊盘;142、电极焊盘;145、电极焊盘;240、用于立起引导销的通孔的阳极的供电电极;250、用于立起引导销的通孔的阴极的供电电极;260、散热器;270、开口部;280、引导销的阳极的供电电极;290、引导销的阴极的供电电极;340、电极端子;350、陶瓷电容器;410、本实施方式的一层;420、本地总线的示意图;421、主总线;422、短截线;430、跳层连接的示意图;560、双向三态栅极驱动器;561、双向三态栅极驱动器;600、栅极控制信号线;610、数据信号线;611、数据信号线;640、数据信号线;700、双向三态栅极驱动器;710、栅极控制信号线;720、数据信号线;721、数据信号线;730、not电路;731、三态缓冲器;732、三态缓冲器;800、散热板;801、散热片a;802、散热片b;803、散热片c;901、发热点a;902、发热点b;903、发热点c。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1