3D存储芯片的制作方法

3d存储芯片

技术领域

1.本发明实施例涉及存储器技术领域,具体地说,涉及一种3d存储芯片。

背景技术:

2.目前,存储芯片,尤其是dram存储芯片,主要分为平面dram和利用3ds(3-dimensional stack,三维堆叠)技术形成的三维堆叠dram。

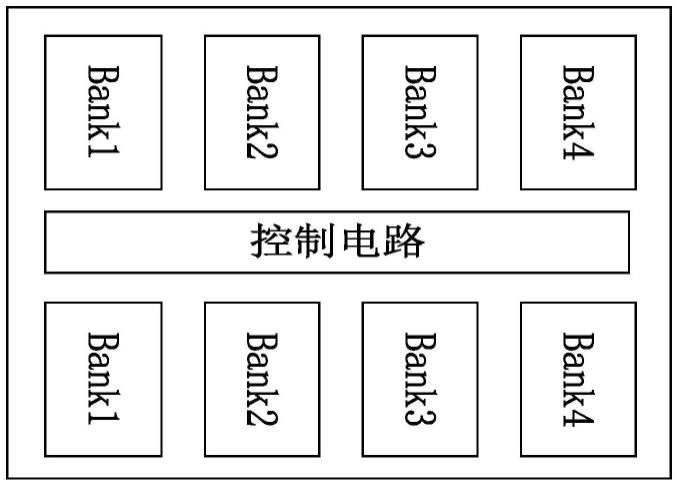

3.对于平面dram,可以参见图1所示的平面dram的示例,存储阵列部分(bank1-bank4,)和控制电路在一个芯片上。存储阵列部分通常包含有存储单元,控制电路通常包括解码译码电路、数据写入电路和数据读出电路等功能电路。

4.平面dram由于制造工艺限制,特别是存储电容的制造工艺限制,使得存储芯片存在较大的寄生电阻电容,影响存储芯片中的功能电路的处理性能,因此,具有速度慢、功耗高,并行处理数据的能力差的缺陷。

5.在三维堆叠dram中,较常见的方式是基于tsv(through-silicon-via,硅通孔)技术联通各个存储部分,可以通过tsv技术把各个存储层堆叠起来,层和层之间会有金属层等间隔。最典型的例子就是hbm(high bandwidth memory,高带宽存储器)和hmc(hybrid memory cube,混合立方存储器)。但hbm和hmc均使用硅中介层,因此成本很高,同时也rc延迟很大,功耗大,散热差的问题。

技术实现要素:

6.在发明内容部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本技术实施例的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

7.本技术实施例通过提供一种3d存储芯片,解决了现有存储芯片寄生电阻电容大、使用硅通孔技术而带来的制造成本高、rc延迟大,功耗大,散热差的问题。

8.为至少部分地解决上述问题,第一方面,本技术实施例提供了一种3d存储芯片,可以包括:

9.相互堆叠的存储部分和控制部分,所述存储部分与所述控制部分通过混合键合方式相连接,其中,所述混合键合方式为通过金属导体使所述存储部分的连接焊盘和所述控制部分的连接焊盘相连接,所述存储部分设置有存储阵列,所述存储芯片的功能电路设置在所述控制部分。

10.在第一方面的第一种可能的实施方式中,所述功能电路包括sram修复单元电路,所述sram修复单元电路用于取代所述存储阵列中失效的存储单元,以对所述存储阵列进行修复。

11.在第一方面的第二种可能的实施方式中,所述存储部分还设置有灵敏放大器;

12.所述存储芯片的其他功能电路设置在所述控制部分。

13.在第一方面的第三种可能的实施方式中,所述存储部分还设置有行列译码电路;

14.所述存储芯片的其他功能电路设置在所述控制部分。

15.在第一方面的第四种可能的实施方式中,所述存储部分还设置有存储部分电源电路;

16.所述存储芯片的其他功能电路设置在所述控制部分。

17.在第一方面的第五种可能的实施方式中,所述功能电路包括运算功能模块。

18.在第一方面的第六种可能的实施方式中,所述运算功能模块为cpu或gpu。

19.在第一方面的第七种可能的实施方式中,所述控制部分包括控制部分芯片,所述存储部分包括存储部分芯片,所述控制部分芯片和/或存储部分芯片包括设置在芯片金属层内的金属层穿孔组件,所述连接焊盘设置于所述金属层穿孔组件中远离所述衬底层的第一导体件。

20.在第一方面的第八种可能的实施方式中,所述第一导体件为所述连接焊盘。

21.在第一方面的第九种可能的实施方式中,所述金属层穿孔组件还包括靠近所述衬底层的第二导体件;

22.所述衬底层包括衬底通孔,所述衬底通孔连通于所述第二导体件,所述连接焊盘设置于所述第二导体件。

23.在第一方面的第十种可能的实施方式中,所述第一导体件与所述第二导体件之间设置有导体连接孔,所述第二导体件通过所述导体连接孔连接于所述第一导体件,以使信号能够通过所述衬底层传输至所述第一导体件。

24.在第一方面的第十一种可能的实施方式中,所述第二导体件为所述连接焊盘。

25.在第一方面的第十二种可能的实施方式中,所述衬底通孔填充有填充导体层,所述连接焊盘设置于所述填充导体层远离所述金属层的一侧,所述连接焊盘通过所述填充导体层与所述第二导体件相连接。

26.在第一方面的第十三种可能的实施方式中,所述连接焊盘的形状与所述第一导体件和/或所述第二导体件的形状相配合。

27.在第一方面的第十四种可能的实施方式中,所述连接焊盘的形状为圆形或多边形。

28.在第一方面的第十五种可能的实施方式中,所述连接焊盘还用于所述存储芯片封装引线的键合。

29.在第一方面的第十六种可能的实施方式中,所述存储部分包括两个或三个以上的存储部分芯片;和/或,

30.所述控制部分包括两个或三个以上的控制部分芯片。

31.在第一方面的第十七种可能的实施方式中,所述混合键合方式为通过金属导体使所述存储部分芯片的连接焊盘和所述控制部分芯片的连接焊盘相连接。

32.在第一方面的第十八种可能的实施方式中,所述存储部分芯片之间通过混合键合方式相连接;和/或,

33.所述控制部分芯片之间通过混合键合方式相连接。

34.在第一方面的第十九种可能的实施方式中,所述存储部分包括具有相同容量存储阵列的两个或三个以上的存储部分芯片;和/或,

35.所述存储部分包括具有不同容量存储阵列的两个或三个以上的存储部分芯片。

36.在第一方面的第二十种可能的实施方式中,所述两个或三个以上的存储部分芯片设置在同一平面,每个所述存储部分芯片相互独立。

37.在第一方面的第二十一种可能的实施方式中,两个或三个以上的所述存储部分芯片的堆叠方向相同。

38.在第一方面的第二十二种可能的实施方式中,两个或三个以上的所述存储部分芯片中至少包括一个易失存储芯片和一个非易失存储芯片。

39.在第一方面的第二十三种可能的实施方式中,所述易失存储芯片为dram芯片,所述为非易失存储芯片为nand flash芯片。

40.在第一方面的第二十四种可能的实施方式中,两个或三个以上的所述存储部分芯片堆叠设置,相邻的所述存储部分芯片与所述控制部分芯片通过混合键合方式相连接。

41.在第一方面的第二十五种可能的实施方式中,两个或三个以上的所述控制部分芯片堆叠设置,相邻的所述存储部分芯片与所述控制部分芯片通过混合键合方式相连接。

42.在第一方面的第二十六种可能的实施方式中,两个或三个以上的所述存储部分芯片之间隔地堆叠设置有至少一个所述控制部分芯片,所述控制部分芯片两侧的存储部分芯片数量相同。

43.在第一方面的第二十七种可能的实施方式中,两个或三个以上的所述存储部分芯片不间隔的堆叠设置。

44.在第一方面的第二十八种可能的实施方式中,两个或三个以上的所述控制部分芯片包括至少一个模拟功能电路芯片和至少一个数字功能电路芯片,其中,所述模拟功能电路芯片仅设置有模拟功能电路,所述数字功能电路芯片仅设置有数字功能电路。

45.在第一方面的第二十九种可能的实施方式中,在所述两个或三个以上的所述存储部分芯片包括相邻的两个朝向一致的存储部分芯片。

46.在第一方面的第三十种可能的实施方式中,在所述两个或三个以上的所述控制部分芯片包括相邻的两个朝向一致的存控制分芯片。

47.在第一方面的第三十一种可能的实施方式中,在所述两个或三个以上的所述存储部分芯片包括相邻的两个相向设置的存储部分芯片。

48.在第一方面的第三十二种可能的实施方式中,在所述两个或三个以上的所述控制部分芯片包括相邻的两个相向设置的存控制分芯片。

49.在第一方面的第三十三种可能的实施方式中,相邻的所述存储部分芯片和所述控制部分芯片通过混合键合方式连接。

50.相比现有技术,本发明实施例中提供的3d存储芯片至少包括以下有益效果:

51.本发明实施例提供的3d存储芯片,包括相互堆叠的存储部分和控制部分,上述存储部分与上述控制部分通过混合键合方式相连接。其中,上述混合键合方式为通过金属导体使上述存储部分的连接焊盘和上述控制部分的连接焊盘相连接,上述存储部分设置有存储阵列,上述存储芯片的功能电路设置在上述控制部分。通过将单一存储芯片扩展成相互堆叠的存储部分和控制部分两部分芯片,并且在不同部分设置制作工艺或要求不同的功能电路和存储阵列。作为同一存储芯片的存储部分和控制部分两部分芯片之间不需要驱动接口电路或模块(phy),使得存储芯片堆叠的芯片密度可以做的很高,组成存储芯片的存储部

分芯片和控制部分芯片混合键合寄生参数(寄生电阻值、寄生电容值)很小,因此,rc延时小,进而数据传输速度没有损失,可实现存储芯片的高带宽数据传输。

附图说明

52.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图:

53.图1为一些示例中的平面dram的示意性结构图;

54.图2为本发明实施例提供的一种3d存储芯片的示意性结构图;

55.图3为本发明实施例提供的一种3d存储芯片中的单一芯片的示意性结构图;

56.图4a为本发明实施例提供的另一种3d存储芯片中的单一芯片的示意性结构图;

57.图4b为本发明实施例提供的又一种3d存储芯片中的单一芯片的示意性结构图;

58.图5为本发明实施例提供的一种具有多个存储部分的3d存储芯片的示意性结构图;

59.图6为本发明实施例提供的另一种具有多个存储部分的3d存储芯片的示意性结构图;

60.图7为本发明实施例提供的又一种具有多个存储部分的3d存储芯片的示意性结构图;

61.图8为本发明实施例提供的一种具有多个控制部分的3d存储芯片的示意性结构图;

62.图9为本发明实施例提供的另一种具有多个控制部分的3d存储芯片的示意性结构图。

具体实施方式

63.下面结合附图以及实施例对本发明做进一步的详细说明,以令本领域技术人员参照说明书文字能够据以实施。

64.应当理解,本文所使用的诸如“具有”、“包含”以及“包括”术语并不排除一个或多个其它元件或其组合的存在或添加。

65.除此之外,还需要说明的是,除非另有明确的规定和限定,术语“设置”、“连接”应做广义理解。例如,可以是固定连接,也可以是可拆卸连接;可以是直接相连,也可以通过中间媒介间接相连;可以是一体地连接,也可以是两个元件内部的连通。也可以是两个元件之间可以进行信号传递、数据通信。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

66.目前,为了获得更高的带宽,通常采用传统的tsv结构联通各个存储部分的hbm芯片和hmc芯片。其中,hbm芯片将多个ddr双倍速率同步动态随机存储部分芯片以及一个pld(programmable logic device,可编程逻辑器件)堆叠在一起后和gpu封装在一起,并利用硅通孔与微凸块接合实现芯片至芯片间连接,实现大容量,高位宽的ddr组合阵列。而hmc芯片是在一个基本逻辑层上堆叠了多个dram层,在一个异构封装中实现了逻辑和dram工艺的

最佳组合。dram层只处理数据,而逻辑层处理hmc中的所有控制功能。

67.但是,要想实现几十层的堆叠结构非常困难,实现难度大且由于技术不成熟还会存在运行风险高、稳定性差等问题。并且,hbm和hmc均使用硅中介层,因此成本很高,出货量也非常有限。另外,由于存在大量dram堆叠和gpu封装在一起的情况,也会严重影响其散热性能。

68.针对上述问题,本技术实施例提供一种3d存储芯片,解决了现有平面存储芯片或者通过硅通孔技术等技术实现的堆叠存储芯片而带来的制造成本高、电路灵活性差、运行风险高、稳定性差、rc延迟大、功耗大的问题。

69.图2为本发明实施例提供的一种3d存储芯片的示意性结构图,如图2所示,上述3d存储芯片,可以包括:

70.相互堆叠的控制部分100和存储部分200,上述存储部分200与上述控制部分100通过混合键合方式相连接,其中,上述混合键合方式为通过金属导体使上述存储部分200的连接焊盘和上述控制部分100的连接焊盘相连接。示例性的,上述金属导体为金属导体连接孔结构,上述存储部分设置有存储阵列,所述存储芯片的功能电路设置在上述控制部分。

71.在一些示例中,控制部分100和存储部分200可以分别为单独的平面芯片或晶圆。例如,可以是堆叠的平面芯片(c2c,chip to chip),即为上下堆叠的3d芯片;也可以是堆叠的晶圆(w2w,wafer to wafer),经过切割之后,形成上下堆叠的3d芯片。

72.在一些示例中,上述混合键合方式可以采用金属导体300的两端分别与存储部分200与控制部分100上的连接焊盘(connect pad)相连接。

73.示例性的,上述控制部分可以包括控制部分芯片,上述存储部分可以包括存储部分芯片,上述控制部分芯片和/或存储部分芯片可以包括设置在芯片金属层内的金属层穿孔组件,上述连接焊盘设置于上述金属层穿孔组件中远离上述衬底层的第一导体件,上述连接焊盘也可以设置于衬底穿孔中远离金属层的一侧。

74.如图3所示,在一些示例中,控制部分100和存储部分200可以是平面芯片或者晶圆。所以控制部分100和存储部分200在分别制造和生产时,可以包括衬底层20和金属层10,也可称为器件层和金属连线层。金属层10可以包括相对设置的第一表面和第二表面,上述金属层10的第二表面设置在上述衬底层20上,金属层10内可以设置金属层穿孔组件,上述金属层穿孔组件可以包括:第一导体件11、第二导体件12和导体连接孔,上述第一导体件11,可以形成于上述金属层10的第一表面。上述第二导体件12可以形成于上述金属层10的第二表面。为了便于说明可以将芯片的衬底层所在一侧表面称为芯片的反面或者背面;金属层所在一侧表面称为芯片的正面。存储部分200或控制部分100的正面或者背面可以设置有连接焊盘,上述连接焊盘可以用于上述控制部分100和存储部分200之间的混合键合或者用于上述存储芯片的封装引线的键合。

75.示例性的,参考图3,连接焊盘可以设置在控制部分芯片或存储部分芯片的正面上可以理解为上述连接焊盘设置在上述金属层穿孔组件的第一导体件11上。

76.示例性的,上述连接焊盘的形状与上述第一导体件和/或上述第二导体件的形状相可以配合,用于满足混合键合时连接焊盘与金属导体的充分接触。示例性的,上述连接焊盘的形状可以为矩形或者圆形,也可以为其他多边形或者为其它形状,在此不做限定。

77.示例性的,上述连接焊盘还可以为上述第一导体件,可以理解为上述金属层中的

顶层金属所代表的第一导体件可以直接作为上述连接焊盘使用,上述连接焊盘能够同样用于混合键合使用,并可以进一步简化芯片制造的工艺。

78.根据一些实施例,如图4a所示,上述衬底层20可以包括衬底通孔21,上述衬底通孔21连通于上述第二导体件12,上述连接焊盘可以设置于上述第二导体件12。

79.示例性的,上述第一导体件与上述第二导体件之间设置有导体连接孔,上述第二导体件通过上述导体连接孔连接于上述第一导体件,以使信号能够通过上述衬底层传输至上述第一导体件。

80.示例性的,连接焊盘可以设置在控制部分芯片或存储部分芯片的背面上,从芯片的背面对衬底层进行挖孔形成上述衬底通孔至金属层的最底层金属所代表的第二导体件,进而在最底层金属设置连接焊盘。上述最底层金属和金属层的最顶层金属所代表的第一导体件可以通过导体连接孔相连接,以使信号能够通过上述衬底层中的第二导体件传输至上述第一导体件。

81.示例性的,在上述最底层金属设置连接焊盘的方式可以有两种:

82.第一种方式可以参考图4a,可以将最底层金属直接设置为连接焊盘。

83.第二种方式可以参考图4b,为衬底通孔21填充导体后,在芯片背面用金属设置连接焊盘23,这里的连接焊盘23通过衬底通孔21中填充的填充导体层22与最底层金属所代表的第二导体件12连接。上述衬底通孔底部的连接焊盘23通过填充导体层22与第二导体件12连用后,便可以通过导体连接孔与第一导体件相连接,以使信号能够通过上述衬底层20传输至上述金属层10的最顶层金属,从而让信号联通整个芯片。

84.示例性的,在最底层金属中的第二导体件上设置的连接焊盘的形式或通过填充导体层与第二导体件连接的连接焊盘的形式与最顶层金属中的第一导体件或连接焊盘的形状可以是一致的,同样用于满足混合键合时连接焊盘与金属导体的充分接触。示例性的,上述连接焊盘的形状可以为矩形或者圆形,也可以是其他多边形或者为其它形状,在此不做限定。例如,上述连接焊盘在上述存储部分或上述控制部分的正面时,连接焊盘设置在最顶层金属上,上述连接焊盘在上述存储部分或上述控制部分的背面时,上述连接焊盘直接或通过填充导体层间接与最底层金属连接,并且两面的连接焊盘都可以采用相同大小的圆形。

85.需要说明的是,连接焊盘的设置目的是为了便于芯片与混合键合中的金属导体连接。连接焊盘设置在芯片正面时,它与金属层中金属层穿孔组件的最顶层金属相连接,其中,最顶层金属可以直接设置为连接焊盘的形式;连接焊盘设置在芯片背面时,它与金属层的最底层金属连接。因为在芯片背面设置连接焊盘需要进行衬底的挖孔,所以相比较而言,在芯片不处于堆叠芯片中的中间位置时,在最顶层金属上设置连接焊盘进行混合键合相对更为容易、可靠性也更高。

86.示例性的,上述存储部分包括两个或三个以上的上述存储部分芯片,上述存储部分芯片之间通过混合键合方式相连接;和/或,控制部分可以包括两个或三个以上的上述控制部分芯片,上述控制部分芯片之间通过混合键合方式相连接。而其中,控制部分芯片之间、存储部分芯片之间及控制部分与存储部分芯片之间的堆叠方式可以有做种形式,在此不做限定。

87.具体的,上述3d存储芯片存储部分和控制部分通过混合键合方式进行连接,因为

混合键合的rc寄生参数很小,存储部分和控制部分两部分芯片之间不需要驱动接口电路或模块(phy),进一步的将原本平面dram中的电路模块可以依据需要灵活的放置在存储部分或控制部分中;甚至还可以将存储部分扩展为多个存储功能芯片的堆叠,使得存储芯片堆叠的芯片密度可以做的很高,存储部分芯片和控制部分相连接的混合键合的寄生参数(寄生电阻值、寄生电容值)很小,因此,rc延时小,进而数据传输速度没有损失,可实现存储芯片的高带宽数据传输。

88.结合上述示例,参考图2,上述相互堆叠的控制部分100和存储部分200,在存储部分200中与控制部分100相连的一侧表面可以设置有连接焊盘以便用于混合键合,即在上述连接焊盘上生长混合键合的金属导体的方式。相应的在控制部分100中与存储部分200相连的一侧表面也设置有连接焊盘以便用于混合键合,即在上述连接焊盘上生长混合键合的金属导体的方式。通过混合键合的金属导体使得上述控制部分100和存储部分200连接及进行数据通信。

89.示例性的,前述连接焊盘可以设置在存储部分200或控制部分100的正面或者背面。在一些示例中,上述相互堆叠的控制部分100和存储部分200可以是面对面的方式,即控制部分100的芯片正面和存储部分200的芯片正面相对,两部分的芯片正面通过混合键合的方式连接,控制部分100的芯片反面和存储部分200的芯片反面在外侧。这样,只需要在控制部分100和存储部分200的最顶层金属上设置连接焊盘进行混合键合以金属导体300连接即可。如前所述,因为在最顶层金属上设置连接焊盘进行混合键合更为容易、可靠性也更高。所以这里优选的采用面对面的方式进行混合键合,制造而成的3d存储芯片的可靠性更高、良率更好。

90.在一些示例中,由于上述连接焊盘还用于上述存储芯片封装引线的键合,在上述相互堆叠的控制部分100和存储部分200在通过混合键合的金属导体300连接后,上述相互堆叠的控制部分100和存储部分200中的存储部分芯片和/或控制部分芯片背离上述金属导体的一侧可以设置有也设置有连接焊盘,其中,上述连接焊盘可以用于引出封装引脚连线,以便进行3d芯片的封装。

91.需要说明的是,上述存储部分和上述控制部分上的金属层穿孔组件中的孔为非贯穿的孔,在对芯片进行封装时,与传统的tsv不同,虽然信号可以穿过整个芯片进行传输,但是芯片上的孔不需要穿透整个芯片,上述连接焊盘可以用于引出引脚连线,上述存储芯片进行封装后可以通过从上述连接焊盘引出的引脚引线与外部电路连接,以作为一个功能单元,配合与之相连的集成电路实现自身的电子设备上的整体功能。

92.上述示例对将3d存储芯片拆分成相互堆叠的存储部分和控制部分后,对存储部分和控制部分之间的混合键合方式及单一芯片内确保数据传输的穿孔结构进行了详细说明。以下会结合一些示例,对上述3d存储芯片中,存储部分和控制部分各自功能分配进行具体说明。

93.根据一些实施例,上述3d存储芯片,可以包括:相互堆叠的存储部分和控制部分,上述存储部分与上述控制部分通过混合键合方式相连接,其中,上述混合键合方式可以为通过金属导体使上述存储部分的连接焊盘和上述控制部分的连接焊盘相连接,上述存储部分设置有存储阵列,上述存储芯片的功能电路设置在上述控制部分。

94.在一些示例中,上述存储部分可以设置有最基本的存储单元,例如,存储阵列。而

上述3d存储芯片的功能电路可以设置在上述控制部分上。

95.示例性的,上述功能电路可以包括:行列译码电路、电源电路、数据处理电路和接口电路。在上述3d存储芯片中,在对上述存储部分进行数据读出时,由控制部分通过接收上述读数据相关的命令,上述行列译码电路对地址进行解码后,选中存储部分中相应存储阵列中的数据,数据从存储部分进入到控制部分,之后在控制部分中再经过接口电路的驱动和数据处理电路时钟控制进行数据的读出。在上述3d存储芯片中,在对上述存储部分进行数据写入时,数据在上述控制部分经过接口电路的驱动和数据处理电路的数据线的分配后,写入到上述存储部分的存储阵列中,从而能够完整实现存储芯片的基本功能。

96.因为上述存储部分的存储阵列中的最小存储单元(memory cell)使用的是能够存储数据的特殊工艺,所以它的制作生产工艺非常的复杂和不好控制。将存储阵列放置在存储部分可以保证工艺的一致性,且因为其他电路已经放到控制部分,所以它的工艺的特殊性不会对其他电路造成影响。

97.根据一些实施例,上述功能电路还可以包括sram修复单元电路,上述sram修复单元电路用于取代上述存储阵列中失效的存储单元,以对上述存储阵列进行修复。通常情况下,在存储阵列中会设置有冗余单元,目的是修复存储阵列中失效的单元。在本发明中,在功能电路还可以包括sram修复单元电路,用于取代存储阵列中的冗余单元。这样的好处是,控制部分可以通过使用逻辑工艺制作出性能更好的sram电路,用sram电路对储阵列中失效的单元进行修复。

98.根据一些实施例,控制部分可以使用专门的逻辑工艺,而逻辑工艺也可以满足部分的模拟电路的性能要求,这样可以不受存储单元的特殊工艺的影响。逻辑工艺可以很好的使包括行列译码电路、电源电路、数据处理电路、接口电路和sram修复单元电路等的其他电路发挥更好的性能。例如,行列译码电路、数据处理电路等纯数字的逻辑,使用逻辑工艺可以实现更高数据频率和带宽,同时还可能节省功耗。

99.根据一些实施例,在上述存储芯片中,上述存储部分设置有存储阵列和灵敏放大器,上述存储芯片的其他功能电路设置在上述控制部分。在对上述存储部分进行数据读出时,由控制部分通过接收上述读数据相关的命令,上述行列译码电路对地址进行解码后,选中存储部分中相应存储阵列中的数据,数据从存储部分中经过灵敏放大器放大之后进入到控制部分,之后在控制部分中再经过接口电路的驱动和数据处理电路时钟控制进行数据的读出。因为存储阵列中的存储单元使用的是能够存储数据的特殊工艺,所以它的制作生产工艺非常的复杂和不好控制。将其和灵敏放大器放置在存储部分可以保证工艺的一致性,且因为其他电路已经放到控制部分,所以它的工艺的特殊性不会对其他电路造成影响。同时灵敏放大器与存储阵列中的存储单元直接相连,灵敏放大器与存储单元放在作为存储部分的同一个芯片中可以保证数据读出的匹配性,数据读出准确率更高。

100.根据一些实施例,上述存储部分还可以设置有行列译码电路,上述存储芯片的其他功能电路设置在上述控制部分。这里将上述行列译码电路增加到了存储部分上。可以理解的是,在上述存储部分中,上述行列译码电路对存储阵列会进行频繁的操作和控制,与存储阵列联系非常紧密,它们之间的连线也非常多。将上述行列译码电路放到存储部分中,可以有效减少上述存储部分和上述控制部分之间混合键合的连线,降低3d芯片制造的复杂度提高良率。同时,行列译码电路和存储阵列放在一起可以减少由于工艺失配带来的误差。

101.示例性的,上述存储部分还设置有存储部分电源电路,上述存储芯片的其他功能电路设置在上述控制部分。具体的,数据读写工作时和其它必要的操作时,上述存储阵列和上述灵敏放大器需要消耗大量的电量,将存储阵列和灵敏放大器所需要的具有基本供电单元电路的存储部分电源电路放置在存储部分中,基本供电功能可以很好的满足数据读写工作时存储部分中功能电路对电能的需要。提高上述存储部分工作的稳定性和可靠性。

102.需要说明的是,在上述电源电路设置在存储部分的同时,上述控制部分也可同样设置基本的控制部分电源电路,上述两个电源电路可以分别为存储部分和控制部分供电。当然,在上述电源电路设置在存储部分的方案中,可以不再在控制部分设置电源电路,而是在控制部分需要供电时,复用存储部分的电源电路。而在此方案中,上述存储部分由于设置有用于供电的电源电路,所以依然提高存储部分稳定性和可靠性的技术效果。

103.上述控制部分,可以理解为通常存储芯片中的控制部分,虽然能够进行例如行、列译码和简单的数据处理操作,但是并不具备运算功能。相应的,在一些示例中,上述存储芯片的控制部分可以不局限于只是通常存储芯片具有的控制功能,还可以包含其他更强大的逻辑功能,例如,可以将控制部分扩展为处理器。

104.根据一些实施例,在上述3d存储芯片中,在上述控制部分中还可以设置运算功能模块。上述运行功能模块可以是cpu(central processing unit/processor,中央处理器)或gpu(graphics processing unit,图形处理器)。这样,上述存储部分的数据可以直接在上述控制部分中进行数据运算处理。由于上述控制部分和上述存储部分是通过混合键合的方式连接,相互之间信号传输的寄生参数小,所以它们组成的系统可以克服存储障碍,大大提高数据的处理能力。

105.需要说明的是,3d存储芯片中的上述存储部分和控制部分依然可以采用如图2所示的混合键合方式,而组成3d存储芯片中的平面芯片中信号的传输可以通过上述不穿透整个芯片的芯片穿孔方案实现。无需设置穿透硅通孔,只需要在衬底上开设衬底通孔,在金属层内开设金属层穿孔组件,大大降低了孔的直径和长度,进而降低了刻蚀的工艺难度,降低了占用金属层的面积,降低了电阻寄生参数和电容寄生参数,缩短了芯片单元的制备周期,降低了生产成本。

106.在将3d存储芯片拆分成相互堆叠的存储部分和控制部分的方案中,上述示例对存储部分和控制部分之间的混合键合方式、单一芯片内确保数据传输的穿孔结构和存储部分和控制部分各自功能分配进行了详细的说明,下面将进一步对3d芯片中相互堆叠的存储部分和控制部分堆叠方式进行具体的说明。

107.如图2所示,上述3d存储芯片,可以包括:

108.相互堆叠的控制部分100和存储部分200,上述存储部分200与上述控制部分100通过混合键合相连接。其中,上述存储部分可以包括两个或三个以上的存储部分芯片,和/或,上述控制部分可以包括两个或三个以上的控制部分芯片。例如,上述3d存储芯片可以包括由三个存储部分芯片组成的存储部分和一个控制部分芯片构成的控制部分,或,上述3d存储芯片可以包括由一个存储部分芯片组成的存储部分和三个控制部分芯片构成的控制部分,或,上述3d存储芯片可以包括由三个存储部分芯片组成的存储部分和三个控制部分芯片构成的控制部分。这里的控制部分芯片或存储部分芯片指单独的芯片(die),或晶圆(wafer),这里的芯片指2d平面芯片,这里的晶圆指2d平面晶圆。述存储部分和控制部分通

过混合键合方式连接后可以形成多种组合方式。

109.上述3d存储芯片存储部分和控制部分通过混合键合方式进行连接,作为同一存储芯片的存储部分和控制部分两部分芯片之间不需要驱动接口电路或模块(phy),进一步的可以使得存储芯片堆叠的芯片密度可以做的很高,可以进行更多个芯片的堆叠,存储部分和控制部分相连接的混合键合的寄生参数(寄生电阻值、寄生电容值)很小,因此,rc延时小,进而数据传输速度没有损失,可实现存储芯片的高带宽数据传输。

110.示例性的,上述存储部分芯片和/或上述控制部分芯片之间可以通过混合键合方式连接。上述混合键合方式可以为通过金属导体使上述存储部分的连接焊盘和上述控制部分的连接焊盘相连接。上述存储部分可以看作是3d存储芯片的多个堆叠的芯片中主要作为存储功能使用的芯片,上述控制部分可以看作是3d存储芯片的多个堆叠的芯片中主要作为控制功能使用的芯片。

111.根据一些实施例,在上述存储芯片中,除了存储部分芯片与控制部分芯片之间可以采用上述混合键合方式连接,上述存储部分芯片之间也可以通过混合键合方式相连接,上述控制部分芯片之间也可以通过混合键合方式相连接。

112.在一些示例中,上述存储部分包括具有相同容量存储阵列的两个或三个以上的存储部分芯片;和/或,上述存储部分包括具有不同容量存储阵列的两个或三个以上的存储部分芯片。

113.根据一些实施例,两个或三个以上的存储部分芯片可以设置在同一平面,每个上述存储部分芯片相互独立。这里的存储部分芯片可以是具有存储阵列的存储单元,这些存储单元可以分别与上述控制部分通过混合键合方式以金属导体相连接。这里的同一平面芯片中多个存储单元可以没有物理连接关系,即,不通过引脚连线或金属导体相连接。

114.图5为本发明实施例提供的一种具有多个存储单元的3d存储芯片的示意性结构图。这里具有多个存储单元是指存储部分在同一平面芯片中具有多个存储单元。如图5所示,上述存储部分可以包括第一存储单元、第二存储单元直到第n存储单元,上述n个存储单元可以分别与上述控制部分通过混合键合以金属导体相连接。上述n个存储单元之间可以没有物理连接关系,即,上述n个存储单元不通过引脚连线或金属导体相连接,但是上述n个存储单元并没有相互堆叠设置,而是在位置上设置在同一平面。

115.具体的,上述n个存储单元与上述控制部分相连的一侧表面设置有连接焊盘作为用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体(混合键合),相应的在控制部分与上述n个存储单元相连的一侧表面也可以设置有连接焊盘,再通过上述混合键合的金属导体连接,使得上述控制部分和上述n个存储单元分别连接及进行数据通信。此种结构,控制部分对存储部分的控制相对容易,可靠性相对较高。n个存储单元可以为相同容量(或不同容量)的存储阵列,彼此相互独立。示例性的,在需要时上述相互独立的存储单元可以相互取代。这样的好处是,如果某一个存储单元出现失效导致工作不正常,其它的存储单元可以作为冗余单元进行替换,从而提高整个3d存储芯片的可靠性。

116.示例性的,参见图5,采用一个平面芯片构成的控制部分和多个存储单元作为一个平面的存储部分,如前述因为在芯片背面设置连接焊盘需要进行衬底的挖孔,所以相比较而言,在最顶层金属上设置连接焊盘进行混合键合相对更为容易、可靠性也更高。所以存储部分和控制部分优先采用面对面的混合键合方式,即控制部分100的芯片正面和存储部分

200的芯片正面相对,两部分的芯片正面通过混合键合的方式连接,控制部分100的芯片反面和存储部分200的芯片反面在外侧。

117.根据一些实施例,在上述存储芯片中,上述两个或三个以上的存储部分芯片堆叠设置,相邻的两个芯片之间通过混合键合的方式相连接。可以理解的是,不仅存储部分与控制部分的芯片可以采用混合键合的方式相连接,存储部分芯片与存储部分芯片之间也可以采用上述混合键合方式连接。在上述两个或三个以上的存储部分芯片堆叠设置且相邻的两个芯片之间通过混合键合的方式相连接时,上述存储芯片方案可以存在多种情况,当然每种情况也具有相应的功能和特点。

118.示例性的,两个或三个以上的上述存储部分芯片可以不间隔的堆叠设置。图6为本发明实施例提供的另一种具有多个存储部分的3d存储芯片的示意性结构图,如图6所示,上述存储芯片的控制部分可以包括一个控制部分芯片110,上述控制部分芯片具有数据及信号处理的功能。上述存储芯片的存储部分可以包括第一存储部分芯片210和第二存储部分芯片220。控制部分芯片110、第一存储部分芯片210和第二存储部分芯片220自上而下依次堆叠。上述第一存储部分芯片210和第二存储部分芯片220与上述控制部分芯片110堆叠设置。具体的,上述第一存储部分芯片210与上述控制部分芯片110相连的一侧表面设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合方式,相应的在控制部分芯片110与上述第一存储部分芯片210相连的一侧表面也可以设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述金属焊盘上生长金属导体以混合键合方式使得上述控制部分芯片110和上述存储部分芯片210连接及进行数据通信。

119.这里需要说明的是,如前述因为在芯片的最顶层金属上设置连接焊盘进行混合键合相对更为容易、可靠性也更高,所以控制部分芯片110正面面对第一存储部分芯片210。相应的,由于上述存储部分芯片210还需要继续连接上述存储部分芯片220,第二存储部分芯片220也设置为正面面对第一存储部分芯片210。即在控制部分芯片110和第二存储部分芯片220的正面设置连接焊盘,用于与混合键合中的金属导体连接。

120.对于放置在控制部分芯片110和第二存储部分芯片220之间的第一存储部分芯片210,因为它的正面和背面都要通过混合键合的方式与控制部分芯片110和第二存储部分芯片220相连接,所以它的正面朝向可以依情况放置。但是,为了保证第一存储部分芯片210和第二存储部分芯片220的一致性,通常第一存储部分芯片210和第二存储部分芯片220正面的朝向最好一致,这样,第一存储部分芯片210和第二存储部分芯片220的一致性会很好,相对整个3d芯片而言,存储部分的第一存储部分芯片210和第二存储部分芯片220的匹配性会很好,由此制造的芯片可靠性以及芯片工作的可靠性、数据读写的可靠性会很好。

121.可以理解的是,上述存储部分可以为多个存储部分芯片堆叠。上述存储芯片具有扩展存储容量方便及形式简单的优点。当上述存储部分为多个存储部分芯片堆叠时,多个存储部分芯片堆叠时方向一致,即多个存储部分芯片正面都朝上或都朝下。

122.示例性的,上述存储部分堆叠的多个存储部分芯片可以为同样的芯片,也可以为不同的芯片。上述存储部分堆叠的多个存储部分芯片为不同的芯片时,可以包括至少一个易失存储芯片,例如:dram存储芯片,和至少一个非易失存储芯片,例如:nandflash存储芯片。这样的好处是既能通过dram存储芯片保证数据存取的速度,又能通过nandflash存储芯片,确保在芯片掉电时,非易失存储芯片上的数据不会丢失。

123.根据一些实施例,在上述存储芯片中,两个或三个以上的上述存储部分芯片之间隔地堆叠设置有至少一个所述控制部分芯片,上述控制部分芯片两侧的存储部分芯片数量相同。具体的,图7为本发明实施例提供的又一种具有多个存储部分的3d存储芯片的示意性结构图,如图7所示,上述存储芯片的控制部分可以包括一个控制部分芯片110,上述控制部分芯片具有数据及信号处理的功能。上述存储部分可以包括第一存储部分芯片210和第二存储部分芯片220。上述存储芯片还可以形成其他结构,例如,控制部分的控制部分芯片110设置在第一存储部分芯片210和第二存储部分芯片220之间。

124.具体的,上述第一存储部分芯片210与上述控制部分芯片110相连的一侧表面设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合,相应的在控制部分芯片110与上述第一存储部分芯片210相连的一侧表面也可以设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合,使得上述控制部分芯片110和上述第一存储部分芯片210连接及进行数据通信。相应的,由于上述控制部分芯片110还需要继续连接上述第二存储部分芯片220,所以需要在上述控制部分芯片110背离上述金属导体的一侧设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合,并通过混合键合的方式与上述第二存储部分芯片220继续连接,形成芯片堆叠结构。上述存储芯片具有扩展存储容量方便、形式简单及对称性好的优点。需要说明的是,上述存储部分不限于具有第一存储部分芯片210和第二存储部分芯片220,还可以具有更多的存储部分芯片并继续形成芯片堆叠结构。

125.同样的,上述存储芯片具有扩展存储容量方便及形式简单的优点。上述存储部分堆叠的多个存储部分芯片可以为同样的芯片,也可以为不同的存储芯片。上述存储部分堆叠的多个存储部分芯片为不同的芯片时,可以包括其中至少一个为易失存储芯片,如dram存储芯片,和至少一个另一个为非易失存储芯片,如nand flash存储芯片。这样的好处是既能通过dram存储芯片保证数据存取的速度,又能通过nand flash存储芯片,确保在芯片掉电时,非易失存储芯片上的数据不会丢失。

126.根据一些实施例,在上述存储芯片中,上述两个或三个以上的控制部分芯片堆叠设置,相邻的两个芯片之间通过金属导体以混合键合方式相连接。在上述两个或三个以上的控制部分芯片堆叠设置且相邻的两个芯片之间通过金属导体相连接时,上述存储芯片方案可以存在多种情况,当然每种情况也具有相应的功能和特点。

127.示例性的,上述存储芯片中,两个或三个以上的上述控制部分芯片可以包括至少一个模拟功能电路芯片和至少一个数字功能电路芯片,其中,上述模拟功能电路芯片仅设置有模拟功能电路,上述数字功能电路芯片仅设置有数字功能电路。图8为本发明实施例提供的一种具有多个控制部分的3d存储芯片的示意性结构图,如图8所示,上述存储芯片的存储部分可以包括一个存储部分芯片210。上述存储芯片的控制部分可以包括第一控制部分芯片110和第二控制部分芯片120,上述第一控制部分芯片110具有数据及信号处理的功能,上述第二控制部分芯片120具有电源供给的功能。上述第一控制部分芯片110和第二控制部分芯片120与上述存储部分芯片210堆叠设置。第一控制部分芯片110、第二控制部分芯片120和存储部分芯片210自上而下依次堆叠。

128.具体的,上述第二控制部分芯片120与上述存储部分芯片210相连的一侧表面设置

有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合;相应的,在存储部分芯片210与上述第二控制部分芯片120相连的一侧表面也可以设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合。使得上述第二控制部分芯片120和上述存储部分芯片210连接及进行数据通信。相应的,由于上述第二控制部分芯片120还需要继续连接上述第一控制部分芯片110,所以需要在上述第二控制部分芯片120背离上述存储部分芯片210的一侧设置连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体(混合键合);并通过上述混合键合的方式与上述控制部分芯片110继续连接,形成芯片堆叠结构。

129.需要说明的是,上述存储部分不限于存储部分芯片210,上述控制部分不限于第一控制部分芯片110和第二控制部分芯片120,还可以具有更多的控制部分芯片并继续形成芯片堆叠结构。上述存储芯片由于控制部分分为多个芯片,可以分别设置模拟功能和数字功能,是的控制部分能够兼容模拟功能工艺和数字功能工艺,能够结合各个工艺的优点性能更强。

130.同样的,除了如图8中所示的第一控制部分芯片110、存储部分芯片210和第二控制部分芯片220由上至下一次堆叠的方式,也可以为其它的方式,它们的堆叠顺序不限定。

131.上述存储部分的存储部分芯片210可以设置有最基本的存储单元,例如,存储阵列。而上述存储芯片的功能电路可以设置在上述控制部分芯片110和控制部分芯片120中。控制部分芯片110的功能电路可以包括:行列译码电路、数据处理电路和接口电路。控制部分芯片120的功能电路可以包括:电源电路。在上述存储芯片中,在对上述存储部分进行数据读出时,由控制部分通过接收上述读数据相关的命令,上述行列译码电路对地址进行解码后,选中存储部分中相应存储阵列中的数据,数据从存储部分进入到控制部分,之后在控制部分中再经过接口电路的驱动和数据处理电路时钟控制进行数据的读出。在上述存储芯片中,在对上述存储部分进行数据写入时,数据在上述控制部分经过接口电路的驱动和数据处理电路的数据线的分配后,写入到上述存储部分的存储阵列中,从而能够完整实现存储芯片的基本功能。因为存储阵列中的存储单元使用的是能够存储数据的特殊工艺,所以它的制作生产工艺非常的复杂和不好控制。将存储阵列放置在存储部分可以保证工艺的一致性,且因为其他电路已经放到控制部分,所以它的工艺的特殊性不会对其他电路造成影响。

132.图9为本发明实施例提供的另一种具有多个控制部分的3d存储芯片的示意性结构图,如图9所示,上述存储芯片的控制部分可以包括一个存储部分芯片210。上述存储芯片的控制部分可以包括第一控制部分芯片110和第二控制部分芯片120,上述第一控制部分芯片110可以具有数据及信号处理的功能,上述第二控制部分芯片120可以具有电源供给的功能。上述第一控制部分芯片110和第二控制部分芯片120与上述存储部分芯片210堆叠设置。具体的,上述第二控制部分芯片120与上述存储部分芯片210相连的一侧表面设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合。相应的在存储部分芯片210与上述第二控制部分芯片120相连的一侧表面也可以设置有连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合。使得上述控第二制部分芯片120和上述存储部分芯片210连接及进行数据通信。相应的,由于上述存储部分芯片210还需要继续连接上述第一控制部分芯片110,所以需要在

上述存储部分芯片210背离上述金属导体的一侧设置连接焊盘用于与混合键合中的金属导体连接,之后在上述连接焊盘上生长金属导体形成混合键合,并通过混合键合的方式与上述第一控制部分芯片110继续连接,形成芯片堆叠结构。需要说明的是,上述存储部分不限于存储部分芯片210,上述控制部分不限于具有控制部分芯片210和220,还可以具有更多的控制部分芯片并继续形成芯片堆叠结构。上述存储芯片由于控制部分分为多个芯片,可以分别设置模拟功能电路和数字功能电路,是的控制部分能够兼容模拟功能工艺和数字功能工艺,能够结合各个工艺的优点性能更强。

133.在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接或彼此可通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

134.尽管本发明的实施方案已公开如上,但其并不仅仅限于说明书和实施方式中所列运用,它完全可以被适用于各种适合本发明的领域,对于熟悉本领域的人员而言,可容易地实现另外的修改,因此在不背离权利要求及等同范围所限定的一般概念下,本发明并不限于特定的细节与这里示出与描述的图例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1