半导体存储器装置及半导体存储器装置的制造方法与流程

1.本公开总体上可以涉及半导体存储器装置及半导体存储器装置的制造方法,并且更具体地,涉及三维半导体存储器装置及三维半导体存储器装置的制造方法。

背景技术:

2.半导体存储器装置包括能够存储数据的多个存储器单元。三维半导体存储器装置的存储器单元可以三维地布置。当制造三维半导体存储器装置时,由于各种原因可能会发生故障。因此,半导体存储器装置的操作特性可能会劣化。

技术实现要素:

3.根据本公开的一方面,一种半导体存储器装置可以包括沟道结构、阻挡绝缘层、数据储存层、上选择线和隧道绝缘层。沟道结构可以包括第一柱部和从第一柱部延伸的第二柱部。阻挡绝缘层可以围绕沟道结构的第一柱部的侧壁。数据储存层可以设置在沟道结构的第一柱部和阻挡绝缘层之间。上选择线可以与阻挡绝缘层的端部和数据储存层的端部交叠,阻挡绝缘层的端部和数据储存层的端部面向第二柱部的延伸方向,上选择线围绕沟道结构的第二柱部的侧壁。隧道绝缘层可以设置在沟道结构的第一柱部和数据储存层之间,隧道绝缘层在沟道结构的第二柱部和上选择线之间延伸。

4.根据本公开的另一方面,一种半导体存储器装置可以包括第一沟道结构、第二沟道结构、隧道绝缘层、数据储存层、阻挡绝缘层、第一下选择线、第二下选择线、隔离层、第一上选择线、第二上选择线、层间绝缘层和字线。第一沟道结构和第二沟道结构可以彼此平行地延伸。隧道绝缘层可以围绕第一沟道结构和第二沟道结构中的每个的侧壁。数据储存层可以围绕第一沟道结构和第二沟道结构中的每个的侧壁,并且隧道绝缘层插置于数据储存层和第一沟道结构和第二沟道结构中的每个的侧壁之间。阻挡绝缘层可以围绕第一沟道结构和第二沟道结构中的每个的侧壁,并且数据储存层和隧道绝缘层插置于阻挡绝缘层和第一沟道结构和第二沟道结构中的每个的侧壁之间。第一下选择线可以围绕第一沟道结构,并且阻挡绝缘层、数据储存层和隧道绝缘层插置于第一下选择线和第一沟道结构之间。第二下选择线可以围绕第二沟道结构,并且阻挡绝缘层、数据储存层和隧道绝缘层插置于第二下选择线和第二沟道结构之间。隔离层可以设置在第一下选择线和第二下选择线之间。第一上选择线可以围绕第一沟道结构,并且隧道绝缘层插置于第一上选择线和第一沟道结构之间,第一上选择线设置在第一下选择线上。第二上选择线可以围绕第二沟道结构,并且隧道绝缘层插置于第二上选择线和第二沟道结构之间,第二上选择线设置在第二下选择线上。层间绝缘层和字线可以交替层叠在第一下选择线和第一上选择线之间,其中层间绝缘层和字线在第二下选择线和第二上选择线之间延伸。

5.根据本公开的另一方面,一种制造半导体存储器装置的方法可以包括:在基板上形成第一导电层;在第一导电层上交替层叠第一材料层和第二材料层;形成贯穿第一材料层和第二材料层的孔,孔延伸到基板的内部;在孔的表面上顺序地层叠阻挡绝缘层、数据储

存层和隧道绝缘层;在隧道绝缘层上形成填充孔的中央区域的沟道结构;去除基板,使得暴露出第一导电层和阻挡绝缘层;顺序地去除阻挡绝缘层的一部分和数据储存层的一部分,使得在第一导电层和隧道绝缘层之间限定凹陷区域;以及形成填充凹陷区域的第二导电层,第二导电层围绕隧道绝缘层。

附图说明

6.现在将在下文中参照附图来描述示例实施方式。然而,它们可以以不同的形式实施,并且不应被解释为限于本文阐述的实施方式。

7.在附图中,为了图示清楚,可能夸大了尺寸。将理解的是,当元件被称为在两个元件“之间”时,它可以是这两个元件之间的唯一元件,或者也可以存在一个或更多个中间元件。贯穿全文,相似的附图标记指代相似的元件。

8.图1是例示根据本公开的实施方式的半导体存储器装置的存储块的电路图。

9.图2是示意性地例示根据本公开的实施方式的半导体存储器装置的立体图。

10.图3a是例示图2所示的半导体存储器装置的位线的布局的平面图。

11.图3b是沿着图3a所示的线i-i

′

截取的半导体存储器装置的截面图。

12.图4是图3b中所示的区域a的放大截面图。

13.图5a是图4中所示的沟道结构的第一部分、隧道绝缘层和第二导电图案的截面图,而图5b是图4中所示的沟道结构的第一柱部、隧道绝缘层、数据储存层和第一阻挡绝缘层的截面图。

14.图6是例示根据本公开的实施方式的半导体存储器装置的存储块的电路图。

15.图7是示意性地例示根据本公开的实施方式的半导体存储器装置的立体图。

16.图8a是例示图7所示的半导体存储器装置的位线的布局的平面图。

17.图8b是沿着图8a所示的线ii-ii

′

截取的半导体存储器装置的截面图。

18.图9是图8b中所示的区域b的放大截面图。

19.图10a、图10b、图10c、图10d、图10e、图11、图12、图13、图14a、图14b、图15a、图15b、图16a、图16b、图17a、图17b和图17c是例示根据本公开的实施方式的半导体存储器装置的制造方法的图。

20.图18a、图18b、图18c、图18d、图18e、图18f、图18g、图18h、图18i、图18j、图18k、图18l、图18m和图18n是例示根据本公开的实施方式的半导体存储器装置的制造方法的图。

21.图19是例示根据本公开的实施方式的存储器系统的配置的框图。

22.图20是例示根据本公开的实施方式的计算系统的配置的框图。

具体实施方式

23.本文所公开的特定结构或功能描述仅是出于描述根据本公开的构思的实施方式的目的而例示的。根据本公开的构思的实施方式可以以各种形式来实现,并且不应被解释为限于本文阐述的实施方式。

24.实施方式提供了可以改善半导体存储器装置的操作特性的半导体存储器装置及半导体存储器装置的制造方法。

25.图1是例示根据本公开的实施方式的半导体存储器装置的存储块的电路图。

26.参照图1,半导体存储器装置可以包括多个存储块blk,其中每个存储块blk可以包括连接至公共源极层csl和位线bl的多个存储器单元串ms1、ms2和ms3。

27.存储器单元串ms1、ms2和ms3中的每个可以包括串联连接的多个存储器单元mc、源极选择晶体管sst、和至少一个漏极选择晶体管dst。在实施方式中,存储器单元串ms1、ms2和ms3中的每个可以包括连接在多个存储器单元mc和位线bl之间的一个漏极选择晶体管dst。在另一实施方式中,存储器单元串ms1、ms2和ms3中的每个可以包括连接在多个存储器单元mc和位线bl之间的两个或更多个漏极选择晶体管dst。

28.多个存储器单元mc可以经由源极选择晶体管sst连接至公共源极层csl,并且可以经由漏极选择晶体管dst连接至位线bl。

29.设置在相同高度的源极选择晶体管sst的栅极可以连接至彼此隔离的源极选择线ssl1、ssl2和ssl3。设置在相同高度的漏极选择晶体管dst的栅极可以连接至彼此隔离的漏极选择线dsl1、dsl2和dsl3。

30.在实施方式中,存储块blk可以包括在相同高度彼此隔离的第一源极选择线ssl1、第二源极选择线ssl2和第三源极选择线ssl3。存储块还可以包括在相同高度彼此隔离的第一漏极选择线dsl1、第二漏极选择线dsl2和第三漏极选择线dsl3。然而,本公开的实施方式不限于此。在另一实施方式中,存储块blk可以包括在相同高度彼此隔离的两条源极选择线,或者可以包括在相同高度彼此隔离的四条或更多条源极选择线。此外,存储块blk可以包括在相同高度彼此隔离的两条漏极选择线,或者可以包括在相同高度彼此隔离的四条或更多条漏极选择线,其中在相同高度彼此隔离的漏极选择线的数量可以等于或不同于在相同高度彼此隔离的源极选择线的数量。

31.多个存储器单元mc的栅极可以连接至多条字线wl,其中字线wl可以设置在不同的高度,并且设置在相同高度的存储器单元mc的栅极可以连接至单条字线wl。

32.多个存储器单元串ms1、ms2和ms3可以连接至每条字线wl。在实施方式中,多个存储器单元串ms1、ms2和ms3可以划分为可以由第一源极选择线ssl1、第二源极选择线ssl2和第三源极选择线ssl3单独选择的第一组、第二组和第三组。第一组可以包括第一存储器单元串ms1。第二组可以包括第二存储器单元串ms2。第三组可以包括第三存储器单元串ms3。

33.第一存储器单元串ms1可以经由连接至第一漏极选择线dsl1的漏极选择晶体管dst分别连接至位线bl。第二存储器单元串ms2可以经由连接至第二漏极选择线dsl2的漏极选择晶体管dst分别连接至位线bl。第三存储器单元串ms3可以经由连接至第三漏极选择线dsl3的漏极选择晶体管dst分别连接至位线bl。第一存储器单元串ms1中的一个、第二存储器单元串ms2中的一个、以及第三存储器单元串ms3中的一个可以连接至单条位线bl。

34.根据施加至第一源极选择线ssl1的栅极信号,第一存储器单元串ms1可以连接至公共源极层csl。根据施加至第二源极选择线ssl2的栅极信号,第二存储器单元串ms2可以连接至公共源极层csl。第三存储器单元串ms3可以根据施加至第三源极选择线ssl3的栅极信号来连接至公共源极层csl。因此,多个存储器单元串ms1、ms2和ms3可以被隔离为在读取操作或验证操作中可以针对源极选择线ssl1、ssl2和ssl3中的每一条同时被单独选择的组。在实施方式中,在读取操作或验证操作中,可以选择第一源极选择线ssl1、第二源极选择线ssl2和第三源极选择线ssl3中的一条,使得第一组的第一存储器单元串ms1、第二组的第二存储器单元串ms2和第三组的第三存储器单元串ms3当中的一个组可以连接至公共源

极层csl。因此,在本公开的实施方式中,与在读取操作或验证操作中第一存储器单元串ms1、第二存储器单元串ms2和第三存储器单元串ms3同时连接至公共源极层的情况相比,可以减小沟道电阻。因此,在本公开的实施方式中,可以减少读取干扰。

35.图2是示意性地例示根据本公开的实施方式的半导体存储器装置的立体图。

36.参照图2,半导体存储器装置可以包括外围电路结构ps、位线bl、栅极层叠结构gst1和gst2以及公共源极层csl。栅极层叠结构gst1和gst2中的每一个可以构成存储块。

37.为了控制存储器单元的操作,外围电路结构ps可以包括外围电路。

38.栅极层叠结构gst1和gst2中的每一个可以与外围电路结构ps交叠,并且可以设置在位线bl和公共源极层csl之间。外围电路结构ps可以与栅极层叠结构gst1和gst2交叠,并且位线bl插置于其间。公共源极层csl可以与位线bl交叠,并且栅极层叠结构gst1和gst2可以插置于其间。

39.栅极层叠结构gst1和gst2可以包括第一栅极层叠结构gst1和第二栅极层叠结构gst2,第一栅极层叠结构gst1和第二栅极层叠结构gst2彼此面对。

40.第一栅极层叠结构gst1和第二栅极层叠结构gst2中的每一个可以包括:包括上选择线的上选择组、包括下选择线的下选择组、以及设置在上选择组和下选择组之间的字线wl。在实施方式中,上选择线可以被配置为源极选择线ssl1、ssl2和ssl3。下选择线可以被配置为漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b。

41.源极选择线ssl1、ssl2和ssl3,字线wl以及漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b中的每一个可以在第一方向d1和第二方向d2上延伸,其中第一方向d1可以被定义为xyz坐标系中的x轴的方向。第二方向d2可以被定义为xyz坐标系中的y轴的方向。

42.源极选择线ssl1、ssl2和ssl3可以在相同的高度彼此隔离。在实施方式中,源极选择线ssl1、ssl2和ssl3可以在第一方向d1上彼此间隔开。源极选择线ssl1、ssl2和ssl3可以设置在公共源极层csl和包括字线wl的层叠结构之间。

43.字线wl可以在第三方向d3上彼此间隔开,第三方向d3可以被定义为xyz坐标系中的z轴的方向。

44.每条字线wl可以延伸以与彼此隔离的源极选择线ssl1、ssl2和ssl3交叠。

45.漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b可以设置在位线bl与包括字线wl的层叠结构之间的至少一层中。在实施方式中,漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b可以包括第一高度的漏极选择线dsl1a、dsl2a和dsl3a以及第二高度的漏极选择线dsl1b、dsl2b和dsl3b。第二高度的漏极选择线dsl1b、dsl2b和dsl3b可以在第三方向d3上与第一高度的漏极选择线dsl1a、dsl2a和dsl3a间隔开。第一高度的漏极选择线dsl1a、dsl2a和dsl3a可以在位线bl的延伸方向上彼此间隔开,并且第二高度的漏极选择线dsl1b、dsl2b和dsl3b也可以在位线bl的延伸方向上彼此间隔开。在实施方式中,第一高度的漏极选择线dsl1a、dsl2a和dsl3a以及第二高度的漏极选择线dsl1b、dsl2b和dsl3b可以在第一方向d1上彼此间隔开。

46.外围电路结构ps可以与包括源极选择线ssl1、ssl2和ssl3的上选择组交叠。除了包括漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b的下选择组之外,位线bl可以设置在外围电路结构ps和包括源极选择线ssl1、ssl2和ssl3的上选择组之间。

47.位线bl和公共源极线中的每一者可以延伸以与第一栅极层叠结构gst1和第二栅极层叠结构gst2交叠。

48.图3a是例示图2所示的半导体存储器装置的位线的布局的平面图。

49.参照图3a,位线bl可以彼此平行地延伸,并且可以彼此间隔开。在实施方式中,位线bl可以在第一方向d1上延伸,并且可以在第二方向d2上彼此间隔开。

50.位线bl可以连接至在第三方向d3上延伸的沟道结构ch,并且可以经由位线接触结构ct连接至沟道结构ch。

51.沟道结构ch可以贯穿第一栅极层叠结构gst1和第二栅极层叠结构gst2,并且可以被划分成由彼此间隔开的源极选择线ssl1、ssl2和ssl3控制的组。在实施方式中,沟道结构ch可以包括配置有第一沟道结构ch1的第一组、配置有第二沟道结构ch2的第二组和配置有第三沟道结构ch3的第三组。第一沟道结构ch1的侧壁可以由第一栅极层叠结构gst1的第一源极选择线ssl1围绕。第一沟道结构ch1可以由第一源极选择线ssl1控制。第二沟道结构ch2的侧壁可以由第一栅极层叠结构gst1的第二源极选择线ssl2围绕,并且第二沟道结构ch2可以由第二源极选择线ssl2控制。第三沟道结构ch3的侧壁可以由第二栅极层叠结构gst2的第三源极选择线ssl3围绕。第三沟道结构ch3可以由第三源极选择线ssl3控制。

52.第一沟道结构ch1中的一个、第二沟道结构ch2中的一个和第三沟道结构ch3中的一个可以并联连接至单条位线bl。

53.第一栅极层叠结构gst1的字线wl可以延伸以围绕第一沟道结构ch1的侧壁和第二沟道结构ch2的侧壁。

54.附图中所示的实施方式例示了第一高度的漏极选择线dsl1a、dsl2a和dsl3a之间的隔离结构以及第二高度的漏极选择线dsl1b、dsl2b和dsl3b之间的隔离结构与第二源极选择线ssl2和第三源极选择线ssl3之间的隔离结构相似的情况。更具体地,第一高度的漏极选择线dsl1a、dsl2a和dsl3a可以包括第一高度的第一漏极选择线至第三漏极选择线。第二高度的漏极选择线dsl1b、dsl2b和dsl3b可以包括第二高度的第一漏极选择线至第三漏极选择线。

55.第一沟道结构ch1可以贯穿第一高度的第一漏极选择线dsl1a和第二高度的第一漏极选择线dsl1b。第二沟道结构ch2可以贯穿第一高度的第二漏极选择线dsl2a和第二高度的第二漏极选择线dsl2b。第三沟道结构ch3可以贯穿第一高度的第三漏极选择线dsl3a和第二高度的第三漏极选择线dsl3b。

56.参照图3a中,线i-i

′

与单条位线bl交叠。与单条位线bl交叠的沟道结构ch可以包括:经由与线i-i

′

交叠的位线接触结构ct连接至单条位线bl的沟道结构;以及经由与线i-i

′

不交叠的位线接触结构ct连接至另一条位线bl的沟道结构。

57.图3b是沿着图3a所示的线i-i

′

截取的半导体存储器装置的截面图。

58.参照图3b,源极选择线ssl1、ssl2和ssl3可以通过沟槽t彼此隔离,沟槽t可以填充有上绝缘层197。上绝缘层197可以在公共源极层csl和包括源极选择线ssl1、ssl2和ssl3的上选择组之间延伸。

59.公共源极层csl可以包括顺序层叠在上绝缘层197上的掺杂半导体层199a、导电金属屏障层199b和金属层199c。掺杂半导体层199a可以包括n型杂质和p型杂质中的至少一个。

60.第一栅极层叠结构gst1的字线wl可以通过栅极隔离层151与第二栅极层叠结构gst2的字线wl间隔开。第一栅极层叠结构gst1的字线wl也可以通过栅极隔离层151与第二栅极层叠结构gst2的字线wl绝缘。栅极隔离层151可以在包括第一栅极层叠结构gst1的漏极选择线dsl1a、dsl2a、dsl1b和dsl2b的第一下选择组与包括漏极选择线dsl3a和dsl3b的第二下选择组之间延伸。

61.第一栅极层叠结构gst1和第二栅极层叠结构gst2中的每个还可以包括在第三方向d3上彼此间隔开地层叠的层间绝缘层111。针对字线wl和漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b提供的导电层与层间绝缘层111可以在第三方向d3上交替设置。

62.包括于第一栅极层叠结构gst1中的第一高度的第一漏极选择线dsl1a可以通过漏极隔离层153与包括于第一栅极层叠结构gst1中的第一高度的第二漏极选择线dsl2a间隔开。包括于第一栅极层叠结构gst1中的第一高度的第一漏极选择线dsl1a可以通过漏极隔离层153与包括于第一栅极层叠结构gst1中的第一高度的第二漏极选择线dsl2a绝缘。漏极隔离层153可以在第二高度的第一漏极选择线dsl1b和第二高度的第二漏极选择线dsl2b之间延伸。第二高度的第一漏极选择线dsl1b包括在第一栅极层叠结构gst1中。第二高度的第二漏极选择线dsl2b包括在第一栅极层叠结构gst1中。

63.沟道结构ch中的每个可以包括沟道层131和芯绝缘层133,其中沟道层131可以包括半导体材料。沟道层131可以围绕芯绝缘层133的侧壁,并且可以沿着芯绝缘层133的第一表面延伸。芯绝缘层133面对公共源极层csl,并且也可以与掺杂半导体图案135交叠。掺杂半导体图案135可以与芯绝缘层133的面对位线bl的第二表面接触。沟道层131可以延伸以围绕掺杂半导体图案135的侧壁。

64.每个沟道结构ch可以包括第一柱部pa和从第一柱部pa在第三方向d3上延伸的第二柱部pb,其中第一柱部pa的中央区域可以填充有芯绝缘层133和掺杂半导体图案135,并且芯绝缘层133可以延伸到第二柱部pb的中央区域。第一柱部pa的外壁和第二柱部pb的外壁可以配置有沟道层131。

65.参照第一层叠结构gst1,第一柱部pa的侧壁不仅可以由层间绝缘层111和字线wl围绕,而且可以由对应于第一柱部pa的第一高度的漏极选择线dsl1a或dsl2a和对应于第一柱部pa的第二高度的漏极选择线dsl1b或dsl2b围绕。第二柱部pb的侧壁可以由对应于第二柱部pb的源极选择线ssl1或ssl2围绕,其中沟道结构ch的第二柱部pb可以在第三方向d3上延伸以贯穿上绝缘层197,并且可以延伸到公共源层csl的内部。

66.第一柱部pa的侧壁可以由第一阻挡绝缘层121、数据储存层123和隧道绝缘层125围绕。第一阻挡绝缘层121、数据储存层123和隧道绝缘层125可以设置在第一柱部pa1与层间绝缘层111和字线wl中的每一个之间。第一阻挡绝缘层121、数据储存层123和隧道绝缘层125可以在第一柱部pa和对应于第一柱部pa的第一高度的漏极选择线dsl1a或dsl2a之间延伸,并且可以在第一柱部pa和对应于第一柱部pa的第二高度的漏极选择线dsl1b或dsl2b之间延伸。

67.数据储存层123可以设置在第一阻挡绝缘层121和第一柱部pa之间。隧道绝缘层125可以设置在数据储存层123和第一柱部pa之间,并且可以在第二柱部pb和对应于第二柱部pb的源极选择线ssl1或ssl2之间延伸。

68.每个沟道结构ch的第二柱部pb可以比隧道绝缘层125在第三方向d3上更突出。每个沟道结构ch可以具有锥状形状。随着沟道结构ch变得越靠近位线bl和外围电路结构ps,沟道结构ch的宽度变得越宽。

69.位线bl可以通过绝缘层161与沟道结构ch间隔开,绝缘层161可以在位线bl与第一栅极层叠结构gst1和第二栅极层叠结构gst2中的每一个之间延伸。位线接触结构ct可以在贯穿绝缘层161的同时将一些沟道结构ch电连接至位线bl。

70.位线bl可以通过第一绝缘结构163与外围电路结构ps间隔开,该第一绝缘结构163可以包括层叠在位线bl和外围电路结构ps之间的两个或更多个绝缘层。

71.第一互连结构165和第一导电接合焊盘167可以掩埋在第一绝缘结构163中,其中第一互连结构165可以包括多个导电图案。第一导电接合焊盘167可以连接至第一互连结构165,并且可以面对外围电路结构ps。在实施方式中,第一导电接合焊盘167可以经由第一互连结构165电连接至位线bl。

72.外围电路结构ps可以包括包含晶体管180a和180b的基板171、第二绝缘结构191、第二互连结构193和第二导电接合焊盘195。

73.晶体管180a和180b可以设置在基板171的由隔离层173分隔开的有源区中。晶体管180a和180b中的每个可以包括设置在有源区上的栅极绝缘层181、设置在栅极绝缘层181上的栅电极183、以及形成于栅电极183两侧的有源区中的结185。晶体管180a和180b中的一些(例如,180b)可以构成用于控制位线bl的预充电操作和放电操作的页缓冲器电路。

74.第二绝缘结构191可以设置在第一绝缘结构163和基板171之间,可以包括两个或更多个绝缘层并且可以接合到第一绝缘结构163。

75.第二互连结构193和第二导电接合焊盘195可以掩埋在第二绝缘结构191中,其中第二互连结构193可以包括多个导电图案。第二导电接合焊盘195可以连接至第二互连结构193,并且可以面对第一导电接合焊盘167。第二导电接合焊盘195可以接合至第一导电接合焊盘167,并且可以经由第二互连结构193电连接至页缓冲器电路的晶体管180b。

76.根据以上描述的实施方式,位线bl可以经由第一互连结构165、第一导电接合焊盘167、第二导电接合焊盘195和第二互连结构193连接至页缓冲器电路的晶体管180b。

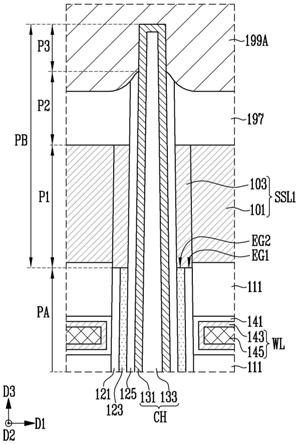

77.图4是图3b中所示的区域a的放大截面图。

78.参照图4,第一阻挡绝缘层121可以包括面向第三方向d3的端部eg1,并且数据储存层123还可以包括面向第三方向d3的端部eg2。根据第一阻挡绝缘层121的蚀刻量和数据储存层123的蚀刻量,第一阻挡绝缘层121的端部eg1和数据储存层123的端部eg2的位置可以变化。第一阻挡绝缘层121的端部eg1可以与数据储存层123的端部eg2设置在相同的高度,或者可以与数据储存层123的端部eg2设置在不同的高度。

79.源极选择线(例如,ssl1)可以与第一阻挡绝缘层121的端部eg1和数据储存层123的端部eg2交叠。根据第一阻挡绝缘层121的蚀刻量和数据储存层123的蚀刻量,源极选择线ssl1和第一阻挡绝缘层121的端部eg1之间的界面以及源极选择线ssl1和数据储存层123的端部eg2之间的界面可以设置在与源极选择线ssl1和层间绝缘层111之间的界面的高度基本相等或不同的高度。

80.源极选择线ssl1可以包括第一导电图案101和第二导电图案103,其中第一导电图案101可以在平面方向上延伸以与第二柱部pb交叉。在实施方式中,第一导电图案101可以

在第一方向d1和第二方向d2上延伸以平行于字线wl。第二导电图案103可以设置在第一导电图案101和隧道绝缘层125之间。

81.第二导电图案103可以包括硅、金属硅化物和导电金属屏障物中的至少一种,其中金属硅化物可以包括硅化钨或硅化镍,并且导电金属屏障物可以包括钛和氮化钛。

82.沟道结构ch的第二柱部pb可以包括由源极选择线ssl1围绕的第一部分p1、从第一部分p1在第三方向d3上延伸的第二部分p2、以及从第二部分p2在第三方向d3上延伸的第三部分p3。第二部分p2和第三部分p3可以在第三方向d3上比源极选择线ssl1突出更远。第二部分p2的侧壁可以由上绝缘层197围绕。第三部分p3可以与公共源极层的掺杂半导体层199a接触。

83.沟道结构ch的芯绝缘层133可以从第一柱部pa的中央区域延伸到第一部分p1、第二部分p2和第三部分p3中的每个的中央区域。沟道结构ch的沟道层131可以延伸以构成第一部分p1、第二部分p2和第三部分p3中的每个的外壁。公共源极层的掺杂半导体层199a可以与第三部分p3的沟道层131接触。

84.字线wl可以包括导电金属屏障层143和金属层145。第二阻挡绝缘层141可以设置在字线wl和第一阻挡绝缘层121之间,并且可以在层间绝缘层111和字线wl之间延伸。像字线wl一样,图3b中所示的漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b中的每条可以包括导电金属屏障层143和金属层145。第二阻挡绝缘层141可以设置在第一阻挡绝缘层121与图3b中所示的漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b中的每条之间,并且在层间绝缘层111和图3b中所示的漏极选择线dsl1a、dsl2a、dsl3a、dsl1b、dsl2b和dsl3b之间延伸。

85.第二阻挡绝缘层141可以包括介电常数高于第一阻挡绝缘层121的介电常数的绝缘材料,并且尽管在附图中未示出,但是可以省略第二阻挡绝缘层141。

86.图5a是图4中所示的沟道结构的第一部分、隧道绝缘层和第二导电图案的截面图。图5b是图4中所示的沟道结构的第一柱部、隧道绝缘层、数据储存层和第一阻挡绝缘层的截面图。

87.参照图5a和图5b,沟道结构ch的芯绝缘层133的侧壁可以由沟道结构ch的沟道层131围绕,其中沟道层131的侧壁可以由隧道绝缘层125围绕。

88.参照图5a,隧道绝缘层125可以延伸以围绕第二柱部pb的侧壁的一部分。第二柱部pb的第一部分p1的侧壁可以由隧道绝缘层125围绕,其中隧道绝缘层125可以与第二柱部pb的第一部分p1接触。第二柱部pb的第一部分p1可以由源极选择线(例如,图4中所示的ssl1)的第二导电图案103围绕,并且隧道绝缘层125插置于其间,使得可以在第一部分p1和源极选择线的交叉部分限定具有全环绕栅极(gate all around:gaa)的源极选择晶体管。

89.参照图5b,隧道绝缘层125可以延伸以围绕第一柱部pa的侧壁。第一柱部pa的侧壁可以不仅由隧道绝缘层125围绕,而且由围绕隧道绝缘层125的侧壁的数据储存层123和围绕数据储存层123的侧壁的第一阻挡绝缘层121围绕。

90.在实施方式中,数据储存层123可以形成为能够存储使用fowler-nordheim(福勒-诺德海姆隧穿)改变的数据的材料层。材料层可以包括能够捕获电荷的氮化物层。第一阻挡绝缘层121可以包括能够阻挡电荷的氧化物层。隧道绝缘层125可以形成为电荷可以通过隧穿通过的氧化硅层。

91.图6是例示根据本公开的实施方式的半导体存储器装置的存储块的电路图。

92.参照图6,半导体存储器装置可以包括多个存储块blk

′

,其中每个存储块blk

′

可以包括连接至公共源极层csl

′

和位线bl

′

的多个存储器单元串ms1

′

、ms2

′

和ms3

′

。

93.存储器单元串ms1

′

、ms2

′

和ms3

′

中的每个可以包括串联连接的多个存储器单元mc

′

、漏极选择晶体管dst

′

和至少一个源极选择晶体管sst

′

。在实施方式中,存储器单元串ms1

′

、ms2

′

和ms3

′

中的每个可以包括连接在多个存储器单元mc

′

和公共源极层csl

′

之间的一个源极选择晶体管sst

′

。在另一实施方式中,存储器单元串ms1

′

、ms2

′

和ms3

′

中的每个可以包括串联连接在多个存储器单元mc

′

和公共源极层csl

′

之间的两个或更多个源极选择晶体管sst

′

。

94.多个存储器单元mc

′

可以经由源极选择晶体管sst

′

连接至公共源极层csl

′

。多个存储器单元mc

′

可以经由漏极选择晶体管dst

′

连接至位线bl

′

。

95.设置在相同高度的漏极选择晶体管dst

′

的栅极可以连接至彼此隔离的漏极选择线dsl1

′

、dsl2

′

和dsl3

′

。

96.在实施方式中,存储块blk

′

可以包括在相同高度彼此隔离的第一漏极选择线dsl1

′

、第二漏极选择线dsl2

′

和第三漏极选择线dsl3

′

。然而,本公开的实施方式不限于此。在另一实施方式中,存储块blk

′

可以包括在相同高度彼此隔离的两条漏极选择线,或者可以包括在相同高度彼此隔离的四条或更多条漏极选择线。

97.设置在相同高度的源极选择晶体管sst

′

的栅极可以连接至单条源极选择线ssl

′

。

98.多个存储器单元mc

′

的栅极可以连接至多条字线wl

′

,其中,字线wl

′

可以设置在不同的高度,并且设置在相同高度的存储器单元mc

′

的栅极可以连接至单条字线wl

′

。

99.多个存储器单元串ms1

′

、ms2

′

和ms3

′

可以连接至每条字线wl

′

。在实施方式中,多个存储器单元串ms1

′

、ms2

′

和ms3

′

可以划分为第一组、第二组和第三组,第一组、第二组和第三组可以由第一漏极选择线dsl1

′

、第二漏极选择线dsl2

′

和第三漏极选择线dsl3

′

单独选择。第一组可以包括第一存储器单元串ms1

′

,第二组可以包括第二存储器单元串ms2

′

,并且第三组可以包括第三存储器单元串ms3

′

。

100.第一存储器单元串ms1

′

可以经由连接至第一漏极选择线dsl1

′

的漏极选择晶体管dst

′

分别连接至位线bl

′

。第二存储器单元串ms2

′

可以经由连接至第二漏极选择线dsl2

′

的漏极选择晶体管dst

′

分别连接至位线bl

′

。第三存储器单元串ms3

′

可以经由连接至第三漏极选择线dsl3

′

的漏极选择晶体管dst

′

分别连接至位线bl

′

。第一存储器单元串ms1

′

中的一个、第二存储器单元串ms2

′

中的一个、以及第三存储器单元串ms3

′

中的一个可以连接至单条位线bl

′

。

101.第一存储器单元串ms1

′

、第二存储器单元串ms2

′

和第三存储器单元串ms3

′

可以根据施加到源极选择线ssl

′

的栅极信号而连接至公共源极层csl

′

。

102.图7是示意性地例示根据本公开的实施方式的半导体存储器装置的立体图。

103.参照图7,半导体存储器装置可以包括外围电路结构ps

′

、公共源极层csl

′

、栅极层叠结构gst1

′

和gst2

′

以及位线bl

′

,其中栅极层叠结构gst1

′

和gst2

′

中的每个可以构成存储块。

104.外围电路结构ps

′

可以包括用于控制存储器单元的操作的外围电路,并且可以与栅极层叠结构gst1

′

和gst2

′

交叠,并且公共源极层csl

′

插置于其间。

105.公共源极层csl

′

可以在相同高度彼此间隔开,并且可以与位线bl

′

交叠,并且栅极层叠结构gst1

′

和gst2

′

插置于其间。

106.栅极层叠结构gst1

′

和gst2

′

可以包括彼此面对的第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

。

107.第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

中的每一个可以包括:包括上选择线的上选择组、包括下选择线的下选择组、以及设置在上选择组和下选择组之间的字线wl

′

。在实施方式中,上选择线可以配置有漏极选择线dsl1

′

、dsl2

′

和dsl3

′

,而下选择线可以配置有源极选择线ssl

′

[a]和ssl

′

[b]。

[0108]

漏极选择线dsl1

′

、dsl2

′

和dsl3

′

,字线wl

′

以及源极选择线ssl

′

[a]和ssl

′

[b]中的每条可以在第一方向d1和第二方向d2上延伸,其中第一方向d1可以被定义为xyz坐标系中的x轴的方向,而第二方向d2可以被定义为xyz坐标系中的y轴的方向。

[0109]

漏极选择线dsl1

′

、dsl2

′

和dsl3

′

可以在相同高度彼此隔离,并且可以在位线bl

′

的延伸方向上彼此间隔开。在实施方式中,漏极选择线dsl1

′

、dsl2

′

和dsl3

′

可以在第一方向d1上彼此间隔开。漏极选择线dsl1

′

、dsl2

′

和dsl3

′

可以设置在位线bl

′

与包括字线wl

′

的层叠结构之间。

[0110]

字线wl

′

可以在第三方向d3上彼此间隔开,其中第三方向d3可以被定义为xyz坐标系中的z轴的方向。字线wl

′

中的每条可以延伸以与彼此隔离的漏极选择线dsl1

′

、dsl2

′

、和dsl3

′

交叠。

[0111]

源极选择线ssl

′

[a]和ssl

′

[b]可以设置在公共源极层csl

′

与包括字线wl

′

的层叠结构之间的至少一层中。在实施方式中,源极选择线ssl

′

[a]和ssl

′

[b]可以包括第一高度的源极选择线ssl

′

[a]和第二高度的源极选择线ssl

′

[b]。第二高度的源极选择线ssl

′

[b]可以与第一高度的源极选择线ssl

′

[a]间隔开。

[0112]

外围电路结构ps

′

可以与包括漏极选择线dsl1

′

、dsl2

′

和dsl3

′

的上选择组交叠。除了包括源极选择线ssl

′

[a]和ssl

′

[b]的下选择组之外,公共源极层csl

′

可以设置在外围电路结构ps

′

和包括漏极选择线dsl1

′

、dsl2

′

和dsl3

′

的上选择组之间。

[0113]

位线bl

′

可以延伸以与第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

交叠。公共源极层csl

′

可以分别与第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

交叠。

[0114]

图8a是例示图7所示的半导体存储器装置的位线的布局的平面图。

[0115]

参照图8a,位线bl

′

可以彼此平行地延伸,并且可以彼此间隔开。在实施方式中,位线bl

′

可以在第一方向d1上延伸,并且可以在第二方向d2上彼此间隔开。

[0116]

位线bl

′

可以连接至在第三方向d3上延伸的沟道结构ch

′

,并且可以经由位线接触结构ct

′

连接至沟道结构ch

′

。

[0117]

沟道结构ch

′

可以贯穿第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

,并且沟道结构ch

′

可以被划分为由彼此间隔开的漏极选择线dsl1

′

、dsl2

′

和dsl3

′

控制的组。在实施方式中,沟道结构ch

′

可以包括配置有第一沟道结构ch1

′

的第一组、配置有第二沟道结构ch2

′

的第二组、和配置有第三沟道结构ch3

′

的第三组。第一沟道结构ch1

′

的侧壁可以由第一栅极层叠结构gst1

′

的第一漏极选择线dsl1

′

围绕,并且可以由第一漏极选择线dsl1

′

控制。第二沟道结构ch2

′

的侧壁可以由第一栅极层叠结构gst1

′

的第二漏极选择线dsl2

′

围绕,并且可以由第二漏极选择线dsl2

′

控制。第三沟道结构ch3

′

的侧壁可以由第二栅极层叠

结构gst2

′

的第三漏极选择线dsl3

′

围绕,并且可以由第三漏极选择线dsl3

′

控制。

[0118]

第一沟道结构ch1

′

中的一个、第二沟道结构ch2

′

中的一个和第三沟道结构ch3

′

中的一个可以并联连接至单条位线bl

′

。

[0119]

第一栅极层叠结构gst1

′

的字线wl

′

和第一栅极层叠结构gst1

′

的源极选择线ssl

′

[a]和ssl

′

[b]中的每条可以延伸以围绕第一沟道结构ch1

′

的侧壁和第二沟道结构ch2

′

的侧壁。

[0120]

参照图8a,线ii-ii

′

与单条位线bl

′

交叠。与单条位线bl

′

交叠的沟道结构ch可以包括经由与线ii-ii

′

交叠的位线接触结构ct

′

连接至单条位线bl

′

的沟道结构,以及经由与线ii-ii

′

不交叠的位线接触结构ct连接至另一位线bl

′

的沟道结构。

[0121]

图8b是沿着图8a所示的线ii-ii

′

截取的半导体存储器装置的截面图。

[0122]

参照图8b,第一栅极层叠结构gst1

′

的字线wl

′

可以通过第一沟槽t1

′

与第二栅极层叠结构gst2

′

的字线wl

′

间隔开,其中第一沟槽t1

′

可以在包括第一栅极层叠结构gst1

′

的源极选择线ssl

′

[a]和ssl

′

[b]的第一下选择组与包括第二栅极层叠结构gst2

′

的源极选择线ssl

′

[a]和ssl

′

[b]的第二下选择组之间延伸。

[0123]

第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

中的每一个还可以包括在第三方向d3上彼此间隔开地层叠的层间绝缘层211。针对字线wl

′

和源极选择线ssl

′

[a]和ssl

′

[b]提供的导电层以及层间绝缘层211可以在第三方向d3上交替设置。

[0124]

公共源极层csl

′

可以设置在第一栅极层叠结构gst1

′

和第二栅极层叠结构gst2

′

与外围电路结构ps

′

之间。第一沟槽t1

′

可以在公共源极层csl

′

之间延伸并且可以填充有栅极隔离层251填充第一沟槽t1

′

。栅极隔离层251和公共源极层csl

′

可以面对外围电路结构ps

′

,并且第一绝缘结构261插置于其间。

[0125]

包括漏极选择线dsl1

′

、dsl2

′

和dsl3

′

的上选择组可以与公共源极层csl

′

交叠,并且包括源极选择线ssl

′

[a]和ssl

′

[b]的下选择组以及字线wl

′

插置于其间。漏极选择线dsl1

′

、dsl2

′

和dsl3

′

可以通过第二沟槽t2

′

彼此隔离,其中可以用第一上绝缘层295填充第二沟槽t2

′

。第一上绝缘层295可以在位线bl

′

与包括漏极选择线dsl1

′

、dsl2

′

和dsl3

′

的上选择组之间延伸。位线bl

′

可以与漏极选择线dsl1

′

、dsl2

′

和dsl3

′

间隔开,并且第二上绝缘层297以及第一上绝缘层295插置于其间。

[0126]

位线bl

′

可以包括金属层299b和设置在金属层299b与第二上绝缘层297之间的导电金属屏障层299a,并且可以经由位线接触结构ct

′

连接至沟道结构ch

′

。

[0127]

位线接触结构ct

′

可以贯穿第一上绝缘层295和第二上绝缘层297,以将一些沟道结构ch

′

电连接至位线bl

′

。

[0128]

参照第一栅极层叠结构gst1

′

,每个沟道结构ch

′

可以包括沟道层231和芯绝缘层233,其中芯绝缘层233的侧壁可以由第一栅极层叠结构gst1

′

和第一上绝缘层295围绕。沟道层231可以包括半导体材料,可以设置在芯绝缘层233和第一栅极层叠结构gst1

′

之间,可以在芯绝缘层233和第一上绝缘层295之间延伸,并且可以在公共源极层csl

′

和第一栅极层叠结构gst1

′

之间延伸。

[0129]

参照与第一栅极层叠结构gst1

′

相对应的公共源极层csl

′

,公共源极层csl

′

可以包括平行于字线wl

′

延伸的水平图案hp和从水平图案hp在第三方向d3上朝向芯绝缘层233延伸的垂直图案vp。沟道层231可以延伸以围绕垂直图案vp的侧壁,并且在水平图案hp和第

一栅极层叠结构gst1

′

之间延伸。公共源极层csl

′

可以形成为包括n型杂质和p型杂质中的至少一种的掺杂半导体层。

[0130]

每个沟道结构ch

′

可以包括第一柱部pa

′

和从第一柱部pa

′

在第三方向d3上延伸的第二柱部pb

′

。可以用芯绝缘层233和公共源极层csl

′

的垂直图案vp填充第一柱部pa

′

的中央区域,并且芯绝缘层233可以延伸到第二柱部pb

′

的中央区域。第一柱部pa

′

的外壁和第二柱部pb

′

的外壁可以配置有沟道层231。

[0131]

参照第一栅极层叠结构gst1

′

,第一柱部pa

′

的侧壁可以不仅由层间绝缘层211和字线wl

′

围绕,而且由对应于第一柱部pa

′

的第一高度的源极选择线ssl

′

[a]和对应于第一柱部pa

′

的第二高度的源极选择线ssl

′

[b]围绕。第二柱部pb

′

的侧壁可以由对应于第二柱部pb

′

的漏极选择线dsl1

′

或dsl2

′

围绕,并且沟道结构ch

′

的第二柱部pb

′

可以延伸到第一上绝缘层295的内部。

[0132]

第一柱部pa

′

的侧壁可以由第一阻挡绝缘层221、数据储存层223和隧道绝缘层225围绕,其中第一阻挡绝缘层221、数据储存层223和隧道绝缘层225可以设置在第一柱部pb

′

与层间绝缘层221和字线wl

′

中的每个之间。第一阻挡绝缘层221、数据储存层223和隧道绝缘层225可以在第一高度的源极选择线ssl

′

[a]和第一柱部pa

′

之间延伸,可以在第二高度的源极选择线ssl

′

[b]和第一柱部pa

′

之间延伸,并且可以在第一栅极层叠结构gst1

′

和沟道层231之间延伸。

[0133]

数据储存层223可以设置在第一阻挡绝缘层221和第一柱部pa

′

之间。隧道绝缘层225可以设置在数据储存层223和第一柱部pa

′

之间,并且可以在第二柱部pb

′

和对应于第二柱部pb

′

的漏极选择线dsl1

′

或dsl2

′

之间延伸。

[0134]

每个沟道结构ch

′

可以具有锥状形状。随着沟道结构ch

′

变得越靠近公共源极层csl

′

和外围电路结构ps

′

,沟道结构ch

′

的宽度变得越宽。一些沟道结构ch

′

可以经由位线接触结构ct

′

连接至位线bl

′

。位线接触结构ct

′

可以贯穿第一上绝缘层295和第二上绝缘层297,并且可以延伸以与沟道结构ch

′

的沟道层231接触。

[0135]

公共源极层csl

′

可以通过第一绝缘结构261与外围电路结构ps

′

间隔开,其中第一绝缘结构261可以接合到外围电路结构ps

′

。

[0136]

外围电路结构ps

′

可以包括包含晶体管280a和280b的基板271,第二绝缘结构291和互连结构293。

[0137]

晶体管280a和280b可以设置在基板271的由隔离层273分隔开的有源区中,并且晶体管280a和280b中的每个可以包括栅极绝缘层281、栅电极283和结285,如参照图3b所述。晶体管280a和280b中的一些(例如,280b)可以构成用于控制位线bl

′

的预充电操作和放电操作的页缓冲器电路。

[0138]

第二绝缘结构291可以设置在第一绝缘结构261和基板271之间,可以包括两个或更多个绝缘层,并且可以接合到第一绝缘结构261。

[0139]

互连结构293可以掩埋在第二绝缘结构291中,可以包括多个导电图案,可以电连接至页缓冲器电路的晶体管280b,并且可以经由第一通孔接触结构v1和第二通孔接触结构v2连接至位线bl

′

。

[0140]

第一通孔接触结构v1可以贯穿栅极隔离层251,可以贯穿第一绝缘结构261和第二绝缘结构291以与互连结构293接触,并且可以在第三方向d3上延伸以贯穿第一上绝缘层

295。第二通孔接触结构v2可以与第一通孔接触结构v1接触,并且可以延伸以贯穿第二上绝缘层297。第一通孔接触结构v1可以包括导电金属屏障层296a和金属层296b,而第二通孔接触结构v2也可以包括导电金属屏障层298a和金属层298b。

[0141]

根据以上描述的实施方式,位线bl

′

可以经由第一通孔接触结构v1、第二通孔接触结构v2和互连结构293连接至页缓冲器电路的晶体管280b。

[0142]

图9是图8b中所示的区域b的放大截面图。

[0143]

参照图9,第一阻挡绝缘层221可以包括面向第三方向d3的端部eg1

′

,并且数据储存层223也可以包括面向第三方向d3的端部eg2

′

。

[0144]

漏极选择线(例如,dsl1

′

)可以与第一阻挡绝缘层221的端部eg1

′

和数据储存层223的端部eg2

′

交叠。

[0145]

漏极选择线dsl1

′

可以包括第一导电图案201和第二导电图案203。第一导电图案201可以在平面方向上延伸以与第二柱部pb

′

交叉。具体而言,第一导电图案201可以在第一方向d1和第二方向d2上延伸以平行于字线wl

′

。第二导电图案203可以设置在第一导电图案201和隧道绝缘层225之间,并且可以在漏极选择线dsl1

′

和第二柱部pb

′

之间的交叉部分处提供具有全环绕栅极(gaa)结构的漏极选择晶体管。

[0146]

第二导电图案203可以包括硅、金属硅化物和导电金属屏障物中的至少一种,其中金属硅化物可以包括硅化钨或硅化镍,并且导电金属屏障物可以包括钛和氮化钛。

[0147]

沟道结构ch

′

的第二柱部pb

′

可以包括由漏极选择线dsl1

′

围绕的第一部分p1

′

、从第一部分p1

′

在第三方向d3上延伸的第二部分p2

′

和从第二部分p2

′

在第三方向d3上延伸的第三部分p3

′

。第二部分p2

′

和第三部分p3

′

可以在第三方向d3上比漏极选择线dsl1

′

突出更远,并且可以由上绝缘层295覆盖。

[0148]

位线接触结构ct

′

可以贯穿第一绝缘层295,并且可以延伸以与第三部分p3

′

的沟道层231接触。位线接触结构ct

′

的导电金属屏障层298a可以设置在位线接触结构ct

′

的金属层298b与沟道层231之间,并且可以在位线接触结构ct

′

的金属层298b和第一上绝缘层295之间延伸。

[0149]

沟道结构ch

′

的芯绝缘层233可以从第一柱部pa

′

的中央区域延伸到第一部分p1

′

、第二部分p2

′

和第三部分p3

′

的中央区域。

[0150]

如参照图4所描述的,字线wl

′

可以包括导电金属屏障层243和金属层245。如参照图4所描述的,第二阻挡绝缘层241可以设置在字线wl

′

和第一阻挡绝缘层221之间。与字线wl

′

类似,图8b中示出的源极选择线ssl

′

[a]和ssl

′

[b]中的每条可以包括导电金属屏障层243和金属层245。第二阻挡绝缘层241可以设置在第一阻挡绝缘层221与图8b中所示的源极选择线ssl

′

[a]和ssl

′

[b]中的每条之间,并且可以在层间绝缘层211与图8b中所示的源极选择线ssl

′

[a]和ssl

′

[b]中的每条之间延伸。

[0151]

隧道绝缘层225、数据储存层223和第一阻挡绝缘层221可以由参照图5b描述的材料制成。第二阻挡绝缘层241可以包括介电常数比第一阻挡绝缘层221的介电常数高的绝缘材料。

[0152]

图10a、图10b、图10c、图10d、图10e、图11、图12、图13、图14a、图14b、图15a、图15b、图16a、图16b、图17a、图17b和图17c是例示根据本公开的实施方式的半导体存储器装置的制造方法的图。

[0153]

图10a至图10e是例示在接合工艺之前执行的工艺的截面图。

[0154]

参照图10a,可以在第一基板301上形成第一导电层305。在形成第一导电层305之前,可以在第一基板301上形成相对于第一基板301具有蚀刻选择性的第一保护层303。在实施方式中,第一基板301可以包括硅,并且第一保护层303可以包括氮化物。

[0155]

第一导电层305可以包括在执行随后的去除第一保护层303的蚀刻工艺时相对于蚀刻材料具有抗蚀刻性的导电材料。在实施方式中,第一导电层305可以包括硅。

[0156]

随后,第一材料层311和第二材料层313可以交替地层叠在第一导电层303上。在实施方式中,第一材料层311可以是诸如氧化硅之类的用于层间绝缘层的绝缘材料,并且第二材料层313可以是诸如氮化硅之类的相对于第一材料311具有蚀刻选择性的牺牲材料。在另一实施方式中,第一材料层311可以是用于层间绝缘层的绝缘材料,并且第二材料层313可以是用于字线和下选择线的导电材料。在下文中,为了便于描述,将主要基于第一材料层311由用于层间绝缘层的绝缘材料制成并且第二材料层313由牺牲材料制成的实施方式来描述制造工艺。然而,本公开的实施方式不限于此。

[0157]

随后,可以形成孔320以贯穿第一材料层311和第二材料层313。孔320可以贯穿第一导电层305和第一保护层303,并且延伸到第一基板301的内部。可以通过从第一材料层311和第二材料层313当中距离第一基板301最远的第一材料层311朝向第一基板301执行蚀刻工艺来形成孔320。因此,孔320可以具有锥状形状。随着孔320变得距第一基板301越远,孔320的宽度变得越宽。

[0158]

随后,第一阻挡绝缘层321、数据储存层323和隧道绝缘层325可以顺序地层叠在孔320的表面上。数据储存层323可以由使能数据的存储并且相对于第一阻挡绝缘层321和隧道绝缘层325具有蚀刻选择性的材料制成。在实施方式中,第一阻挡绝缘层321可以包括氧化物,数据储存层323可以包括氮化硅,并且隧道绝缘层325可以包括氧化硅。

[0159]

随后,可以用沟道结构330和掺杂半导体图案335来填充孔320的中央区域,其中沟道结构330可以包括沟道层331和芯绝缘层333。沟道层331可以沿着隧道绝缘层325的表面延伸,并且可以包括半导体材料。在实施方式中,沟道层可以包括硅。芯绝缘层333和掺杂半导体图案335可以填充通过沟道层331打开的孔320的中央区域。在用芯绝缘层333填充孔320的一部分之后,掺杂半导体图案335可以设置在芯绝缘层333上。填充孔320的中央区域的沟道结构330可以具有锥状形状。随着孔320变得距离第一基板301越远,沟道结构330的宽度变得越宽。

[0160]

参照图10b,可以形成第一沟槽340以贯穿图3a所示的第一材料层311和第二材料层313,其中可以通过蚀刻第一材料层311和第二材料层313来限定第一沟槽340。在蚀刻第一材料层311和第二材料层313时,第一导电层305可以用作蚀刻停止层。

[0161]

当图10a中所示的第二材料层313是牺牲材料时,可以通过第一沟槽340用导电图案347替换图10a所示的第二材料层313。用导电图案347替换图10a所示的第二材料层313的工艺包括通过经由第一沟槽340去除图10a中所示的第二材料层313来打开第一材料层311之间的栅极区域的工艺,以及用导电图案347填充栅极区域的工艺。

[0162]

在用导电图案347填充栅极区域之前,可以沿着每个栅极区域的表面形成第二阻挡绝缘层341,其中,每个导电图案347可以填充由第二阻挡绝缘层341打开的栅极区域的一部分。

[0163]

导电图案347可以由各种导电材料形成。在实施方式中,每个导电图案347可以包括导电金属屏障层343和金属层345。每个导电图案347可以在第一材料层311之间围绕沟道结构330的侧壁。

[0164]

参照图10c,可以用可以是绝缘材料的栅极隔离层351来填充图10b中所示的第一沟槽340。

[0165]

随后,可以形成第二沟槽353以贯穿图10b中所示的导电图案347中的至少一个。在实施方式中,第二沟槽353可以贯穿两个导电图案。图10b中所示的导电图案347中的一些可以通过第二沟槽353隔离成漏极选择线347d。未被第二沟槽353贯穿的其它导电图案可以定义为字线347w。

[0166]

参照图10d,可以用可以由绝缘材料形成的漏极隔离层357填充图10c中所示的第二沟槽353。

[0167]

随后,第一绝缘层361可以形成为延伸以与沟道结构330、栅极隔离层351、漏极隔离层357和层间绝缘层311交叠。连续地,可以形成位线接触结构363以贯穿第一绝缘层361。位线接触结构363可以电连接至沟道结构330和掺杂半导体图案335。

[0168]

随后,位线365可以形成为与位线接触结构363接触。位线365可以延伸到第一绝缘层361上。在实施方式中,位线365可以在第一方向d1上延伸。

[0169]

参照图10e,接合结构可以形成在位线365上,并且可以包括第一绝缘结构367和掩埋在第一绝缘结构367中的第一导电接合焊盘371。

[0170]

在形成第一导电接合焊盘371之前,可以形成第一互连结构369以包括掩埋在第一绝缘结构367中的多个导电图案。第一互连结构369的一些导电图案可以电连接至位线365。第一导电接合焊盘371可以与第一互连结构369接触,并且可以经由第一互连结构369电连接至位线365。

[0171]

图11是例示形成外围电路结构的工艺的截面图。

[0172]

参照图11,形成外围电路结构390的工艺可以包括:在第二基板381中形成分隔第二基板381的有源区的隔离层383的工艺;在由源极隔离层383分隔开的有源区中形成晶体管385a和385b的工艺;形成连接至晶体管385a和385b的第二互连结构389的工艺;以及形成连接至第二互连结构389的第二导电接合焊盘391的工艺。

[0173]

晶体管385a和385b可以包括与参照图3a描述的晶体管相同的组件。晶体管385a和385b当中的一些(例如,385b)可以构成页缓冲器电路。

[0174]

包括晶体管385a和385b的第二基板381可以被第二绝缘结构387覆盖。第二互连结构389和第二导电接合焊盘391可以掩埋在第二绝缘结构387中。

[0175]

第二互连结构389可以包括多个导电图案,其中一些导电图案可以连接至页缓冲器电路的晶体管385b。第二导电接合焊盘391可以经由第二互连结构389连接至页缓冲器电路的晶体管385b。

[0176]

图12是例示接合工艺的截面图。

[0177]

参照图12,外围电路结构390可以对齐成面对接合结构的第一绝缘结构367和第一导电接合焊盘371。

[0178]

随后,外围电路结构390的第二绝缘结构387和第二导电接合焊盘391可以接合到接合结构的第一绝缘结构367和第一导电接合焊盘371。

[0179]

在执行接合工艺的工艺之后,工艺温度可以限制在450℃或更低,使得可以减少由于高温在第一导电接合焊盘371和第二导电接合焊盘391中出现缺陷。

[0180]

图13是例示在接合工艺之后执行的一些工艺的截面图。

[0181]

参照图13,可以去除图12中所示的第一基板301,并且可以由图12所示的第一保护层303保护第一导电层305。随后,可以选择性地去除图12中所示的第一保护层303,使得可以暴露出第一导电层305和第一阻挡绝缘层321。

[0182]

图14a和图14b是图13中所示的区域c的放大工艺截面图。

[0183]

参照图14a,可以通过选择性地去除第一阻挡绝缘层321的一部分而在第一导电层305和数据储存层323之间形成初步凹陷区域403。保留的第一阻挡绝缘层321可以设置为比导电金属屏障层343和金属层345更靠近第一导电层305。

[0184]

参照图14b,通过选择性地去除数据储存层323,可以在第一导电层305和隧道绝缘层325之间限定凹陷区域405。保留的第一阻挡绝缘层321和保留的数据储存层323可以设置为比导电金属屏障层343和金属层345更靠近第一导电层305。

[0185]

图15a和图15b是例示在形成凹陷区域之后继续的后续工艺的截面图。

[0186]

参照图15a,可以沿着第一导电层305和隧道绝缘层325的表面形成第二导电层411,并且第二导电层411可以填充图14b所示的凹陷区域405。

[0187]

第二导电层411可以包括硅、金属硅化物和导电金属屏障物中的至少一种,其中金属硅化物可以包括硅化钨或硅化镍,并且导电金属屏障物可以包括钛和氮化钛。

[0188]

参照图15b,可以去除第二导电层411的一部分,使得暴露出隧道绝缘层325和第一导电层305。第二导电层411可以保留为在图14b中所示的凹陷区域405中围绕隧道绝缘层325的侧壁。

[0189]

图16a和图16b是例示隔离上选择线的工艺的工艺截面图。

[0190]

参照图16a,可以通过比第一导电层305在第三方向d3上突出更远的沟道结构330来限定不平坦结构。可以沿着不平坦结构的表面形成第二保护层421,并且可以减小台阶覆盖的条件下沉积第二保护层421。在实施方式中,可以通过台阶覆盖比原子层沉积(ald)的台阶覆盖更减小的物理气相沉积(pvd)或化学气相沉积(cvd)来沉积第二保护层421。第二保护层421可以包括相对于第一导电层305具有蚀刻选择性的材料。在实施方式中,第二保护层421可以包括可以通过等离子体增强化学气相沉积(pe-cvd)而沉积的非晶碳层(acl)。

[0191]

在减小台阶覆盖的条件下沉积的第二保护层421可以在不平坦结构的凸部上比在不平坦结构的凹部上形成得相对厚,可以具有悬垂(overhang)结构,并且可以具有彼此面对的侧壁,并且每个第一开口423插置于彼此面对的侧壁之间。随着悬垂结构距离第一导电层305变得越远,每个第一开口423的宽度可以通过第二保护层421而变窄。

[0192]

随后,通过使用光刻工艺,可以在第二保护层421上形成掩模图案431。掩模图案431可以是可以包括第二开口433的光致抗蚀剂图案。

[0193]

第二开口433可以分别与栅极隔离层351和漏极隔离层357交叠。可以通过第二开口433使与栅极隔离层351和漏极隔离层357交叠的第一开口423暴露。

[0194]

位于沟道结构330的外围的第一导电层305可以被具有悬垂结构的第二保护层421阻挡。

[0195]

参照图16b,可以通过经由图16a中所示的第二开口433所暴露出的第一开口423蚀

刻第一导电层305,来形成贯穿第一导电层305的第三沟槽441。可以通过第三沟槽441来限定上选择线。在实施方式中,上选择线可以是源极选择线443。每条源极选择线443可以包括由第三沟槽441分隔开的第一导电层305和在第一导电层305和隧道绝缘层325之间的第二导电层411。

[0196]

根据本公开的实施方式,第二导电层411保留成在隧道绝缘层325与第一导电层305之间围绕沟道结构330,使得在隧道绝缘层325和第三沟槽441之间的源极选择线443的保留宽度可以变宽。因此,在本公开的实施方式中,可以稳定地形成具有全环绕栅极(gaa)的选择晶体管。

[0197]

图17a至图17c例示了在形成源极选择线443之后继续的后续工艺的实施方式。

[0198]

参照图17a,可以形成上绝缘层451以填充第三沟槽441,并覆盖源极选择线443、沟道结构330和隧道绝缘层325,其中上绝缘层451可以包括氧化物。

[0199]

参照图17b,可以通过诸如回蚀工艺之类的蚀刻工艺来蚀刻上绝缘层451的一部分和隧道绝缘层325的一部分,使得可以暴露出沟道结构330的沟道层331。

[0200]

上绝缘层451可以保留在第三沟槽441中,并且可以保留成覆盖源极选择线433。

[0201]

参照图17c,可以在沟道层331的暴露区域上形成公共源极层的掺杂半导体层455。

[0202]

图18a、图18b、图18c、图18d、图18e、图18f、图18g、图18h、图18i、图18j、图18k、图18l、图18m和图18n是例示根据本公开的实施方式的半导体存储器装置的制造方法的图。

[0203]

参照图18a,如参照图10a所描述的,可以在基板501上形成第一保护层503和第一导电层505。随后,如参照图10a所描述的,第一材料层511和第二材料层513可以交替层叠在第一导电层505上,以形成层叠结构510。

[0204]

随后,可以形成孔520,该孔520贯穿第一材料层511、第二材料层513、第一导电层505和第一保护层503,并且延伸到第一基板501的内部。

[0205]

参照图18b,第一阻挡绝缘层521、数据储存层523和隧道绝缘层525可以顺序地层叠在图18a中所示的孔520的表面上,其中第一阻挡绝缘层521、数据储存层523和隧道绝缘层525中的每个不仅可以沿着孔520的侧壁和底表面延伸,而且可以沿着层叠结构510的顶表面延伸。

[0206]

数据储存层523可以由使能数据的存储并且相对于第一阻挡绝缘层521和隧道绝缘层525具有蚀刻选择性的材料制成,第一阻挡绝缘层521和隧道绝缘层525可以由参照图10a描述的材料制成。

[0207]

随后,可以用初步沟道结构530p填充图18a中所示的孔520的中央区域,该初步沟道结构530p可以包括沟道层531和芯绝缘层533。沟道层531可以形成为半导体层,并且可以沿着隧道绝缘层525的表面延伸。在实施方式中,沟道层531可以包括硅。芯绝缘层533可以设置在沟道层531上,并且可以填充如图18a中所示的孔520的中央区域。芯绝缘层533可以形成为使如图18a中所示的孔520的上端打开的高度。

[0208]

在形成芯绝缘层533之后,可以用掺杂半导体层539填充由芯绝缘层533打开的孔的上端。掺杂半导体层539可以包括填充孔的上端的垂直部539a和从垂直部539a平行于层叠结构510的顶表面延伸的水平部539b。

[0209]

参照图18c,可以形成第一沟槽540,其中第一沟槽540可以贯穿图18b中所示的掺杂半导体层539、沟道层531、隧道绝缘层525、数据储存层523、第一阻挡绝缘层521、第一材

料层511和第二材料层513。因此,可以限定初步栅极层叠结构510p和沟道结构530。

[0210]

沟道结构530可以包括贯穿初步栅极层叠结构510p的柱部pp,其中沟道结构530的柱部pp可以包括贯穿初始栅极层叠结构510p的芯绝缘层533和沟道层531。

[0211]

图18b中所示的掺杂半导体层539可以通过第一沟槽540被隔离成公共源极层539s。

[0212]

参照图18d,如参照图10b所描述的,可以用导电图案547替换第二材料层513,其中导电图案547中与公共源极层539s相邻的至少一个导电图案可以用作源极选择线,而其它的导电图案可以用作字线。如参照图10b所描述的,在形成导电图案547之前,可以形成第二阻挡绝缘层541。

[0213]

参照图18e,可以用栅极隔离层551填充图18d中所示的第一沟槽540。栅极隔离层551可以由绝缘材料形成。

[0214]

随后,可以形成接合结构,该接合结构可以覆盖栅极隔离层551和公共源极层539s。接合结构可以配置有第一绝缘结构561。

[0215]

参照图18f,可以提供外围电路结构590,外围电路结构590可以包括晶体管585a和585b、连接至晶体管585a和585b的互连结构589、以及第二绝缘结构587。晶体管585a和585b可以形成在第二基板581的由隔离层583分隔开的有源区中。晶体管585a和585b以及互连结构589可以掩埋在第二绝缘结构587中,第二绝缘结构587可以包括两个或更多个绝缘层。

[0216]

随后,外围电路结构590可以被对齐为使得外围电路结构590面对第一绝缘结构561。随后,外围电路结构590的第二绝缘结构587可以接合至第一绝缘结构561。

[0217]

参照图18g,可以顺序地去除图18f中所示的第一基板501和第一保护层503,使得可以暴露出第一导电层505和第一阻挡绝缘层521。

[0218]

参照图18h,可以通过使用参照图14a和图14b描述的工艺来去除第一阻挡绝缘层521的一部分和数据储存层523的一部分。因此,可以在第一导电层505和隧道绝缘层525之间限定凹陷区域605。

[0219]

参照图18i,可以通过使用参照图15a和图15b描述的工艺将填充图18h中所示的凹陷区域605的第二导电层611形成为在第一导电层505和隧道绝缘层525之间围绕隧道绝缘层625的侧壁。

[0220]

参照图18j,可以通过使用参照图16a和图16b所描述的隔离上选择线的工艺,来形成贯穿第一导电层505的第二沟槽641。可以由第二沟槽641来限定上选择线。在实施方式中,上选择线可以是漏极选择线643。每条漏极选择线643可以包括由第二沟槽641分隔开的第一导电层505和在第一导电层505和隧道绝缘层525之间的第二导电层611。

[0221]

根据本公开的实施方式,第二导电层611保留成在隧道绝缘层525和第一导电层505之间围绕沟道结构530,使得可以稳定地形成具有全环绕栅极(gaa)结构的选择晶体管。

[0222]

参照图18k,第一上绝缘层651可以形成为填充第二沟槽641,并且可以形成为覆盖漏极选择线643、沟道结构530和隧道绝缘层525。第一上绝缘层651可以包括氧化物。可以通过诸如化学机械抛光(cmp)之类的工艺对第一上绝缘层651的表面进行平坦化。

[0223]

参照图18l,第一接触孔660可以形成为贯穿第一上绝缘层651的与栅极隔离层551交叠的部分、栅极隔离层551、第一绝缘结构561和第二绝缘结构587。第一接触孔660可以形成为暴露出互连结构589的导电图案,并且可以暴露出互连结构589的连接至页缓冲器电路

的晶体管(例如,585b)的导电图案。

[0224]

随后,可以形成第一通孔接触结构665,第一通孔接触结构665可以填充第一接触孔660,并且可以包括沿着第一接触孔660的表面延伸的导电金属屏障层661和填充由导电金属屏障层661打开的第一接触孔660的中央区域的金属层663。

[0225]

参照图18m,第二上绝缘层667可以形成在第一上绝缘层651上,并且可以延伸以覆盖第一通孔接触结构665。

[0226]

随后,可以形成接触孔670a和670b,接触孔670a和670b可以贯穿第一上绝缘层651和第二上绝缘层667中的至少一个,并且可以包括第二接触孔670a和第三接触孔670b。

[0227]

第二接触孔670a可以贯穿第二上绝缘层667,以暴露出第一通孔接触结构665。除了第一上绝缘层651和第二上绝缘层667之外,第三接触孔670b还可以贯穿隧道绝缘层525,以暴露出沟道层531。

[0228]

参照图18n,可以通过用导电材料填充图18m中所示的第二接触孔670a和第三接触孔670b中的每一个来形成第二通孔接触结构675a和位线接触结构675b。在实施方式中,形成第二通孔接触结构675a和位线接触结构675b的工艺可以包括:沿着第二接触孔670a和第三接触孔670b中的每一个的表面形成导电金属屏障层671的工艺;以及用金属层673填充第二接触孔670a和第三接触孔670b中的每一个的由导电金属屏障层617打开的中央区域的工艺。

[0229]

第二通孔接触结构675a可以填充图18m中所示的第二接触孔670a,并且与第一通孔接触结构665接触。位线接触结构675b可以填充图18m中所示的第三接触孔670b,并且可以与沟道结构530的沟道层531接触。

[0230]

随后,可以执行如参照图8b所描述的用于形成位线的后续工艺。

[0231]

图19是例示根据本公开的实施方式的存储器系统1100的配置的框图。

[0232]

参照图19,存储器系统1100可以包括存储器装置1120和存储器控制器1110。

[0233]

存储器装置1120可以包括沟道结构、阻挡绝缘层和隧道绝缘层。沟道结构可以包括第一柱部和从第一柱部延伸的第二柱部。阻挡绝缘层可以围绕第一柱部的侧壁,数据储存层在阻挡绝缘层和第一柱部之间,选择线与面向第二柱部的延伸方向的数据储存层的端部和阻挡绝缘层的端部交叠,选择线围绕第二柱部的侧壁。隧道绝缘层可以设置在第一柱部和数据储存层之间,隧道绝缘层在选择线和第二柱部之间延伸。

[0234]

存储器装置1120可以是配置有多个闪存芯片的多芯片封装件。

[0235]

存储器控制器1110可以控制存储器装置1120,并且可以包括静态随机存取存储器(sram)1111、中央处理单元(cpu)1112、主机接口1113、纠错块1114和存储器接口1115。sram 1111可以用作cpu 1112的操作存储器,cpu 1112可以执行用于存储器控制器1110的数据交换的整体控制操作,并且主机接口1113可以包括用于与存储器系统1100连接的主机的数据交换协议。纠错块1114可以检测并纠正从存储器装置1120读取的数据中所包含的错误。存储接口1115可以与存储器装置1120接口连接。存储器控制器1110可以还包括用于存储与主机接口连接的代码数据等的只读存储器(rom)。

[0236]

图20是例示根据本公开的实施方式的计算系统1200的配置的框图。

[0237]

参照图20,计算系统1200可以包括电连接至系统总线1260的cpu 1220、随机存取存储器(ram)1230、用户接口1240、调制解调器1250和存储器系统1210。计算系统1200可以

是移动装置。

[0238]

存储器系统1210可以配置有存储器装置1212和存储器控制器1211。存储器装置1212可以包括沟道结构、阻挡绝缘层和隧道绝缘层。沟道结构可以包括第一柱部和从第一柱部延伸的第二柱部。阻挡绝缘层可以围绕第一柱部的侧壁,数据储存层在阻挡绝缘层和第一柱部之间,选择线与面向第二柱部的延伸方向的数据储存层的端部和阻挡绝缘层的端部交叠,选择线围绕第二柱部的侧壁。隧道绝缘层可以设置在第一柱部和数据储存层之间,隧道绝缘层在选择线和第二柱部之间延伸。

[0239]

在实施方式中,本公开可以提供具有晶圆接合结构的半导体装置,其包括选择线、阻挡绝缘层、数据储存层和隧道绝缘层,其中选择线包括第一导电图案和第二导电图案,其中第一导电图案围绕隧道绝缘层,并且其中第二导电图案与阻挡绝缘层的端部和数据储存层的端部交叠,第二导电图案插置于第一导电图案和隧道绝缘层之间。

[0240]

根据本公开,可以形成具有全环绕栅极(gaa)结构的选择线。因此,可以改善半导体存储器装置的操作特性。

[0241]

相关申请的交叉引用

[0242]

本技术要求于2020年10月16日在韩国知识产权局提交的韩国专利申请no.10-2020-0134645的优先权,其全部公开内容通过引用合并于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1