带有功率转换器模块的半导体器件的制作方法

带有功率转换器模块的半导体器件

1.相关申请的交叉引用

2.本技术要求2020年7月24日提交的美国临时申请no.63/056,302的优先权,其全部内容以引用方式并入本文。

技术领域

3.本公开涉及半导体器件。更具体地,本公开涉及包括功率转换器模块的半导体器件。

背景技术:

4.在电气工程中,功率转换是将电能从一种形式转换为另一种形式的过程。功率转换器是可以转换电能的电器件。一些功率转换器将交流电(ac)转换为直流电(dc)。其它功率转换器,即dc-dc功率转换器,将dc源从一个电压电平转换为另一个电压电平。

5.降压(buck)转换器,也称为减压(step-down)转换器,是一种dc-dc转换器,其(在增加电流的同时)从输入端口(电源)到输出端口(耦接到负载)减少电压。升压(boost)转换器,也称为增压(step-up)转换器,是一种dc-dc功率转换器,其(在减少电流的同时)从输入端口(电源)到输出端口(耦接到负载)增加电压。降压转换器和升压转换器都是开关模式电源的形式。

6.扁平无引线封装件(包括四方扁平无引线(qfn))可安装到印刷电路板(pcb)上以电连接集成电路。扁平无引线是一种表面安装技术,是将集成电路(ic)芯片连接到没有通孔的pcb表面的若干种封装技术之一。扁平无引线包括由平面铜引线框架基板制成的近芯片级塑料包封的封装件(模制)。封装件底部上的周边焊盘(焊区(land))提供与pcb的电连接。

技术实现要素:

7.第一示例涉及包括管芯的半导体器件,该管芯包括功率转换器模块。功率转换器模块包括输出端口和返回端口。半导体器件还包括连接组件,该连接组件包括被配置成耦接到印刷电路板(pcb)的电路部件的焊盘。连接组件还包括第一层,该第一层经图案化以包括第一迹线和第二迹线,该第一迹线耦接到功率转换器模块的输出端口和返回端口中的一个,并且该第二迹线耦接到功率转换器模块的输出端口和返回端口中的另一个。连接组件还包括第二层,该第二层经图案化以在第一迹线和连接组件的第三层之间提供第一导通孔并且在第一迹线和连接组件的第三层之间提供第二导通孔。连接组件的第三层经图案化以提供第一导通孔和焊盘的第一焊盘之间的第一导电路径的一部分以及第二导通孔和焊盘的第二焊盘之间的第二导电路径的一部分。

8.第二示例涉及一种用于形成半导体器件的方法。该方法包括形成具有层的连接组件,该层包括分布在整个连接组件中的电介质,其中这些层在连接组件的第一迹线和焊盘的第一焊盘之间形成第一电路径并且在连接组件的第二迹线和焊盘的第二焊盘之间形成

第二电路径。该方法还包括将管芯安装到连接组件。该管芯包括功率转换器模块,该功率转换器模块在管芯表面处包括输出端口和返回端口。输出端口被配置成耦接到连接组件的第一迹线。返回端口被配置成耦接到连接组件的第二迹线。连接组件的第一电路径和第二电路径中的至少一个在正交于管芯的表面的方向上延伸一段距离,该距离大于连接组件的单层的厚度。

附图说明

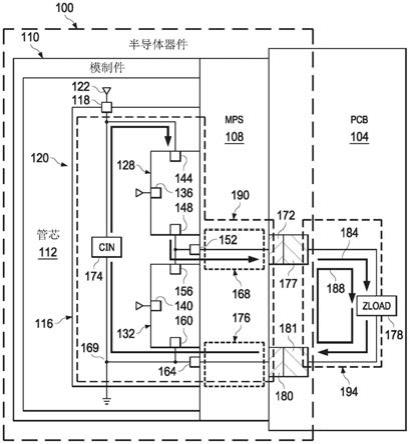

9.图1示出了在印刷电路板(pcb)上安装有功率转换器模块的半导体器件的示例的图。

10.图2示出了在pcb上安装有功率转换器模块的半导体器件的示例的另一图。

11.图3示出了多层封装基板的视图的示例。

12.图4示出了在pcb上安装有功率转换器模块的半导体器件的示例的又一图。

13.图5示出了用于具有功率转换器模块的管芯的多层封装基板的三维(3d)模型的视图。

14.图6示出了用于具有功率转换器模块的管芯的多层封装基板的第一电路径和第二电路径的3d模型的视图。

15.图7示出了用于形成多层封装基板的方法的第一阶段。

16.图8示出了用于形成多层封装基板的方法的第二阶段。

17.图9示出了用于形成多层封装基板的方法的第三阶段。

18.图10示出了用于形成多层封装基板的方法的第四阶段。

19.图11示出了用于形成多层封装基板的方法的第五阶段。

20.图12示出了用于形成多层封装基板的方法的第六阶段。

21.图13示出了用于形成多层封装基板的方法的第七阶段。

22.图14示出了用于形成多层封装基板的方法的第八阶段。

23.图15示出了用于形成多层封装基板的方法的第九阶段。

24.图16示出了形成半导体器件的第一封装阶段。

25.图17示出了形成半导体器件的第二封装阶段。

26.图18示出了形成半导体器件的第三封装阶段。

27.图19示出了用于形成半导体器件的示例方法的流程图。

具体实施方式

28.本公开涉及一种半导体器件,诸如包括具有功率转换器模块的管芯的ic封装件。功率转换器模块包括输出端口和返回端口。管芯粘附到连接组件,诸如多层封装基板,其在功率转换器模块的输出端口和多层封装基板的第一焊盘之间形成第一电路径。多层封装基板还在功率转换器模块的返回端口与多层封装基板的第二焊盘之间形成第二电路径。ic芯片可以安装在印刷电路板(pcb)上,该印刷电路板在功率转换器模块的输出端口和返回端口之间完成电路路径。由功率转换器模块的输出端口和返回端口之间的电路路径限制的区域限定回路区域。回路区域越大,功率转换器模块的寄生电感就越大。因此,制造多层封装基板以缩减回路区域,进而缩减功率转换器模块的寄生电感,从而缩减由功率转换器模块

的操作引起的电磁干扰(emi)。

29.为了缩减回路区域,选择第一电路径和第二电路径的几何形状。更具体地,在一个示例中,第一电路径和第二电路径线性地延伸穿过多层封装基板。在另一示例中,第一电路径线性地延伸穿过多层封装基板的两层到达多层封装基板的第三层,并且第二电路径线性地延伸穿过多层封装基板。在任一情况下,相对于限制为两层的四方扁平无引线(qfn)处理所采用的常规引线框架而言,回路区域减少。

30.图1示出了安装在印刷电路板(pcb)104上的半导体器件100的示例的图。半导体器件100可以被实现为例如集成电路(ic)封装件。半导体器件100包括多层封装基板108(图中标记为mps),诸如多层封装基板qfn。此外,半导体器件100的管芯112安装在多层封装基板108上并且包封在模制件110(例如塑料)中。在提供的示例中,多层封装基板108被用作一种类型的连接组件,用于将管芯112连接到pcb 104。在其它示例中,其它类型的连接组件可用于代替多层封装基板108。

31.管芯112包括用于实现电操作的模块。特别地,管芯112包括功率转换器模块116。作为一个示例,功率转换器模块116是ac-dc转换器。作为另一个示例,功率转换器模块116是dc-dc转换器,诸如降压转换器(减压转换器)或升压转换器(增压转换器)。对于所提供的示例,假设功率转换器模块116是dc-dc转换器。

32.为了说明的目的,包括电路图示120以示出电流通过半导体器件100和pcb 104的流动。电路图示120包括耦接到功率转换器模块116的输入端口118的电压源122。功率转换器模块116包括高侧晶体管128和低侧晶体管132。在一些示例中,高侧晶体管128和低侧晶体管132实现为场效应晶体管(fet),诸如n沟道金属氧化物半导体场效应晶体管(nmos)。在其它示例中,高侧晶体管128和低侧晶体管132被实现为双极结型晶体管(bjt),诸如npn晶体管。在其它示例中,可使用其它晶体管。此外,虽然半导体器件100示出了单个高侧晶体管128和单个低侧晶体管132,但在其它示例中,高侧晶体管128和低侧晶体管132二者均表示背对背连接或以阵列连接(例如,并联连接)的多个相应的高侧晶体管和低侧晶体管。

33.高侧晶体管128的控制节点136(例如,栅极或基极)由第一控制信号驱动,并且低侧晶体管132的控制节点140由第二控制信号驱动。第一控制信号与第二控制信号为互补信号。

34.高侧晶体管128的输入节点144(例如,漏极或集电极)耦接到输入端口118。高侧晶体管128的输出节点148(例如,源极或发射极)耦接到功率转换器模块116的输出端口152。此外,高侧晶体管128的输出节点148耦接到低侧晶体管132的输入节点156(例如,漏极或集电极)。低侧晶体管132的输出节点160耦接到功率转换器模块116的返回端口164。返回端口164还耦接到电中性节点(例如,地)169。输入电容174(标记为cin)表示返回端口164和输入端口118之间的寄生电容。

35.多层封装基板108被设计成在功率转换器模块116的输出端口152和多层封装基板108的第一焊盘172之间提供第一电路径168。多层封装基板108还被设计为在功率转换器模块116的返回端口164和多层封装基板108的第二焊盘180之间提供第二电路径176。

36.多层封装基板108的第一焊盘172耦接到负载178(标记为zload)的第一端子177,并且第二焊盘180耦接到负载178的第二端子181,从而完成功率转换器模块116的输出端口152和返回端口164之间的电路路径。负载178表示阻抗负载,诸如电感器、电容器和电阻器

的组合。此外,负载178在多层封装基板108的第一焊盘172和第二焊盘180之间提供导电路径。

37.在功率转换器模块116的操作中,第一控制信号和第二控制信号分别控制高侧晶体管128和低侧晶体管132的开关状态。此外,第一控制信号和第二控制信号被设定成使得如果高侧晶体管128打开(例如,以线性操作模式操作),则低侧晶体管132关闭(例如,以截止操作模式操作)。在这种状态下,高侧晶体管128打开并且低侧晶体管132关闭,电流沿着标记为第一电流回路184的路径流动。相反,当第一控制信号和第二控制信号导致高侧晶体管128关闭(例如,以截止模式操作)并且低侧晶体管132打开(例如,以线性模式操作),存储在负载178的能量(例如,从电感器)被释放,从而导致电流沿着标记为第二电流回路188的路径流动。

38.功率转换器模块116的操作引起电磁干扰(emi)。emi由在功率转换器模块116的操作期间发生的相对高的电流瞬变(di/dt)和/或相对高的电压瞬变(dv/dt)引起。更具体地,流过第一电流回路184和第二电流回路188的电流由于寄生电感而引起emi,诸如第一电路径168和第二电路径176的寄生电感。此外,emi与由对应电流回路限制的区域成比例。因此,第一电流回路184在比第二电流回路188更大的水平上引起emi。

39.由第一电流回路184限制的区域可以被划分为两个区域,即包括半导体器件100内的区域的第一区域190和包括pcb 104上的区域的第二区域194。因此,缩减第一区域190的大小减小由第一电流回路184引起的emi。

40.为了缩减第一区域190的大小,选择第一电路径168和第二电路径176的几何形状以提供缩小第一区域190大小的有效导电路径。如图所示,第一电路径168和/或第二电路径176越短,第一区域190越小,从而缩减第一电流回路184的寄生电感和emi。

41.第一电路径168和第二电路径176的几何形状利用由多层封装基板108提供的多个层。在一些示例中,多层封装基板108包括四(4)层,但是在其它示例中,多层封装基板108具有多于四(4)层。在一些示例中,多层封装基板108的第一层经图案化使得第一电路径168包括耦接到功率转换器模块116的输出端口152的第一迹线。此外,多层封装基板108的第一层经图案化使得第二电路径176包括耦接到功率转换器模块116的返回端口164的第二迹线。此外,多层封装基板108包括第二层,该第二层经图案化使得第一电路径168在第一迹线和多层封装基板108的第三层之间提供第一导通孔。此外,多层封装基板108的第二层经图案化使得第二电路径176在第一迹线和多层封装基板108的第三层之间提供第二导通孔。此外,多层封装基板108的第三层经图案化使得第一电路径168在第一导通孔和第一焊盘172之间提供第一导电路径(例如,迹线和/或导通孔)。另外,多层封装基板108的第三层经图案化使得第二电路径176在第二导通孔和第二焊盘180之间提供第二导电路径(例如,迹线和/或导通孔)。

42.存在可用于第一电路径168和第二电路径176的若干种不同的几何形状。在一些示例中,第一电路径168和第二电路径176平行,并且在正交于管芯112的表面的方向上基本线性延伸。在其它示例中,第一电路径包括在多层封装基板108的第三层处的迹线,其在平行于管芯112的表面的方向上延伸。

43.在任何此种示例中,多层封装基板108的多层(例如,四(4)层或更多层)实现了用于第一电路径168和第二电路径176的几何结构,这些几何结构在常规双层qfn引线框架中

是不可用的。因此,提供第一电路径168和第二电路径176以缩小第一区域190的大小,从而缩减由功率转换器模块116的操作引起的emi。

44.图2示出了安装在pcb 204上的半导体器件200的示例的图。半导体器件200可用于实现图1的半导体器件100,并且pcb 204可用于实现图1的pcb 104。半导体器件200可以实现为例如ic封装件。半导体器件200包括多层封装基板208,诸如多层封装基板qfn。此外,半导体器件100的管芯212安装在多层封装基板108上。

45.管芯212包括用于实现电操作的模块。特别地,管芯212包括功率转换器模块216。作为一个示例,功率转换器模块216是ac-dc转换器。作为另一示例,功率转换器模块216是dc-dc转换器,诸如降压转换器(减压转换器)或升压转换器(增压转换器)。对于所提供的示例,假设功率转换器模块216是dc-dc转换器。

46.功率转换器模块216包括输出端口220和返回端口224,可以分别对应图1的输出端口152和返回端口164。多层封装基板208的第一电路径228耦接到功率转换器模块216的输出端口220并在输出端口220和多层封装基板208的第一焊盘232之间提供导电路径。此外,多层封装基板208的第二电路径236耦接到功率转换器模块216的返回端口224并在返回端口224和多层封装基板208的第二焊盘240之间提供导电路径。

47.如所指出的,半导体器件200安装在pcb 204上。更具体地,半导体器件200安装成使得多层封装基板208的第一焊盘232耦接到pcb 204上的负载248的第一端子244,并且多层封装基板的第二焊盘240耦接到负载248的第二端子252。负载248表示从功率转换器模块216向其提供功率的电路部件。负载248包括与电容器258和电阻负载260之间的并联连接件串联连接的电感器256。负载248可用于实现图1的负载178。电感器256可以被称为负载电感器。此外,电阻负载260可以表示为电阻器。另外,在各种示例中,电阻负载260被实现为电容性电阻性和电感性部件或其一些子集的组合。此外,负载248的架构基于被选为功率转换器模块216的功率转换器的类型(例如,降压转换器、升压转换器、ac-dc转换器等)而改变。

48.多层封装基板208包括四层,第一层264、第二层268、第三层272和第四层276。第一电路径228包括形成在多层封装基板208的第一层264上的第一迹线282。第一电路径228还包括第一导通孔286,其在第一迹线282和多层封装基板208的第三层272上的第一电路径228的第二迹线290之间提供导电路径。第一电路径228还包括第二导通孔294,其在第二迹线290和多层封装基板208的第一焊盘232之间提供导电路径。此外,第二迹线290提供第一导通孔286和第一焊盘232之间的导电路径的一部分。

49.多层封装基板208的层具有的厚度基于半导体器件200的所选应用而变化。然而,多层封装基板208的两层的组合比多层封装基板208的单层厚。例如,第一层264和第二层268具有的组合厚度大于第三层272的厚度。

50.第二电路径236包括形成在多层封装基板208的第一层264上的第三迹线298。第二电路径236还包括第三导通孔302,其在第三迹线298和多层封装基板208的第三层272上的第二电路径236的第四迹线306之间提供导电路径。第二电路径236还包括第四导通孔310,其在第四迹线306和多层封装基板208的第二焊盘240之间提供导电路径。此外,第四迹线306提供第三导通孔302和第二焊盘240之间的导电路径的一部分。第一电路径228和第二电路径236分别引起第一寄生电感312和第二寄生电感314。

51.在操作中,电流回路(例如,对应于图1的第一电流回路184)限制第一区域320和第

二区域324。第一区域320对应于图1的第一区域190,使得第一区域320表示半导体器件200内的电流回路的部分。第一区域320和第二区域324组合的大小与功率转换器模块216的操作引起的emi量成比例。

52.为了缩小第一区域320的面积(这减小电流回路的面积),选择第一电路径228和第二电路径236的几何形状以形成从功率转换器模块216的输出端口220到多层封装基板208的第一焊盘232以及从多层封装基板208的第二焊盘240到功率转换器模块216的返回端口224的基本线性路径。更具体地,第一电路径228和第二电路径236在正交于(垂直)管芯212的表面328的方向上延伸,使得在一些示例中第一电路径228和第二电路径236平行。为第一电路径228和第二电路径236提供基本线性路径缩减第一寄生电感312和第二寄生电感314,这改善功率转换器模块216的整体性能。

53.在一些示例中,为了进一步缩小第一区域320,第一焊盘232和第二焊盘240被实现为岛状焊盘。岛状焊盘(或者称为独立焊盘)是指不与多层封装基板208的周边相交的焊盘。换言之,岛状焊盘与多层封装基板208的周边间隔开。

54.图3示出了图2的多层封装基板208的表面视图。图3所示的多层封装基板208的表面表示安装在图2的pcb 204上的表面。为了简化说明,图2和图3使用相同的附图标记来表示相同的结构。多层封装基板208包括被定位成岛状焊盘的第一焊盘232和第二焊盘240,与焊盘336相比,岛状焊盘不与多层封装基板208的周边332相交(与其间隔开)。如图3所示,焊盘(包括第一焊盘232和第二焊盘240)的放置是一个示例。在其它示例中,一些焊盘(包括第一焊盘232和第二焊盘240)比所示的更大或更小。例如,在一些示例中,第一焊盘232和/或第二焊盘240从多层封装基板208的中心区域延伸到与周边332相交的区域。

55.返回参考图2,在一些示例中,第一焊盘232和/或第二焊盘240可以从多层封装基板208的中心区域延伸到多层封装基板208的周边332以增加功率转换器模块216操作期间的电流。如图所示,通过定位第一端子244和第二端子252以分别匹配第一焊盘232和第二焊盘240的位置,第二区域324也被缩小,从而进一步缩减由功率转换器模块216的操作引起的emi。

56.为了比较的目的,包括了方框340,其近似采用常规技术的回路电流的区域。方框340横穿沿着多层封装基板208的周边332定位的焊盘336。如图所示,方框340所限制的区域明显大于第一区域320和第二区域324的组合。因此,通过实现多层封装基板208,第一区域320以及在一些示例中第二区域324被缩小,从而缩减由功率转换器模块216的操作引起的emi。

57.图4示出了安装在pcb 404上的半导体器件400的另一个示例的图。半导体器件400可用于实现图1的半导体器件100,并且pcb 404可用于实现图1的pcb 104。半导体器件400可以被实现为例如ic芯片。半导体器件400包括多层封装基板408,诸如多层封装基板qfn。此外,半导体器件100的管芯412安装在多层封装基板108上。

58.管芯412包括用于实现电操作的模块。特别地,管芯412包括功率转换器模块416。作为一个示例,功率转换器模块416是ac-dc转换器。作为另一示例,功率转换器模块416是dc-dc转换器,诸如降压转换器(减压转换器)或升压转换器(增压转换器)。对于所提供的示例,假设功率转换器模块416是dc-dc转换器。

59.功率转换器模块416包括输出端口420和返回端口424,其可以分别对应于图1的输

出端口152和返回端口164。多层封装基板408的第一电路径428耦接到功率转换器模块416的输出端口420以在输出端口420和多层封装基板408的第一焊盘432之间提供导电路径。此外,多层封装基板408的第二电路径436耦接到功率转换器模块416的返回端口424并且在返回端口424和多层封装基板408的第二焊盘440之间提供导电路径。

60.如所指出的,半导体器件400安装在pcb 404上。更具体地,半导体器件400安装成使得多层封装基板408的第一焊盘432耦接到pcb 404上的负载448的第一端子444,并且多层封装基板408的第二焊盘440耦接到负载448的第二端子452。负载448表示从功率转换器模块416向其提供功率的电路部件。负载448包括与电容器458和电阻负载460(标记为rload)之间的并联连接件串联连接的电感器456。负载448可以用来实现图1的负载178。电感器456可以被称为负载电感器。此外,电阻负载460可以表示为电阻器。此外,在各种示例中,电阻负载460被实现为电容性电阻性和电感性部件或其一些子集的组合。此外,负载448的架构基于被选为功率转换器模块416的功率转换器的类型(例如,降压转换器、升压转换器、ac-dc转换器等)而改变。

61.多层封装基板408包括四层,第一层464、第二层468、第三层472和第四层476。第一电路径428包括形成在多层封装基板408的第一层464上的第一迹线482。第一电路径428还包括第一导通孔486,其在第一迹线482和多层封装基板408的第三层472上的第一电路径428的第二迹线490之间提供导电路径。第一电路径428还包括第二导通孔494,其在第二迹线490和多层封装基板408的第一焊盘432之间提供导电路径。

62.多层封装基板208的层具有大约(例如,在10%以内)相等的厚度。因此,多层封装基板208的两层的组合比多层封装基板208的单层厚。例如,第一层464和第二层468具有的组合厚度大于第三层472的厚度。

63.第二电路径436包括形成在多层封装基板408的第一层464上的第三迹线498。第二电路径436还包括第三导通孔502,其在第三迹线498和多层封装基板408的第三层472上的第二电路径436的第四迹线506之间提供导电路径。第二电路径436还包括第四导通孔510,其在第四迹线506和多层封装基板408的第二焊盘之间提供导电路径440。此外,第四迹线506在第三导通孔502和第四导通孔510之间提供导电路径。第一电路径428和第二电路径436分别提供第一寄生电感512和第二寄生电感514。

64.在操作中,电流回路(例如,对应于图1的第一电流回路184)限制第一区域520和第二区域524。第一区域520对应于图1的第一区域190,使得第一区域520表示半导体器件400内的电流回路的一部分。第一区域520和第二区域524组合的大小与功率转换器模块416的操作引起的emi量成比例。

65.为了缩小第一区域520的面积(这减小电流回路的面积),第一电路径428和第二电路径436的几何形状被选择为形成l形多边形(例如,不规则多边形)。更具体地,第一电路径428从正交于管芯412的表面528的方向从输出端口420到第二迹线490线性地延伸一段距离,该距离大于多层封装基板408的第三层472的厚度。第二迹线490提供电路径,该电路径在平行于表面528的方向上从多层封装基板408的内部区域延伸到多层封装基板408的周边532。因此,第一焊盘432位于管芯412的周边532处。另外,第二电路径436提供从多层封装基板408的第二焊盘440到功率转换器模块416的返回端口424的基本线性路径。更具体地,第二电路径436在正交于(垂直于)管芯412的表面528的方向上延伸。为第一电路径428和第二

电路径436提供几何形状缩减第二寄生电感514,这改善功率转换器模块416的整体性能。

66.为了比较的目的,包括方框540,其近似采用常规技术的回路电流的区域。方框540是矩形形状。如图所示,方框540所限制的区域大于第一区域520和第二区域524的组合。因此,通过实现多层封装基板408,第一区域520被缩小,使得缩减由功率转换器模块416的操作引起的emi。

67.图5示出了用于半导体器件的多层封装基板600的三维(3d)模型,其中已经使管芯和模制(封装)透明以示出多层封装基板600的细节。多层封装基板600包括表示与管芯的连接的端口604,其中只有一些被标记。多层封装基板600可用于实现图1的多层封装基板108和/或图2的多层封装基板208。附加地或替代地,多层封装基板600可以被修改/调整以适应特定的设计参数。

68.多层封装基板600的分区608表示多层封装基板600中的提供功率转换器模块(例如,图2的功率转换器模块216)和pcb(例如,图2的pcb 204)之间的连接的部分。分区608包括第一电路径612和第二电路径616。

69.第一电路径612包括端口620,其表示到功率转换器模块的输出端口的连接。第二电路径616包括端口624,其表示到功率转换器模块的返回端口的连接。多层封装基板600包括限定半导体器件边界的周边628。

70.出于说明的目的,多层封装基板600的图包括用于实现第一电路径612和第二电路径616的两个不同示例的第二视图。这些第二视图示出了多层封装基板600的下侧的一部分的示例。

71.第一示例包括可用于分别实现第一电路径612和第二电路径616的第一电路径630和第二电路径634。多层封装基板600包括四(4)层。因此,第一电路径630和第二电路径634的第一示例也包括四(4)层。第一电路径630包括将端口620耦接到第一焊盘640的导电部件(例如,迹线和导通孔)的堆叠。如第一示例的第一电路径630所示,在端口620和第一焊盘640之间形成线性路径。此外,第二电路径634包括将端口624耦接到第二焊盘644的导电部件(例如,迹线和导通孔)的堆叠。如图所示,第一焊盘640和第二焊盘644被认为是不与多层封装基板600的周边628相交的岛状焊盘。

72.第二示例包括可用于分别实现第一电路径612和第二电路径616的第一电路径660和第二电路径664。如所指出的,多层封装基板600包括四(4)层,使得第一电路径660和第二电路径664的第二示例也包括四(4)层。第一电路径660包括将端口620耦接到第一焊盘670的导电部件(例如,迹线和导通孔)的堆叠。如第一示例的第一电路径660所示,在端口620和第一焊盘670之间形成线性路径。此外,第二电路径634包括将端口624耦接到第二焊盘674的导电部件(例如,迹线和导通孔)的堆叠。如图所示,第一焊盘640和第二焊盘644和第二焊盘674均包括从多层封装基板600的内部延伸到多层封装基板600的周边628的部分。与第一示例的第一焊盘640和第二焊盘644相比,第二示例的第一焊盘670和第二焊盘674被放大以增加表面区域和电流。增加表面区域进一步缩减由功率转换器模块的操作引起的emi。

73.图6示出了分别可用作图5的第一电路径612和图5的第二电路径616的第一电路径720和第二电路径724的第一视图700和第二视图710的另一个示例。第一电路径720和第二电路径724可用于实现图4的第一电路径428和第二电路径436。另外,第一电路径720和第二电路径436可以修改/调整以适应特定的设计参数。

74.在第一视图700和第二视图710所示的示例中,第一电路径720包括在对应于图6的端口620的端口728和用于多层封装基板(图6的多层封装基板600)的第一焊盘732之间提供导电路径的导通孔和迹线的堆叠。此外,在所示示例中,第一电路径720包括第一迹线736,其从端口728下面的区域延伸到第一焊盘732上面的区域。类似地,第二电路径724也包括在对应于图6的端口624的端口740和第二焊盘744之间提供导电路径的迹线和导通孔的堆叠。更具体地,第二电路径724还包括第二迹线738,其位于包括端口740的区域下面并延伸到包括第二焊盘744的区域。通过在多层封装基板的顶层以外的层上提供第一迹线736和第二迹线738,第一电路径720和第二电路径724缩减由对应功率转换器的操作引起的emi。在其它示例中,其它处理技术可用于在端口728与第一焊盘732之间和/或在端口740与第二焊盘744之间提供导电路径。例如,在一些示例中,可采用耦接金属将管芯凸块连接到pcb以实现导电路径。

75.图7至图15示出了用于制造多层封装基板(诸如图1的多层封装基板108、图2的多层封装基板208、图3的多层封装基板408或图6的多层封装基板600)的方法的阶段。图7至图15的方法示出了如何使用多层(四层)材料来提供多层封装基板。此外,可以采用类似的方法来提供其它类型的连接器组件。

76.如图7所示,在800处,在第一阶段中,第一金属层图案900镀在金属载体904上以形成多层封装基板的第一层。如图8所示,在第二阶段中,在810处,柱908(例如,铜柱或由其它金属形成的柱)镀在第一金属层图案900上。如图9所示,在820处,在第三阶段中,在压缩模制操作中第一电介质层912被施加到柱908和第一金属层图案900。如图10所示,在第四阶段中,在825处,在研磨操作中第一电介质层912的一部分被去除,使得柱908的区域暴露,并且形成多层封装基板的第二层。

77.如图11所示,在第五阶段中,在835处,第二金属层图案916镀在多层封装基板的第二层的第一电介质层912上,以形成多层封装基板的第三层。如图12所示,在第六阶段中,在840处,将柱920(例如,铜柱或由其它金属形成的柱)施加到第二金属层图案916。如图13所示,在第七阶段中,在845处,在压缩模制操作中第二电介质层924被施加到柱920和第二金属层图案916。如图14所示,在第八阶段中,在850处,在研磨操作中第二电介质层924的一部分被去除,使得柱920的区域暴露,并且形成多层封装基板的第四层。如图15所示,在第九阶段中,在855处,在去载体操作中,金属载体904被去除。在855处执行的去载体操作暴露了第一金属层图案900的区域。如图7至图15所示,通过实现该方法,多层封装基板的所得四层可用于提供相对复杂的电路径。具体地,如图7至图15所示,在将管芯安装在多层封装基板上之前形成(预模制)第一电介质层912和第二电介质层924。这种预模制操作将电介质分布在整个多层封装基板上,并实现本文所述的信号路径的复杂性。例如,在一个示例中,第一金属镀层图案904和第二金属镀层图案916的第一部分可用于形成第一电路径,诸如图2的第一电路径228。类似地,第一金属镀层图案904和第二镀层图案916的第二部分可用于形成第二电路径,诸如图2的第二电路径236。

78.图16至图18示出了用于封装半导体器件(例如,ic芯片)的方法的阶段。通过图16至图18的方法形成的半导体器件可用于实现图1的半导体器件100、图2的半导体器件200和/或图4的半导体器件400。如图16所示,在第一阶段中,在1000处,提供多层封装基板1100。作为一个示例,多层封装基板1100是用图7至图15所示的方法形成的。如图17所示,在

第二阶段中,在1010处,在焊接操作中管芯1104被安装在(粘附到)多层封装基板1100上。该管芯包括功率转换器模块。如图18所示,在第三阶段中,在1020处,在封装操作中模制件1112被施加到管芯1104和多层封装基板1100以形成半导体器件1120。

79.如图16至图18所示,在所示方法中,利用用于管芯1104的电介质预模制多层封装基板1100。也就是说,电介质分布在整个多层封装基板1100中。因此,粘附管芯1104不需要施加电介质材料来保持多层封装基板1100中的层的位置静止。

80.图19示出了用于形成半导体器件(例如,ic封装件)的示例方法1200的流程图。例如,可以采用方法1200来形成图1的半导体器件100、图2的半导体器件200和/或图4的半导体器件400。在1210处,可以形成多层封装基板(例如,图1的多层封装基板108)或其它类型的连接器组件。多层封装基板1210可以例如用图7至图15所示的方法形成。多层封装基板可以包括包含分布在整个多层封装基板中的电介质的层(如图15和图18所示)。多层封装基板的层形成多层封装基板的第一迹线与焊盘的第一焊盘之间的第一电路径以及多层封装基板的第二迹线与焊盘的第二焊盘之间的第二电路径。

81.在1215处,将管芯(例如,图1的管芯112)安装到多层封装基板,管芯包括功率转换器模块(例如,图1的功率转换器模块116),该功率转换器模块包括位于管芯表面处的输出端口和返回端口。输出端口被配置成耦接到多层封装基板的第一迹线。返回端口被配置成耦接到多层封装基板的第二迹线。第一电路径在正交于管芯的表面的方向上延伸一段距离,该距离大于多层封装基板的单层的厚度。在1220处,模制材料被施加到管芯和多层封装基板以形成半导体器件。

82.上面已经描述的是示例。当然,不可能描述部件或方法的每一种可能的组合,但是本领域的普通技术人员将认识到许多进一步的组合和排列是可能的。因此,本公开旨在涵盖落入本技术的范围内的所有此类变更、修改和变化,包括所附权利要求。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1