半导体存储装置的制作方法

半导体存储装置

1.本技术享受以日本专利申请2020-155472号(申请日:2020年9月16日)为基础申请的优先权。本技术通过参照该基础申请而包括基础申请的全部内容。

技术领域

2.本发明的实施方式涉及半导体存储装置。

背景技术:

3.半导体存储装置具备壳体、容纳于壳体的基板及安装于基板的半导体存储器部件。半导体存储装置被期待着散热性的提高。

技术实现要素:

4.本发明的一实施方式所要解决的课题在于,提供一种能够谋求散热性的提高的半导体存储装置。

5.一实施方式的半导体存储装置具有壳体、第1基板模块、多个散热板及1个以上的连接部。第1基板模块包括第1基板和1个以上的第1电子部件。第1基板模块容纳于壳体内。多个散热板在壳体内在第1基板的厚度方向上与第1基板模块相面对的位置沿厚度方向配置。1个以上的连接部与第1基板模块及多个散热板相接。

附图说明

6.图1是示出第1实施方式的半导体存储装置的外观的一例的立体图。

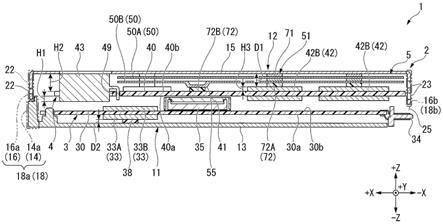

7.图2是沿着图1的ii-ii线的剖视图。

8.图3是第1实施方式的基体侧基板模块的仰视图。

9.图4是第1实施方式的基体侧基板模块的俯视图。

10.图5是第1实施方式的罩侧基板模块的仰视图。

11.图6是第1实施方式的罩侧基板模块的俯视图。

12.图7是示出拆卸了第1实施方式的罩的状态的半导体存储装置的立体剖视图。

13.图8是沿着图7的viii-viii线的剖视图。

14.图9是第2实施方式的半导体存储装置的剖视图。

15.图10是第2实施方式的基板模块的仰视图。

16.图11是第2实施方式的基板模块的俯视图。

17.标号说明

[0018]1…

半导体存储装置

[0019]2…

壳体

[0020]3…

基体侧基板模块(第2基板模块)

[0021]4…

罩侧基板模块(第1基板模块)

[0022]

15

…

第2主壁(第1壁)

[0023]

18a

…

第1侧壁(第2壁)

[0024]

18b

…

第2侧壁(第2壁)

[0025]

22

…

第1连通孔(连通孔)

[0026]

23

…

第2连通孔(连通孔)

[0027]

30

…

主基板(第2基板)

[0028]

33

…

nand(第2电子部件)

[0029]

40

…

子基板(第1基板)

[0030]

42

…

nand(第1电子基板)

[0031]

43

…

电容器(安装部件)

[0032]

50

…

内板(散热板)

[0033]

50a

…

第1板(散热板)

[0034]

50b

…

第2板(散热板)

[0035]

51

…

连接部

[0036]

72

…

罩侧缓冲部(热传导性构件)

[0037]

75

…

第1间隔件(间隔件)

[0038]

76

…

第2间隔件(间隔件)

[0039]

77

…

紧固连结销(保持部)

[0040]

100

…

半导体存储装置

[0041]

101

…

基板模块(第1基板模块)

[0042]

110

…

基板(第1基板)

具体实施方式

[0043]

以下,参照附图来说明实施方式的半导体存储装置。此外,在以下的说明中,对具有同一或类似的功能的结构标注同一标号。并且,存在省略这些结构的重复的说明的情况。在本说明书中,“平行”包括“大致平行”的情况。在本说明书中,“正交”包括“大致正交”的情况。在本说明书中,“相面对”意味着2个构件的至少一部分互相重叠。在本说明书中,“连接”不仅包括2个构件在中间什么也不夹设而相邻的情况,也包括在2个构件之间夹设别的构件的情况。另外,“相接”意味着在2个构件之间什么也不夹设而相邻。

[0044]

首先,对x方向、y方向及z方向进行定义。x方向及y方向是沿着后述的子基板40的第1面40a的方向中的互相交叉的方向(参照图2)。x方向是+x方向和-x方向的统称。+x方向是从后述的壳体2的第2侧壁18b朝向第1侧壁18a的方向(参照图2)。以下,将+x方向为了方便而称作“+x”。-x方向是与+x相反的方向。以下,将-x方向为了方便而称作

“‑

x”。在不区分+x和-x的情况下,简称作“x方向”。x方向是“第1方向”的一例。y方向是+y方向和-y方向的统称。+y方向是从后述的dram32a朝向控制器31的方向(参照图3)。以下,将+y方向为了方便而称作“+y”。-y方向是与+y相反的方向。以下,将-y方向为了方便而称作

“‑

y”。在不区分+y和-y的情况下,简称作“y方向”。y方向是“第2方向”的一例。z方向是与x方向及y方向交叉的方向。z方向是+z方向和-z方向的统称。+z方向是从后述的基体侧基板模块3朝向罩侧基板模块4的方向(参照图2)。以下,将+z方向为了方便而称作“+z”。-z方向是与+z相反的方向。以下,将-z方向为了方便而称作

“‑

z”。在不区分+z和-z的情况下,简称作“z方向”。z方向是后

述的主基板30、子基板40及基板110各自的厚度方向。

[0045]

(第1实施方式)

[0046]

本实施方式的半导体存储装置1是例如ssd(solid state drive:固态驱动器)这样的存储装置。半导体存储装置1例如向服务器装置、个人计算机等信息处理装置安装。半导体存储装置1作为信息处理装置的存储区域来利用。在本实施方式中,将安装半导体存储装置1的信息处理装置称作主机装置。

[0047]

半导体存储装置1例如具备壳体2、基体侧基板模块3、罩侧基板模块4及散热模块5。罩侧基板模块4是第1基板模块的一例。散热模块5相对于罩侧基板模块4位于+z侧。

[0048]

接着,对壳体2进行详细说明。图1是示出第1实施方式的半导体存储装置1的外观的一例的立体图。

[0049]

壳体2构成半导体存储装置1的外廓。壳体2例如是以x方向为长边方向、以y方向为短边方向、以z方向为厚度方向的箱状。壳体2例如为金属制。壳体2也可以由多个构件构成。

[0050]

壳体2具有基体11和罩12。壳体2通过基体11和罩12在z方向上被组合而形成。基体11及罩12由紧固连结构件17紧固连结。紧固连结构件17例如是螺纹件。

[0051]

基体11是朝向罩12开口的箱型。即,基体11是+z开放的碗状。基体11具备第1主壁13和第1周壁14。第1主壁13是以x方向为长边方向、以y方向为短边方向、以z方向为厚度方向的矩形形状。第1主壁13在基体11中最靠-z侧。第1主壁13具有4个端部。第1主壁13的4个端部即为+x侧、-x侧、+y侧及-y侧的端部。第1周壁14从第1主壁13的除了-x侧的端部之外的3个端部分别向+z侧(罩12侧)延伸。即,第1周壁14从第1主壁13的+x侧的端部、第1主壁13的+y侧的端部及第1主壁13的-y侧的端部的各自向+z侧延伸。

[0052]

罩12是朝向基体11开口的箱型。即,罩12是-z开放的碗状。罩12具备第2主壁15和第2周壁16。第2主壁15是以x方向为长边方向、以y方向为短边方向、以z方向为厚度方向的矩形形状。第2主壁15是“第1壁”的一例。第2主壁15在罩12中最靠+z侧。第2主壁15与第1主壁13在z方向上相面对。第2主壁15具有4个端部。第2主壁15的4个端部即为+x侧、-x侧、+y侧及-y侧的端部。第2周壁16从第2主壁15的4个端部分别向-z侧延伸。

[0053]

接着,对壳体2的结构进一步进行详细说明。图2是沿着图1的ii-ii线的剖视图。

[0054]

基体11的第1周壁14及罩12的第2周壁16构成壳体2的周壁18。将周壁18中的+x侧称作第1侧壁18a。第1侧壁18a是沿着y方向及z方向的板状。第1侧壁18a由第1部分14a及第2部分16a构成。第1部分14a在第1周壁14中相对于第1主壁13位于+x侧。第2部分16a在第2周壁16中相对于第2主壁15位于+x侧。在第1侧壁18a形成有多个第1连通孔22。将周壁18中的-x侧称作第2侧壁18b。第2侧壁18b是沿着y方向及z方向的板状。第2侧壁18b由第2周壁16中的相对于第2主壁15位于-x侧的第3部分16b构成。第3部分16b在第2周壁16中相对于第2主壁15位于-x侧。在第2侧壁18b形成有多个第2连通孔23。第1侧壁18a及第2侧壁18b的各自是第2壁的一例。

[0055]

第1连通孔22是将第1侧壁18a在x方向上贯通的通气孔。第1连通孔22使壳体2的内外连通。更详细而言,第1连通孔22形成于第1侧壁18a的第2部分16a。多个第1连通孔22在第1侧壁18a中在y方向及z方向上隔开间隔而形成。

[0056]

第2连通孔23是将第2侧壁18b在x方向上贯通的通气孔。第2连通孔23使壳体2的内外连通。更详细而言,第2连通孔23形成于第2侧壁18b的第3部分16b。多个第2连通孔23在第

2侧壁18b中在y方向及z方向上隔开间隔而形成。

[0057]

第1连通孔22及第2连通孔23可以是,任一者作为吸气孔发挥功能,任一者作为排气孔发挥功能。例如,在半导体存储装置1被放置于风从+x侧向-x侧流动的环境的情况下,壳体2的外部的空气从第1连通孔22向壳体2的内部流入,从第2连通孔23向壳体2的外部排出。在半导体存储装置1被放置于风从+x侧向-x侧流动的环境的情况下,壳体2的外部的空气从第2连通孔23向壳体2的内部流入,从第1连通孔22向壳体2的外部排出。以下,对半导体存储装置1被放置于风从+x侧向-x侧流动的环境的情况进行说明。

[0058]

而且,在第2侧壁18b形成有连接口25。更详细而言,连接口25形成于第2侧壁18b中的构成第1周壁14的部分。连接口25是比第1连通孔22及第2连通孔23大的开口部。连接口25位于比第2连通孔23靠-z侧处。连接口25是使后述的外部连接器34向壳体2的外部露出的开口部。

[0059]

接着,对基体侧基板模块3进行详细说明。图3是第1实施方式的基体侧基板模块3的仰视图。图4是第1实施方式的基体侧基板模块3的俯视图。

[0060]

基体侧基板模块3是电子电路安装基板。基体侧基板模块3是第2基板模块的一例。基体侧基板模块3相对于罩侧基板模块4位于-z侧。

[0061]

基体侧基板模块3具备主基板30、控制器31、多个dram(dynamic random access memory:动态随机存取存储器)32、多个nand型闪速存储器(nand)33、外部连接器34及内部连接器35。

[0062]

主基板30是基板。主基板30例如是印制布线基板。主基板30是第2基板的一例。主基板30是以x方向为长边方向、以y方向为短边方向、以z方向为厚度方向的板状。在主基板30能够安装任意的数量的电子部件。主基板30配置于壳体2内。主基板30通过螺钉等而固定于基体11。主基板30具备第1面30a和第2面30b。第1面30a是与第1主壁13相面对的面。第1面30a是-z侧的面。第2面30b位于与第1面30a相反的一侧。第2面30b是与罩侧基板模块4相面对的面。第2面30b是+z侧的面。

[0063]

控制器31是soc(system on a chip:片上系统)。控制器31是第2电子部件的一例。控制器31统括地控制半导体存储装置1。控制器31与dram32及nand33相比发热量大。在图3所示的例子中,控制器31安装于主基板30的第1面30a的中央部。控制器31在x方向上位于1个以上的nand33与外部连接器34之间。

[0064]

dram32是数据缓冲器。dram32是易失性的半导体存储器。dram32是第2电子部件的另一例。dram32是半导体存储器部件的一例。在dram32中暂时地保存从主机装置接收到的写入数据和/或从nand33读出的读出数据。在dram32中,存在dram32a和dram32b这2个种类。dram32a安装于第1面30a。dram32b安装于第2面30b。

[0065]

nand33是非易失性的半导体存储器芯片。nand33是第2电子部件的另一例。nand33是半导体存储器部件的另一例。在多个nand33中,存在nand33a和nand33b这2个种类。nand33a安装于第1面30a。nand33b安装于第2面30b。

[0066]

外部连接器34将半导体存储装置1和主机装置连接。外部连接器34形成于主基板30中的-x侧。如图2所示,外部连接器34在基体侧基板模块3容纳于壳体2内的状态下,通过连接口25而向壳体2的外部露出。外部连接器34具有多个连接端子。多个连接端子在y方向上排列。多个连接端子在主基板30的第1面30a及第2面30b露出。

[0067]

内部连接器35是所谓的基板间连接器(b to b连接器)。内部连接器35例如安装于主基板30的第2面30b的中央部。内部连接器35具有与后述的内部连接器41连接的多个连接端子。

[0068]

如图2所示,基体侧基板模块3经由多个基体侧缓冲部38而与第1主壁13相接。基体侧缓冲部38是所谓的tim(thermal interface material:热界面材料)。基体侧缓冲部38具有缓冲功能和散热功能(热传导功能)。基体侧缓冲部38也可以被称作“热传导性构件”。基体侧缓冲部38由热传导性优异且弹性比控制器31、dram32及nand33优异的材料(例如,树脂材料等)形成。基体侧缓冲部38例如由热传导率比主基板30及子基板40高的材料形成。基体侧缓冲部38形成为以z方向为厚度方向的片材状。基体侧缓冲部38夹设于控制器31与第1主壁13之间、dram32a与第1主壁13之间、nand33a与第1主壁13之间及其他的各种电子部件与第1主壁13之间。基体侧缓冲部38例如可以是润滑脂、粘接材料等。控制器31、dram32a及nand33a分别经由基体侧缓冲部38而与第1主壁13热连接。基体侧缓冲部38也可以夹设于主基板30的第1面30a与第1主壁13之间,将主基板30的第1面30a与第1主壁13热连接。

[0069]

接着,对罩侧基板模块4进行详细说明。图5是罩侧基板模块4的仰视图。

[0070]

罩侧基板模块4是电子电路安装基板。罩侧基板模块4例如具备子基板40、内部连接器41、多个nand42及多个电容器43。

[0071]

子基板40是基板(例如印制布线基板)。子基板40是第1基板的一例。子基板40是以x方向为长边方向、以y方向为短边方向、以z方向为厚度方向的板状。在子基板40能够安装任意的数量的电子部件。子基板40配置于壳体2内。子基板40与主基板30平行地配置。子基板40通过螺钉等而固定于基体11。在子基板40中的+x侧的端部形成有缺口部49。缺口部49将子基板40在z方向上贯通,并且向+x侧开放。子基板40具备第1面40a和第2面40b。第1面40a是与基体侧基板模块3相面对的面。第1面40a是-z侧的面。第2面40b是与第2主壁15相面对的面。第2面40b位于与第1面40a相反的一侧。第2面40b是+z侧的面。

[0072]

内部连接器41是与基体侧基板模块3的内部连接器35连接的连接器。内部连接器41具有多个连接端子。内部连接器41例如安装于子基板40的第1面40a的中央部。

[0073]

nand42是非易失性的半导体存储器。nand42是半导体存储器部件的另一例。在nand42中,存在nand42a和nand42b这2个种类。nand42a安装于子基板40的第1面40a。nand42b安装于子基板40的第2面40b。

[0074]

电容器43是承担电源备用功能的电容器。电容器43是安装部件的一例。电容器43例如是氧化铝电解电容器或导电性高分子钽固体电解电容器等。例如,电容器43在来自主机装置的电力供给被意外地切断的情况下,对控制器31、dram32、nand33及nand42供给电力。例如,电容器43在直到暂时地存储于dram32的数据向nand33或nand42存储为止的期间,向控制器31、dram32、nand33及nand42供给电力。电容器43是以x方向为轴向的圆柱状。电容器43的z方向的厚度比nand42的z方向的厚度大。例如,电容器43的z方向的厚度为nand42的z方向的厚度的2倍以上。如图6所示,电容器43使用多个。多个电容器43以容纳于子基板40的缺口部49内的状态安装于子基板40。多个电容器43在缺口部49内在y方向上排列。如图7所示,在y方向上相邻的2个电容器43之间的间隙随着从中央部朝向+z侧或-z侧而逐渐变宽。如图2所示,电容器43相对于子基板40向z方向的两侧突出。例如,电容器43相对于子基板40的第1面40a向-z侧的突出量h1比电容器43相对于子基板40的第2面40b向+z侧的突出

量h2小。例如,电容器43相对于子基板40的第2面40b的突出量h2比nand42b相对于子基板40的第2面40b的突出量h3大。nand42b的突出量h3是nand42b的z方向的厚度。例如,电容器43的突出量h2为nand42b的突出量h3的2倍以上。例如,电容器43的突出量h2比主基板30的第1面30a与第1主壁13之间的z方向的间隙大。罩侧基板模块4的电容器43的-z侧的端部相对于基体侧基板模块3的nand33b在z方向上分离。

[0075]

接着,对散热模块5进行详细说明。散热模块5将在罩侧基板模块4中产生的热散发。如图2所示,散热模块5在壳体2内配置于第2主壁15与子基板40之间。散热模块5在相对于电容器43向-x侧偏移的位置处,将罩侧基板模块4从+z侧覆盖。散热模块5至少与罩侧基板模块4相接即可,也可以与壳体2分离。散热模块5例如也可以配置于基体侧基板模块3与罩侧基板模块4之间。散热模块5还可以配置于基体侧基板模块3与基体11之间。

[0076]

散热模块5例如具备多个内板50和多个连接部51。内板50例如是2张。连接部51例如是7个。以下,对内板50及连接部51进行详细说明。

[0077]

对内板50进行详细说明。内板50是散热器(heat sink)。内板50是散热板的一例。内板50使在基体侧基板模块3中产生的热散发。内板50是以x方向为长边方向、以y方向为短边方向、以z方向为厚度方向的板状。内板50与子基板40及第2主壁15平行。多个内板50在z方向上隔开间隙而配置。多个内板50之间的z方向的间隙比主基板30与第1主壁13之间的z方向的间隙小。多个内板50之间的z方向的间隙比主基板30与子基板40之间的z方向的间隙小。内板50至少具有将全部的nand42b从+z侧覆盖的大小。例如,内板50的x方向的长度为主基板30的x方向的长度的1/2以上。内板50的x方向的长度为子基板40的x方向的长度的1/2以上。例如,内板50的y方向的长度为主基板30的y方向的长度的1/2以上。内板50的y方向的长度为子基板40的y方向的长度的1/2以上。内板50由热传导性比主基板30及子基板40优异的材料形成。热传导性优异的材料例如是铝、铜等金属材料。内板50的最小厚度比主基板30及子基板40的最小厚度薄。内板50位于电容器43的高度范围内。即,多个内板50中的最靠+z侧的内板50(后述的第1板50a)的+z侧的面位于比电容器43的+z侧的端靠-z侧处。因此,多个内板50在x方向上与电容器43重叠。此外,内板50的厚度、张数、布局等能够任意设定。只要是内板50和nand42b经由连接部51而连接的结构即可,例如内板50也可以是一张。

[0078]

多个内板50包括第1板50a和第2板50b。第1板50a和第2板50b互相平行。

[0079]

第1板50a是多个内板50中的最靠+z侧的内板50。第1板50a与第2主壁15相面对。第1板50a与第2主壁15之间的z方向的间隙比主基板30与第1主壁13之间的z方向的间隙小。第1板50a与第2主壁15之间的z方向的间隙比主基板30与子基板40之间的z方向的间隙小。

[0080]

第2板50b是多个内板50中的最靠-z侧的内板50。第2板50b与罩侧基板模块4相面对。第2板50b与nand42b之间的z方向的间隙比主基板30与第1主壁13之间的z方向的间隙小。第2板50b与nand42b之间的z方向的间隙比主基板30与子基板40之间的z方向的间隙小。在第2板50b中的与内部连接器41互相重叠的区域形成有鼓出部55。鼓出部55相对于第2板50b的其他部分而朝向子基板40鼓出。

[0081]

接着,对连接部51进行详细说明。图7是示出拆卸了罩12的状态的半导体存储装置1的立体剖视图。

[0082]

连接部51是将散热模块5和壳体2连接的构件。连接部51与罩侧基板模块4、内板50及第2主壁15相接。连接部51使在罩侧基板模块4中产生的热向多个内板50及第2主壁15移

动。连接部51配置于与nand42b在z方向上重叠的位置。连接部51夹设于nand42b与第2主壁15之间。连接部51的x方向及y方向的尺寸比对应的nand42的x方向及y方向的尺寸小。相邻的连接部51之间的间隙供空气流动。

[0083]

连接部51具备紧固连结部71和罩侧缓冲部72。紧固连结部71是连结多个内板50和第2主壁15的构件。紧固连结部71也可以与子基板40相接。罩侧缓冲部72是夹设于紧固连结部71与罩侧基板模块4之间的缓冲构件。罩侧缓冲部72与紧固连结部71及nand42b相接。罩侧缓冲部72使热从nand42b向紧固连结部71移动。

[0084]

接着,对紧固连结部71的详情进行详细说明。在此,首先对用于供紧固连结部71贯通第2主壁15、第1板50a及第2板50b的贯通孔即主壁贯通孔80、第1贯通孔81及第2贯通孔82进行说明。如图8所示,主壁贯通孔80形成于第2主壁15。主壁贯通孔80将第2主壁15在z方向上贯通。主壁贯通孔80在x方向及y方向上隔开间隔而排列。在第2主壁15中的主壁贯通孔80的周围也可以形成有凹陷部85。在图8的例子中,主壁贯通孔80在凹陷部85的底面处开口。第1贯通孔81形成于第1板50a。第1贯通孔81将第1板50a在z方向上贯通。第1贯通孔81在x方向及y方向上隔开间隔而排列。第2贯通孔82形成于第2板50b。第2贯通孔82将第2板50b在z方向上贯通。第2贯通孔82在x方向及y方向上隔开间隔而排列。多个主壁贯通孔80、第1贯通孔81及第2贯通孔82中的对应的主壁贯通孔80、第1贯通孔81及第2贯通孔82在从z方向观察时互相重叠。

[0085]

紧固连结部71具备第1间隔件75、第2间隔件76及紧固连结销77。第1间隔件75及第2间隔件76是间隔件的一例。紧固连结销77是保持部的一例。

[0086]

第1间隔件75是在第2主壁15与第1板50a之间确保间隙的间隔件。第1间隔件75是以z方向为轴向的筒状。第1间隔件75由热传导性优异的材料形成。热传导性优异的材料例如是铝、铜等金属材料。第1间隔件75由热传导率比主基板30及子基板40高的材料形成。第1间隔件75夹设于第1板50a与第2主壁15之间。第1间隔件75与第1板50a及第2主壁15分别相接。如图7所示,第1间隔件75的外径比nand42的x方向的最大尺寸小。第1间隔件75的外径比nand42的y方向的最大尺寸小。在第1间隔件75形成有将第1间隔件75在z方向上贯通的第1通过孔75a。第1通过孔75a与第1贯通孔81及主壁贯通孔80连通。

[0087]

第2间隔件76是在第1板50a与第2板50b之间确保间隙的间隔件。第2间隔件76是以z方向为轴向的筒状。第2间隔件76由热传导性优异的材料形成。热传导性优异的材料例如是铝、铜等金属材料。第2间隔件76由热传导率比主基板30及子基板40高的材料形成。第2间隔件76在第1板50a与第2板50b之间与第1间隔件75同轴地配置。第2间隔件76夹设于第1板50a与第2板50b之间。第2间隔件76与第1板50a及第2板50b分别相接。在第2间隔件76形成有将第2间隔件76在z方向上贯通的第2通过孔76a。第2间隔件76的第2通过孔76a与第1贯通孔81及第2贯通孔82连通。如图7所示,第2间隔件76的外径与第1间隔件75的外径相等。

[0088]

紧固连结销77是所谓的铆接销。紧固连结销77由热传导性优异的材料形成。热传导性优异的材料例如是铝、铜等金属材料。紧固连结销77由热传导率比主基板30及子基板40高的材料形成。

[0089]

紧固连结销77具有头部77a及轴部77b。头部77a是紧固连结销77的+z侧的端部。头部77a从轴部77b呈凸缘状地伸出。头部77a的一部分与第2主壁15、第1间隔件75及第2间隔件76在z方向上相面对。头部77a从相对于第2主壁15而与第1间隔件75相反的一侧与第2主

壁15相接。头部77a配置于凹陷部85内。轴部77b在主壁贯通孔83、第1通过孔75a、第1贯通孔81、第2贯通孔82及第2通过孔76a内在z方向上贯通。

[0090]

在轴部77b的前端部形成有铆接部77c。铆接部77c是紧固连结销77的-z侧的端部。铆接部77c通过在轴部77b插通于主壁贯通孔83、第1通过孔75a、第1贯通孔81、第2贯通孔82及第2通过孔76a内后,轴部77b的-z侧的端部以被向外周侧扩张的方式塑性变形而形成。铆接部77c从第2贯通孔82的开口缘伸出。铆接部77c的一部分(从第2贯通孔82的开口缘伸出的部分)与头部77a、第2主壁15、第1间隔件75及第2间隔件76在z方向上相面对。铆接部77c从相对于第2板50b而与第2间隔件76相反的一侧与第2板50b相接。

[0091]

由此,第2主壁15及各内板50以在第1板50a与第2主壁15之间以及相邻的2个内板50之间空出了间隙的状态夹持于头部77a与铆接部77c之间。多个内板50之间的间隙优选与第1连通孔22及第2连通孔23的至少任一者、在y方向上相邻的多个电容器43之间的间隙在x方向上互相重叠。第1板50a与第2主壁15之间的间隙优选与第1连通孔22及第2连通孔23的至少任一者、在y方向上相邻的多个电容器43之间的间隙在x方向上互相重叠。第2板50b与子基板40之间的间隙优选与第1连通孔22及第2连通孔23的至少任一者、在y方向上相邻的多个电容器43之间的间隙在x方向上互相重叠。此外,紧固连结销77也可以以头部77a位于-z侧且铆接部77c位于+z侧的状态被组装。

[0092]

接着,对罩侧缓冲部72的详情进行说明。罩侧缓冲部72是具有缓冲功能及热传导功能的构件。罩侧缓冲部72是所谓的tim(thermal interface material:热界面材料)。罩侧缓冲部72是以z方向为厚度方向的片材状。罩侧缓冲部72由热传导性优异且弹性比第1间隔件75、第2间隔件76、主基板30及子基板40优异的树脂材料形成。罩侧缓冲部72例如由热传导率比主基板30及子基板40高的材料形成。罩侧缓冲部72可以是润滑脂、粘接材料等。罩侧缓冲部72是热传导性构件的一例。

[0093]

罩侧缓冲部72存在第1缓冲部72a和第2缓冲部72b这2个种类。

[0094]

第1缓冲部72a是位于第2板50b与nand42b之间的罩侧缓冲部72。如图8所示,第1缓冲部72a夹设于紧固连结销77的铆接部77c与nand42b之间。第1缓冲部72a与紧固连结销77的铆接部77c及nand42b相接。第1缓冲部72a也可以以夹设于第2板50b与nand42b之间的状态与第2板50b及nand42b相接。

[0095]

第2缓冲部72b是位于子基板40与鼓出部55之间的罩侧缓冲部72。第2缓冲部72b与鼓出部55及子基板40相接。鼓出部55与子基板40中的与内部连接器41在z方向上重叠的部分隔着第2缓冲部72b相面对。鼓出部55抑制罩侧基板模块4相对于基体侧基板模块3向+z侧的位移。基体侧基板模块3的内部连接器35与罩侧基板模块4的内部连接器41的连接被确保。

[0096]

接着,对半导体存储装置1的作用进行说明。

[0097]

在nand42a或42b中产生的热的一部分通过第1缓冲部72a及紧固连结部71而向多个内板50及罩12传递。由此,在nand42a或42b中产生的热被高效地散发。另外,罩侧基板模块4的温度上升被抑制。

[0098]

另外,相对于半导体存储装置1例如从+x侧向-x侧流动的空气通过第1连通孔22而向壳体2内流入。流入到壳体2内的空气通过电容器43的周围而到达散热模块5。通过电容器43的周围的空气流过在y方向上相邻的电容器43间的间隙中的位于+z侧的部分。

[0099]

到达了散热模块5的空气通过在z方向上相邻的多个内板50之间的间隙、第1板50a与第2主壁15之间的间隙及第2板50b与子基板40之间的间隙而向-x侧流动。由此,热从散热模块5散发。通过了散热模块5的空气通过第2连通孔23而从壳体2排出。

[0100]

此外,在基体侧基板模块3中产生的热经由基体侧缓冲部38而向基体11传递、经由内部连接器35而向罩侧基板模块4传递。传递到罩侧基板模块4的热的一部分通过如上述那样经由罩侧缓冲部72向多个内板50及罩12传递而被散发。

[0101]

接着,对本实施方式的结构的效果进行说明。

[0102]

本实施方式的半导体存储装置1在壳体2内在z方向上与罩侧基板模块4相面对的位置具备在z方向上配置的多个内板50和与罩侧基板模块4及多个内板50相接的连接部51。根据该结构,能够将在罩侧基板模块4中产生的热的一部分通过连接部51而向多个内板50传递。由此,与没有内板50的结构相比,能够提高散热性。另外,能够抑制罩侧基板模块4的温度上升。

[0103]

在本实施方式的半导体存储装置1中,连接部51与作为半导体存储装置1的主要的发热源的nand42b相接。根据该结构,在nand42b中产生的热容易经由连接部51而向多个内板50传递。由此,能够将在罩侧基板模块4中产生的热高效地散发。另外,散热性提高。

[0104]

在本实施方式中,多个连接部51与多个nand42b分别相接。根据该结构,能够将各在nand42b中产生的热通过各连接部51而向多个内板50高效地传递。由此,散热性提高。

[0105]

在本实施方式中,连接部51与壳体2(第2主壁15)相接。根据该结构,在连接部51中传递的热的一部分向壳体2传递后,从壳体2散发。由此,散热性提高。

[0106]

在本实施方式中,内板50配置于罩侧基板模块4与第2主壁15之间。根据该结构,容易将传递到内板50的热向第2主壁15传递。由此,能够抑制在壳体2内产生的热在壳体2内滞留。

[0107]

在本实施方式中,内板50配置于与电容器43在x方向上重叠的位置。由此,能够提高小型且散热性优异的半导体存储装置。

[0108]

在本实施方式中,在壳体2的第1侧壁18a形成有使壳体2的内外连通的第1连通孔22。根据该结构,通过在例如通过第1连通孔22而流入到壳体2内的空气与散热模块5之间进行热交换,能够将散热模块5的热有效地散发。

[0109]

在本实施方式中,连接部51(紧固连结部71)在x方向及y方向上互相隔开间隔而配置。根据该结构,能够将在罩侧基板模块4中产生的热向内板50传递。由此,散热性提高。

[0110]

在本实施方式中,连接部51具备夹设于在z方向上相邻的2个内板50之间的第2间隔件76。根据该结构,能够确保在z方向上相邻的2个内板50的间隔。由此,能够使空气向在z方向上相邻的2个内板50之间流通。另外,能够确保散热模块5的表面积。

[0111]

在本实施方式中,紧固连结销77将内板50、第1间隔件75及第2间隔件76一并保持。根据该结构,散热模块5由紧固连结销77一体地组装。因而,容易在半导体存储装置1组装散热模块5。

[0112]

在本实施方式的半导体存储装置1中,散热模块5通过紧固连结销77而固定于壳体2。根据该结构,能够通过紧固连结销77而向壳体2散发热。另外,也能够通过散热模块5来加强壳体2。

[0113]

在本实施方式中,在第2板50b与nand42之间夹设缓冲部72。根据该结构,能够提高

耐冲击性。另外,能够吸收部件公差。

[0114]

在本实施方式中,nand42b与第1主壁13之间的最小距离d1比nand33a与第2主壁15之间的最小距离d2大。根据该结构,能够确保散热模块5的配置空间。

[0115]

(第2实施方式)

[0116]

图9是第2实施方式的半导体存储装置100的剖视图。如图9所示,第2实施方式的半导体存储装置100具备壳体2、基板模块101及散热模块120。在第2实施方式的半导体存储装置100中,在取代基体侧基板模块3及罩侧基板模块4而使用基板模块101这一点上与上述的第1实施方式不同。在第2实施方式的半导体存储装置100中,基板模块101在壳体2内位于比z方向的中央部靠-z侧(基体11侧)处。

[0117]

图10是基板模块101的仰视图。如图10所示,基板模块101是电子电路安装基板。基板模块101例如具备基板110、控制器31、多个dram32、多个nand33、外部连接器34及电容器43。基板模块101是第1基板模块的一例。

[0118]

基板110例如是印制布线基板。基板110是“第1基板”的一例。基板110在从z方向观察时是以x方向为长边方向且以y方向为短边方向的矩形形状。如图9所示,基板110以z方向为厚度方向而配置于壳体2内。基板110与第1主壁13及第2主壁15平行地配置。基板110通过螺钉等而固定于基体11。基板110具备第1面110a和第2面110b。第1面110a是与第1主壁13相面对的面。第2面110b位于与第1面110a相反的一侧。第2面110b是与散热模块120相面对的面。

[0119]

如图10所示,控制器31在基板110的第1面110a上相对于基板110的中央部安装于-x侧。多个dram32a在第1面110a上在x方向上隔开间隔而排列。相对于基板110的中央部位于-y侧(参照图11)。多个dram32b在第2面110b上在x方向上隔开间隔而排列。

[0120]

多个nand33a在第1面110a上在x方向及y方向上隔开间隔而排列。多个nand33b在第2面110b上在x方向及y方向上隔开间隔而排列。多个nand33b是“第1电子部件”的一例。

[0121]

图11是基板模块101的俯视图。如图11所示,多个电容器43在基板110的第2面110b的外周部分处在x方向及y方向上排列。各电容器43的一部分在从z方向观察时与nand33b互相重叠。

[0122]

散热模块120是散热构件。散热模块120具有将例如在基板模块101中产生的热的一部分散发的功能。如图9所示,散热模块120具备多个内板50和多个连接部51。例如,多个内板50包括在z方向上隔开间隔而配置的3张内板50。在各内板50的+x侧的端部形成有退避部121。退避部121是用于避免内板50与电容器43的干涉的缺口部。换言之,各内板50的一部分与电容器43的-x侧的端部相比位于+x侧。各连接部51具备紧固连结部71及缓冲部72。多个连接部51在x方向及y方向上隔开间隔而排列。连接部51经由缓冲部72而与dram32b、nand33b及基板110相接。

[0123]

在本实施方式的半导体存储装置100中,基板模块101在壳体2内仅容纳有1个。由此,容易在壳体2内确保散热模块的配置空间。因而,能够谋求散热性的进一步提高。

[0124]

根据以上说明的至少一个实施方式,具有壳体、第1基板模块、多个散热板及1个以上的连接部。第1基板模块包括第1基板和1个以上的第1电子部件。第1基板模块容纳于壳体内。多个散热板在壳体内在第1基板的厚度方向上与第1基板模块相面对的位置沿厚度方向配置多个。1个以上的连接部与第1基板模块及多个散热板相接。根据该结构,能够谋求散热

性的提高。

[0125]

实施方式是例示,发明的范围不限定于它们。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1