三相全桥封装芯片的制作方法

1.本发明实施例涉及芯片封装技术领域,尤其涉及一种三相全桥封装芯片。

背景技术:

2.目前全桥的金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)功率模块,均是采用6个mosfet单管或3个半桥封装的mosfet单管(每一mosfet单管内部封装有2个mosfet晶粒)在水泵或电机控制板上进行组合,实现产生三相工作电压应用于泵或电机。通过采用6个mosfet单管或3个半桥封装的mosfet单管进行组合的功率模块不仅需要对各个mosfet单管固定在水泵或电机控制板上,还需要对各个mosfet单管进行线路连接,在该过程中会导致全桥的金属氧化物半导体场效应晶体管功率模块体积过大,集成度低并且线路复杂。

技术实现要素:

3.本发明实施例提供一种三相全桥封装芯片,以减小全桥的功率模块设计体积,简化全桥的功率模块线路连接,实现高度集成的三相全桥封装芯片。

4.第一方面,本发明实施例提供了一种三相全桥封装芯片,其包括基底、三个第一功率晶粒和三个第二功率晶粒;三个第一功率晶粒构成三相全桥的上桥臂,三个第二功率晶粒构成三相全桥的下桥臂;

5.基底包括第一基岛区、第二基岛区和拉筋区;拉筋区围绕第一基岛区、以及围绕第二基岛区;三个第一功率晶粒均设置于第一基岛区,每一第二功率晶粒设置于每一第二基岛区;三个第一功率晶粒分别对应与一个第二功率晶粒连接。

6.可选地,一个第一功率晶粒和一个第二功率晶粒构成三相全桥的一个桥臂;第一功率晶粒和第二功率晶粒均包括第一极、第二极和栅极;

7.第一功率晶粒的第一极与电源连接,第一功率晶粒和第二功率晶粒的栅极均接入控制信号,第一功率晶粒的第二极与第二功率晶粒的第一极连接,第二功率晶粒的第二极接地。

8.可选地,第一基岛区包括首尾相连的第一边缘、第二边缘、第三边缘和第四边缘,第二基岛区包括首尾相连的第五边缘、第六边缘、第七边缘和第八边缘;第一边缘与第七边缘平行且相邻设置;

9.拉筋区包括第一图案化结构、第二图案化结构以及第三图案化结构;

10.第一图案化结构设置于第一基岛区的第三边缘的外侧;第二图案化结构置于第一边缘和第七边缘之间;第三图案化结构设置于第二边缘的外侧,或者第三图案化结构设置于第四边缘的外侧。

11.可选地,第一图案化结构远离第三边缘的一侧设置有第一凹陷区;

12.三相全桥封装芯片还包括第一焊盘,第一焊盘设置于第一凹陷区内。

13.可选地,三个第二基岛区相邻设置;

14.拉筋区还包括第四图案化结构、第五图案化结构以及第六图案化结构;

15.第四图案化结构的一部分设置于相邻的第二基岛区的第六边缘和第八边缘之间,第四图案化结构的另一部分设置于处于外侧的第二基岛区的第七边缘和第二图案化结构之间;第五图案化结构设置于第二基岛区的第五边缘的外侧;第六图案化结构设置于处于外侧的第二基岛区的第六边缘的外侧,或者第六图案化结构设置于处于外侧的第二基岛区的第八边缘的外侧。

16.可选地,第五图案化结构远离第五边缘的一侧设置有第二凹陷区;

17.三相全桥封装芯片还包括第二焊盘和第三焊盘,第二焊盘和第三焊盘设置于第二凹陷区内。

18.可选地,一个第一功率晶粒和一个第二功率晶粒构成三相全桥的一个桥臂;第一功率晶粒和第二功率晶粒均包括第一极、第二极和栅极;

19.第一功率晶粒的第一极与第一基岛区连接,第一功率晶粒的栅极与一第一焊盘连接,第一功率晶粒的第二极与一第二基岛区连接,第二功率晶粒的第一极与第二基岛区连接,第二功率晶粒的第二极与一第二焊盘连接,第二功率晶粒的栅极与一第三焊盘连接;第一基岛区与电源连接,第一焊盘和第三焊盘与控制信号接口连接,第二焊盘接地。

20.可选地,三相全桥封装芯片还包括封装层;

21.封装层封装基底上除第一基岛区、第二基岛区、第一焊盘、第二焊盘以及第三焊盘的所有部分。

22.可选地,三相全桥封装芯片还包括过渡区,过渡区位于拉筋区之间、拉筋区和第一基岛区之间以及拉筋区和第二基岛区之间;基底对应过渡区的厚度小于基底对应第一基岛区的厚度,以及基底对应过渡区的厚度小于基底对应第二基岛区的厚度。

23.可选地,基底对应拉筋区内的区域镂空。

24.本实施例的技术方案,通过利用基底、第一功率晶粒和第二功率晶粒设计的三相全桥封装芯片可以减小全桥的功率模块的设计体积,利用基底设计固定承载第一功率晶粒和第二功率晶粒的线路框架替代部分全桥的功率模块的连接线路,简化了全桥的功率模块的线路连接,实现高度集成的三相全桥封装芯片的无外延引脚的封装设计。

附图说明

25.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图做一简单地介绍,显而易见地,下面描述中的附图虽然是本发明的一些具体的实施例,对于本领域的技术人员来说,可以根据本发明的各种实施例所揭示和提示的器件结构,驱动方法和制造方法的基本概念,拓展和延伸到其它的结构和附图,毋庸置疑这些都应该是在本发明的权利要求范围之内。

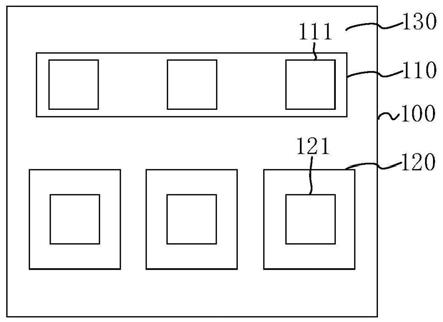

26.图1为本发明实施例提供的一种三相全桥封装芯片内部的结构示意图;

27.图2为本发明实施例提供的一种三相全桥封装芯片等效电路的结构示意图;

28.图3为本发明实施例提供的另一种三相全桥封装芯片内部的结构示意图;

29.图4为本发明实施例提供的另一种三相全桥封装芯片内部的结构示意图;

30.图5为本发明实施例提供的另一种三相全桥封装芯片内部的结构示意图。

具体实施方式

31.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

32.本发明实施例提供了一种三相全桥封装芯片,图1为本发明实施例提供的一种三相全桥封装芯片内部的结构示意图。如图1所示,三相全桥封装芯片包括基底100、三个第一功率晶粒111和三个第二功率晶粒121;三个第一功率晶粒111构成三相全桥的上桥臂,三个第二功率晶粒121构成三相全桥的下桥臂;基底100包括第一基岛区110、第二基岛区120和拉筋区130;拉筋区130围绕第一基岛区110、以及围绕第二基岛区120;三个第一功率晶粒111均设置于第一基岛区110,每一第二功率晶粒121设置于每一第二基岛区120;三个第一功率晶粒111分别对应与一个第二功率晶粒121连接。

33.具体地,三相全桥封装芯片可以将直流电转化成三相的交流电。三个第一功率晶粒111和三个第二功率晶粒121为三相全桥封装芯片的控制核心,基底100为三个第一功率晶粒111和三个第二功率晶粒121进行电路连接的载体,实现第一功率晶粒111和第二功率晶粒121的电气连接,还可以起到固定第一功率晶粒111和第二功率晶粒121以及与外部装置连接的桥梁作用。

34.另外,三个第一功率晶粒111均设置在第一基岛区110上,并且第一功率晶粒111与第一基岛区110电连接,也就是第一功率晶粒111可以通过与第一基岛区110的连接实现信号的传输。三个第二功率晶粒121分别设置在每一第二基岛区120上,并且第二功率晶粒121与第二基岛区120电连接,也就是第二功率晶粒121可以通过与第二基岛区120的连接实现信号的传输。拉筋区130可以固定连接所述基底100上设置的其他区域,从而提高其他区域的稳定性。例如拉筋区130用于固定基底100上设置的第一基岛区110和第二基岛区120,对此拉筋区130围绕第一基岛区110和第二基岛区120设置。

35.综上,本方案通过利用基底100、第一功率晶粒111和第二功率晶粒121设计的三相全桥封装芯片可以减小全桥的功率模块的设计体积,利用基底100设计固定承载第一功率晶粒111和第二功率晶粒121的线路框架替代部分全桥的功率模块的连接线路,简化了全桥的功率模块的线路连接,实现高度集成的三相全桥封装芯片的无外延引脚的封装设计。

36.图2为本发明实施例提供的一种三相全桥封装芯片等效电路的结构示意图。如图2所示,一个第一功率晶粒111和一个第二功率晶粒121构成三相全桥的一个桥臂101;第一功率晶粒111和第二功率晶粒121均包括第一极d、第二极s和栅极g;第一功率晶粒111的第一极d与电源vcc连接,第一功率晶粒111和第二功率晶粒121的栅极g均接入控制信号,第一功率晶粒111的第二极s与第二功率晶粒121的第一极d连接,第二功率晶粒121的第二极s接地gnd。

37.其中,第一功率晶粒111和第二功率晶粒121可以为金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)。三相全桥封装芯片的每一相的输出电流是在三相全桥的上桥臂和三相全桥的下桥臂共同控制下输出的。其中,三相全桥封装芯片的上桥臂由共阳极的三个第一功率晶粒111构成,其在电源正半周导通,并输出的正向电流。三相全桥封装芯片的下桥臂由共阴极的三个第二功率晶粒121构

成,其在电源负半周导通,并输出的是反向电流。三个第一功率晶粒111分别对应与一个第二功率晶粒121连接,从而实现一组共阴极的第二功率晶粒121与一组共阳极的第一功率晶粒111的串联,实现将直流电转化成三相的交流电。一个第一功率晶粒111和一个第二功率晶粒121构成三相全桥的一个桥臂101,可以从每一桥臂101中第一功率晶粒111与第二功率晶粒121的连接处分别引出a相电压、b相电压以及c相电压。

38.图3为本发明实施例提供的另一种三相全桥封装芯片内部的结构示意图,如图3所示,第一基岛区包括首尾相连的第一边缘001、第二边缘002、第三边缘003和第四边缘004,第二基岛区包括首尾相连的第五边缘005、第六边缘006、第七边缘007和第八边缘008;第一边缘001与第七边缘007平行且相邻设置;拉筋区包括第一图案化结构131、第二图案化结构132以及第三图案化结构133;第一图案化结构131设置于第一基岛区的第三边缘003的外侧;第二图案化结构132置于第一边缘001和第七边缘007之间;第三图案化结构133设置于第二边缘002的外侧,或者第三图案化结构133设置于第四边缘004的外侧。

39.具体地,第一基岛区是由第一边缘001、第二边缘002、第三边缘003和第四边缘004依次首尾相接构成的四边形,例如矩形结构的第一基岛区。第二基岛区是由第五边缘005、第六边缘006、第七边缘007和第八边缘008依次首尾相接构成的四边形,例如矩形结构的第二基岛区。第一基岛区用于对应设置三个功率晶粒,第二基岛区用于对应设置一个功率晶粒,并且第一基岛区上的每一第一功率晶粒111与第二基岛上设置的每一第二功率晶粒121对应连接,第一基岛区的第一边缘001与第二基岛区的第七边缘007平行且相邻设置,由此便于第一基岛区和第二基岛区上设置的第一功率晶粒111和第二功率晶粒121的连接。围绕第一基岛区设置的拉筋区包括第一图案化结构131、第二图案化结构132以及第三图案化结构133。其中,第一图案化结构131、第二图案化结构132以及第三图案化结构133与第一基岛区在基底上设置的具体位置关系为:第一图案化结构131设置于第一基岛区110的第三边缘003的外侧;第二图案化结构132置于第一边缘001和第七边缘007之间;第三图案化结构133设置于第二边缘002的外侧,或者第三图案化结构133设置于第四边缘004的外侧。由此第一图案化结构131、第二图案化结构132以及第三图案化结构133围绕第一基岛区,实现了对第一基岛区的稳定固定。

40.继续参考图3,可选地,第一图案化结构131远离第三边缘003的一侧设置有第一凹陷区1311;三相全桥封装芯片还包括第一焊盘,第一焊盘设置于第一凹陷区内1311。

41.具体地,三相全桥封装芯片的基底上还设置有第一凹陷区1311,并且第一凹陷区1311内还设置有第一焊盘。其中,第一焊盘用于与第一基岛区上设置的第一功率晶粒111电连接,作为第一基岛区上设置的第一功率晶粒111与外部装置进行信号传输的桥梁。第一凹陷区1311设置于第一图案化结构131远离第三边缘003的一侧,由此第一图案化结构131便于稳定固定第一焊盘,并且第一图案化结构131也保证了第一焊盘和第一基岛区的稳定连接。需要注意的是:基底对应第一图案化结构131的厚度小于基底对应第一凹陷区1311对应设置的第一焊盘的厚度。

42.继续参考图3,可选地,三个第二基岛区相邻设置;拉筋区还包括第四图案化结构134、第五图案化结构135以及第六图案化结构136;第四图案化结构134的一部分设置于相邻的第二基岛区的第六边缘006和第八边缘008之间,第四图案化结构134的另一部分设置于处于外侧的第二基岛区的第七边缘007和第第二图案化结构132之间;第五图案化结构

135设置于第二基岛区的第五边缘005的外侧;第六图案化结构136设置于处于外侧的第二基岛区的第六边缘006的外侧,或者第六图案化结构136设置于处于外侧的第二基岛区的第八边缘008的外侧。

43.具体地,三相全桥封装芯片的基底上设置有三个相邻的第二基岛区,并且每一第二基岛区的第七边缘007与第一基岛区的第一边缘001平行且相邻,由此可见第二基岛区设置于第一基岛区的第一边缘001外侧。拉筋区还包括第四图案化结构134、第五图案化结构135以及第六图案化结构136。围绕第二基岛区设置的拉筋区包括第二图案化结构132、第四图案化结构134、第五图案化结构135以及第六图案化结构136。其中,第二图案化结构132、第四图案化结构134、第五图案化结构135以及第六图案化结构136与第二基岛区在基底上设置的具体位置关系为:第二图案化结构132设置于三个第二基岛区的第七边缘007的外侧,第四图案化结构134的一部分设置于相邻的第二基岛区的第六边缘006和第八边缘008之间,第四图案化134结构的另一部分设置于处于外侧的第二基岛区的第七边缘007和第二图案化结构132之间;第五图案化结构135设置于第二基岛区的第五边缘005的外侧;第六图案化结构136设置于处于外侧的第二基岛区的第六边缘006的外侧,或者第六图案化结构136设置于处于外侧的第二基岛区的第八边缘008的外侧。由此第二图案化结构132、第四图案化结构134、第五图案化结构135以及第六图案化结构136围绕第二基岛区,实现了对第二基岛区的稳定固定。

44.继续参考图3,可选地,第五图案化结构135远离第五边缘005的一侧设置有第二凹陷区1351;三相全桥封装芯片还包括第二焊盘和第三焊盘,第二焊盘和第三焊盘设置于第二凹陷区1351内。

45.具体地,三相全桥封装芯片的基底上还设置有第二凹陷区1351,并且第二凹陷区1351内还设置有第二焊盘和第三焊盘。其中,第二焊盘和第三焊盘用于与第二基岛区上设置的第二功率晶粒121电连接,作为第二基岛区上设置的第二功率晶粒121与外部装置进行信号传输的桥梁。第二凹陷区1351设置于第五图案化结构135远离第五边缘005的一侧,由此第五图案化结构135便于稳定固定第二焊盘和第三焊盘,并且第五图案化结构135也保证了第二焊盘、第三焊盘和第二基岛区的稳定连接。需要注意的是:基底对应第五图案化结构135的厚度小于基底对应第一凹陷区1311对应设置的第二焊盘和第三焊盘的厚度。

46.图4为本发明实施例提供的另一种三相全桥封装芯片内部的结构示意图,如图4所示,一个第一功率晶粒111和一个第二功率晶粒121构成三相全桥的一个桥臂;第一功率晶粒111和第二功率晶粒121均包括第一极d、第二极s和栅极g;第一功率晶粒111的第一极d与第一基岛区110连接,第一功率晶粒111的栅极g与一第一焊盘140连接,第一功率晶粒111的第二极s与一第二基岛区120连接,第二功率晶粒121的第一极d与第二基岛区120连接,第二功率晶粒121的第二极s与一第二焊盘150连接,第二功率晶粒121的栅极g与一第三焊盘160连接;第一基岛区110与电源连接,第一焊盘140和第三焊盘160与控制信号接口连接,第二焊盘150接地。

47.具体地,一个第一功率晶粒111和一个第二功率晶粒121构成三相全桥的一个桥臂100,可以从每一桥臂的第一功率晶粒111与第二功率晶粒121的连接处分别引出a相电压、b相电压以及c相电压。如图4所示,第一功率晶粒111和第二功率晶粒121采用金属氧化物半导体晶粒,其中金属氧化物半导体晶粒的第一面(底面)为第一极d,第二面(正面)为第二极

s,在金属氧化物半导体晶粒第二面的方形区域为栅极g。第一功率晶粒111的第一极d与第一基岛区110连接,可以将第一功率晶粒111的第一极d焊接在第一基岛区110上。第一功率晶粒111的栅极g与一第一焊盘140连接,可以将铜线或金线的一端与第一功率晶粒111的栅极g焊接,将铜线或金线的另一端与第一焊盘140焊接。第一功率晶粒111的第二极s与一第二基岛区120连接,可以将铜片或铝带的一端与第二模块的第一极d焊接,将铜片或铝带的一端与第二基岛区120连接。第二功率晶粒121的第一极d与第二基岛区120连接,可以将第二功率晶粒121的第一极d焊接在第二基岛区120上。第二功率晶粒121的第二极s与一第二焊盘150连接,可以将铜线或金线的一端与第二功率晶粒121的第二极s焊接,将铜线或金线的另一端与第二焊盘150焊接。第二功率晶粒121的栅极g与一第三焊盘160连接,可以将铜线或金线的一端与第二功率晶粒121的栅极g焊接,将铜线或金线的另一端与第三焊盘160焊接。此外,第一基岛区110与电源连接,第一焊盘140和第三焊盘160与控制信号接口连接,第二焊盘150接地。

48.根据以上连接关系可知,第一功率晶粒111的第一极d可以通过第一基岛区110与电源连接,第一功率晶粒111的栅极g可以通过第一焊盘140与控制信号接口连接,第二功率晶粒121的栅极g可以通过第三焊盘160与控制信号接口连接,第一功率晶粒111的第二极s通过第二基岛区120与第二功率晶粒121的第一极d连接,第二功率晶粒121的第二极s通过第二焊盘150接地gnd。

49.可选地,三相全桥封装芯片还包括封装层;封装层封装基底上除第一基岛区、第二基岛区、第一焊盘、第二焊盘以及第三焊盘的所有部分。

50.其中,封装层可以采用环氧树脂,环氧树脂具有优良的耐化学性、强附着力、较好的耐热性以及电绝缘性。由此采用环氧树脂作为封装层,封装除第一基岛区、第二基岛区、第一焊盘、第二焊盘以及第三焊盘的所有部分,可以很好地保护封装层所包裹的部位。由于第一基岛区和第二基岛区上分别需要设置第一功率晶粒和第二功率晶粒,且第一功率晶粒和第二功率晶粒需要与外部接口进行接触电连接,由此封装层不需要包裹第一基岛区和第二基岛区。同理,第一焊盘作为第一基岛区上设置的第一功率晶粒与外部装置进行信号传输的桥梁,第二焊盘和第三焊盘作为第二基岛区上设置的第二功率晶粒与外部装置进行信号传输的桥梁,需要与外部接口进行接触电连接,由此封装层不需要包裹第一焊盘、第二焊盘和第三焊盘。此外,由于拉筋区的厚度小于第一基岛区、第二基岛区、第一焊盘、第二焊盘以及第三焊盘,利用封装层封装拉筋区可以减小拉筋区的应力,并通过封装层实现拉筋区的应力释放。

51.可选地,三相全桥封装芯片还包括过渡区,过渡区位于拉筋区之间、拉筋区和第一基岛区之间以及拉筋区和第二基岛区之间;基底对应过渡区的厚度小于基底对应第一基岛区的厚度,以及基底对应过渡区的厚度小于基底对应第二基岛区的厚度。

52.其中,过渡区的具体作用为:连接第一基岛区、第二基岛和拉筋区。例如将过渡区设置于拉筋区和拉筋区之间、拉筋区和第一基岛区之间以及拉筋区和第二基岛区之间。为了不影响后期对第一基岛区和第二基岛区所承载的功率晶粒的布线设置(主要防止引线与过渡区的接触短路),将过渡区设置于拉筋区之间、拉筋区和第一基岛区之间以及拉筋区和第二基岛区之间,并且设置基底对应过渡区的厚度小于基底对应第一基岛区的厚度,以及基底对应过渡区的厚度小于基底对应第二基岛区的厚度。示例性的,过渡区的厚度为0.1mm

±

0.01mm,第一基岛区和第二基岛区的厚度为0.2mm。基底上设置过渡区可以采用半刻蚀工艺,将过渡区的厚度刻蚀到0.1mm

±

0.01mm。

53.图5为本发明实施例提供的另一种三相全桥封装芯片内部的结构示意图,如图5所示,基底对应拉筋区内的区域镂空。

54.其中,基底对应拉筋区内的区域镂空(阴影区域镂空)。示例性的,第一图案化结构131、第二图案化结构132、第三图案化结构133、第四图案化结构134、第五图案化结构135以及第六图案化结构136的内部区域镂空。其中,基底对应拉筋区内的区域镂空设置,可以采用刻蚀工艺,将拉筋区内部区域刻蚀掉。由此拉筋区的边框可以固定连接所述基底上设置的其他区域,从而提高其他区域的稳定性。此外,将拉筋区内部区域镂空,是在保证正常的电气隔离基础上去掉了不必要的区域,并且保留的基底面积可达整个芯片框架的70%以上,保证了整个芯片框架的快速散热。

55.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1