一种设置有台阶腔体的芯片堆叠封装结构及其制作方法与流程

1.本发明属于芯片堆叠技术领域,尤其涉及阶梯塑封结构的存储类产品封装,具体涉及一种设置有台阶腔体的芯片堆叠封装结构及其制作方法。

背景技术:

2.随着消费类电子产品的发展,高频率、大容量、多功能性和高可靠性存储器设备的需求日益增长。现有的多芯片堆叠封装通常是由多条焊线使芯片通过基板线路进行电性连接,这种封装结构造成封装体厚度大,焊线细长而使电性达不到预想需求。因此,如何降低封装体厚度,提升封装可靠性及减小电性损失,是目前急需解决的一大难题。

技术实现要素:

3.本发明的目的在于克服上述现有技术的缺点,提供一种设置有台阶腔体的芯片堆叠封装结构及其制作方法,以解决现有技术中芯片难以降低封装体厚度,电性损失大的问题。

4.为达到上述目的,本发明采用以下技术方案予以实现:

5.一种设置有台阶腔体的芯片堆叠封装结构,包括底层板,所述底层板上堆叠设置有若干层上层板;所述上层板围绕底层板的周向设置,每一侧所有上层板的外侧壁与底层板的外侧壁对齐;上层板的内侧壁形成台阶,从上到下,上层板的内侧壁逐渐向底层板的中间部分靠近;

6.沿着台阶,所述底层板和上层板上铺设有金属线路,每一个上层板的金属线路上设置有基板焊接点,所述底层板上的金属线路上设置有基板焊接点;所述基板焊接点的下端面连接有金属柱;

7.所述底层板和上层板上依次堆叠有芯片,每一个芯片的下表面设置有芯片焊接点,每一个芯片的芯片焊接点和一个基板焊接点电性连接,所述基板焊接点设置在所述芯片下层的上层板或底层板上。

8.本发明的进一步改进在于:

9.优选的,所述芯片的上表面设置有粘着层。

10.优选的,所述芯片、底层板和上层板上设置有塑封体。

11.优选的,所述底层板的下部设置有锡球

12.优选的,所述金属线路的材质为铜线。

13.优选的,所述芯片和其下部的底层板或上层板为焊接连接。

14.一种上述设置有台阶腔体的芯片堆叠封装结构的制作方法,包括以下步骤:

15.步骤1,制备基板,所述基板包括底层板,所述底层板上堆叠设置有若干层上层板,在底层板和上层板上铺设有金属线路,每一个上层板的金属线路上设置基板焊接点,底层板上的金属线路上设置基板焊接点;

16.步骤2,将待连接芯片的芯片焊接点朝下,一层一层的堆叠倒装焊接到底层板或上

层板上,芯片焊接点和基板焊接点电性连接。

17.优选的,步骤2后,通过塑封料对底层板、上层板和芯片塑封,形成塑封体。

18.优选的,塑封后,在底层板的底面植入锡球。

19.优选的,上下相邻的芯片之间粘结连接。

20.与现有技术相比,本发明具有以下有益效果:

21.本发明公开了一种设置有台阶腔体的芯片堆叠封装结构,该封装结构包括底层板,在底层板上设置有上层板,底层板和上层板同属于基板,在底层板和上层板上设置有金属线路,作为传递信号,实现电连接的载体,在金属线路上焊接芯片,使得芯片之间能够通过金属线路实现信号的传递。本发明的改进之处是通过台阶结构的载板设计方法可以不通过wb工艺对芯片进行堆叠,通过内部线路可有效降低电性损耗,同时芯片贴装在载板腔体内,可以降低封装体厚度。满足市场小型化和薄型化的需求。本发明通过台阶腔体结构载板预留承载芯片空间,方便后期灵活根据需求选取适当数量存储芯片进行焊接扩容,电性损失小,减少了整体厚度。

22.本发明还公开一种设置有台阶腔体的芯片堆叠封装结构的制作方法,该制作方法在基板上直接铺设金属连接线路,使得金属线路能够起到传递信号和电连接的作用。该制备方法简单,易于推广。

附图说明

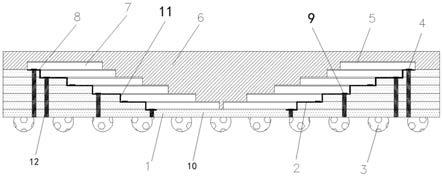

23.图1为发明的结构示意图;

24.图2为本发明的步骤1的结构示意图;

25.图3为本发明的步骤2的结构示意图;

26.图4为本发明的步骤3的结构示意图;

27.图5为本发明的步骤4的结构示意图。

28.图中,1为基板;2为金属线路;3为锡球;4为基板焊接点;5为粘着层;6为塑封体;7为芯片;8

‑

上层板;9

‑

芯片焊接点;10

‑

底层板;11

‑

台阶;12

‑

金属柱。

具体实施方式

29.下面结合附图对本发明做进一步详细描述:

30.在本发明的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制;术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性;此外,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

31.本发明提供一种台阶腔体结构载板制造方法,封装结构包括基板1,塑封体6,芯片7的堆叠体和导电结构。芯片置于重布线路结构上且与重布线结构进行电性连接。载板制作为腔体台阶结构,同时载板台阶结构位置预留焊点,预留焊点和芯片7倒装焊接。

32.具体的,基板1包括底层板10和若干个上层板8,上层板8堆叠的设置在底层板10上,所述上层板8围绕基板1的周向设置,因此上层板8形成环状的上层板8。

33.基板1为四边形,相对应的上层板8也形成四边形的上层板8,每一侧的所有上层板8的外侧壁与底层板10的外侧壁对齐,上层板8的内侧壁形成台阶11,从上到下,上层板8的内侧壁逐渐向底层板10的中间部分靠近,因此,四边形的上层板8中间形成腔体,该腔体的截面积从上到下逐渐缩小。

34.沿着台阶11,所述底层板10的上表面和上层板8的上表面上铺设有金属线路2,金属线路2的材质为铜线,每一个上层板8的金属线路2上设置有基板焊接点4,部分的基板焊接点4通过金属柱12连接至底层板10的底部,金属柱12在基板1内部过孔,起到连接不同层的金属线路2的关系,进行金属线路2之间电信号连接和传输,每一个金属柱12的上端设置有一个基板焊接点4,底层板10上的金属线路2上也设置有基板焊接点4。每一个基板焊接点4的底部都连接有一个金属柱12,金属柱12的下端和底层板10的底部平齐。

35.所述底层板10和上层板8上依次堆叠有芯片7,芯片7和其下层的底层板10或上层板8为焊接连接,每一个芯片7的下表面设置有芯片焊接点9,每一个芯片7的芯片焊接点9均和其下部的基板1的基板焊接点4电性连接,使得芯片7之间能够通过芯片焊接点9,基板焊接点4和金属线路2实现电性连接。芯片7之间的信号通过芯片焊接点9和基板焊接点4之间的连接,使得芯片7的信号能够传递至基板焊接点4,基板焊接点4上的电信号通过金属柱12传递至不同层的金属线路2上,进而通过当层的金属线路2、基板焊接点4和芯片焊接点9传递至不同的芯片7上,同时通过金属柱12传递至底部的锡球3,同时能向外传递电信号。

36.芯片7的上表面设置有粘着层5,使得上下相邻的芯片7之间通过粘着层5进行粘结连接,便于芯片7的堆叠设置。

37.整个腔体被塑封料填充,即芯片7、底层板10和上层板8上设置有塑封体6,形成塑封结构。

38.上述结构的制作方法具体包括以下步骤:

39.步骤1,参见图2,通过多层叠压的方法,制作一个台阶腔体结构基板1,该基板1与普通基板的区别为:普通基板为多层平板结构,本发明的基板1为多层台阶的腔体结构,具体的,基板1的四周为台阶11,基板1四周的高度高于基板1中间的高度,基板1的中间部位只有一层;每一台阶11的上表面设置金属线路2,所述金属线路2为铜材,通过蚀刻曝光等方式在基板1以及台阶的的上表面形成,相邻的台阶11之间通过金属线路2连接,优选的,金属线路2从上到下为连续的金属线路2,方便金属线路2的铺设,每一层台阶11在其上表面均设置有焊接点4。优选的,所述金属线路2中的金属为铜线。

40.步骤2,参见图3,将需要互连的芯片7焊接点朝下,一层一层的堆叠倒装焊接到腔体结构基板1的台阶11上,每一层的芯片7的芯片焊接点9焊接到其下一层基板1的基板焊接点4上,同时通过基板1的金属线路2完成各个芯片7之间的互连,每一个芯片7的上表面设置有粘着层5。

41.步骤3,参见图4,芯片7堆叠焊接完成后,使用塑封料完成产品的包封,形成塑封体6。

42.步骤4,参见图5,在基板1的底部完成锡球3的植入,整个塑封结构制作完成。

43.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精

神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1