引线框架、半导体装置以及引线框架的制造方法与流程

1.本发明涉及引线框架、半导体装置以及引线框架的制造方法。

背景技术:

2.近年来,已知有一种半导体装置,其中,将例如ic(integrated circuit,集成电路)芯片等半导体元件,搭载于由金属制作的引线框架。即,例如,将半导体元件搭载在设于引线框架中央的面状芯片垫上,并将该半导体元件,例如通过引线键合(wire bonding)与设于芯片垫周围的多条引脚连接。然后,有时对搭载于引线框架的半导体元件,例如使用环氧树脂等合成树脂进行封装,由此形成半导体装置。

3.在这种半导体装置中,一般来说,例如使用焊料或贴片膏等来将半导体元件接合到芯片垫。焊料或贴片膏等接合材料有可能流出至芯片垫上的半导体元件接合区域的周围,对此,以往有在接合区域的周围形成沟槽以防止接合材料流出等方案。

4.专利文献1:日本特开2014-203861号公报

5.专利文献2:日本特开2013-058542号公报

技术实现要素:

6.然而,如果要防止接合材料的流出,则存在引线框架的形成工序复杂化的问题。即,例如,如上所述在接合区域的周围形成沟槽时,在形成引线框架的芯片垫后,进行芯片垫上形成沟槽的加工,使得形成引线框架的工序数增加。另一方面,如果不设置用于防止接合材料流出的结构,则接合材料有可能流出至芯片垫的周围,阻碍半导体元件的引线键合,导致半导体装置的可靠性降低。

7.本发明公开的技术是鉴于上述问题而完成的,其目的在于提供一种能够防止接合材料的流出,同时避免形成工序复杂化的引线框架、半导体装置以及引线框架的制造方法。

8.本技术公开的引线框架,在一个形态中,包括:芯片垫,其具有用于搭载半导体元件的搭载面;凹部,其设于所述搭载面;以及引脚,其配置于所述芯片垫的周围,所述凹部包括:底面,其位于从所述凹部的开口面起深度小于所述芯片垫的厚度的位置;多个突起部,其从所述底面突起;以及凹陷部,其从所述底面凹陷。

9.根据本技术所公开的引线框架、半导体装置以及引线框架的制造方法的一个形态,能够获得防止接合材料的流出、同时避免形成工序复杂化的效果。

附图说明

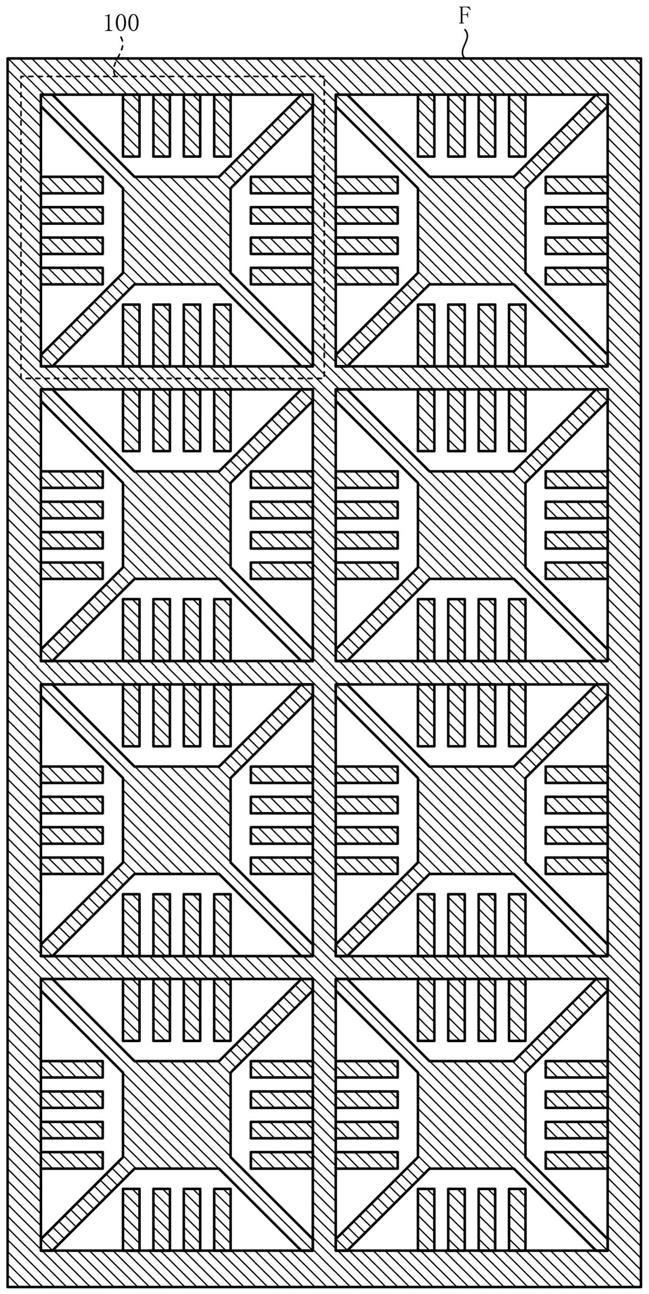

10.图1是表示一实施方式涉及的引线框架集合体的具体示例的图。

11.图2(a)和图2(b)是表示一实施方式涉及的引线框架的结构的图。

12.图3是表示引线框架的制造方法的流程图。

13.图4是表示dfr层压工序的具体示例的图。

14.图5是表示曝光工序的具体示例的图。

15.图6是表示显影工序的具体示例的图。

16.图7是表示蚀刻工序的具体示例的图。

17.图8是表示dfr剥离工序的具体示例的图。

18.图9是表示芯片垫的结构的具体示例的俯视图。

19.图10是表示芯片垫的结构的其他具体示例的俯视图。

20.图11(a)和图11(b)是表示芯片垫的结构的其他具体示例的图。

21.图12(a)和图12(b)是表示芯片垫的结构的其他具体示例的图。

22.图13是表示防镀剂涂敷工序的具体示例的图。

23.图14是表示曝光工序的具体示例的图。

24.图15是表示显影工序的具体示例的图。

25.图16是表示电镀工序的具体示例的图。

26.图17是表示防镀剂剥离工序的具体示例的图。

27.图18是用于说明半导体元件的搭载的图。

28.图19是用于说明引线键合的图。

29.图20是用于说明模塑的图。

30.图21是表示半导体装置的结构的图。

31.符号说明

32.110:引脚、111:镀层、120:芯片垫、121:凹部、121a:底面、122:突起部、123:凹陷部、124:凸缘部、130:连结部、200:金属板、210:dfr、220:防镀剂、230:接合材料、240:半导体元件、250:引线、260:封装用树脂。

具体实施方式

33.下面,参照附图对本技术所公开的引线框架、半导体装置以及引线框架的制造方法的一实施方式进行详细说明。另外,本发明不限于该实施方式。

34.图1是表示一实施方式涉及的引线框架100的集合体的具体示例的图。如图1所示,引线框架100被制造成集合体,由框体f包围的区域内连结有多个引线框架100。在图1所示的示例中,例如,以铜或铜合金金属板为材料,并进行蚀刻和电镀等,从而制造出连结成四行两列的八个引线框架100。

35.通过这样制造多个引线框架100的集合体,能够高效率地制造引线框架100,实现成本降低。将作为集合体制造的多个引线框架100分割成单片,由此获得用于搭载半导体元件等电子部件的引线框架100。分割成单片的各引线框架100的外形呈例如一边为70mm的正方形,厚度为0.1~0.25mm。

36.图2(a)和图2(b)是表示一个引线框架100的结构的图。即,图2(a)为引线框架100的俯视图,图2(b)为图2(a)的x-x线截面图。

37.引线框架100包括:多个引脚110、芯片垫120和连结部130。如图2(a)所示,多个引脚110分别从框体f朝芯片垫120的方向延伸,芯片垫120通过连结部130与框体f连结。此外,如图2(b)所示,引脚110的上表面与芯片垫120的上表面位于同一平面内,引脚110的下表面与芯片垫120的下表面位于同一平面内。也就是说,引脚110与芯片垫120的厚度相同。另外,在使用引线框架100形成半导体装置时,沿图2(a)的虚线切断引线框架100,将引脚110和连

结部130从框体f分离。

38.在将半导体元件等电子部件搭载于引线框架100时,引脚110形成用于将该电子部件与外部部件电气连接的端子。在引线框架100的用于搭载半导体元件的上表面侧,引脚110形成有镀层111。引线框架100上搭载半导体元件时,通过引线键合将半导体元件与镀层111连接。然后,在对搭载于引线框架100的半导体元件利用封装用树脂进行模塑来形成半导体装置后,引脚110的下表面和从框体f切断出的侧面从封装用树脂显露,以形成半导体装置的端子。

39.芯片垫120为形成在引线框架100中央的板状区域,例如通过四个连结部130与框体f连结。在芯片垫120上搭载半导体元件。具体而言,在芯片垫120的中央部形成凹部121,其深度小于芯片垫120的厚度,并在凹部121内搭载半导体元件。凹部121的底面121a位于从凹部121的开口面起深度小于芯片垫120的厚度的位置,该底面121a上设有从底面121a朝上方突起的多个突起部122,并且形成有从底面121a朝下方凹陷的凹陷部123。此外,在形成有凹部121的区域的外侧,形成有朝侧方突出的凸缘部124。

40.突起部122是通过使底面121a的一部分突起至比底面121a浅的位置来形成的。即,突起部122的上端位于底面121a的上方且芯片垫120的上表面的下方。在将半导体元件搭载于凹部121内时,突起部122可提高用于接合半导体元件下表面与底面121a的焊料或贴片膏等接合材料的附着性。即,由于形成突起部122,底面121a变得粗糙,使得接合材料与形成有突起部122的底面121a紧密附着。

41.凹陷部123是通过使底面121a的周缘凹陷至比底面121a深的位置来形成的。即,凹陷部123的底部位于底面121a的下方且芯片垫120的下表面的上方。在将半导体元件搭载于凹部121内时,凹陷部123收纳多余的接合材料,以防止接合材料从凹部121溢出。即,由于形成有凹陷部123,提供到凹部121内的过剩的接合材料流到凹陷部123而被收纳,由此防止接合材料流出至凹部121的外部。

42.凸缘部124是通过使包围凹部121的外周部分的上方部分朝引脚110的方向突出来形成的。在使用封装用树脂对引线框架100和半导体元件进行模塑时,凸缘部124防止引线框架100从封装用树脂脱落。

43.即,由于形成有凸缘部124,可将封装用树脂填充至凸缘部124下方的凹口部分,使引线框架100与封装用树脂的结合强度提高。

44.凹部121、突起部122、凹陷部123和凸缘部124是在通过蚀刻来分离并形成引脚110和芯片垫120时同时形成的。具体而言,在通过蚀刻分离引脚110和芯片垫120时,从芯片垫120的上表面侧进行半蚀刻,由此形成凹部121。同样地,通过从芯片垫120的下表面侧进行半蚀刻,将凸缘部124的下方切除,由此形成凸缘部124。进一步地,在从芯片垫120的上表面侧进行半蚀刻时,利用抗蚀剂保护与突起部122对应的位置,以抑制抗蚀剂部分的蚀刻,由此形成突起部122。并且,通过调整用于形成突起部122的抗蚀剂的密度,在抗蚀剂密度较稀疏的区域形成凹陷部123。对于如上所述的凹部121、突起部122、凹陷部123和凸缘部124的形成方法,将在后文中详细说明。

45.接着,参照图3所示的流程图,对如上构成的引线框架100的制造方法,具体举例说明。以下说明的工序是例如对图1所示的引线框架100的集合体进行的,但在下面,着眼于一个引线框架100来说明各工序的具体示例。

46.首先,对作为材料的金属板等进行清洗等前处理后,在金属板的表面上层压一种蚀刻抗蚀剂、即干膜抗蚀剂(dfr:dry film resist)(步骤s101)。具体而言,例如,如图4所示,在由厚度0.1~0.25mm的铜或铜合金制成金属板200的上表面和下表面上,层压dfr210。

47.然后,按照引线框架100的形状,在dfr210的表面上形成图案掩模,并进行曝光,由此使未形成图案掩模的部分的dfr210固化(步骤s102)。具体而言,例如,如图5所示,对于待形成凹部121的区域211,不使上表面的dfr210固化,而使下表面的dfr210固化。此外,对于待形成凸缘部124的区域212,使上表面的dfr210固化,而不使下表面的dfr210固化。也就是说,对于从金属板200的上表面和下表面的其中一侧表面进行半蚀刻的区域,仅使上表面和下表面的其中一侧表面的dfr210固化,而不使另一侧表面的dfr210固化。

48.相对于此,对于要使引脚110与芯片垫120分离的区域213,不使上表面和下表面这两侧表面的dfr210固化。也就是说,在从金属板200的上表面和下表面这两侧表面进行蚀刻的区域,不使上表面和下表面这两侧表面的dfr210固化。

49.另外,在图5中,用黑色表示dfr210中通过曝光而固化的部分。dfr210中通过曝光而固化的部分成为在显影后残留的残留部。

50.对于待形成凹部121的区域211,不使上表面的dfr210固化,但在与突起部122对应的部分,使dfr210固化。即,区域211的上表面的dfr210中,散布有被固化的残留部。此时,散布的残留部的密度根据区域211内的位置而不同。具体而言,在区域211的中央部211a,残留部的密度较高,而在周缘部211b,残留部的密度较低。换言之,在区域211的中央部211a,每单位面积中残留部所占的面积较大,而在周缘部211b,每单位面积中残留部所占的面积较小。这样,在区域211内,与突起部122对应的dfr210的残留部的密度不均一,存在残留部的密度较高的区域和较低的区域。

51.通过曝光使dfr210固化后,进行dfr210的显影(步骤s103),金属板200的表面仅残留固化后的残留部。即,例如,如图6所示,变成在dfr210的残留部覆盖金属板200的表面、而在残留部以外的部分显露出金属板200的状态。将这样在表面残留有残留部的金属板200浸渍于蚀刻液,进行蚀刻(步骤s104)。具体而言,通过将金属板200浸渍于例如硫酸/过氧化氢系或者过硫酸盐等蚀刻液,金属板200的未由残留部覆盖的表面溶解,成形为引线框架100的形状。

52.即,例如,如图7所示,在未由残留部覆盖的区域213,金属板200从上表面和下表面溶解,使得引脚110与芯片垫120分离。此外,在仅下表面由残留部覆盖的区域211,金属板200从上表面溶解而被半蚀刻,由此形成凹部121。并且,在区域211内分布的残留部的位置,从残留部周围进行蚀刻,由此形成突起部122。也就是说,相比于未由残留部覆盖的部分,在由残留部覆盖的部分上蚀刻得以抑制,由此被蚀刻至比底面121a浅的位置而形成突起部122。进一步地,残留部的密度不均一,在区域211的周缘部211b,残留部较为稀疏,促进该部分的蚀刻,由此被蚀刻至比底面121a深的位置而形成凹陷部123。并且,在仅上表面由残留部覆盖的区域212,金属板200从下表面溶解而被半蚀刻,由此形成凸缘部124。

53.如上所述,通过蚀刻,使引脚110与芯片垫120分离的同时,在芯片垫120上形成凹部121和凸缘部124。并且,在凹部121内,根据dfr210的残留部的密度,进行分别不同的深度的蚀刻,同时形成从凹部121的开口面起的深度与底面121a不同的突起部122和凹陷部123。

54.蚀刻完毕后,例如使用胺类或非胺类剥离液,将dfr210剥离(步骤s105),可得到具

有引脚110和芯片垫120的引线框架100。即,例如,如图8所示,可得到引脚110与芯片垫120分离,并且在芯片垫120上形成有凹部121和凸缘部124的引线框架100。凹部121内的底面121a上,形成有突起部122和凹陷部123。

55.在金属板200的厚度例如为0.2mm(200μm)的情况下,从芯片垫120的最上表面(即,凹部121的开口面)到底面121a为止的深度例如为90μm左右,到突起部122的前端为止的深度例如为85μm左右。因此,从底面121a起的突起部122的高度例如为5μm左右。此外,从芯片垫120的最上表面(即,凹部121的开口面)到凹陷部123为止的深度,例如为110~120μm左右。因此,凹陷部123凹陷至从底面121a起20~30μm左右的深度。

56.这里,通过调整dfr210的残留部的密度,在底面121a上以不均一的密度形成多个突起部122,且在突起部122较为稀疏的区域,形成凹陷部123。即,在底面121a的中央部,较为密集地形成突起部122,而在底面121a的周缘部,较为稀疏地形成突起部122,因此在底面121a的周缘部形成凹陷部123。例如,如图9所示,越靠近底面121a的中央,突起部122的密度越高,而越靠近周缘,突起部122的密度越低,从而在突起部122的密度较低的底面121a的周缘,形成凹陷部123。不过,突起部122和凹陷部123的配置不限于图9所示的配置。

57.例如也可以是,如图10所示,将突起部122配置成同心圆状,并在底面121a的中央部,使突起部122的密度较低,由此在底面121a的中央部形成凹陷部123。同样地,通过调节dfr210的残留部的密度,也能够在底面121a的周缘部和中央部形成凹陷部123,或在底面121a的四角形成凹陷部123。

58.此外,例如,如图11(a)所示,还可以配置连续地突起为圆形的、同心圆的多个突起部122,并在底面121a的中央部形成凹陷部123。在这种情况下,图11(a)的y-y线截面例如呈图11(b)那样,突起部122突起至比凹部121的底面121a高的位置,凹陷部123凹陷至比凹部121的底面121a低的位置。

59.进一步地,例如,如图12(a)所示,还可以配置连续地突起为方形的同心的多个突起部122,并在底面121a的中央部形成凹陷部123。在这种情况下,图12(a)的z-z线截面例如呈图12(b)那样,突起部122突起至比凹部121的底面121a高的位置,凹陷部123凹陷至比凹部121的底面121a低的位置。

60.对成形后的引线框架100,进行洗掉dfr210的残渣等前处理后,为了在引脚110的表面上进行电镀,涂敷防镀剂(步骤s106)。具体而言,例如,如图13所示,在引脚110和芯片垫120的整个表面上涂敷防镀剂220。

61.然后,按照引脚110的电镀对象部分,在防镀剂220的表面形成掩模,并进行曝光,由此使未形成有掩模的部分的防镀剂220固化(步骤s107)。具体而言,例如,如图14所示,使除了引脚110的上表面的一部分(引线键合部分)以外的防镀剂220固化。另外,在图14中,用黑色表示防镀剂220中通过曝光而固化的部分。防镀剂220中通过曝光而固化的部分成为在显影后残留的残留部。

62.通过曝光使防镀剂220固化后,进行防镀剂220的显影(步骤s108),在引线框架100的表面上仅残留固化后的残留部。即,例如,如图15所示,成为防镀剂220的残留部覆盖引线框架100的表面而仅显露出引脚110的上表面的一部分的状态。

63.将这样仅显露引脚110的上表面的一部分的引线框架100,浸渍于例如镀银用电镀液,进行电镀(步骤s109)。具体而言,例如在以氰化银和氰化钾为主成分的电镀液中浸渍引

线框架100,来进行电解电镀或无电电镀,由此在引脚110的上表面形成镀层111。

64.即,例如,如图16所示,在未由防镀剂220覆盖的引脚110的上表面的一部分,电镀液所含的银析出,形成例如厚度0.1~10μm的镀层111。形成镀层111后,例如使用剥离液来剥离防镀剂220(步骤s110),然后进行整个表面的涂层等后处理,由此做出引线框架100。即,做出如下的引线框架100:例如,如图17所示,引脚110的上表面形成有镀层111,芯片垫120的中央形成有凹部121,该凹部121包括突起部122和凹陷部123。

65.如上所述,在进行使引脚110与芯片垫120分离的蚀刻时,由于芯片垫120被半蚀刻而形成凹部121,并且在凹部121的底面121a,形成突起部122和凹陷部123。因此,不增加用于形成引线框架100的工序数,也能够形成用于防止接合材料流出至芯片垫120周围的凹部121。换言之,能够防止接合材料的流出,同时避免形成工序复杂化。此外,还能够形成用于提高接合材料与凹部121的底面121a的附着性的突起部122,并且形成用于收纳多余的接合材料的凹陷部123。

66.下面,对在引线框架100上搭载半导体元件来制造半导体装置的工序进行说明。

67.将半导体元件搭载在引线框架100的芯片垫120上。具体而言,例如,如图18所示,使用焊料或贴片膏等接合材料230,将半导体元件240接合到芯片垫120的凹部121内。此时,由于在凹部121的底面121a形成有突起部122,接合材料230与底面121a的附着性提高,能够将半导体元件240可靠地接合到芯片垫120。而且,在凹部121内接合半导体元件240,因此在接合时,流动性的接合材料230不会流出至芯片垫120的周围。进一步地,即使接合材料230的提供量过多,多余的接合材料也能被收纳于凹陷部123,不会出现接合材料230溢出至凹部121的外部的情形。

68.在将半导体元件240接合到芯片垫120后,例如,如图19所示,通过引线键合将半导体元件240与引脚110连接。即,通过引线250将半导体元件240的电极与引脚110的镀层111之间电气连接。此时,没有从凹部121流出的接合材料230,所以引线键合连接不受阻碍。此外,由于半导体元件240搭载于凹部121内,半导体元件240的上表面的高度接近于引脚110的镀层111的高度,可实现半导体装置的减薄化,同时可以缩短引线250的长度。

69.然后,进行模塑,利用封装用树脂来将搭载于引线框架100的半导体元件240封装。具体而言,将搭载有半导体元件240的引线框架100收纳在模具中,并将流态化的封装用树脂注入到模具内。然后,将封装用树脂加热至规定的温度使其固化,由此,例如,如图20所示,在半导体元件240周围的空间内填充封装用树脂260,将搭载于引线框架100的半导体元件240封装。此时,由于在芯片垫120上形成有凸缘部124,因此封装用树脂260填充至凸缘部124下方的凹口部分,引线框架100与封装用树脂260的结合强度得以提高。即,可以减小引线框架100从封装用树脂260脱落的可能性。

70.在将搭载于引线框架100的半导体元件240由封装用树脂260封装后,在图20所示的虚线部分切断封装用树脂260,同时将引脚110和连结部130与框体f切断开。由此,从引线框架100分离并去除框体f,例如,如图21所示,做出具有引脚110、芯片垫120、半导体元件240和封装用树脂260的半导体装置。该半导体装置中,引脚110的下表面和从框体f切断出的侧面,从封装用树脂260的下表面和侧面显露,作为与外部连接的端子。此外,芯片垫120的下表面从封装用树脂260的下表面显露。

71.综上所述,根据本实施方式,在对金属板进行蚀刻以分离引脚与芯片垫时,对芯片

垫的中央进行半蚀刻来形成凹部,并且对凹部区域中的dfr的密度进行调节,以在底面上形成突起部和凹陷部。由此,不增加工序数,能够形成在芯片垫的中央具有凹部、且在凹部的底面上具有突起部和凹陷部的引线框架。其结果,不会出现在将半导体元件搭载于芯片垫的凹部内时,用于接合半导体元件的接合材料从凹部流出至周围的情形。换言之,能够防止接合材料的流出,同时避免形成工序的复杂化。

72.此外,通过形成于凹部底面上的突起部,能够提高接合材料的附着性,并且通过形成于凹部底面上的凹陷部,能够收纳多余的接合材料。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1