一种硅基电容集成结构及其制备方法与流程

1.本发明涉及电容结构,具体涉及一种硅基电容机构及其制备方法。

背景技术:

2.由于半导体激光器具有制作简单、体积小、重量轻、工作寿命长、效率高等优点,使其在光通信、光泵浦、光存储和激光显示等领域得到广泛应用。

3.目前的半导体激光器,一般采用to管座进行封装,传统的to里面,激光器芯片热沉是氮化铝薄膜电路,将电容、电阻等元器件通过打线方式与芯片实现连接。利用成熟的硅工艺,可以设计并实现高频to基板,实现电阻电容等元件集成,节省物料和简化to的组装工序。

4.但是硅基集成的电容是薄膜形式,一般是金属间有一层介电薄膜,厚度一般小于1微米。薄膜电容不适合打线工艺,打线过程的应力会损伤薄的介电层,导致电容失效或者带来长期工作的可靠性问题。

技术实现要素:

5.本发明所要解决的技术问题是:针对现有技术中硅基薄膜电容打线过程中,打线应力损伤介电层,导致电容失效的技术缺陷,提供一种硅基电容集成结构及其制备方法。

6.为解决上述技术问题,本发明提供了一种硅基电容集成结构,包括:衬底,隔离层,隔离层形成在衬底上;下电极层,下电极层设置在隔离层上;台阶结构,台阶结构设置在下电极层上,台阶结构内包围有至少一层介电层,介电层覆盖在下电极层上;上电极层,上电极层覆盖在介电层上;其中,台阶结构分隔介电层与上电极层的打线区域。

7.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:下电极层的面积、上电极层的面积均大于介电层。

8.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:下电极层连接有与外界电元件连接的引线,引线形成下电极层的打线区域。

9.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:台阶结构上与引线相对应的位置处开设有开口区。

10.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:上电极层的打线区域与下电极层分隔。

11.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:台阶结构和介电层的材料为二氧化硅、氮化硅、氧化锆、或氧化铪。

12.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:介电层的材料为氮化硅;台阶结构的材料为二氧化硅,高度为500埃米到2微米。

13.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:衬底的材料为硅、玻璃或者陶瓷,隔离层为二氧化硅薄膜,厚度为0.2微米到1微米。

14.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:下电极层为铝、

铜、金、银、多晶硅或单晶硅,厚度为0.1微米到1微米。

15.在本发明提供的硅基电容集成结构中,还可以具有这样的特征:上电极层为金、钛、铝、铜以及银中的一种或者多种。

16.本发明还提供了一种硅基电容集成结构的制备方法,包括一下步骤:选衬底;在硅衬底上形成隔离层;在隔离层上形成下电极层,并在下电极层上形成下电极和引线;在下电极层上形成台阶结构,并在台阶结构包围内沉积介电层;在下电极层上刻蚀出下电极的引线区域;在介电层上沉积上电极层。

17.在本发明提供的硅基电容集成结构的制备方法中,还可以具有这样的特征:采用蒸发剥离工艺在下电极层上形成下电极和引线;采用光刻和刻蚀的方法形成台阶结构;用光刻和刻蚀的方法刻蚀出下电极的引线区域;在介电层上用光刻和金属剥离的方法沉积上电极层。

18.本发明的有益效果在于:

19.在本发明的硅基电容集成结构中,在衬底上形成隔离层,然后在隔离层上面设置下电极层,在下电极层上设置台阶结构,且台阶结构包围有介电层,上电极层覆盖在介电层上,基于上述结构,台阶结构能够分隔介电层与上电极层的打线区域,这样使得该电容的打线区域位于台阶结构的外部,避免打线应力集中在介电层内,从而避免电容的薄膜区域被击穿的情况发生,实现了可视化嵌埋电容结构。

20.另外,下电极层的面积大于介电层的面积,且其连接有引线,该引线能够与其他元器件连接。而且引线部分作为该下电极层的打线区域,该打线区域与介电层分隔。

21.此外,台阶结构包围在介电层的外部,且在与下电极层的引线相对应的位置处设置有开口区,实现引线与其他元器件的连接。

22.不仅如此,台阶结构的高度为500埃米到2微米。该台阶结构能够让上电极层的打线区域与介电层分隔。

23.另外,在介电层上覆盖上电极层后,由于上电极层的面积大于介电层的面积,使得台阶结构在显微镜下清晰可见。

24.在发明提供的硅基电容集成结构的制备方法中,选衬底;在硅衬底上形成隔离层;在隔离层上形成下电极层,并在下电极层上形成下电极和引线;在下电极层上形成台阶结构,并在台阶结构包围内沉积介电层;在下电极层上刻蚀出下电极的引线区域;在介电层上沉积上电极层,该制备方法可实现热沉、电阻、埋嵌电容、高频数显、金锡焊盘等及集成一颗芯片、具有小尺寸、温漂小、易集成的特点。

附图说明

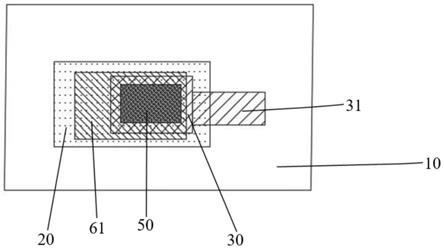

25.图1是本发明实施例中的硅基电容集成结构的剖面图;

26.图2是本发明实施例中的硅基电容集成结构的俯视图。

具体实施方式

27.为了使本发明所解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本发明进行进一步的详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

28.如图1~2所示,本实施例中的硅基电容集成结构包括衬底10、隔离层20、下电极层30、台阶结构40、介电层50、上电极层60。

29.衬底10选用硅、玻璃或者陶瓷,在本实施例中,衬底10选用的材料为硅。

30.隔离层20形成在衬底10上的。隔离层20选用二氧化硅薄膜,该二氧化硅薄膜的厚度为0.2~1μm。这样使得隔离层20能够与衬底10具有相近的热膨胀系数且都是良好的绝缘材料。

31.下电极层30形成在隔离层20上。下电极层30选用铝、铜、金、银、多晶硅或者单晶硅材料。在本实施例中,下电极层30选用的材料是铝。下电极层30的厚度为0.1~1μm。

32.下电极层30连接有引线31,该引线31与其他需要连接的元器件连接。该引线31为下电极的打线区域。

33.台阶结构40设置在下电极层30上方,其面积大于下电极层30的面积,覆盖住下电极层30的边界。台阶结构40包围在介电层50的周围。

34.台阶结构40、介电层50的材料为二氧化硅、氮化硅、氧化锆、氧化铪等薄膜。但在实际应用或其他实施例中,也可以根据需求选用其他的绝缘材料。

35.台阶结构40的高度为500埃米到2微米。介电层50的厚度可以根据实际电容的需求设计

36.台阶结构40上与引线31相对应的位置处设置有开口区,该开口区能够实现引线31与元器件的连接。

37.下电极层30的面积、上电极层60的面积均大于介电层50的面积。

38.上电极层60覆盖在介电层50上,其面积大于介电层50的面积。上电极层60的打线区域61为台阶结构40的外部。该打线区域61与下电极层30的打线区域分割,即上电极层60的打线区域与下电极层30的引线31(即下电极层的打线区域)不重叠。

39.上电极层60选用的材料为金、钛、铝、铜和银中的一种或者多种。上电极层60覆盖后,台阶结构40在显微镜下能够清晰可见。

40.在本实施例中的硅基电容集成结构中,上电极层60、介电层50以及下电极层30构成了该硅基电容集成结构的有效电容区域。

41.上述的硅基电容集成结构的制备方法包括以下步骤:

42.选用硅衬底10;

43.在硅衬底10的表面形成一层绝缘隔离层20,该隔离层20选用的是厚度为0.3μm的二氧化硅薄膜;

44.选用铝作为下电极层30形成在隔离层20上,并采用蒸发剥离工艺在下电极层20上形成引线31,下电极层30的厚度3000埃米

45.在下电极层30上沉积一层厚度为3000埃米的二氧化硅,并用光刻和刻蚀的方法在该二氧化硅上刻蚀出电容区域,暴露出下电极层30下电极金属,形成台阶结构40;

46.然后在台阶结构40包围内再沉积厚度为500埃米的氮化硅薄膜,作为介电层50;

47.用光刻和刻蚀的方法,在下电极层30刻蚀出下电极的引线31;

48.再用光刻和金属剥离的方法,在氮化硅薄膜上沉积材料为金的上电极层60。沉积上电极层60后,上电极层60以台阶结构40为界,形成上电极层60的打线区域61。

49.基于上述制备方法制备得到的硅基电容集成结构在封装过程中,电容的下电极层

30是通过引线31引出,打线可以在引线区域;上电极层60与电容区域有明显的台阶结构40区分,打线在台阶结构40的外部,可以避免打线应力集中在电容薄膜区域。

50.根据上述实施例中的硅基电容集成结构中,在衬底上形成隔离层,然后在隔离层上面设置下电极层,在下电极层上设置台阶结构,且台阶结构包围有介电层,上电极层覆盖在介电层上,基于上述结构,台阶结构能够分隔介电层与上电极层的打线区域,这样使得该电容的打线区域位于台阶结构的外部,避免打线应力集中在介电层内,从而避免电容的薄膜区域被击穿的情况发生,实现了可视化嵌埋电容结构。

51.另外,下电极层的面积大于介电层的面积,且其连接有引线,该引线能够与其他元器件连接。而且引线部分作为该下电极层的打线区域,该打线区域与介电层分隔。

52.此外,台阶结构包围在介电层的外部,且在与下电极层的引线相对应的位置处设置有开口区,实现引线与其他元器件的连接。

53.不仅如此,台阶结构的高度为500埃米到2微米。该台阶结构能够让上电极层的打线区域与介电层分隔。

54.另外,在介电层上覆盖上电极层后,由于上电极层的面积大于介电层的面积,使得台阶结构在显微镜下清晰可见。

55.在发明提供的硅基电容集成结构的制备方法中,选衬底;在硅衬底上形成隔离层;在隔离层上形成下电极层,并在下电极层上形成下电极和引线;在下电极层上形成台阶结构,并在台阶结构包围内沉积介电层;在下电极层上刻蚀出下电极的引线区域;在介电层上沉积上电极层,该制备方法可实现热沉、电阻、埋嵌电容、高频数显、金锡焊盘等及集成一颗芯片、具有小尺寸、温漂小、易集成的特点。

56.显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的精神和范围。这样,倘若本技术的这些修改和变型属于本技术权利要求极其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1