集成电路装置的制作方法

1.本技术是有关于一种装置,详细来说,是有关于一种集成电路装置。

背景技术:

2.目前的半导体封装工艺中,一般使用普通的银胶进行黏晶工艺以完成焊接。然而,银浆会存在烘烤后开裂的风险,并且,当使用某些材料制成载板(如引线框架)时,银浆的颜色与载板颜色相近,造成无法识别银浆在载板的位置。

技术实现要素:

3.有鉴于此,本技术提出一种集成电路装置以解决上述问题。

4.依据本技术一实施例,提出一种集成电路装置。所述集成电路装置包括载板、胶层以及集成电路芯片。所述胶层涂覆于所述载板之上,其中所述胶层包括铜浆,所述胶层的厚度在5

‑

35微米的范围,所述铜浆的粘度系数在10000

‑

30000cps的范围,所述铜浆的触变指数在1.5

‑

3的范围。所述集成电路芯片通过所述胶层粘接于所述载板之上。

5.依据本技术一实施例,所述铜浆为高分子抗氧化铜浆。

6.依据本技术一实施例,所述铜浆包括奈米抗氧化铜粉。

7.依据本技术一实施例,所述铜浆的粘度系数是15880cps。

8.依据本技术一实施例,所述铜浆的触变指数是2.12。

9.依据本技术一实施例,所述胶层的导热系数大于15w/m.k。

10.依据本技术一实施例,所述胶层的厚度在15

‑

35微米的范围。

11.依据本技术一实施例,所述集成电路芯片的厚度大于200微米,所述胶层的溢出高度在所述集成电路芯片的厚度的20%

‑

80%的范围。

12.依据本技术一实施例,所述集成电路芯片的厚度大于200微米,所述胶层的溢出高度在所述集成电路芯片的厚度的40%

‑

60%的范围。

13.依据本技术一实施例,所述集成电路芯片的厚度在100

‑

200微米的范围,所述胶层的溢出高度在所述集成电路芯片的厚度的20%

‑

90%的范围。

14.依据本技术一实施例,所述集成电路芯片的厚度在100

‑

200微米的范围,所述胶层的溢出高度在所述集成电路芯片的厚度的30%

‑

80%的范围。

15.依据本技术一实施例,所述集成电路芯片的厚度小于100微米,所述胶层的溢出高度小于所述集成电路芯片的厚度。

16.依据本技术一实施例,所述集成电路芯片的厚度小于100微米,所述胶层的溢出高度小于所述集成电路芯片的厚度的95%。

17.依据本技术一实施例,所述集成电路芯片的尺寸小于或等于2毫米*2毫米,放置在所述胶层上的所述集成电路芯片的芯片倾斜小于10微米。

18.依据本技术一实施例,所述集成电路芯片的尺寸小于或等于2毫米*2毫米,放置在所述胶层上的所述集成电路芯片的芯片倾斜小于7微米。

19.依据本技术一实施例,所述集成电路芯片的尺寸大于2毫米*2毫米,放置在所述胶层上的所述集成电路芯片的芯片倾斜小于20微米。

20.依据本技术一实施例,所述集成电路芯片的尺寸大于2毫米*2毫米,放置在所述胶层上的所述集成电路芯片的芯片倾斜小于15微米。

附图说明

21.附图是用来提供对本技术的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本技术,但并不构成对本技术的限制。在附图中:

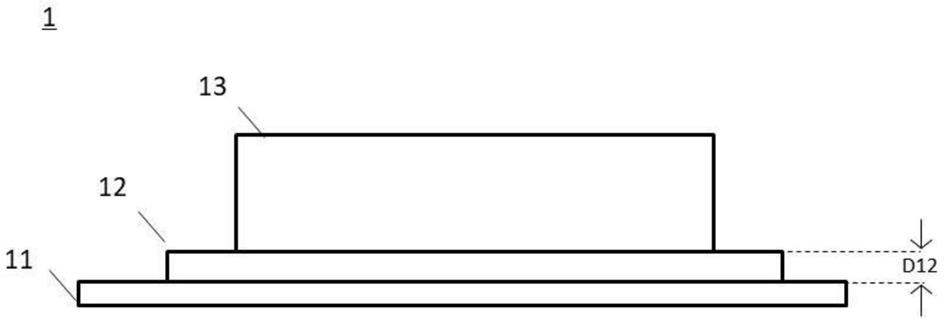

22.图1演示依据本技术一实施例之集成电路装置的侧视视图。

23.图2演示依据本技术另一实施例之集成电路装置的侧视视图。

具体实施方式

24.以下揭示内容提供了多种实施方式或例示,其能用以实现本揭示内容的不同特征。下文所述之组件与配置的具体例子系用以简化本揭示内容。当可想见,这些叙述仅为例示,其本意并非用于限制本揭示内容。举例来说,在下文的描述中,将一第一特征形成于一第二特征上或之上,可能包括某些实施例其中所述的第一与第二特征彼此直接接触;且也可能包括某些实施例其中还有额外的组件形成于上述第一与第二特征之间,而使得第一与第二特征可能没有直接接触。此外,本揭示内容可能会在多个实施例中重复使用组件符号和/或标号。此种重复使用乃是基于简洁与清楚的目的,且其本身不代表所讨论的不同实施例和/或组态之间的关系。

25.再者,在此处使用空间上相对的词汇,譬如「之下」、「下方」、「低于」、「之上」、「上方」及与其相似者,可能是为了方便说明图中所绘示的一组件或特征相对于另一或多个组件或特征之间的关系。这些空间上相对的词汇其本意除了图中所绘示的方位之外,还涵盖了装置在使用或操作中所处的多种不同方位。可能将所述设备放置于其他方位(如,旋转90度或处于其他方位),而这些空间上相对的描述词汇就应该做相应的解释。

26.虽然用以界定本技术较广范围的数值范围与参数皆是约略的数值,此处已尽可能精确地呈现具体实施例中的相关数值。然而,任何数值本质上不可避免地含有因个别测试方法所致的标准偏差。在此处,「约」通常系指实际数值在一特定数值或范围的正负10%、5%、1%或0.5%之内。或者是,「约」一词代表实际数值落在平均值的可接受标准误差之内,视本技术所属技术领域中具有通常知识者的考虑而定。当可理解,除了实验例之外,或除非另有明确的说明,此处所用的所有范围、数量、数值与百分比(例如用以描述材料用量、时间长短、温度、操作条件、数量比例及其他相似者)均经过「约」的修饰。因此,除非另有相反的说明,本说明书与附随权利要求书所揭示的数值参数皆为约略的数值,且可视需求而更动。至少应将这些数值参数理解为所指出的有效位数与套用一般进位法所得到的数值。在此处,将数值范围表示成由一端点至另一端点或介于二端点之间;除非另有说明,此处所述的数值范围皆包括端点。

27.图1演示依据本技术一实施例之集成电路装置1的侧视视图。在某些实施例中,集成电路装置1包括载板11、胶层12以及集成电路芯片13。在某些实施例中,载板11可为引线框架、基板、pcb板等。在某些实施例中,载板11(如引线框架)可以用镀镍钯金材质、纯铜或

铜镀银来制成,本技术不以此为限。在某些实施例中,集成电路芯片13通过胶层12粘接于载板11之上。在某些实施例中,集成电路芯片13可以是以碳化硅、碳化氮或硅材料作为衬底的芯片,本技术不以此为限。

28.在某些实施例中,胶层12涂覆于载板11之上。在某些实施例中,胶层12包括至少由铜粉、粘合剂和单体组成的铜浆。在某些实施例中,铜浆可以是高分子抗氧化铜浆,铜粉可以是奈米抗氧化铜粉,使用高分子抗氧化铜浆可以克服铜容易氧化的缺陷。

29.在某些实施例中,铜浆的粘度系数在10000

‑

30000cps的范围。在某些实施例中,铜浆的粘度系数是15880cps。在某些实施例中,铜浆的触变指数在1.5

‑

3的范围。在某些实施例中,铜浆的触变指数是2.12。需注意的是,本技术不限制铜浆的制造方式。

30.在某些实施例中,胶层12的导热系数大于15w/m.k。在某些实施例中,胶层12的厚度d12在5

‑

35微米的范围,使得产品具有更好的导热性、导电性及剪切强度,产品的导热系数达到15w/m.k,产品单位电阻率≤1.0

×

10

‑

4ω*cm,并且产品的剪切强度(亦称推晶试验推力值)>2.5kg,其中剪切强度是集成电路芯片与载板11通过胶层粘合固化后,为了验证黏合效果,用专用推晶设备给予集成电路芯片推力使集成电路芯片与载板分离的一种试验数据。

31.经申请人研发试验发现,当胶层的厚度>35微米时,会造成集成电路芯片倾斜。

32.在某些实施例中,胶层12的厚度d12在25微米

±

10微米的范围,即15

‑

35微米的范围。

33.需注意的是,图1所示的胶层12的形状仅为范例说明。本领域技术人员应能理解当集成电路芯片13通过胶层12粘接于载板11时,胶层12会产生变形,因此产生溢出高度。图2演示依据本技术另一实施例之集成电路装置1’的侧视视图。在某些实施例中,集成电路装置1’与集成电路装置1大致相同,差异仅在于集成电路装置1’所包括的胶层12’因集成电路芯片13的放置而变形,并有部分胶层12’黏着于集成电路芯片13的侧边。变形的胶层12’具有溢出高度d12’。在某些实施例中,胶层12’的溢出高度d12’与集成电路芯片13的厚度d13相关。

34.在某些实施例中,当集成电路芯片13的厚度d13大于200微米时,胶层12’的溢出高度d12’在集成电路芯片13的厚度d13的20%

‑

80%的范围,低于20%芯片有空洞,粘结不牢,脱落等风险,超出80%有铜胶溢到芯片表面的风险,造成打线不良,芯片短路等异常。在某些实施例中,当集成电路芯片13的厚度d13大于200微米时,胶层12’的溢出高度d12’在集成电路芯片13的厚度d13的40%

‑

60%的范围,卡控在此范围能更好地预防因胶量控制不佳造成上述异常,同时更好地保证铜胶产品的导热,导电性能,产品的导热系数达到15w/m.k,产品单位电阻率≤1.0

×

10

‑

4ω*cm。

35.在某些实施例中,当集成电路芯片13的厚度d13在100

‑

200微米的范围时,胶层12’的溢出高度d12’在集成电路芯片13的厚度d13的20%

‑

90%的范围,低于20%芯片有空洞,粘结不牢,脱落等风险,超出90%有铜胶溢到芯片表面的风险,造成打线不良,芯片短路等异常。在某些实施例中,当集成电路芯片13的厚度d13在100

‑

200微米的范围时,胶层12’的溢出高度d12’在集成电路芯片13的厚度d13的30%

‑

80%的范围,卡控在此范围能更好地预防因胶量控制不佳造成上述异常,同时更好地保证铜胶产品的导热,导电性能,产品的导热系数达到15w/m.k,产品单位电阻率≤1.0

×

10

‑

4ω*cm。

36.在某些实施例中,当集成电路芯片13的厚度d13小于100微米时,胶层12’的溢出高度d12’小于集成电路芯片13的厚度d13的100%(即,小于集成电路芯片13的厚度d13),如果≥100%有铜胶溢到集成电路芯片表面的风险,造成打线不良,芯片短路等异常。在某些实施例中,当集成电路芯片13的厚度d13小于100微米时,胶层12’的溢出高度d12’小于集成电路芯片13的厚度d13的95%,卡控在此范围能更好地预防因胶量控制不佳造成上述异常,同时更好地保证铜胶产品的导热,导电性能,产品的导热系数达到15w/m.k,产品单位电阻率≤1.0

×

10

‑

4ω*cm。

37.在某些实施例中,当集成电路芯片13的尺寸小于或等于2毫米*2毫米,放置在胶层12(或胶层12’)的集成电路芯片13的倾斜小于10微米,更好地控制晶浮,芯片粘结不牢等异常,同时更好地保证铜胶产品的导热性能,使热传导更均匀。在某些实施例中,当集成电路芯片13的尺寸小于或等于2毫米*2毫米,放置在胶层12(或胶层12’)的集成电路芯片13的倾斜小于7微米,卡控在此范围内更好地预防晶浮,芯片粘结不牢等异常,更大程度保证铜胶产品的导热,导电性能,产品的导热系数达到15w/m.k,产品单位电阻率≤1.0

×

10

‑

4ω*cm。

38.在某些实施例中,当集成电路芯片13的尺寸大于2毫米*2毫米,放置在胶层12(或胶层12’)的集成电路芯片13的倾斜小于20微米,更好地控制晶浮,芯片粘结不牢等异常,同时更好地保证铜胶产品的导热性能,使热传导更均匀。在某些实施例中,当集成电路芯片13的尺寸大于2毫米*2毫米,放置在胶层12(或胶层12’)的集成电路芯片13的倾斜小于15微米,卡控在此范围内更好地预防晶浮,芯片粘结不牢等异常,更大程度保证铜胶产品的导热,导电性能,产品的导热系数达到15w/m.k,产品单位电阻率≤1.0

×

10

‑

4ω*cm。

39.在某些实施例中,胶层12(或胶层12’)上单一空洞的面积小于胶层12(或胶层12’)的面积的2%,总体空洞面积小于胶层12(或胶层12’)的面积的15%。在某些实施例中,胶层12(或胶层12’)上单一空洞的面积小于胶层12(或胶层12’)的面积的1%,总体空洞面积小于胶层12(或胶层12’)的面积的5%。

40.本技术的申请人经试验后发现,使用本技术揭露的铜浆进行集成电路黏晶作业时,在点胶后两小时以及胶固化后都没有出现水印现象;并且,即使在停机30分钟后作业,点胶针出胶顺畅,胶的形状及位置无偏移或缺损,说明胶的流动性良好;另外,在出胶后2小时内进行黏晶,高分子抗氧化铜浆仍具有胶的性能。

41.如本文中所使用,术语“近似地”、“基本上”、“基本”及“约”用于描述并考虑小变化。当与事件或情况结合使用时,所述术语可指事件或情况精确地发生的例子以及事件或情况极近似地发生的例子。如本文中相对于给定值或范围所使用,术语“约”大体上意味着在给定值或范围的

±

10%、

±

5%、

±

1%或

±

0.5%内。范围可在本文中表示为自一个端点至另一端点或在两个端点之间。除非另外规定,否则本文中所公开的所有范围包括端点。术语“基本上共面”可指沿同一平面定位的在数微米(μm)内的两个表面,例如,沿着同一平面定位的在10μm内、5μm内、1μm内或0.5μm内。当参考“基本上”相同的数值或特性时,术语可指处于所述值的平均值的

±

10%、

±

5%、

±

1%或

±

0.5%内的值。

42.如本文中所使用,术语“近似地”、“基本上”、“基本”和“约”用于描述和解释小的变化。当与事件或情况结合使用时,所述术语可指事件或情况精确地发生的例子以及事件或情况极近似地发生的例子。举例来说,当与数值结合使用时,术语可指小于或等于所述数值的

±

10%的变化范围,例如,小于或等于

±

5%、小于或等于

±

4%、小于或等于

±

3%、小于

或等于

±

2%、小于或等于

±

1%、小于或等于

±

0.5%、小于或等于

±

0.1%,或小于或等于

±

0.05%。举例来说,如果两个数值之间的差小于或等于所述值的平均值的

±

10%(例如,小于或等于

±

5%、小于或等于

±

4%、小于或等于

±

3%、小于或等于

±

2%、小于或等于

±

1%、小于或等于

±

0.5%、小于或等于

±

0.1%,或小于或等于

±

0.05%),那么可认为所述两个数值“基本上”或“约”相同。举例来说,“基本上”平行可以指相对于0

°

的小于或等于

±

10

°

的角度变化范围,例如,小于或等于

±5°

、小于或等于

±4°

、小于或等于

±3°

、小于或等于

±2°

、小于或等于

±1°

、小于或等于

±

0.5

°

、小于或等于

±

0.1

°

,或小于或等于

±

0.05

°

。举例来说,“基本上”垂直可以指相对于90

°

的小于或等于

±

10

°

的角度变化范围,例如,小于或等于

±5°

、小于或等于

±4°

、小于或等于

±3°

、小于或等于

±2°

、小于或等于

±1°

、小于或等于

±

0.5

°

、小于或等于

±

0.1

°

,或小于或等于

±

0.05

°

。

43.举例来说,如果两个表面之间的位移等于或小于5μm、等于或小于2μm、等于或小于1μm或等于或小于0.5μm,那么两个表面可以被认为是共面的或基本上共面的。如果表面相对于平面在表面上的任何两个点之间的位移等于或小于5μm、等于或小于2μm、等于或小于1μm或等于或小于0.5μm,那么可以认为表面是平面的或基本上平面的。

44.如本文中所使用,术语“导电(conductive)”、“导电(electrically conductive)”和“电导率”是指转移电流的能力。导电材料通常指示对电流流动为极少或零对抗的那些材料。电导率的一个量度是西门子/米(s/m)。通常,导电材料是电导率大于近似地104s/m(例如,至少105s/m或至少106s/m)的一种材料。材料的电导率有时可以随温度而变化。除非另外规定,否则材料的电导率是在室温下测量的。

45.如本文中所使用,除非上下文另外明确规定,否则单数术语“一(a/an)”和“所述”可包含复数指示物。在一些实施例的描述中,提供于另一组件“上”或“上方”的组件可涵盖前一组件直接在后一组件上(例如,与后一组件物理接触)的情况,以及一或多个中间组件位于前一组件与后一组件之间的情况。

46.如本文中所使用,为易于描述可在本文中使用空间相对术语例如“下面”、“下方”、“下部”、“上方”、“上部”、“下部”、“左侧”、“右侧”等描述如图中所说明的一个组件或特征与另一组件或特征的关系。除图中所描绘的定向之外,空间相对术语意图涵盖在使用或操作中的装置的不同定向。设备可以其它方式定向(旋转90度或处于其它定向),且本文中所使用的空间相对描述词同样可相应地进行解释。应理解,当一组件被称为“连接到”或“耦合到”另一组件时,其可直接连接或耦合到所述另一组件,或可存在中间组件。

47.前文概述本公开的若干实施例和细节方面的特征。本公开中描述的实施例可容易地用作用于设计或修改其它过程的基础以及用于执行相同或相似目的和/或获得引入本文中的实施例的相同或相似优点的结构。这些等效构造不脱离本公开的精神和范围并且可在不脱离本公开的精神和范围的情况下作出不同变化、替代和改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1