芯片密封环的制作方法

1.本发明涉及半导体技术领域,尤其是涉及一种芯片密封环。

背景技术:

2.在晶圆封装工艺中,需要对芯片进行切割。为了保护芯片,一般会在芯片和切割道之间,配置芯片密封环(seal ring)。芯片密封环可以防止任何裂痕侵入芯片内部,芯片密封环的部分结构为层间介质层(imd)。

3.半导体业界,想单位晶圆上获得更多的芯片是一直研究的方向。现有技术一般采用的方法为,缩小切割道宽度或者省略芯片密封环结构,减少芯片之外的部位的面积,从而使得有更多的面积形成芯片,以提高晶圆上的芯片的数量。但是因为切割道上要放置足够的电性测试键,甚至一些工艺中的电性测试键全部位于切割道上,电性测试键可以用来测试多种电性,例如用来测试金属层之间的漏电流。因此,如果一味的减少切割道的宽度,可能导致电性测试键无法放置或者影响电性测试键的功能。而如果省去芯片密封环,则可能会带来后续切割崩坏的风险。无论是先进的28nm工艺还是普通的0.18μm工艺,发生过多起芯片裂开的案例,失效分析的结果一般都为在切割道进行切割时,产生的机械力冲破芯片密封环的保护,使得芯片密封环产生裂缝,并且裂缝延伸到芯片的内部,导致芯片内部的线路的断路及损坏,因此,芯片密封环缺一不可。

技术实现要素:

4.本发明的目的在于提供一种芯片密封环,在切割晶圆形成独立芯片时,可以保护芯片不会受到切割产生的机械力的影响,同时,还可以对电性进行测试,减少切割道上的电性测试键,从而减少切割道的宽度,以在晶圆上形成更多的芯片。

5.为了达到上述目的,本发明提供了一种芯片密封环,包括:

6.基底,围绕于芯片形成闭合的环状结构;

7.第一金属层至第n金属层,依次形成在所述基底上,n层所述金属层之间通过介质层隔离开,每层所述金属层均包括第一金属条至第n金属条,同层所述金属层中的所述第一金属条至第n金属条依次围绕于所述芯片从内到外依次形成n个非闭合的环状结构,每个所述金属条均具有第一开口,每层所述金属层的每个金属条均连通到相邻层的一个金属条上,并且同层所述金属层的金属条不能连通到同一金属条上;以及

8.多个电性测试键,用以测试所述金属层的电性,每个所述金属条上具有两个所述电性测试键,两个所述电性测试键分别位于所述第一开口处的金属条的两个端部上。

9.可选的,在所述的芯片密封环中,每层所述金属层的n个金属条中除了条数与当层所述金属层的层数相同的金属条,其余n-1个金属条还具有第二开口,所述第一开口和第二开口在所述金属条相对的两个方向。

10.可选的,在所述的芯片密封环中,同层所述金属层上的金属条之间的距离为1μm。

11.可选的,在所述的芯片密封环中,所述电性测试键包括pad。

12.可选的,在所述的芯片密封环中,所述pad和相邻的金属条的距离为1μm。

13.可选的,在所述的芯片密封环中,所述pad为正方形,所述pad的边长为5μm。

14.可选的,在所述的芯片密封环中,每层所述金属层的每个金属条均通过连接件连通到相邻层的一个金属条。

15.可选的,在所述的芯片密封环中,所述基底和所述第一金属层之间通过介质层隔开,所述第一金属层通过连接件连接到所述基底的表面。

16.可选的,在所述的芯片密封环中,n为四,四层金属层分别为第一金属层、第二金属层、第三金属层和第四金属层;所述第一金属层位于所述基底上,并且通过介质层和所述基底隔开,所述第一金属层还通过连接件与所述基底的表面连通;所述第二金属层位于所述第一金属层上,并且通过介质层与所述第一金属层隔开;所述第三金属层位于所述第二金属层上,并且通过介质层与所述第二金属层隔开;所述第四金属层位于所述第三金属层上,并且通过介质层与所述第三金属层隔开。

17.可选的,在所述的芯片密封环中,每层所述金属层包括四个金属条,分别为第一金属条、第二金属条、第三金属条和第四金属条;所述第一金属条围绕于所述芯片形成非闭合的环状结构;所述第二金属条围绕于所述第一金属条形成非闭合的环状结构;所述第三金属条围绕于所述第二金属条形成非闭合的环状结构;所述第四金属条围绕于所述第三金属条形成非闭合的环状结构。

18.在本发明提供的芯片密封环中,通过电性测试键的信号以获得与电性测试键连通的金属条的电性参数,而金属层包括金属条,所以能通过电性测试键的信号测试金属层的电性参数,因此,本发明的芯片密封环不但可以在切割晶圆形成独立芯片时,保护芯片不会受到切割产生的机械力的影响,同时,还可以对电性进行测试,减少切割道上的电性测试键,从而减少切割道的宽度,以在晶圆上形成更多的芯片。

附图说明

19.图1是本发明实施例的芯片密封环的示意图;

20.图2是本发明实施例的第四层金属层的示意图;

21.图3是本发明实施例的第三层金属层的示意图;

22.图4是本发明实施例的第二层金属层的示意图;

23.图5是本发明实施例的第一层金属层的示意图;

24.图6是本发明实施例的四层金属层连通的示意图;

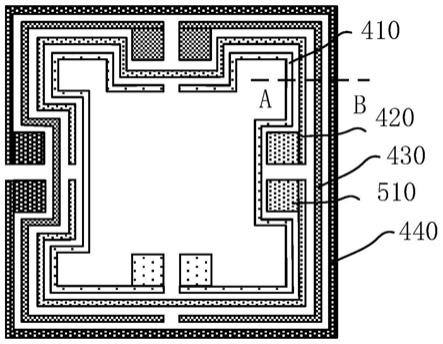

25.图中:1-芯片密封环、100-第一金属层、110-第一金属条、120-第二金属条、130-第三金属条、140-第四金属条、200-第二金属层、210-第一金属条、220-第二金属条、230-第三金属条、240-第四金属条、300-第三金属层、310-第一金属条、320-第二金属条、330-第三金属条、340-第四金属条、400-第四金属层、410-第一金属条、420-第二金属条、430-第三金属条、440-第四金属条、510-电性测试键、600-连接件。

具体实施方式

26.下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准

的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

27.在下文中,术语“第一”“第二”等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。要理解,在适当情况下,如此使用的这些术语可替换。类似的,如果本文所述的方法包括一系列步骤,且本文所呈现的这些步骤的顺序并非必须是可执行这些步骤的唯一顺序,且一些所述的步骤可被省略和/或一些本文未描述的其他步骤可被添加到该方法。

28.发明人发现如何在保留芯片密封环的前提下,如何尽量缩小切割道宽度,以往的电性测试键全部位于切割道上。没有seal ring与电性测试键结合的先例。

29.因此,本发明提供了一种芯片密封环,包括:

30.基底,围绕于芯片形成闭合的环状结构;

31.第一金属层至第n金属层,依次形成在所述基底上,n层所述金属层之间通过介质层隔离开,每层所述金属层均包括第一金属条至第n金属条,同层所述金属层中的所述第一金属条至第n金属条依次围绕于所述芯片从内到外依次形成n个非闭合的环状结构,每个所述金属条均具有第一开口,每层所述金属层的每个金属条均连通到相邻层的一个金属条上,并且同层所述金属层的金属条不能连通到同一金属条上;以及

32.多个电性测试键,用以测试所述金属层的电性,每个所述金属条上具有两个所述电性测试键,两个所述电性测试键分别位于所述第一开口处的金属条的两个端部上。

33.其中,所述基底和所述第一金属层之间通过介质层隔开,所述第一金属层通过连接件连接到所述基底的表面。

34.请参照图1,是芯片密封环的整体结构图,类似于一个整体框架的结构,中间为芯片所在的区域,图1的框架图的内框和外框之间为密封环结构所在的区域,外框之外是切割道区域,在切割道进行切割时就可以将晶圆上的芯片分割开来。而芯片密封环就可以阻挡切割时产生的机械力,防止芯片受到机械力的破坏。本发明实施例在芯片密封环上设置了多个电性测试键,可以通过电性测试键测试金属条的电性参数,以代替原先必须放置在切割道上的部分test-key的功能,不但能保护芯片,还能测试电性问题,还能减少切割道的面积,从而使得在单位面积的晶圆上获得更多的芯片。因此,实际上基底的剖面也图1的框图一样。然后再基底上形成各种金属层以及金属层之间的测试结构。

35.优选的,所述金属条之间的距离为1μm。金属条做成比较规则的形状,可选的,在所述的芯片密封环中,同层所述金属层上的金属条之间的距离为1μm。

36.本发明实施例中,所述电性测试键包括pad。所述pad和相邻的金属条的距离为1μm。所述pad为正方形。所述pad的边长为5μm。每层所述金属层的每个金属条均通过连接件连通到相邻层的一个金属条。通过pad之间的值来测试金属层的电性参数,例如所述金属条的电阻。

37.进一步的,每层所述金属层的n个金属条中除了条数与当层所述金属层的层数相同的金属条,其余n-1个金属条还具有第二开口,所述第一开口和第二开口在所述金属条相对的两个方向。即,所有金属条均具有第一开口,而第x金属层中,除了第x金属条外,其余n-1个金属条还具有第二开口,x的取值为1~n。例如,第一开口在第一边上,则第二开口在第二边上,第一边和第二边为矩形非闭合形状的两个边,并且第一边和第二边平行切相对。例如,图2,第四金属层除第四金属条边外,另三个金属条均有第二开口;图3,第三金属层除第

三金属条边外,另三个金属条均有第二开口;图4,第二金属层除第二金属条边外,另三个金属条均有第二开口;图5,第一金属层除第一金属条边外,另三个金属条均有第二开口。

38.以n为四举一个例子,四层金属层分别为第一金属层、第二金属层、第三金属层和第四金属层;所述第一金属层位于所述基底上,并且通过介质层和所述基底隔开,所述第一金属层还通过连接件与所述基底的表面连通;所述第二金属层位于所述第一金属层上,并且通过介质层与所述第一金属层隔开;所述第三金属层位于所述第二金属层上,并且通过介质层与所述第二金属层隔开;所述第四金属层位于所述第三金属层上,并且通过介质层与所述第三金属层隔开。

39.进一步的,每层所述金属层包括四个金属条,分别为第一金属条、第二金属条、第三金属条和第四金属条;所述第一金属条围绕于所述芯片形成非闭合的环状结构;所述第二金属条围绕于所述第一金属条形成非闭合的环状结构;所述第三金属条围绕于所述第二金属条形成非闭合的环状结构;所述第四金属条围绕于所述第三金属条形成非闭合的环状结构。本发明实施例的线宽以及线之间的距离都可以在制作之前通过设计规则设定好。请参照图2至图6,图2是第四金属层也就是top金属层的俯视图,第四金属层中,除了第四金属条440只有第一开口外,第一金属条410、第二金属条420和第三金属条430均有第一开口和第二开口,并且第一开口和第二开口在相对的方向,此时,测试第四金属条440上的两个电性测试键510就可以测试第四金属条的电性,例如,第四金属条的电阻。测试相邻金属条的电性测试键510可以测试相邻金属条之间的电性参数,例如bvd或漏电流,金属层包括金属条,因此,间接测试了金属层的电性参数。图3是第三金属层的俯视图,第三金属层中,除了第三金属条330只有第一开口外,第一金属条310、第二金属条320和第四金属条340均有第一开口和第二开口,并且第一开口和第二开口在相对的方向,此时,测试第三金属条330上的两个电性测试键510就可以测试第三金属条的电性,例如,第三金属条的电阻。图4是第二金属层的俯视图,第二金属层中,除了第二金属条220只有第一开口外,第一金属条210、第三金属条230和第四金属条240均有第一开口和第二开口,并且第一开口和第二开口在相对的方向,此时,测试第二金属条220上的两个电性测试键510就可以测试第二金属条的电性,例如,第二金属条的电阻。图5是第一金属层的俯视图,第一金属层中,除了第一金属条110只有第一开口外,第二金属条120、第三金属条130和第四金属条140均有第一开口和第二开口,并且第一开口和第二开口在相对的方向,此时,测试第一金属条110上的两个电性测试键510就可以测试第一金属条的电性,例如,第一金属条的电阻。而第一金属条和第二金属条以及第三金属条的第一开口和第四金属条的开口也均不在一个方向,优选的,可以各在一个方向,第一金属条和第二金属条和第三金属条以及第四金属条的第一开口可以分别在矩形的四个边的方形,如果再有第五金属条,则第五金属条的第一开口可以和第一金属条的第一开口在同一个方向,以上均是为了形成更规则更节省面积的金属条的优选方式,在本发明的其他实施例中,第一开口可以是不规则不限定方向的形式。而为了方便测试,电性测试键510都可以放在第一开口的端部金属条上,两个端部就可以各形成一个pad。请继续参照图6,图6是图2中的ab线切开的纵截面图,第一金属层的第一金属条110、第二金属层的第一金属条210、第三金属层的第一金属条310和第四金属层的第一金属条410均通过连接件600连通;第一金属层的第二金属条120、第二金属层的第二金属条220、第三金属层的第二金属条320和第四金属层的第二金属条420均通过连接件600连通;第一金属层的第三金

属条130、第二金属层的第三金属条230、第三金属层的第三金属条330和第四金属层的第三金属条430均通过连接件600连通,第一金属层的第四金属条140、第二金属层的第四金属条240、第三金属层的第四金属条340和第四金属层的第四金属条440均通过连接件600连通。

40.本发明实施例可以在wat测试或者在线测试时进行金属条的电阻测试,因此,每一层金属层制作完成后,就可以在线通过对电性测试键的测试获得金属条的电阻。在完成整个金属层的制作后,也可以通过top金属层(第n层金属层)的测试键测试金属层的电性。

41.综上,在本发明实施例提供的芯片密封环中,通过电性测试键的信号以获得与电性测试键连通的金属条的电性参数,而金属层包括金属条,所以能通过电性测试键的信号测试金属层的电性参数,因此,本发明的芯片密封环不但可以在切割晶圆形成独立芯片时,保护芯片不会受到切割产生的机械力的影响,同时,还可以对电性进行测试,减少切割道上的电性测试键,从而减少切割道的宽度,以在晶圆上形成更多的芯片。

42.上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1