高电压去耦电容器和集成方法与流程

1.所公开的实施例一般地涉及半导体器件中的隔离结构,更具体地涉及能够在高电压下工作的去耦电容器及其制造方法。

背景技术:

2.电气系统通常包含若干个电路,这些电路可以彼此通信但在不同的电压下工作。例如,以110v/220v交流电(ac)工作的微波炉可以在其内部产生高达2800v。高电压必须与用户或系统内的其他电路隔离,同时仍允许在不同电路之间交换信息。电流隔离可用于防止直流电流在不同电路之间流动,同时仍允许交换信号或能量以实现不同电路之间的通信。

3.去耦电容器可用于对电气系统的不同电路进行电流隔离以防止杂散电流流动。物理空间限制可能使得难以在集成电路中实现具有足够高击穿电压的去耦电容器。例如,去耦电容器可以在集成电路的金属化层或后段制程(beol)层中制造。然而,由于被隔离的电路之间会出现可能在数千伏量级的大电压差,因此需要具有比使用该技术制造的击穿电压更高的击穿电压的去耦电容器。因此,需要一种改进的去耦电容器来克服上述挑战。

技术实现要素:

4.在本公开的一方面,提供了一种电容器。所述电容器包括第一导电层,其位于衬底中的第一隔离区中。多个电介质层布置在所述第一隔离区上方。第二导电层布置在所述多个电介质层上方,其中所述第二导电层与所述第一导电层至少部分地重叠。

5.在本公开的另一方面,提供了一种半导体器件。所述半导体器件包括衬底,其包括绝缘层和位于所述绝缘层上方的有源层。第一隔离区布置在所述有源层和所述绝缘层中。第二隔离区布置在所述有源层中,与所述第一隔离区横向相邻。设置电容器。所述电容器包括位于所述第一隔离区中的第一导电层。所述第一导电层是所述电容器的底板。多个电介质层布置在所述第一隔离区上方。第二导电层布置在所述多个电介质层上方。所述第二导电层是所述电容器的顶板,并且所述第二导电层与所述第一导电层至少部分地重叠。

6.在本公开的又一方面,提供了一种制造半导体器件的方法。所述方法包括提供包括绝缘层和位于所述绝缘层上方的有源层的衬底。在所述绝缘层和所述有源层中设置第一隔离区。在所述有源层中设置第二隔离区,其中所述第二隔离区与所述第一隔离区的上部横向相邻。设置电容器。所述电容器包括布置在所述第一隔离区中的第一导电层。多个电介质层布置在所述第一隔离区上方。第二导电层布置在所述多个电介质层上方,其中所述第二导电层与所述第一导电层至少部分地重叠。

7.以下描述的实施例中提供了许多优点。实施例提供了能够高电压工作的去耦电容器。该去耦电容器可以用现有的衬底和金属化堆叠制造,不需要额外的金属化层。该去耦电容器的第一导电层可以集成到衬底层中的隔离区中,从而释放用于上覆金属化堆叠的空间。第一隔离区的上部位于有源层的浅沟槽隔离(sti)层内。因此,不会在器件布局中占用

额外的横向空间。

附图说明

8.通过阅读以下结合附图进行的详细描述,将更好地理解所公开的实施例:

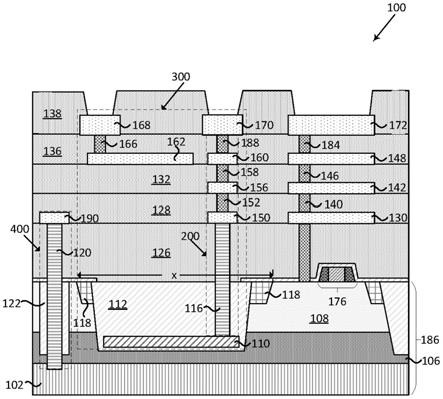

9.图1是根据本公开的实施例的具有去耦电容器的半导体器件。

10.图2至图11示出了根据本公开的一些实施例的用于图1所示的半导体器件的制造工艺流程。

11.为了图示的简单和清楚,附图图示了一般的构造方式,并且可以省略公知的特征和技术的特定描述和细节,以避免不必要地使所描述的器件的实施例的讨论模糊。另外,附图中的元素不一定按比例绘制。例如,附图中的一些元素的尺寸可能相对于其他元素被放大,以帮助提高对器件的实施例的理解。不同附图中的相同参考标号表示相同的元素,而相似的参考标号可以但不一定表示相似的元素。

具体实施方式

12.以下详细描述本质上是示例性的,并非旨在限制器件或者器件的应用和用途。此外,不旨在受到这些器件的先前背景或以下详细描述中提出的任何理论的束缚。

13.图1是根据本公开的实施例的具有去耦电容器300的半导体器件100。参考图1,半导体器件100可以包括具有绝缘层106和位于绝缘层106上方的有源层108的衬底186。第一隔离区112可以布置在绝缘层106和有源层108中。去耦电容器300可以包括第一导电层110、第一隔离区112、多个电介质层126、128和132,以及第二导电层162。在一个实施例中,第一导电层110可以位于第一隔离区112中,并且在优选实施例中,可以位于第一隔离区112的下部中。多个电介质层126、128和132可以位于第一隔离区112上方。第二导电层162可以位于多个电介质层126、128和132上方。在一个实施例中,第二导电层162可以与第一导电层110至少部分地重叠。在另一实施例中,第二导电层162可以与第一导电层110完全重叠。去耦电容器300由虚线轮廓包围。第一导电层110可以作为去耦电容器300的底板,第二导电层162可以作为去耦电容器300的顶板。第一隔离区112和多个电介质层126、128和132可以作为第一导电层110与第二导电层162之间的去耦电容器300的电介质层。

14.第一隔离区112的顶表面可以至少与有源层108的顶表面齐平。第二隔离区118可以布置为与第一隔离区112的上部横向相邻,由此第二隔离区118的宽度x可以大于第一隔离区112。在一个实施例中,第二隔离区118可以比第一隔离区112浅。在一个实施例中,第一隔离区112可以是深沟槽隔离(dti),第二隔离区118可以是浅沟槽隔离(sti)。由于第一隔离区112的上部可以布置在第二隔离区118中,因此去耦电容器300不在半导体器件100中占用额外的横向空间。在一个实施例中,第二隔离区118可以至少部分地围绕第一隔离区112的上部。在另一实施例中,第二隔离区118可以完全围绕第一隔离区112的上部。第一隔离区112可以由合适的电介质材料制成,例如高密度等离子体(hdp)二氧化硅(sio2)或任何其他合适的电介质材料。第二隔离区118可以由合适的电介质材料制成,例如硼磷硅玻璃(bpsg)、原硅酸四乙酯(teos)或任何其他合适的电介质材料。在一个实施例中,第一隔离区112和第二隔离区118可以由相同的电介质材料制成。在另一实施例中,第一隔离区112和第二隔离区118可以由不同的电介质材料制成。

15.在一个实施例中,电介质层126可以是层间电介质(ild)层。电介质层128和132可以分别是第一金属化层150和第二金属化层156的金属间电介质(imd)层。电介质层126可以由合适的电介质材料制成,例如二氧化硅(sio2)、高密度等离子体(hdp)未掺杂硅酸盐玻璃(usg)、原硅酸四乙酯(teos)或任何其他合适的电介质材料。电介质层128和132可以由合适的电介质材料制成,例如二氧化硅、未掺杂硅酸盐玻璃(usg)、氟化硅酸盐玻璃(fsg)、原硅酸四乙酯(teos)或任何其他合适的电介质材料。

16.第一隔离区112可以延伸穿过有源层108和绝缘层106的上部。第一隔离区112可以布置在绝缘层106的下部上方。在一个实施例中,第一导电层110可以布置在第一隔离区112的下部中。在另一实施例中,第一导电层110可以布置在第一隔离区112的底表面上方。在另一实施例中,第一导电层110可以位于第一隔离区112的上部中。衬底186可以包括位于绝缘层106下方的基层102。在一个实施例中,衬底186可以是绝缘体上硅(soi)衬底。绝缘层106的下部和第一隔离区112的下部可以位于第一导电层110与基层102之间以使电容器300的第一导电层110与衬底186的基层102电隔离。

17.去耦电容器300可以包括位于第一导电层110上方的第一互连200,由此第一互连200延伸穿过第一导电层110上方的第一隔离区112的一部分并且穿过多个电介质层126、128、132和136以耦接到第一接合衬垫(pad)170。在替代实施例中,第一互连200可以延伸穿过第一隔离区112的一部分并且穿过多个电介质层126、128、132和136以耦接到金属化线。去耦电容器300可以包括位于第二导电层162上方的第二互连166,由此第二互连166可以延伸穿过电介质层136以耦接到第二接合衬垫168。在替代实施例中,第二互连166可以延伸穿过电介质层136以耦接到另一金属化线。在一个实施例中,电介质层136可以是金属间电介质(imd)层。第一接合衬垫170和第二接合衬垫168可以连接到单独的外部输入端子或单独的电路。第一互连200可以包括多个接触柱116、152、158和188以及金属化层150、156和160。第二互连166可以包括接触柱。

18.第三互连400可以从基层102延伸穿过绝缘层106、有源层108和电介质层126以对基层102进行电偏置。在一个实施例中,第三互连400可以耦接到地端子以将衬底186的基层102接地。第三互连400可以包括接触柱120和金属化层190。

19.上述实施例提供了包括去耦电容器300的半导体器件100,该去耦电容器300由于第一导电层110与第二导电层162之间的较厚电介质层而具有高击穿电压。在一个实施例中,第一隔离区112可以是由合适的电介质层制成,例如二氧化硅(sio2)层。位于第一导电层110上方的第一隔离区112的一部分可以具有约3至4微米(μm)的厚度范围。在一个实施例中,电介质层126、128和132可以由合适的电介质材料制成,例如二氧化硅(sio2)。电介质层126可以具有约0.55至0.95微米(μm)的厚度范围。电介质层128和132可以具有约0.6至1微米(μm)的厚度范围。由此,第一导电层110与第二导电层162之间的电介质层的总厚度介于4至10微米(μm)之间。在一个实施例中,第一导电层110和第二导电层162可以是金属层。

20.图2至图11示出了根据本公开的一些实施例的用于图1所示的半导体器件100的制造工艺流程。图2是根据本公开的实施例的在衬底186的有源层108中具有开口192的部分完成的半导体器件100。参考图2,可以提供合适的衬底186,例如绝缘体上硅(soi)衬底。衬底186可以包括基层102、位于基层102上方的绝缘层106和位于绝缘层106上方的有源层108。基层102可以包括硅。绝缘层106可以包括二氧化硅。有源层108可以包括单晶硅。牺牲二氧

化硅层196和氮化硅层198可以沉积在衬底186的有源层108的顶表面上并且通过常规光刻工艺和湿蚀刻或干蚀刻工艺而被图案化。常规光刻工艺可以包括在牺牲二氧化硅层196和氮化硅层198上方沉积光致抗蚀剂层,随后进行曝光和显影以形成合适的光致抗蚀剂图案。湿蚀刻或干蚀刻工艺可用于去除未被光致抗蚀剂图案覆盖的牺牲二氧化硅层196和氮化硅层198的一部分,并留下牺牲二氧化硅层196和氮化硅层198的另一部分作为硬掩模层216。随后可以去除光致抗蚀剂层。可以使用湿蚀刻或干蚀刻工艺去除未被硬掩模层216覆盖的有源层108的一部分,以在有源层108中形成开口192。随后可以去除硬掩模层216。

21.图3是根据本公开的实施例的在衬底186的有源层108中形成第二隔离区118之后部分完成的半导体器件100。参考图3,可以通过合适的沉积工艺,例如原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在开口192中沉积合适的电介质材料层,例如二氧化硅(sio2)层。有源层108的顶表面上方的二氧化硅层的一部分可以通过合适的平面化工艺,例如化学机械平面化(cmp),而被平面化以在开口192中留下二氧化硅层的另一部分,从而形成第二隔离区118。

22.图4是根据本公开的实施例的在形成开口208和210之后部分完成的半导体器件100。参考图4,开口208延伸穿过第二隔离区118、有源层108和绝缘层106的上部。开口210延伸穿过有源层108和绝缘层106的一部分。开口208和210的形成可以包括沉积光致抗蚀剂层,并通过常规光刻工艺而图案化光致抗蚀剂层,以在衬底186的第二隔离区118的一部分和源层108的一部分上方形成具有开口的合适的光致抗蚀剂图案。可以使用湿蚀刻或干蚀刻工艺去除未被光致抗蚀剂图案覆盖的第二隔离区118的一部分、有源层108的一部分和绝缘层106的一部分,从而形成开口208。类似地,可以使用湿蚀刻或干蚀刻工艺去除未被光致抗蚀剂图案覆盖的有源层108的一部分和绝缘层106的一部分,从而形成开口210。随后可以在蚀刻工艺之后去除光致抗蚀剂图案。

23.图5是根据本公开的实施例的在形成第一隔离区112和第三隔离区122之后部分完成的半导体器件100。在实施例中,第一隔离区112和第三隔离区122可以是深沟槽隔离(dti)区。参考图5,第一隔离区112的上部形成在第二隔离区118中,并且第一隔离区112的下部延伸穿过有源层108和绝缘层106的一部分。第三隔离区122形成在有源层108和绝缘层106的一部分中。第一和第三隔离区112和122的形成可以分别包括通过合适的沉积工艺,例如原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,分别在开口208和210中沉积合适的电介质材料层,例如二氧化硅层。可以使用合适的平面化工艺,例如化学机械平面化(cmp),从第二隔离区118的顶表面去除二氧化硅层的一部分,以在开口208中留下二氧化硅层的另一部分,从而形成第一隔离区112。类似地,可以使用合适的平面化工艺,例如化学机械平面化(cmp),从有源层108的顶表面去除二氧化硅层的一部分,以在开口210中留下二氧化硅层的另一部分,从而形成第三隔离区122。第一隔离区112的上部形成在第二隔离区118中,从而导致紧凑的半导体器件100,这是因为第一隔离区112没有在衬底186的有源层108中占用额外的横向面积。

24.图6是根据本公开的实施例的在有源层108上方形成栅极结构176和和电介质衬里(liner)178之后部分完成的半导体器件100。栅极结构176的形成在本领域中是公知的,将不再进一步详述。尽管未示出,但是可以在有源层108中形成掺杂半导体区以形成与栅极结构176相邻的源极和漏极。电介质衬里178的形成可以包括通过合适的沉积工艺,例如原子

层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在有源层108的顶表面上方、第三和第一隔离(dti)区122和112的顶表面上方、第二隔离区118的顶表面上方以及栅极结构176上方沉积合适的电介质材料层,例如氮化硅(si3n4)层,从而形成电介质衬里178。电介质衬里178可以用作蚀刻停止层,以停止上覆层的蚀刻去除过程。

25.图7是根据本公开的实施例的在形成电介质层126以及开口180和182之后部分完成的半导体器件100。在一个实施例中,电介质层126可以是层间电介质(ild)层。参考图7,电介质层126可以形成在电介质衬里178上方。电介质层126的形成可以包括通过合适的沉积工艺,例如原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在电介质衬里178上方沉积合适的电介质材料层,例如二氧化硅层,从而形成电介质层126。开口180可以形成在电介质层126中、电介质衬里178中以及第三隔离区122中。开口182可以形成在电介质层126中、电介质衬里178中以及第一隔离区112中。开口180和182的形成可以包括沉积光致抗蚀剂层以及通过常规光刻工艺图案化该光致抗蚀剂层以形成合适的光致抗蚀剂图案。可以使用湿蚀刻或干蚀刻工艺去除未被光致抗蚀剂图案覆盖的电介质层126的一部分、电介质衬里178的一部分和第三隔离区122的一部分,从而形成开口180。随后可以去除光致抗蚀剂层。类似地,可以使用湿蚀刻或干蚀刻工艺去除电介质层126的一部分、电介质衬里178的一部分和第一隔离区112的一部分,从而形成开口182。

26.图8是根据本公开的实施例的在形成第一导电层110、第三和第一隔离区122和112、以及电介质层126之后的部分完成的半导体器件100。参考图8,第一导电层110的形成可以包括通过合适的沉积工艺,例如原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在第一隔离区112的下部上方的开口182中沉积合适的导电材料层,例如铝(al)层、钨(w)层、氮化钛(tin)层、钴(co)层或任何其他合适的导电材料层。可以在铝层上沉积光致抗蚀剂层并通过常规光刻工艺图案化该光致抗蚀剂层以形成合适的光致抗蚀剂图案。可以使用湿蚀刻或干蚀刻工艺去除未被光致抗蚀剂图案覆盖的铝层的一部分,在第一隔离区112的下部上方留下铝层的另一部分,从而形成第一导电层110。随后可以去除光致抗蚀剂图案。第三和第一隔离区122和112以及电介质层126的形成可以包括通过合适的沉积工艺,例如原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在第一导电层110上方的开口180和开口182中沉积合适的电介质材料层,例如二氧化硅层。可以使用合适的平面化工艺,例如化学机械平面化(cmp),从电介质层126的顶表面去除二氧化硅层的一部分,在开口180和182中留下二氧化硅层的另一部分,从而分别形成第三和第一隔离区122和112,以及分别位于第三和第一隔离区122和112上方的电介质层126的一部分。

27.图9是根据本公开的实施例的在形成开口220和222之后部分完成的半导体器件100。参考图9,开口220延伸穿过电介质层126、第三隔离区122、绝缘层106、以及基层102的上部。开口222延伸穿过电介质层126、以及第一隔离区112的一部分,以暴露第一导电层110的一部分。开口220和222的形成可以包括在电介质层126上方沉积光致抗蚀剂层,以及通过常规光刻工艺图案化所沉积的光致抗蚀剂层以形成合适的光致抗蚀剂图案。可以使用湿蚀刻或干蚀刻工艺去除未被光致抗蚀剂图案覆盖的电介质层126的一部分、第三隔离区122的一部分、绝缘层106的一部分和基层102的一部分,从而形成开口220。类似地,可以使用湿蚀刻或干蚀刻工艺去除未被光致抗蚀剂图案覆盖的第一导电层110上方的电介质层126的一

部分和第一隔离区112的一部分,从而形成开口222。随后可以去除光致抗蚀剂图案。

28.图10是根据本公开的实施例的在形成接触柱116和120之后部分完成的半导体器件100。参考图10,接触柱116可以延伸穿过电介质层126和第一隔离区112的一部分以接触第一导电层110。接触柱120可以延伸穿过电介质层126、第三隔离区122、绝缘层106、以及基层102的上部。接触柱116和120可以通过以下方式形成:即,通过合适的沉积方法,例如原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在开口220和222中沉积合适的导电材料层,例如钨(w)层或任何其他合适的导电材料层。可以使用合适的平面化工艺,例如化学机械平面化(cmp),从电介质层126的顶表面去除钨层的一部分,在开口220和222中留下钨层的另一部分,从而分别形成接触柱120和116。尽管未示出,但是在一个实施例中,去耦电容器300的第二导电层162可以形成在接触柱116和电介质层126上方。

29.图11是根据本公开的实施例的分别在接触柱116和120上方形成金属化层150和190之后部分完成的半导体器件100。参考图11,金属化层150的形成可以包括在电介质层126上方和接触柱116上方沉积光致抗蚀剂层。可以使用常规光刻工艺图案化光致抗蚀剂层以在接触柱116上方形成开口。可以通过合适的沉积工艺,例如电镀、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺,在接触柱116上方的开口中沉积合适的导电材料层,例如铜(cu)层、铝(al)层或任何其他合适的导电材料层。可以在剥离工艺中去除光致抗蚀剂层以在接触柱116上方留下铜层的一部分,从而形成金属化层150。金属化层190和栅极结构176上方的金属化层130也可以通过类似于金属化层150的形成的常规光刻工艺、导电层沉积和随后的剥离工艺而形成。

30.返回参考图1,其中示出了根据本公开的实施例的在形成电介质层128、132、136和138,接触柱152、158、188、140、146、184和166,金属化层156、160、142、148,第二导电层162,以及接合衬垫168、170和172之后的半导体器件100。参考图1,电介质层128可以形成在金属化层150、130和190上方以及电介质层126上方。在一个实施例中,电介质层128可以是金属间电介质(imd)层。接触柱152可以形成在电介质层128中且在金属化层150上方。接触柱140可以形成在电介质层128中且在金属化层130上方。接触柱152和140的形成可以包括分别在金属化层150和130上方的电介质层128中形成开口。可以在开口中沉积合适的导电材料,例如钨或任何其他合适的导电材料。可以使用合适的平面化工艺,例如化学机械平面化,从电介质层128的顶表面去除钨,以在金属化层150和130上方的开口中留下另一钨层,从而分别形成接触柱152和140。金属化层156和142可以分别形成在接触柱152和140上方。电介质层132可以形成在电介质层128上方以及金属化层156和142上方。在一个实施例中,电介质层132可以是金属间电介质(imd)层。接触柱158可以形成在电介质层132中且在金属化层156上方。接触柱146可以形成在金属化层142上方的电介质层132中。接触柱158和146的形成可以包括分别在金属化层156和142上方的电介质层132中形成开口。可以在开口中沉积合适的导电材料,例如钨或任何其他合适的导电材料。可以使用合适的平面化工艺,例如化学机械平面化,从电介质层132的顶表面去除钨,以在金属化层156和142上方的开口中留下另一钨层,从而分别形成接触柱158和146。

31.金属化层160和148可以分别形成在接触柱158和146上方。去耦电容器300的第二导电层162可以形成在第一导电层110上方的第一隔离区112的一部分上方、电介质层126、

128和132上方。去耦电容器300的第二导电层162以及金属化层160和148可以由相同的导电材料制成。电介质层136可以形成在第二导电层162上方以及金属化层160和148上方。在一个实施例中,电介质层136可以是金属间电介质(imd)层。接触柱166、188和184可以形成在去耦电容器300的第二导电层162上方以及金属化层160和148上方的电介质层136中。接触柱166、188和184的形成可以包括分别在第二导电层162以及金属化层160和148上方的电介质层136中形成开口。可以在开口中沉积合适的导电材料,例如钨或任何其他合适的导电材料。可以使用合适的平面化工艺,例如化学机械平面化,从电介质层136的顶表面去除钨,以分别在第二导电层162以及金属化层160和148上方的开口中留下另一钨层,从而分别形成接触柱166、188和184。接合衬垫168、170和172可以分别形成在接触柱166、188和184上方。接合衬垫168、170和172的形成可以包括与第二导电层162以及金属化层160和148的形成类似的常规光刻工艺、导电层沉积以及随后的剥离工艺。电介质层138可以形成在接合衬垫168、170和172上方。开口可以形成在电介质层138中以暴露接合衬垫168、170和172。在一个实施例中,接触柱140、146和184以及金属化层130、142和148可用于将栅极结构176连接到输入或输出端子。

32.电介质层128、132、136和138可以由与电介质层126相同的电介质材料制成并且使用相同的沉积工艺沉积。在一个实施例中,去耦电容器300的第二导电层162以及金属化层156、142、160和148可以由与金属化层150、130和190相同的导电材料制成并且使用相同的沉积和图案化工艺来制造。在另一实施例中,去耦电容器300的第二导电层162可以由与金属化层150、130、190、156、142、160和148不同的导电材料制成。

33.说明书和权利要求书中的术语“第一”、“第二”、“第三”等(如果有)用于区分相似的元素,而并不一定用于描述特定的次序或时间顺序。应当理解,如此使用的术语在适当的情况下是可互换的,以使得本文描述的器件的实施例例如能够以不同于本文示出或以其他方式描述的顺序操作。说明书和权利要求书中的术语“左”、“右”、“前”、“后”、“顶部”、“底部”、“上方”、“下方”等(如果有)是用于描述的目的,而不一定用于描述永久性的相对位置。应当理解,如此使用的术语在适当的情况下是可互换的,以使得本文描述的器件的实施例例如能够以不同于本文示出或以其他方式描述的取向操作。类似地,如果本文描述的方法包括一系列步骤,则本文中呈现的这些步骤的顺序不一定是可以执行这些步骤的唯一顺序,所述步骤的特定步骤可以被省略和/或另外一些在此未描述的特定步骤可以被添加到该方法中。此外,术语“包括”、“包含”、“具有”及其任何变体旨在涵盖非排他性的包含内容,使得包括一系列元素的过程、方法、物品或器件不一定限于这些元素,而是可以包括未明确列出的或并非这些过程、方法、物品或器件所固有的其他元素。

34.尽管上面对器件的详细描述中已经给出了若干示例性实施例,但是应当理解,存在许多变型。还应当理解,实施例仅是示例,并非旨在以任何方式限制器件的范围、适用性、尺寸或配置。而是,上面的详细描述将为本领域技术人员提供实现器件的示例性实施例的便利指南,将理解,在不偏离所附权利要求中陈述的本公开范围的情况下,可以对示例性实施例中描述的元素的功能和布置及其制造方法进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1